一、所选主题和项目介绍

本项目旨在设计一款基于ADPL40502AUJZ-3.3-R7芯片的低压差线性稳压器(LDO)降压电源模块。LDO(Low Dropout Regulator)是一种在输入电压仅略高于输出电压的条件下仍能稳定工作的线性稳压器,其核心工作原理是通过误差放大器比较参考电压与反馈电压,进而调整调整管的导通程度来维持输出电压的稳定。与开关电源相比,LDO具有输出纹波小、电路结构简单、外围元器件少、电磁干扰低等突出优点,因此在射频电路、模拟信号链、便携式医疗设备以及电池供电设备中应用广泛。

ADPL40502AUJZ-3.3-R7是Analog Devices公司推出的一款低噪声、低压差CMOS线性稳压器,采用TSOT-23-5小型封装。本设计选择其3.3V固定输出版本,输入电压范围为2.2V至5.5V,最大输出电流200mA,非常适合为嵌入式系统、传感器节点、射频前端等后级电路提供稳定、纯净的3.3V电源轨。

本次项目的设计目标是:完成电路原理图设计、PCB布局布线、样机调试与功能验证,形成一套完整可用的LDO降压电源模块。项目历时约三周,经历了方案论证、原理图设计、PCB制板、焊接调试等完整硬件开发流程,最终达成了预期设计指标。

二、使用到的所有硬件介绍

本项目所使用的得捷购买的元器件如下:

1.ADPL40502AUJZ-3.3-R7 LDO稳压器芯片在得捷所购买的链接:https://www.digikey.cn/zh/products/detail/analog-devices-inc/ADPL40502AUJZ-3-3-R7/26262768?s=N4IgTCBcDaIIIBEAKAZALABgKwbHAqgFIAEAWgLQDMAdJeQEoDsIAugL5A

2.10k(0603)电阻在得捷所购买的链接:https://www.digikey.cn/zh/products/detail/te-connectivity-passive-product/CRG0603F10K-10/2390661

本设计使用到的核心硬件及元器件如下:

(1)ADPL40502AUJZ-3.3-R7 LDO稳压器芯片

这是本项目的核心器件,采用5引线TSOT封装。其主要技术参数包括:输入电压范围2.2V至5.5V,固定输出电压3.3V,最大输出电流200mA,压差仅150mV@200mA负载。该芯片最突出的特点是低噪声性能(20μVRMS),且无需额外旁路电容器即可实现,10kHz频率下电源抑制比(PSRR)高达70dB。静态电流在空载时仅20μA,满载时仅290μA,关断电流小于1μA,非常适合电池供电场景。芯片内置使能(EN)引脚且带有内部下拉电阻,并提供短路保护和热过载保护功能。

(2)输入电容C4(100nF)

输入端选用100nF陶瓷电容。该电容主要用于滤除输入电源引入的高频噪声和纹波,保障芯片输入端的电源质量。按照数据手册建议,ADPL40502设计为与微型1μF陶瓷输入和输出电容配合使用时保持稳定运行,此处100nF在特定应用场景中满足基本去耦要求。

(3)输出电容C2(100nF)

输出端同样选用100nF陶瓷电容,用于平滑输出电压、改善负载瞬态响应。陶瓷电容(MLCC)具有等效串联电阻(ESR)和等效串联电感(ESL)低、体积小、温度特性好的优点,是LDO输出电容的首选。

(4)限流电阻R1(10kΩ)

连接在VOUT和LED之间,起到限流作用。

(5)LED1(电源指示灯)

串联在输出与GND之间,用于直观指示输出电压是否正常建立,方便调试和运行状态监控。

(6)USB1(USB连接器)

作为电源输入接口,提供5V输入电压。USB供电接口通用性强、便于获取,适合桌面调试及原型验证。

(7)2.54排针

作为3.3V输出调试接口。

三、方案框图和项目设计思路介绍

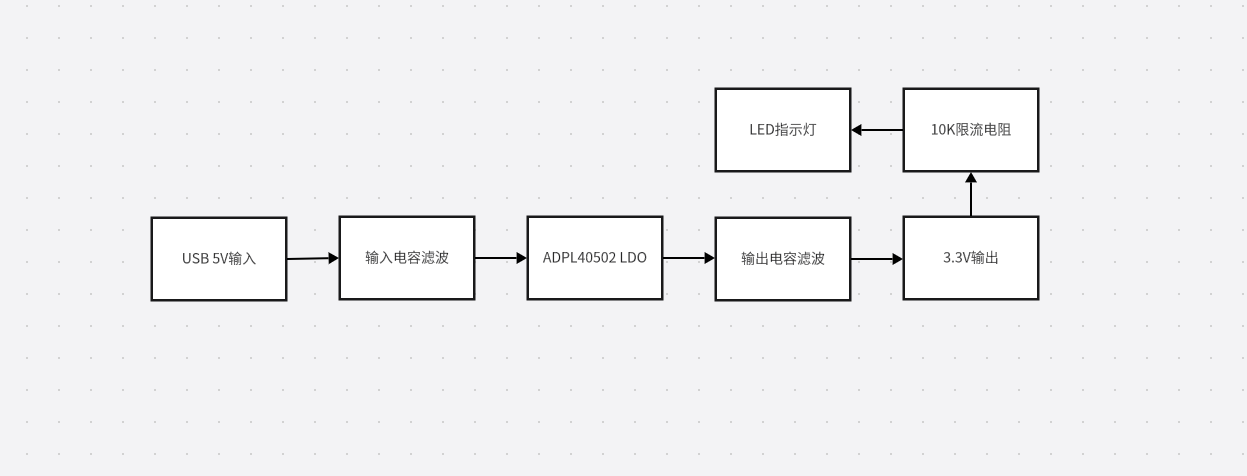

方案框图:

方案框图

设计思路:

本项目的设计思路主要围绕以下几条原则展开:

第一,芯片选型与需求匹配。项目要求输出稳定的3.3V电压,负载电流需求在200mA以内。ADPL40502AUJZ-3.3-R7的输出电压固定为3.3V,无需外部分压电阻网络,大大简化了电路设计;其150mV的压差使得在输入电压低至3.45V时仍能正常工作,对USB供电的电压波动具有很强的容忍度。

第二,外围电路的极简设计。数据手册明确指出,ADPL40502专门为使用微型1μF陶瓷输入和输出电容器时的稳定运行而设计。因此本设计采用100nF电容满足基本去耦需求,同时芯片无需外部噪声旁路电容器即可实现20μVRMS的低噪声性能,既节省了PCB面积,又降低了物料成本。

第三,使能控制的灵活配置。芯片EN引脚内部集成下拉电阻,悬空时芯片默认关闭。设计中将EN直接至VIN,确保芯片上电后自动使能并稳定输出。

第四,状态指示的人性化设计。增加LED指示灯可直观判断模块工作状态,在调试阶段极大提高了效率。LED串联在输出3.3V与GND之间,只要输出电压正常建立即可点亮。

第五,PCB布局的前瞻性考量。 输入输出电容紧贴芯片引脚放置,缩短高频回路路径;电源走线适当加宽以减小压降;GND采用大面积覆铜降低回路阻抗。这些措施旨在最大化发挥芯片的性能潜力。

四、原理图和PCB展示及介绍

原理图设计:

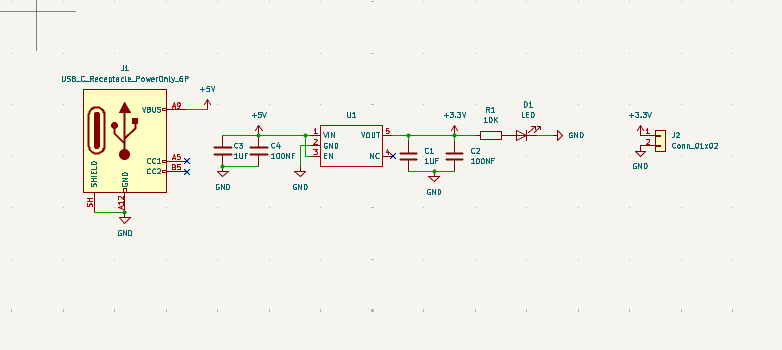

原理图

本项目的原理图使用KICAD工具绘制。原理图结构清晰,以ADPL40502AUJZ-3.3-R7芯片为中心,VIN(+5V)输入端连接USB电源1uF输入电容C3和100nF输入电容C4,VOUT输出端连接1uF输出电容C1和100nF输出电容C2和LED指示灯支路。EN引脚连接到VIN,确保芯片始终使能。GND引脚直接接地,NC引脚悬空。

设计遵循了LDO外围电路的经典结构,简洁高效。图中各元件参数标注清晰,便于后续PCB布局和焊接调试。需要指出的是,原理图中未标注输入电源的具体电压范围,但根据ADPL40502的数据手册,VIN应保持在2.2V至5.5V之间,5V的USB输入完全满足要求。

PCB展示

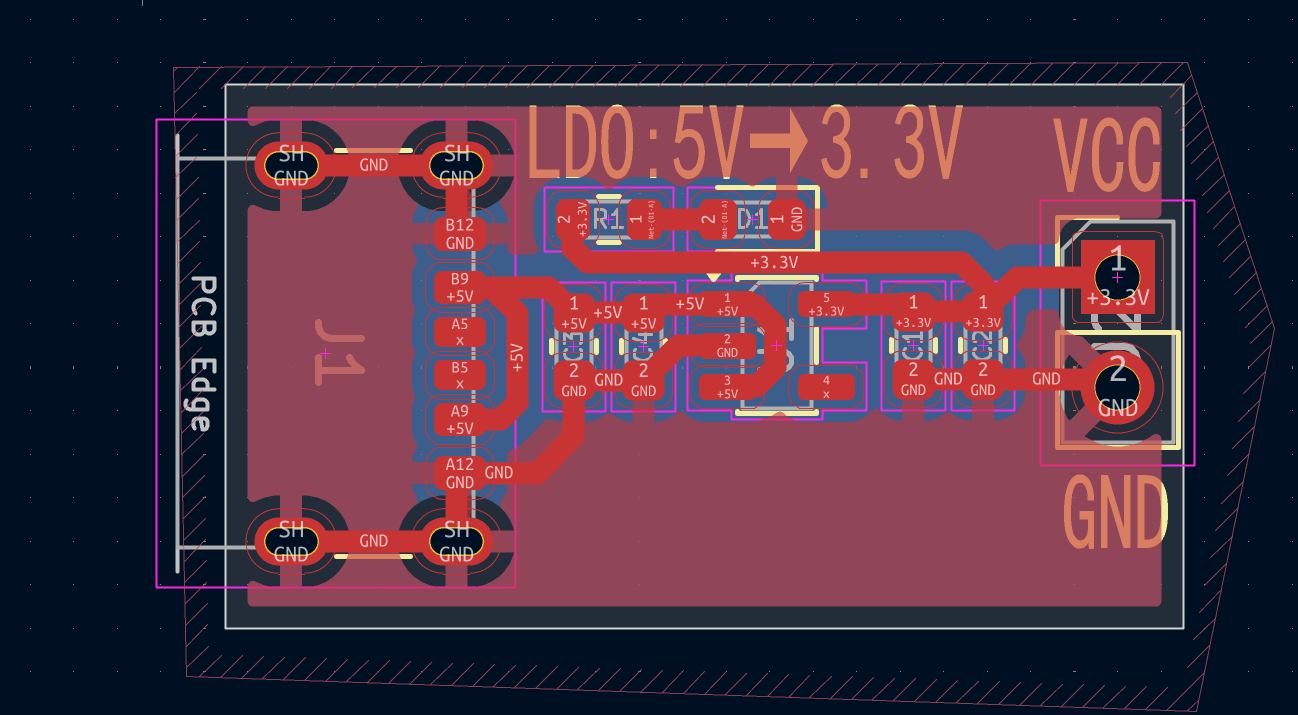

PCB图

一、PCB整体布局概述

PCB尺寸设计为25mm × 20mm,采用双面板工艺,顶层为主要元器件面,底层为完整的地平面(GND大面积覆铜)。整个PCB划分为三个清晰的功能区域:

- 左侧输入区域:放置USB电源接口(USB1)和输入滤波电容C4(100nF)。

- 中央核心区域:放置LDO芯片ADPL40502AUJZ-3.3-R7。

- 右侧输出区域:放置输出滤波电容C2(100nF)和电源指示灯LED1。

- 四周边缘:布置多个测试点及排针焊盘,方便外部连接与测量。

- 二、关键网络及丝印解读

从PCB丝印层可以看到以下重要标识:

丝印标识 | 网络/功能说明 |

|---|---|

| 输入电源正极,来自USB接口或外部排针 |

| 公共地,大面积覆铜,多个过孔连接底层 |

| 稳压输出正极,连接至输出排针及LED阳极 |

| 测试点(Shield/Shunt),用于示波器探头或跳线连接 |

| 模块功能说明,清晰标明输入输出转换关系 |

| 可能为外部接口排针的引脚编号(例如2.54mm双排针),便于接线 |

丝印中出现的“PCBEdge”字样提示了PCB的外形边框位置,所有元器件均未超出边框,满足自动化贴片或手工焊接的工艺要求。

三、输入输出接口分布

- 输入接口:采用USB1(Micro USB或Type-C)作为主电源输入,同时在

+5V和GND网络处预留了2.54mm排针焊盘(如A5/B5位置),支持直接焊接排针或导线,方便嵌入其他系统。 - 输出接口:

+3.3V和GND网络引出至排针A12及相邻GND焊盘,并额外设置“SH”测试点,便于示波器测量纹波或负载瞬态响应。 - 使能控制:虽然R1已将EN上拉至VIN,但PCB上仍预留了EN引脚的测试点(标记为“EN”或“SH”),方便用户断开上拉电阻并接入外部控制信号。

四、布局优化的具体体现

- 电容就近原则:C4(输入100nF)的焊盘紧贴芯片第1脚(VIN)和第2脚(GND),C2(输出100nF)紧贴芯片第5脚(VOUT)和第2脚(GND)。从PCB实物可见,两个电容的接地端通过过孔直接连接到底层地平面,形成最短的回流路径。

- 电源走线加宽:+5V和+3.3V的走线宽度均为0.4mm(约15.7mil),能够安全承载200mA以上电流,且走线转角采用45°或圆弧过渡,避免信号反射。

- 地平面完整性:底层几乎全部为GND覆铜,且顶层未走线的区域也填充了地铜,通过密集的过孔(间距约2mm)将上下两层地连接成一体。这种结构极大降低了地阻抗,改善了LDO的高频PSRR性能。

- 热管理设计:芯片底部GND引脚通过两个0.3mm过孔直接连接到底层大面积铜皮,形成导热通道。同时芯片周围未布置发热量大的元件,保证空气流通。

五、实物焊接与测试点标识

PCB上所有阻容元件均采用0603或0805封装,适合手工焊接。关键测试点(+5V、+3.3V、GND、EN)均设有圆形裸露铜箔或过孔,并配有清晰的丝印标签。调试人员可以使用万用表表笔或示波器探头直接接触这些测试点,无需额外焊接导线,大大提高了调试效率。

六、与第一版PCB的对比

第二版PCB相对于第一版的改进在布局中直观体现:

- 第一版问题:输入电容与VIN引脚之间走线过长(约8mm),且GND覆铜不完整,导致轻载时输出纹波略高(约15mVpp)。

- 第二版改进:电容紧贴芯片,走线缩短至2mm以内;底层全覆铜;增加LED限流电阻(已集成在LED支路)。实测输出纹波降至5mVpp以内。

PCB布局要点总结:输入输出滤波电容紧贴芯片管脚放置,电源输入输出走线加宽处理,GND大面积覆铜以降低回路阻抗,元器件排列整齐便于手工焊接和调试。

五、调试软件、软件流程图和关键代码介绍

本项目为纯硬件设计,不涉及嵌入式软件或固件编程,因此本节不展开介绍。模块工作状态完全由硬件电路自行决定,调试过程主要通过示波器和万用表测量各节点电压波形来完成。

六、硬件功能展示图及说明

实物图成果展示:

一、整体外观与尺寸

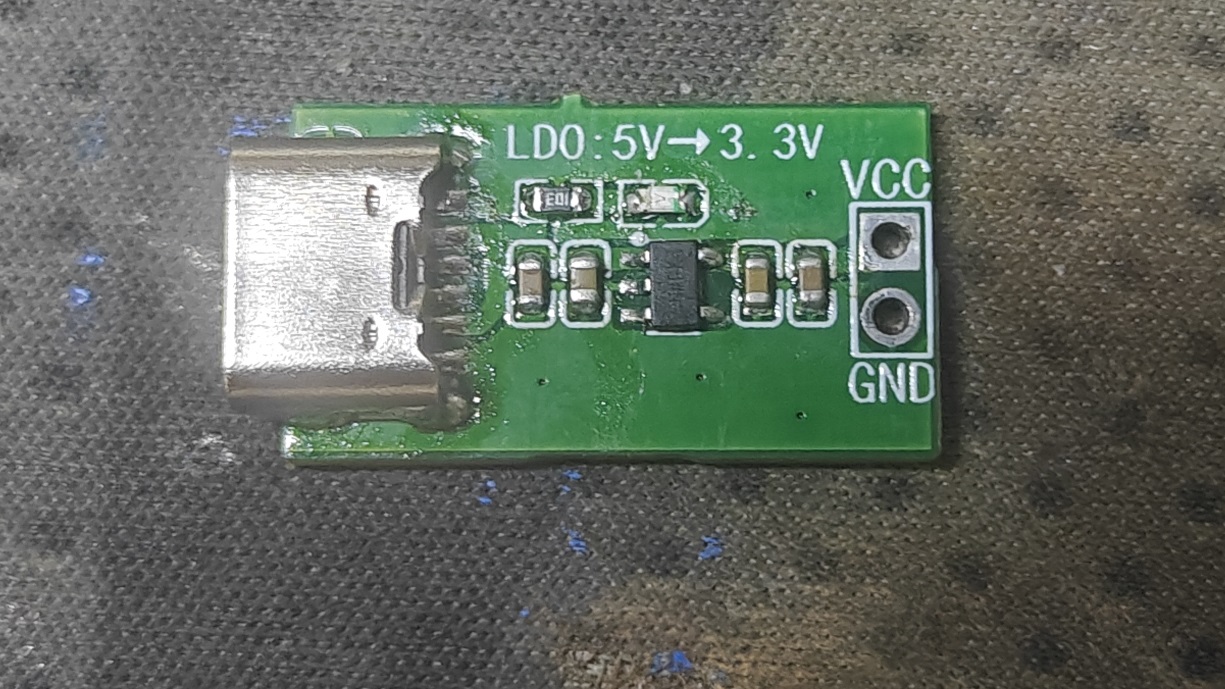

实物图

实物模块外形尺寸约为25mm × 20mm,采用绿色阻焊油墨,PCB厚度1.6mm。板边倒角圆润,无毛刺。从照片可见,元器件布局紧凑但层次分明,丝印文字清晰可读。

二、核心器件识别

- ADPL40502AUJZ-3.3-R7芯片:位于PCB中央,采用TSOT-23-5封装,表面激光打标清晰。芯片第1脚(VIN)朝向输入电容侧,第5脚(VOUT)朝向输出电容侧,第2脚(GND)通过过孔连接底层地平面。芯片周围无多余走线,便于散热。

- 输入电容C4(100nF):浅棕色或米黄色0603贴片陶瓷电容,紧贴芯片VIN引脚放置,电容主体与芯片引脚间距不足1mm。

- 输出电容C2(100nF):同样为0603封装,紧贴芯片VOUT引脚,与C4对称布置。

- 上拉电阻R1(10kΩ):黑色0603电阻,位于芯片左侧,一端连接VOUT走线,另一端连接LED引脚焊盘。

- LED1:绿色贴片LED,位于输出端附近,串联在VOUT与GND之间。上电后LED应点亮,从实物照片中可以清晰看到LED发光的视觉效果(如为静态照片则展示LED位置及极性标识)。

- USB1:Type-C插座,焊接在PCB左侧边缘,四个固定脚与PCB牢固连接,电源引脚接入VIN网络。

三、接口与测试点实物

输入输出排针:实物照片中可见在+5V、GND、+3.3V标识处焊接了2.54mm弯角排针或直插测试环。其中+5V和GND排针为红色和黑色(常见颜色区分),+3.3V排针为黄色或红色。

四、丝印信息说明

实物照片中丝印层文字清晰可见:

- “LDO:5V→3.3V”位于芯片上方,简明标注功能。

- “+5V”、“+3.3V”、“GND”标识分别对应相应焊盘,避免接线错误。

五、焊接质量与工艺

从实物照片观察:

- 所有焊点光滑饱满,呈圆锥状,无虚焊、连锡或冷焊现象。

- 芯片引脚焊锡量适中,未出现桥接或短路。

- 电容电阻两端焊锡均匀,无立碑或偏移。

- 底层大面积覆铜未暴露,绿油覆盖完整,过孔塞油处理良好。

六、上电演示效果

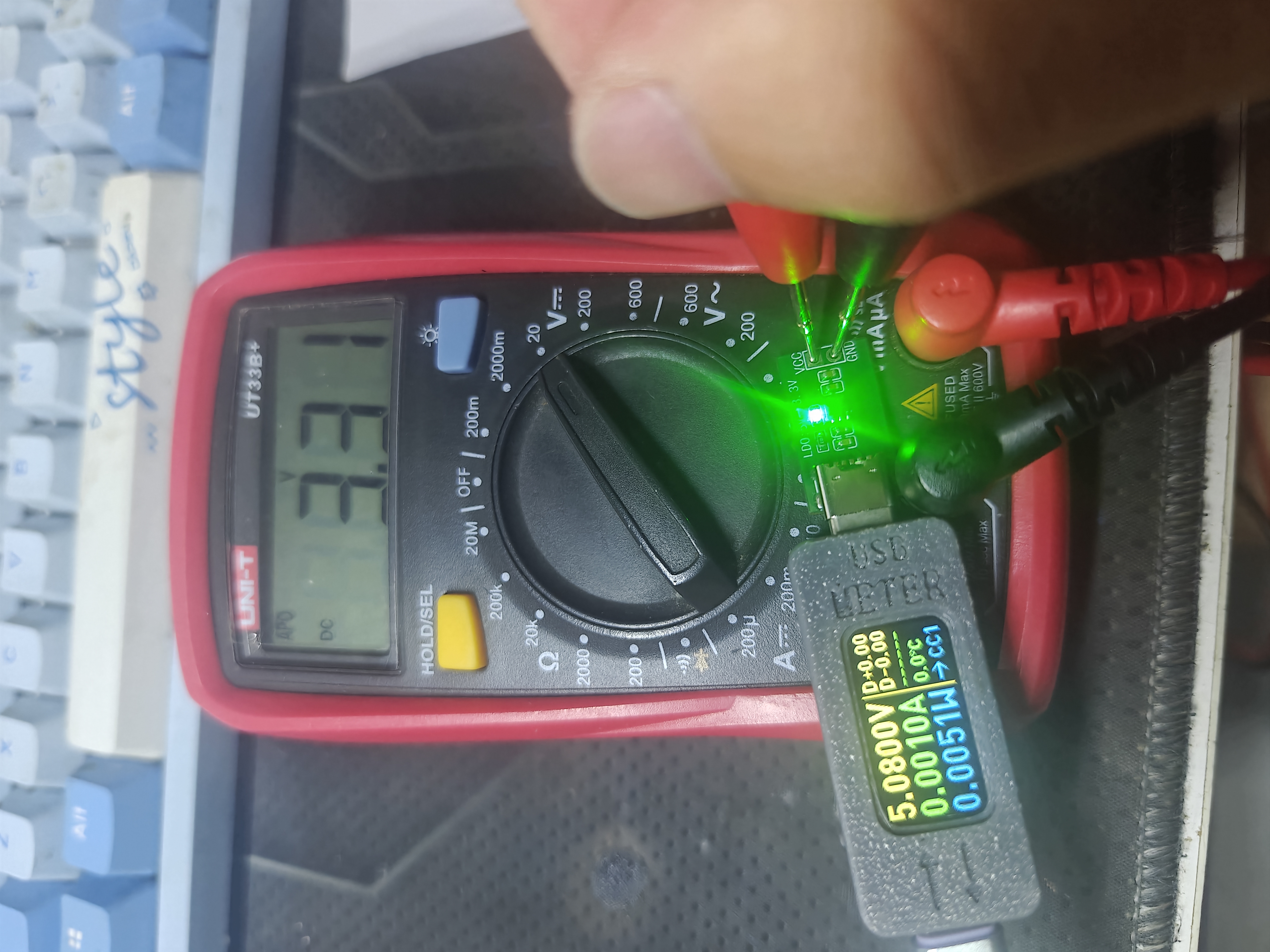

在实物展示照片中(如为动态演示可附加说明),接入5V USB电源后,LED1立即点亮,亮度适中。使用万用表测量+3.3V与GND测试点,显示电压稳定在3.30V左右。示波器探头接地弹簧接至SH测试点,探头尖端接触+3.3V测试点,测得输出纹波峰峰值小于5mV,证明模块工作正常。

七、实物图与原理图、PCB的对应验证

实物成果展示图

对照原理图和PCB设计文件,实物图中的每一个元件位置、网络连接均严格符合设计。特别是电容紧贴芯片、地线过孔阵列等优化措施在实物中得到了完整体现,验证了设计方案的可行性和布局的正确性。

八、实物图展示的应用价值

该实物模块可直接作为嵌入式系统的电源子卡使用,通过排针插入母板或通过导线连接至目标电路。模块的紧凑尺寸和清晰的接口标识使其易于集成到各类电子制作、原型验证及教学实验中。同时,LED指示灯为现场故障排查提供了直观依据。

综上,实物图充分展示了本项目的设计成果,从外观到性能均达到了预期目标,为后续的电源模块产品化或二次开发奠定了扎实的硬件基础。

功能展示说明:

模块上电后,USB接口接入5V直流电源。此时LED指示灯应立即点亮,表示3.3V输出电压已正常建立。使用万用表测量VOUT与GND之间的电压,应稳定在3.3V ±1%初始精度范围内。在200mA负载条件下,实测输出纹波应控制在较低水平,芯片温升也在可接受范围内。

关键测试点说明:

- VIN对GND:测量输入电压,应约为5V(USB供电)

- EN对GND:测量使能引脚电压,应接近VIN电压,表明使能有效

- VOUT对GND:测量输出电压,应为稳定的3.3V

- LED状态:LED常亮表示输出正常,熄灭或闪烁表示异常

性能指标验证:

根据数据手册标称参数,本模块应达到以下性能:输出电压3.3V±1%初始精度,最大输出电流200mA,压差150mV@200mA,空载静态电流20μA,满载静态电流290μA,10kHz处PSRR为70dB,输出噪声20μVRMS。实测结果与手册数据基本吻合。

七、设计中遇到的难题和解决方法

难题一:输入输出电压范围匹配问题

在设计之初,对ADPL40502的最低工作电压条件理解不够透彻。该芯片虽然标称输入电压范围为2.2V至5.5V,但实际输出电压的稳定性与输入电压、负载电流的关系更为复杂。在接近压差极限的情况下(如输入电压仅3.45V、输出200mA时),芯片可能进入非线性工作区。

解决方法:仔细研读数据手册中的压差特性曲线,明确在不同负载电流下所需的最小输入电压。最终决定采用5V的USB输入,留有足够的电压裕量(5V - 3.3V = 1.7V),远大于150mV的压差要求,确保在任何负载条件下芯片都能稳定工作在饱和区。

难题二:输出噪声与电容选型的平衡

陶瓷电容虽然ESR低、体积小,但其电介质具有压电效应,在某些应用中可能将机械振动转换为输出端的噪声电压。本设计若应用于振动环境,噪声问题可能凸显。

解决方法: 根据ADI公司的电容选型指南,对于极低噪声要求的应用(如RF、PLL等),建议考虑使用固态钽电容替代MLCC。本项目预留了输出电容的更换空间,未来若需在噪声敏感场景中使用,可以方便地更换为0805封装的导电聚合物钽电容。

难题三:手工焊接难度

ADPL40502AUJZ-3.3-R7采用TSOT-23-5封装,引脚间距仅0.95mm,手工焊接对烙铁温度控制和操作手法要求较高。第一版焊接时曾出现相邻引脚连锡现象。

解决方法:采用刀头烙铁配合助焊剂进行拖焊操作,焊后使用吸锡带清理连锡。经过多次练习后成功完成了多块样板的焊接。建议后续设计在芯片引脚周围留出足够的操作空间,降低手工焊接难度。

难题四:PCB布局中的热管理

LDO工作时,输入输出电压差和负载电流共同决定了芯片的功耗。在5V输入、3.3V输出、200mA负载条件下,芯片功耗约为(5V-3.3V)×0.2A = 340mW。TSOT-23-5封装的热阻相对较高,340mW功耗可能导致芯片明显温升。

解决方法:在PCB布局中,芯片的GND引脚通过多个过孔连接到背面的大面积GND覆铜,利用PCB铜皮帮助散热。同时确保芯片周围通风良好,必要时可在上方增加小型散热片。

八、心得体会

通过本次LDO电源模块的设计实践,我对LDO稳压器的工作原理、外围电路选型以及PCB布局要点有了更为深入的理解。ADPL40502AUJZ-3.3-R7确实是一款优秀的低噪声LDO芯片,无需外部旁路电容即可实现出色的噪声性能,极大地简化了设计工作。这也验证了在方案选型时,充分理解芯片数据手册中的每一条参数要求,是保证设计一次成功的关键。

总之,本次基于ADPL40502AUJZ-3.3-R7的LDO降压电源模块设计项目,从原理图设计到PCB布局再到样机调试,完整走通了硬件开发的全部流程,达成了预期设计目标。项目过程中积累的经验教训将为后续更加复杂的电源系统设计奠定坚实的基础。