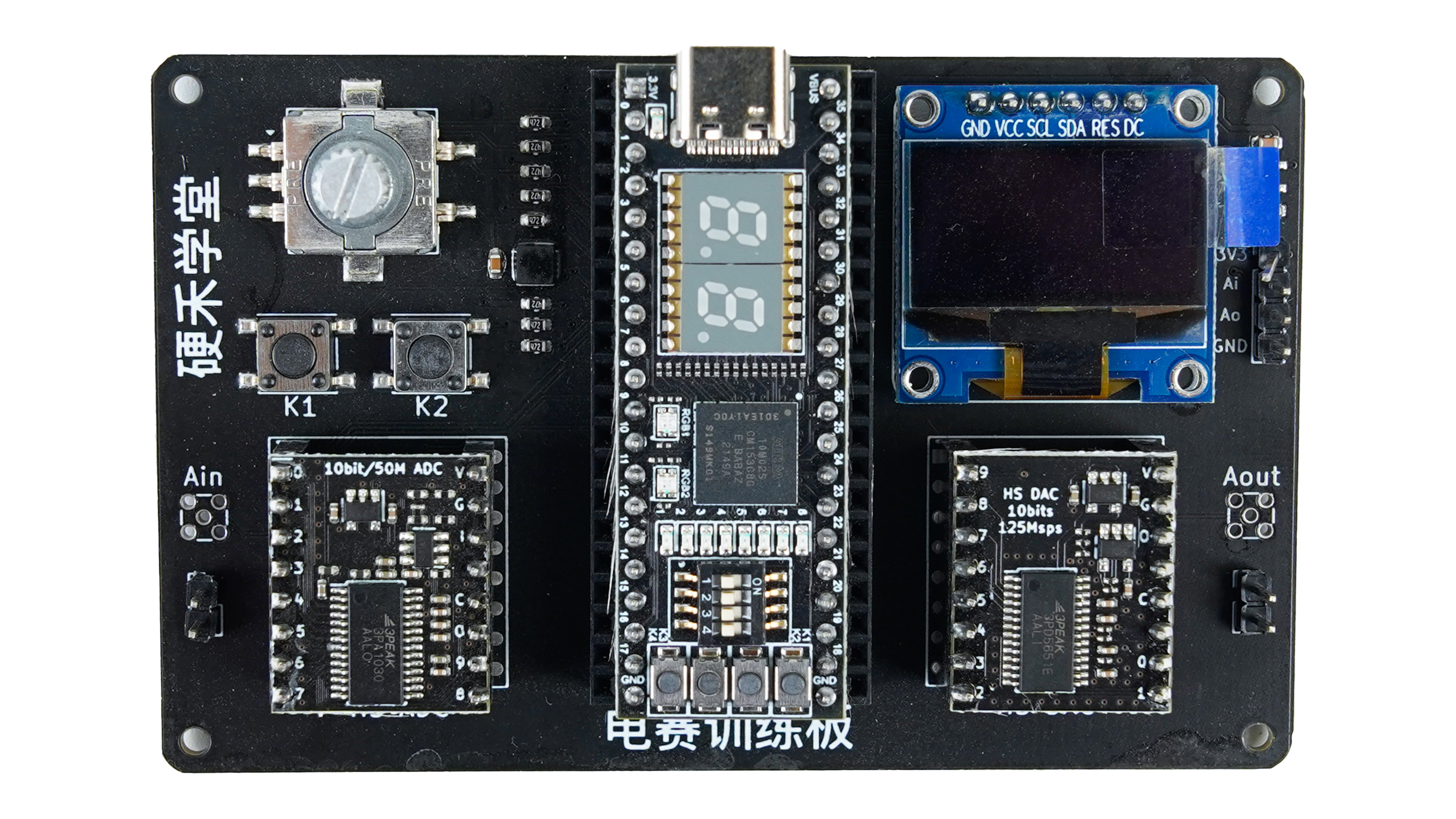

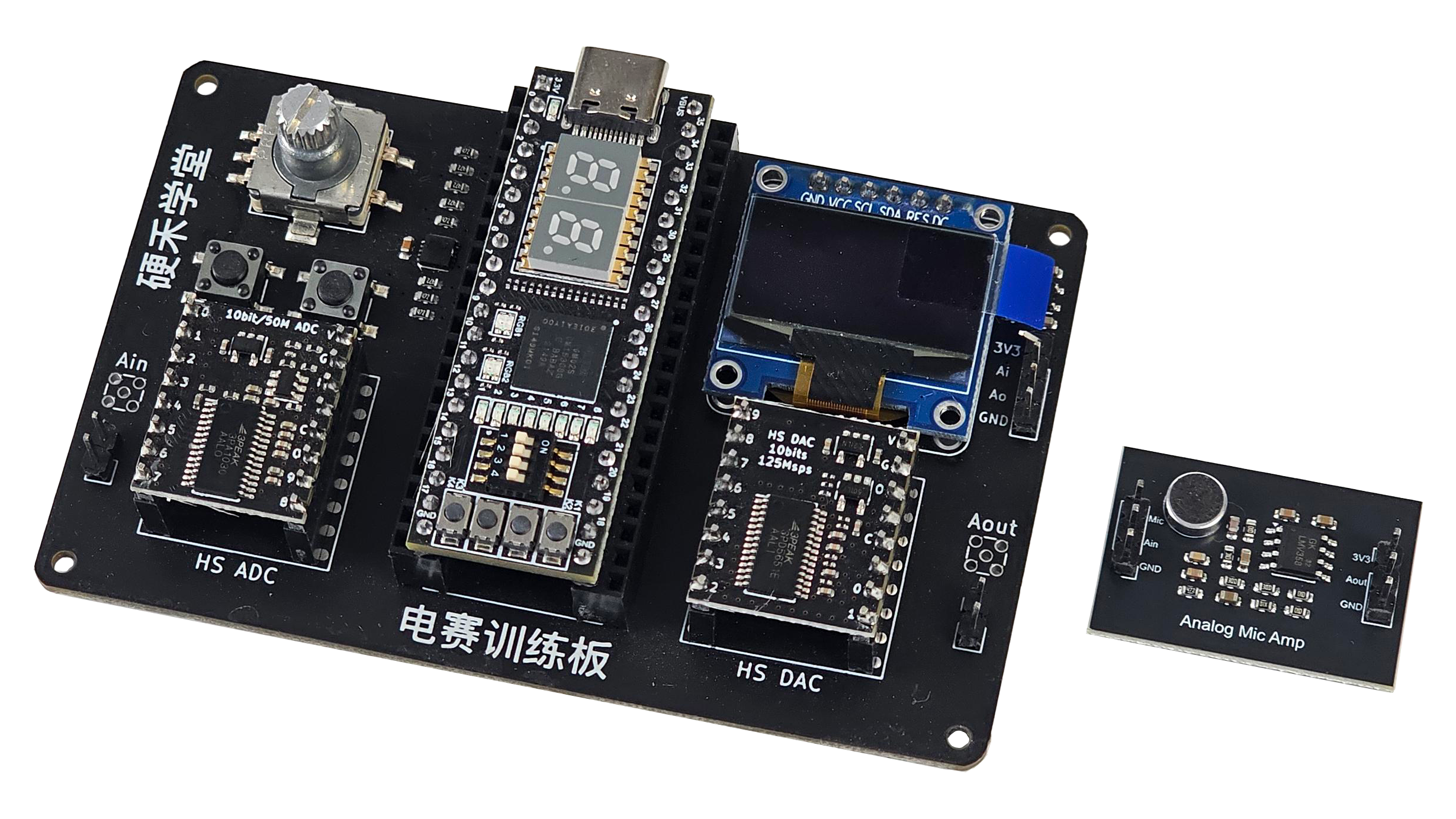

专为全国大学生电子设计竞赛技能培训设计,帮助信号源、仪器仪表、控制以及信号处理类题目的训练,核心模块可以是基于全FPGA或MCU+FPGA混合架构的核心板,板上有通过两个16Pin的插座可以安装高速ADC(16Pin可再用模块/同时支持DIP和邮票孔)、高速DAC(16Pin可再用模块/支持DIP和邮票孔)、板上安装了高速比较器、姿态传感器、旋转编码器以及按键等。

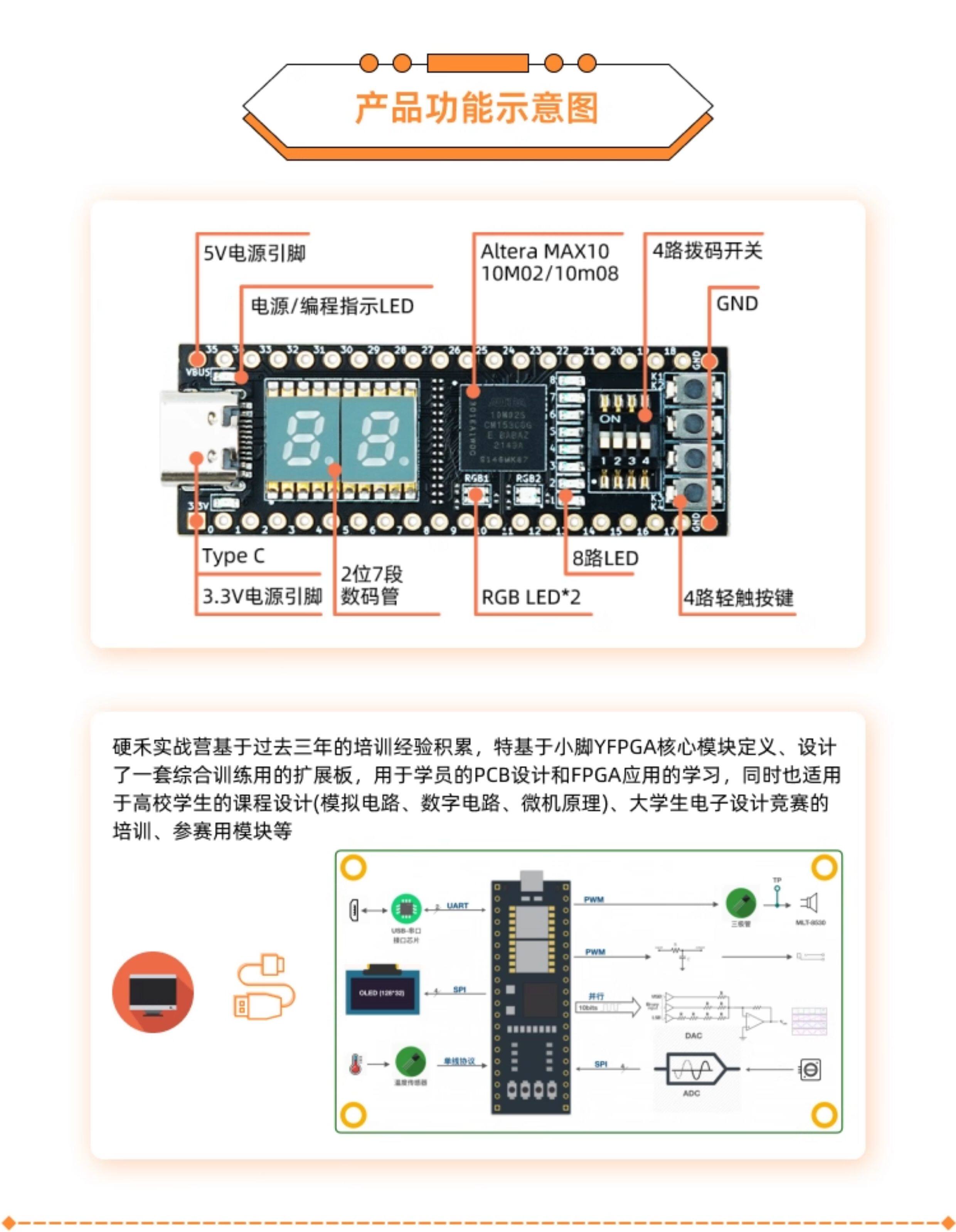

本产品支持搭任意版本小脚丫核心板,2026年寒假练活动统一使用Altera MAX10系列10M02SCM芯片的核心板。

现全系列商品均已更换成Type-C口最新款核心板

套件介绍

板卡适用范围:

- 大二学生、FPGA学习者做与FPGA相关的数字系统实验

- 备战全国大学生电子设计竞赛

- 通过完成历年电赛中的相关题目来掌握FPGA的应用

- 适用于电赛中测试测量、无线通信、控制类的题目

关键器件介绍

- 核心模块(硬禾提供两种模块):

- 全FPGA的核心模块,比如小脚丫FPGA核心板,支持Lattice版本和Intel/Altera版本的小脚丫FPGA核心板

- FPGA + MCU混合的模块 - 采用STM32G031进行控制输入响应、信息在OLED上的显示、数据的处理;采用FPGA进行高速数据采集、高速DDS信号产生、高速频率计/计数器、数字信号处理(FFT、数字滤波等)

- 信息显示:128 * 64 OLED,通过SPI总线驱动

- 控制输入: 旋转编码器/按键

- 信号采集:10bit/50Msps 高速ADC

- 信号生成:10bit/120Msps 高速DAC

- 频率测量:高速比较器

- 控制输出:PWM

- 传感器:三轴姿态感知

系统框图:

可以训练的技能:

- 用OLED显示信息,并掌握SPI总线以及显示屏的驱动原理

- 控制信息的按键输入以及按键消抖的软件/FPGA逻辑处理

- 旋转编码器的输入以及译码 - MCU软件实现/FPGA逻辑实现

- ADC高速数据采集以及缓存处理

- ADC低速数据采集以及数据处理、MCU的响应

- Sigma Delta ADC的实现(通过高速比较器)以及数字滤波器的使用

- FFT - 傅立叶变换,用于频谱分析

- 数字滤波器 - 通过FPGA内部逻辑/乘法器实现,以及通过MCU的程序实现

- 频率计/计数器设计 - FPGA逻辑实现,以及MCU的定时器/代码实现方法

- 高速DAC以及DDS信号发生器的构成及参数控制

- 通过PWM构成DAC实现DDS - 任意波形产生

- 姿态传感器的数据采集、处理以及信息显示

- UART的数据传输

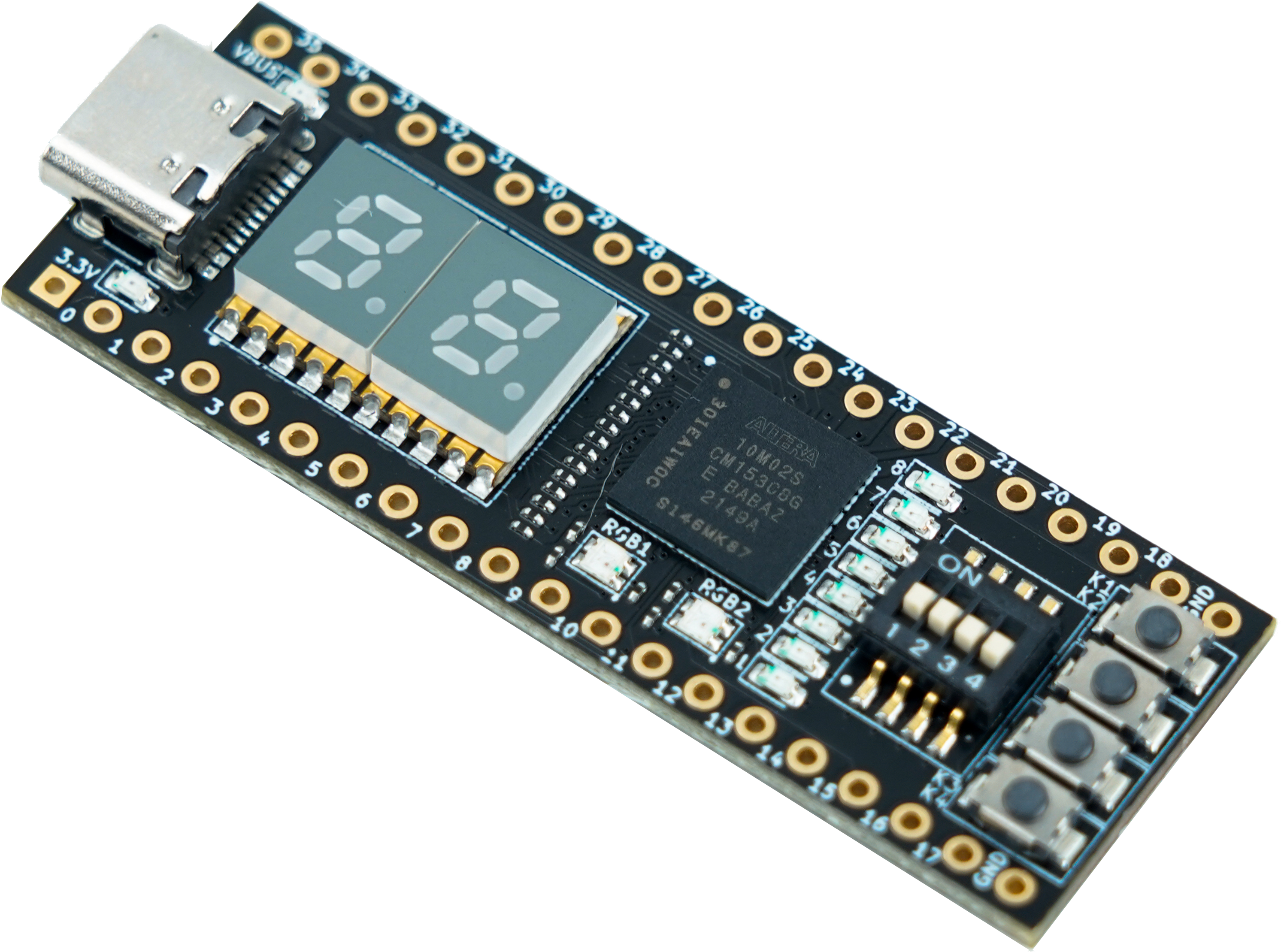

小脚丫FPGA核心板:

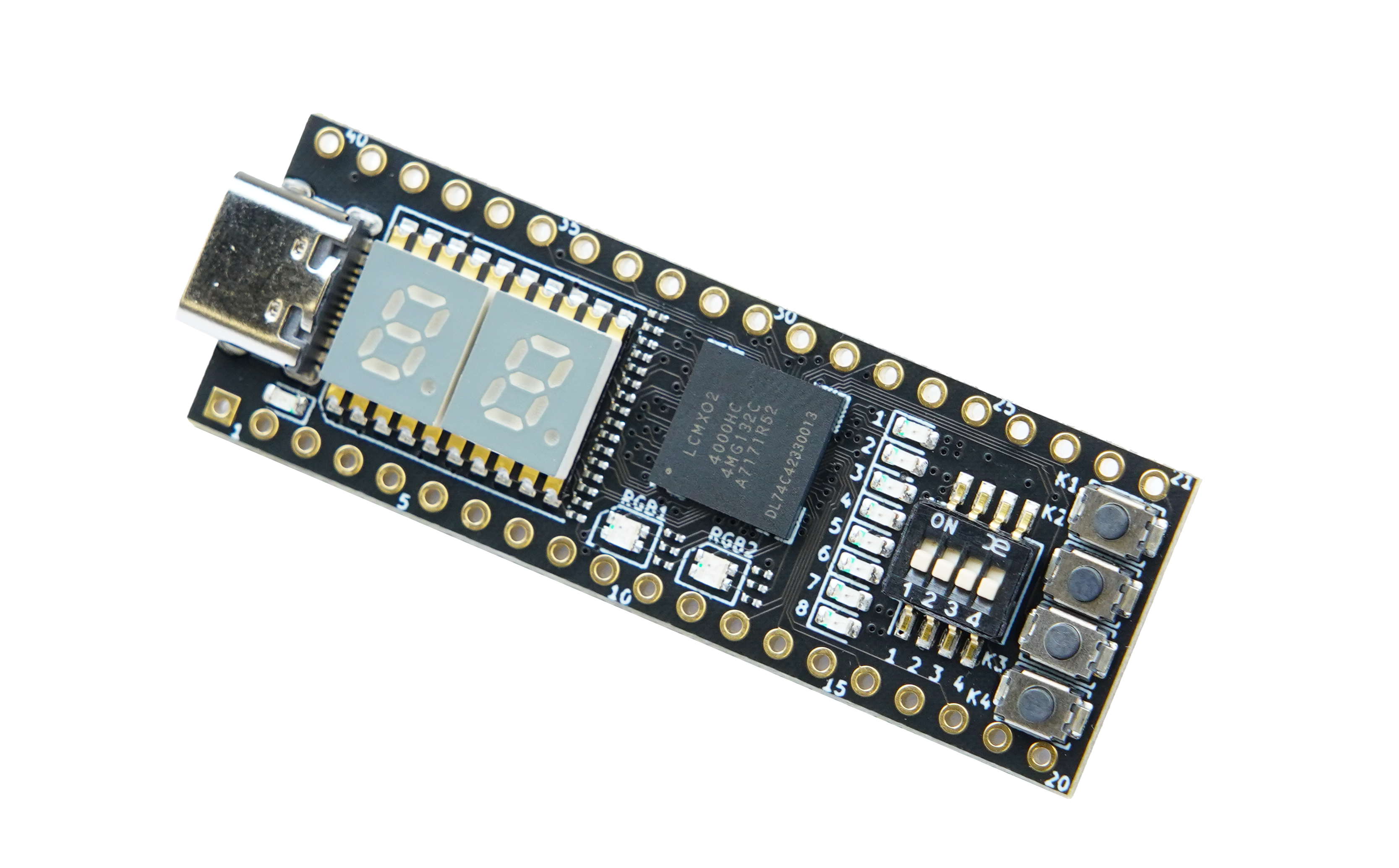

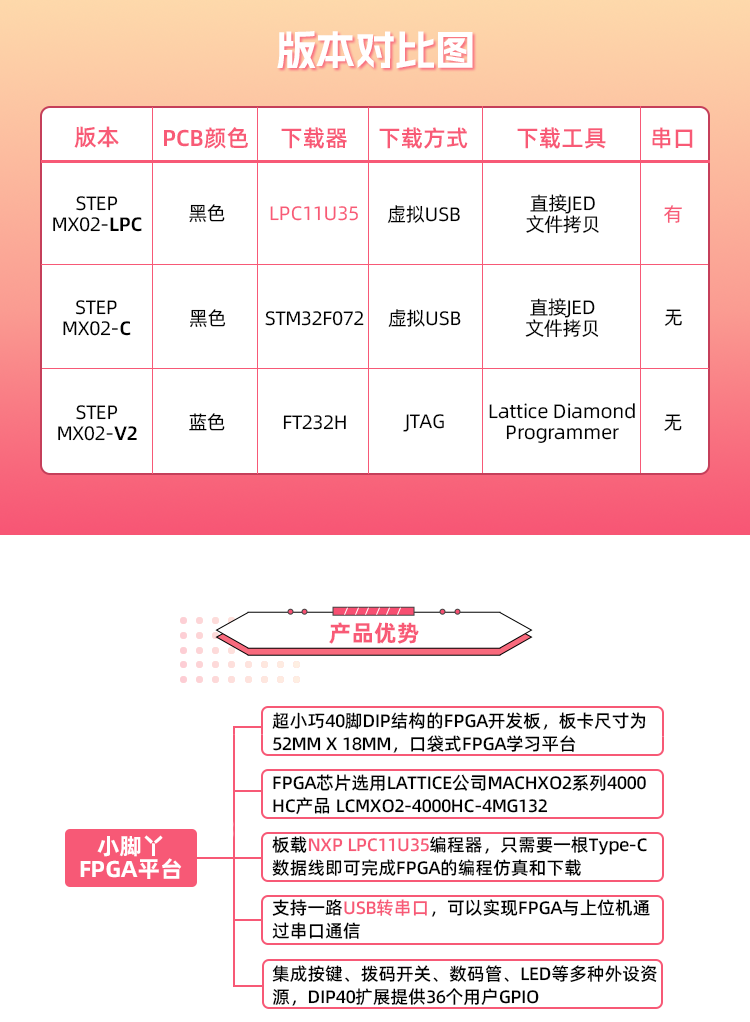

STEP小脚丫FPGA学习平台是苏州思得普信息科技公司专门针对FPGA初学者(尤其是学习数字电路的在校同学)打造的一系列性价比最高、学习门槛最低的学习模块系列。板上选用的芯片兼具了FPGA和CPLD的优点,瞬时上电启动,无需外部重新配置FPGA,是学习数字逻辑绝佳的选择。系列中所有板子的大小兼容标准的DIP40封装,尺寸只有52mm x 18mm,非常便于携带,而且能够直接插在面包板上或以模块的方式放置在其它电路板上以即插即用的方式,大大简化系统的设计。

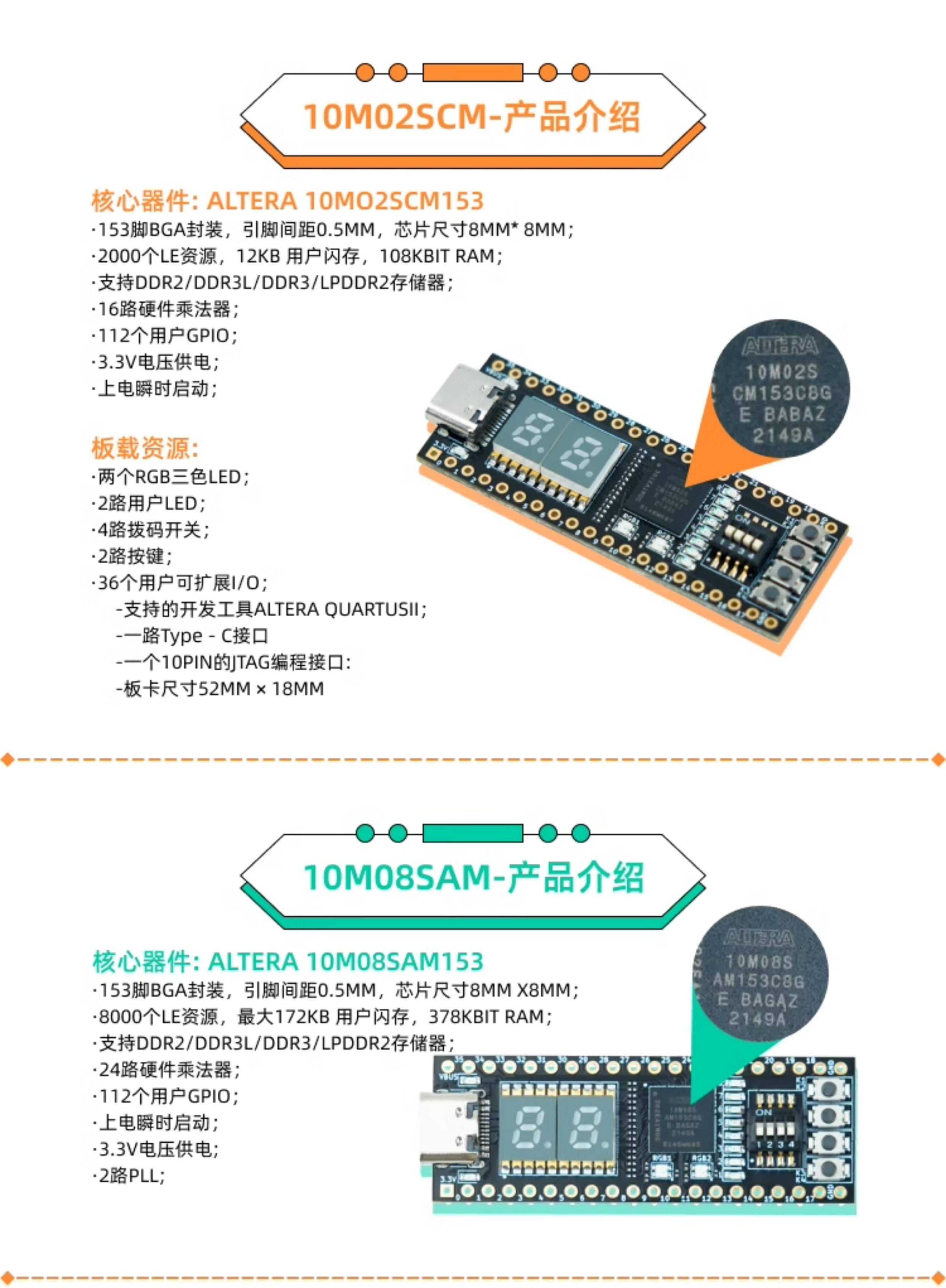

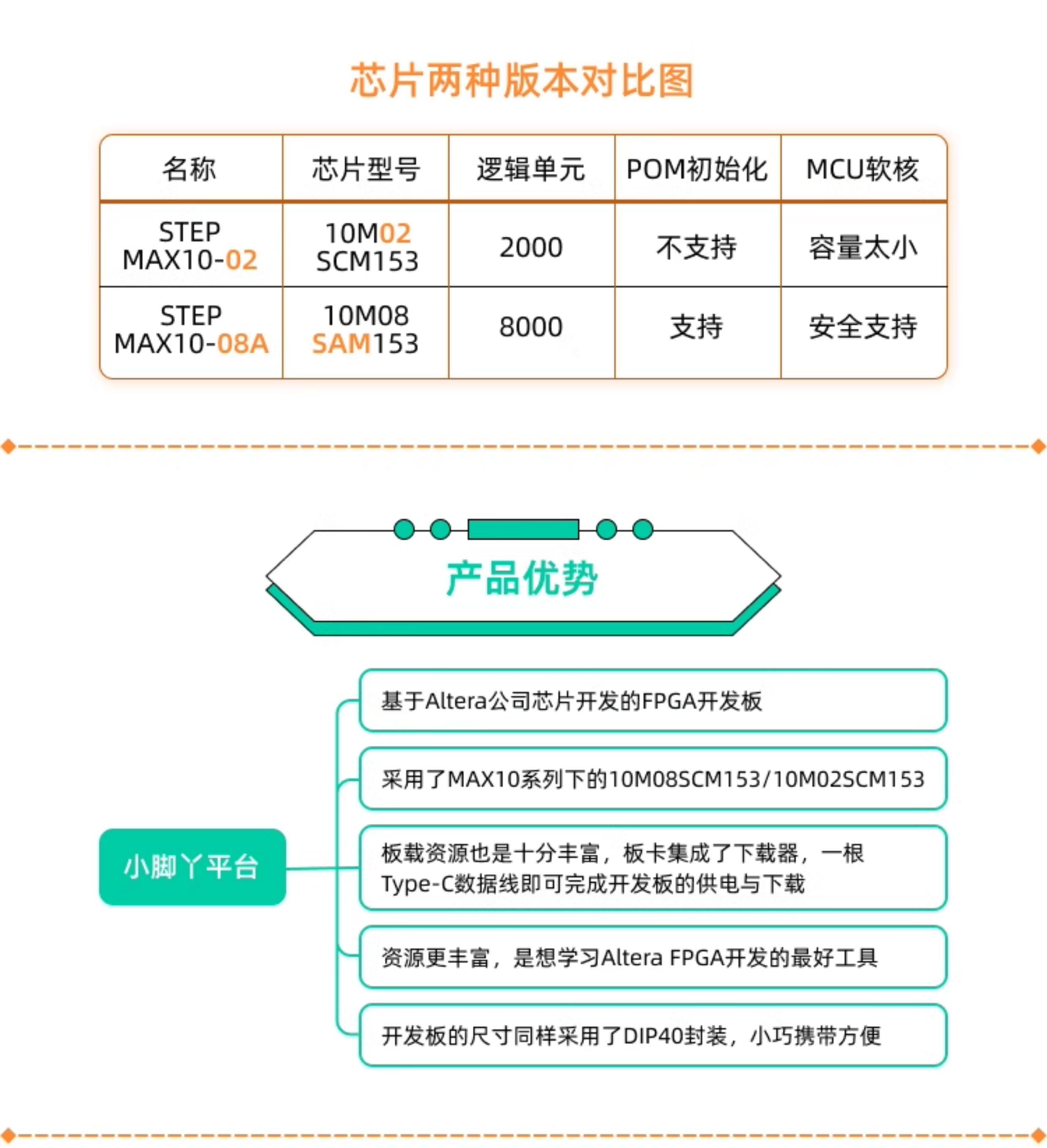

1. STEP-Altera-MAX10-02:https://www.eetree.cn/platform/4752

STEP-MAX10是小脚丫平台基于Altera公司芯片开发的FPGA开发板。核心FPGA芯片采用了Altera公司MAX10系列下的10M02SCM153/10M08SAM153,这些芯片管脚完全兼容,封装相同,区别是内部资源不同。小脚丫STEP MAX10开发板的尺寸同样也采用了DIP40封装,小巧携带方便。板载资源也是十分丰富,集成了USB-Blaster编程器和按键、拨码开关、数码管、LED等多种外设资源。板上的36个FPGA IO接口都通过2.54mm通孔焊盘引出,可以和面包板配合使用,快速搭建自己的硬件电路。板卡尺寸为52mm x 18mm,能够灵活的嵌入到插座或者其他的系统中。

STEP-MAX10 FPGA板上集成的编程器能够完美支持Intel-Altera工具Quartus系列开发软件,只需要一根Type-C USB数据线就能够完成FPGA的编程仿真和下载,使用更加方便。

Altera小脚丫网盘资料 链接:https://pan.baidu.com/s/1guMNzIYx2Q4sUGhQ1pSUvg#list/path=%2F

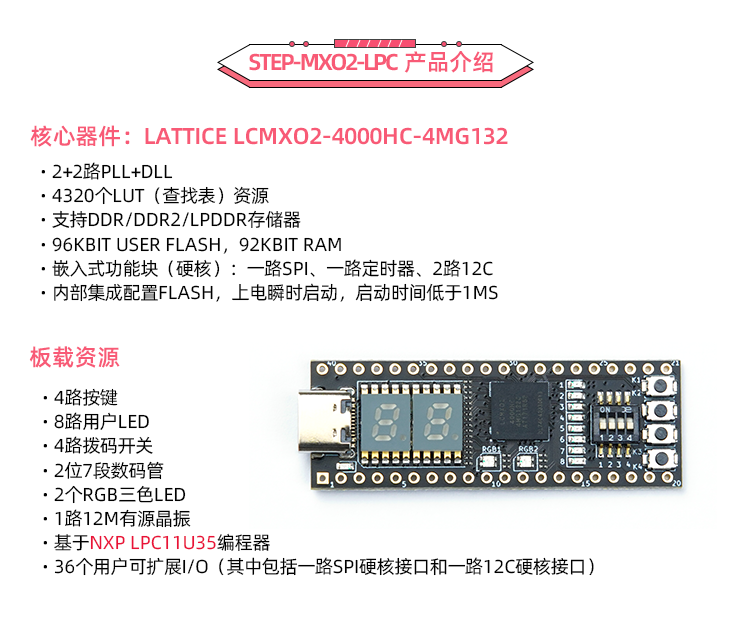

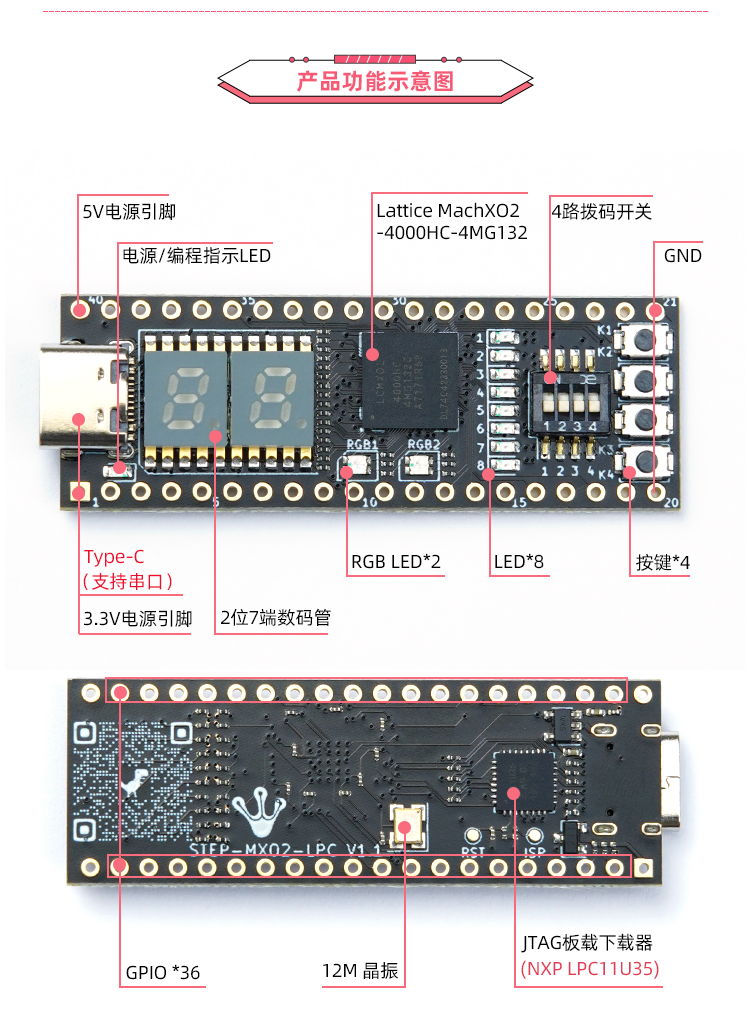

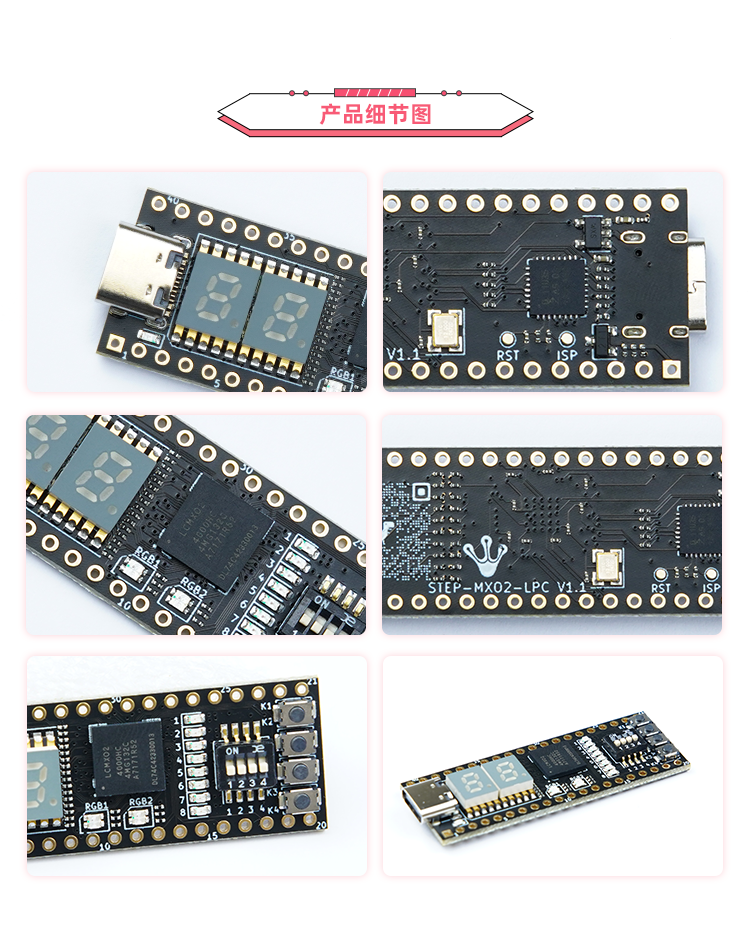

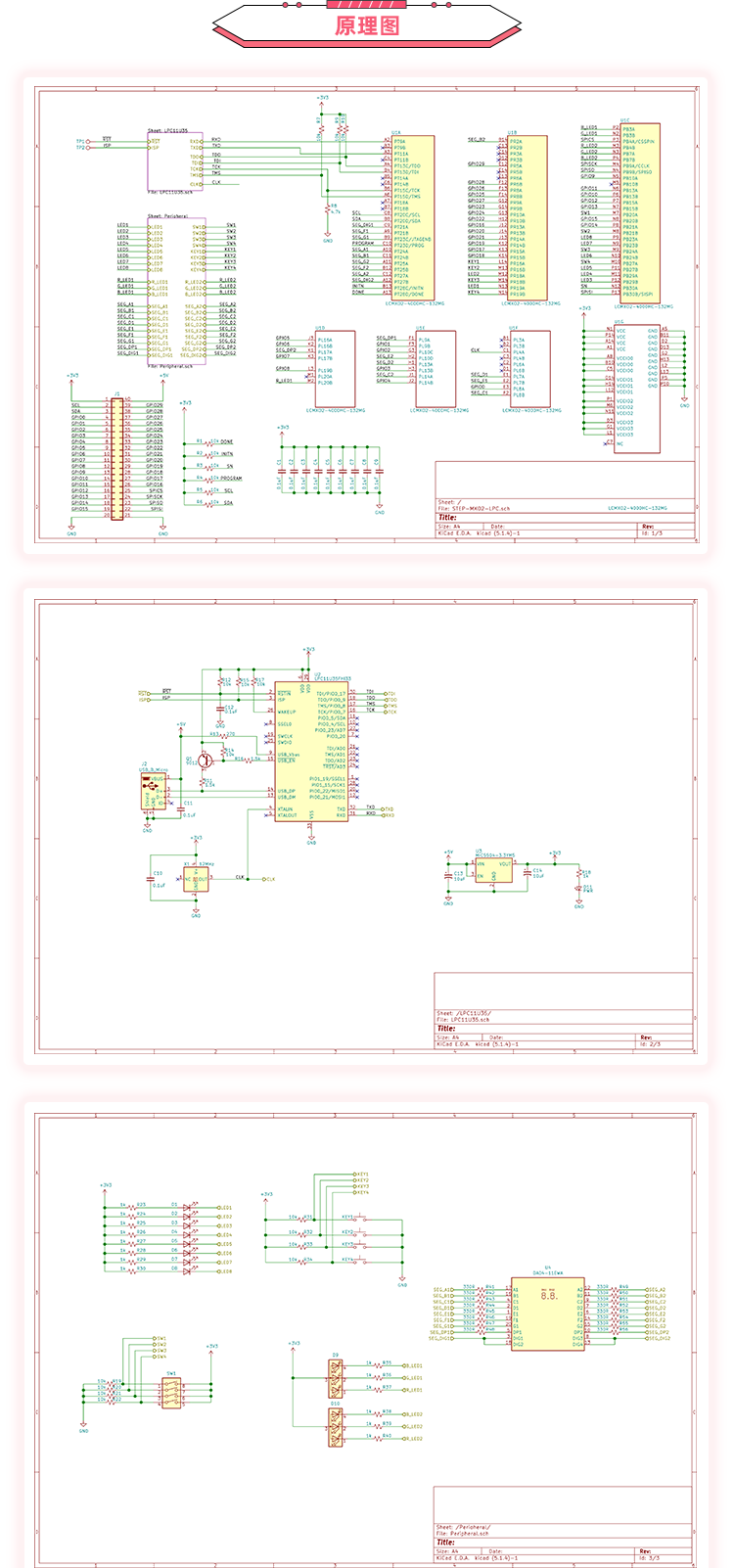

2. STEP-MXO2-LPC:https://www.eetree.cn/platform/583

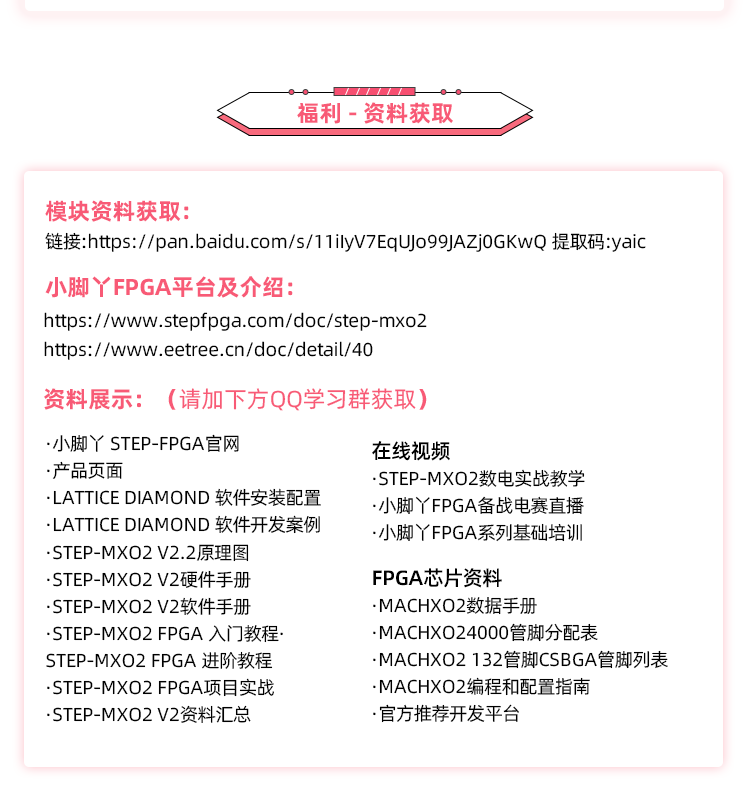

Lattice小脚丫网盘资料 链接:https://pan.baidu.com/s/11iIyV7EqUJo99JAZj0GKwQ 提取码:yaic

最新推出的STEP-MXO2-LPC在易用性方面做了大幅升级:

- 使用了USB Type C接口提供板上+5V供电、FPGA的配置,并新增了UART通信的功能,因此无需再通过其它端口与PC进行数据通信

- 支持U盘模式(连接到上位机的USB端口,上位机自动弹出StepFPGA的U盘盘符)的下载,任何操作系统的电脑 - Windows、Mac OS以及Linux(包括树莓派)都可以在不安装任何驱动程序的情况下,直接将生成的jed配置文件发送到StepFPGA盘中即可完成编程

- 为配合这款小脚丫FPGA的使用,我们特别升级了Web IDE系统,用户不必再下载安装Diamond软件,即可在任何一款电脑上通过浏览器进行FPGA的编程和编译。图形化的界面使得操作非常直观、便捷

习惯于使用Diamond编程FPGA的用户仍然可以使用Diamond软件进行编译、生成jed文件,只是最终的下载只需要将要下载的文件发送到StepFPGA盘中即可。

管脚映射关系

本平台支持多种核心模块,每一种核心模块的管脚映射关系如下表:

功能管脚 | 核心模块管脚编号 | XO2-4000HC FPGA管脚 | Intel/Altera MAX10 FPGA管脚 | STM32G031 + UP5K FPGA管脚 |

OLED_SCK | 39 | E12 | B4 | PA0/ADC0 - Pin 6 |

OLED_SDA | 37 | G12 | A7 | PA4/ADC4 - Pin 10 |

OLED_DC | 4 | E3 | M5 | PA8/MCO - Pin 16 |

OLED_RST | 36 | F13 | B6 | PA5/ADC5 - Pin 11 |

Encoder_A | 2 | C8 | M4 | PB0/ADC8 - Pin 14 |

Encoder_B | 3 | B8 | P3 | PB1/ADC9 - Pin 15 |

Encoder_S | 5 | F3 | R3 | PC6 - Pin 17 |

SW_S1 | 6 | G3 | L6 | PA11 - Pin 18 |

SW_S2 | 7 | H3 | P4 | PA12 - Pin 19 |

Sensor_SCL | 8 | J2 | L7 | I2C_SCL - Pin 26 |

Sensor_SDA | 33 | G14 | B7 | I2C_SDA - Pin 27 |

Sensor_INT | 34 | G13 | D7 | PA7/ADC7 - Pin 13 |

PWM_OUT | 35 | F14 | E7 | PA6/ADC6 - Pin 12 |

Ain | 38 | F12 | A5 | PA1/ADC1 - Pin 7 |

ADC_D0 | 9 | J3 | R5 | 26 |

ADC_D1 | 10 | K2 | P6 | 27 |

ADC_D2 | 11 | K3 | R7 | 28 |

ADC_D3 | 12 | L3 | P7 | 31 |

ADC_D4 | 13 | N5 | P8 | 32 |

ADC_D5 | 14 | P6 | P9 | 34 |

ADC_D6 | 15 | N6 | R9 | 2 |

ADC_D7 | 16 | P7 | R11 | 36 |

ADC_D8 | 17 | N7 | P12 | 25 |

ADC_D9 | 18 | P8 | R14 | 48 |

ADC_CLK | 19 | N8 | P15 | 47 |

DAC_D9 | 32 | H12 | C8 | 18 |

DAC_D8 | 31 | J13 | B8 | 13 |

DAC_D7 | 30 | J14 | D10 | 12 |

DAC_D6 | 29 | K12 | A9 | 11 |

DAC_D5 | 28 | K14 | A11 | 10 |

DAC_D4 | 27 | K13 | A13 | 9 |

DAC_D3 | 26 | J12 | B11 | 6 |

DAC_D2 | 25 | P3 | A14 | 4 |

DAC_D1 | 24 | M4 | B13 | 3 |

DAC_D0 | 23 | N4 | B14 | 46 |

DAC_CLK | 22 | P13 | B15 | 45 |

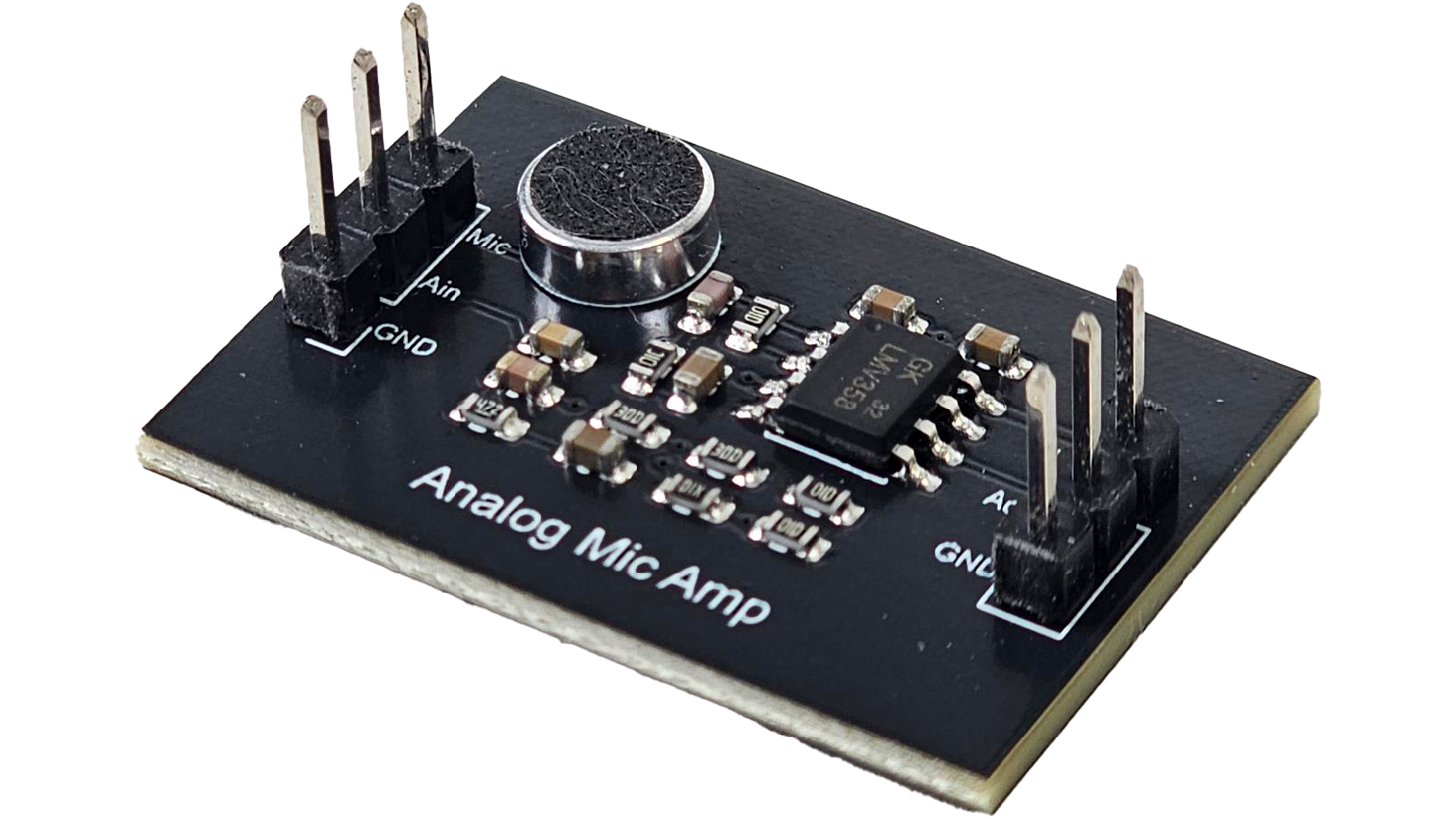

麦克风放大模块

麦克风放大模块原理图请于附件下载

文档资料

- 小脚丫FPGA编程Web IDE

- Quartus Prime下载安装

- Lattice Diamond安装配置

- Lattice Diamond使用案例

- STEP-MXO2-C快速上手指南

- STEP-MXO2 FPGA 入门教程

- STEP-MXO2 FPGA 进阶教程

- STEP-MXO2 FPGA 项目实战

- FPGA入门基础项目案例

- FPGA相关的中级综合性项目案例

- 在FPGA上实现软核处理器

- 小脚丫在数字电路课程学习中的应用教程

- DDS生成任意波形的方法及Verilog代码实例

- PWM的应用及相应的Verilog代码