简介:

这是一款采用思瑞浦3Peaks公司的高速ADC芯片3PA1030设计制作的DIP16封装的高速ADC模块,能够搭配FPGA实现对模拟信号的采集,它能够支持对1Vpp/10MHz模拟信号的采集,采样率达到50Msps,提供10位的采样精度。

这个模块专为全国大学生电子设计竞赛的测试测量仪器题目而设计,也可以用在需要高速数据采集的其它应用中,比如简易示波器的制作、低于10MHz的模拟信号的数据采集、数字通信等。

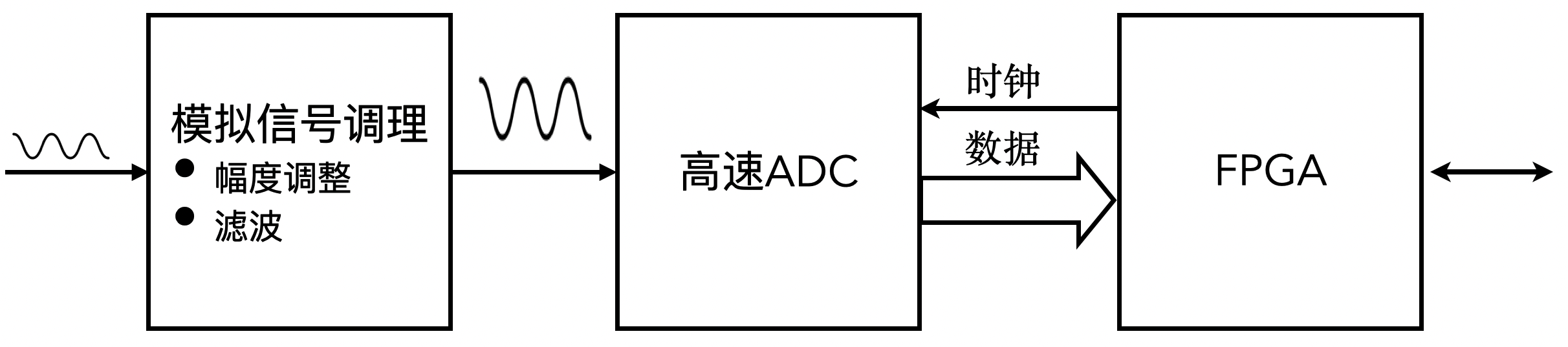

工作原理:

在很多电子系统中需要对通过模拟的电信号进行量化,变成数字量传输到数字信号处理器、MCU等在数字域进行数字信号的处理。ADC在将模拟信号转换为数字量的过程中是最关键的器件。根据被采集的模拟信号的带宽以及对幅度范围来选择适当精度、适当采样率的ADC对模拟信号进行量化,以保证对原始模拟信号的尽可能真实的表征。

针对模拟带宽在DC-1MHz范围内的模拟信号基本上都采用高精度的串行ADC进行量化,尤其是当今的多数MCU内部都集成了采样率达到5Msps、精度到12位的ADC,但对于频率高于1MHz的模拟信号的量化就需要采用并行接口的ADC,且采样率要更高,我们可以看到20Msps、50Msps、80Msps、100Msps的ADC非常普遍,在设计中可以综合各方面的因素来选择性价比最佳的器件用在自己的设计中。

国产半导体厂商中做并行高速ADC得不多,3Peaks公司的3PA1030是颗不错的选择,尤其是用在电赛中,它能够提供高达50Msps的采样率,10位的精度也比较适中,因此非常适合用在数据采集技能的训练,以及解决电赛的测试测量的题目中。

由于高速ADC属于模拟/混合的高速器件,其对输入模拟电压以及带宽的要求都需要搭配适当的外围电路来达到起应用的性能,再考虑到模块的灵活性,我们特意设计了一个“最小系统”的高速ADC模块,将必要的外围器件,比如输入端的缓冲、电源电压的生成及电源的去耦,并采用了标准的宽体DIP16封装,方便用户将其作为一个即插即用的“部件”适配到各种系统中。

主要性能指标:

类型 | 高速DAC |

核心芯片 | 3PA1030 |

输入信号电压[最大] | 10Vpp |

输入信号频率范围 | DC-10MHz |

采样率[最大] | 50Msps |

分辨率 | 10位 |

接口方式 | 并行 |

板卡尺寸 | 17.2mm x 20.8mm |

输入电压 | 3.3V - 5V |

输出信号电平 | 3.0V |

管脚定义:

管脚属性 | 管脚名 | 管脚编号 | 管脚名 | 管脚属性 | |

O | D0 | 1 | 16 | Vdd | P |

O | D1 | 2 | 15 | GND | P |

O | D2 | 3 | 14 | Ain | I |

O | D3 | 4 | 13 | x | NC |

O | D4 | 5 | 12 | CLK | I |

O | D5 | 6 | 11 | D10 | O |

O | D6 | 7 | 10 | D9 | O |

O | D7 | 8 | 9 | D8 | O |

电气特性:

描述 | 最小值 | 典型值 | 最大值 | 单位 |

供电电压 | 3.3 | - | 5 | V |

输入模拟信号电压 | 0.05 | - | 10 | Vpp |

输入模拟信号带宽 | DC | 10,000,000 | Hz | |

分辨率 | - | - | 10 | bit |

转换率 | - | - | 50M | SPS |

应用示例:

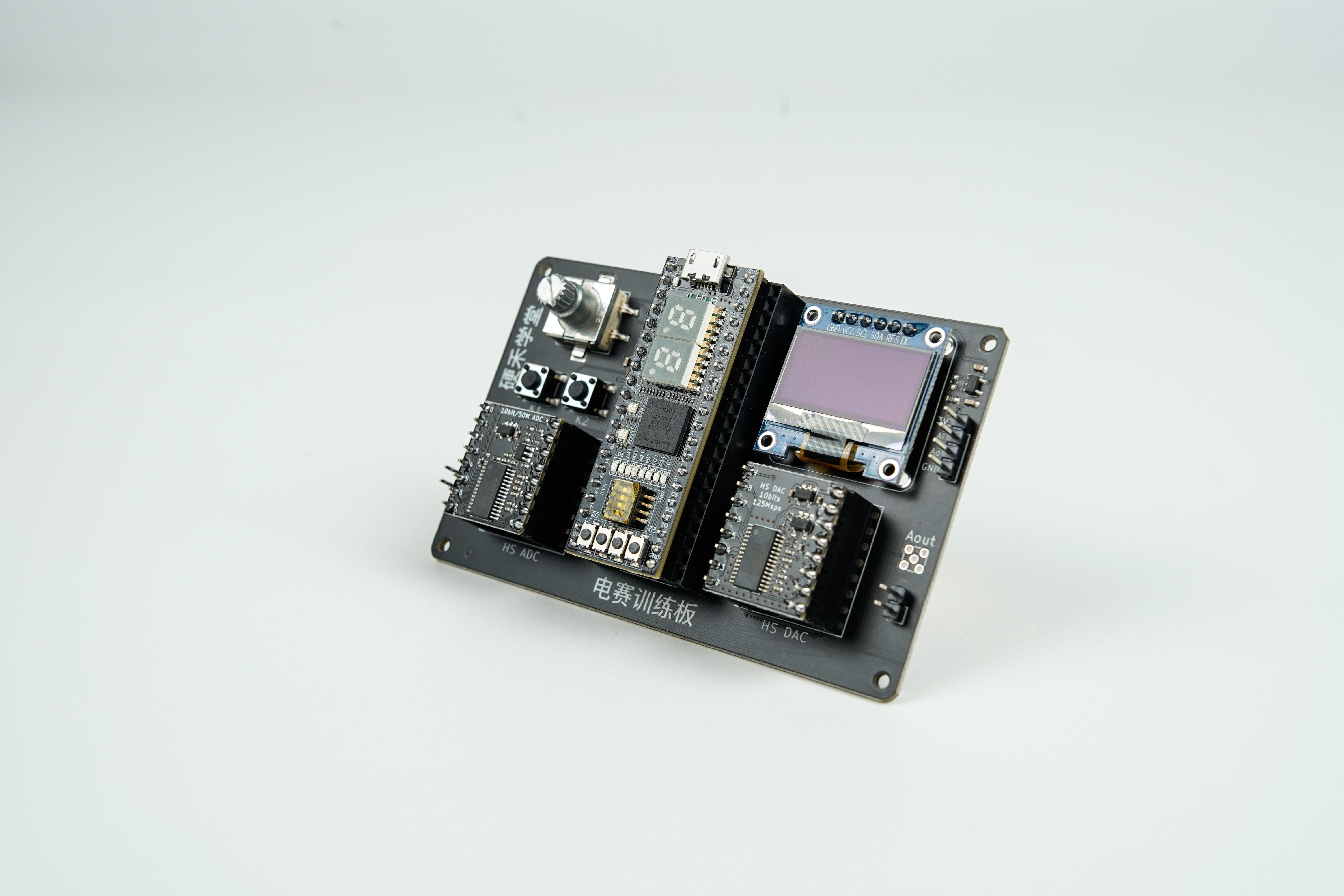

全国大学生电子设计竞赛综合训练板,可以搭配任意一款小脚丫FPGA核心模块