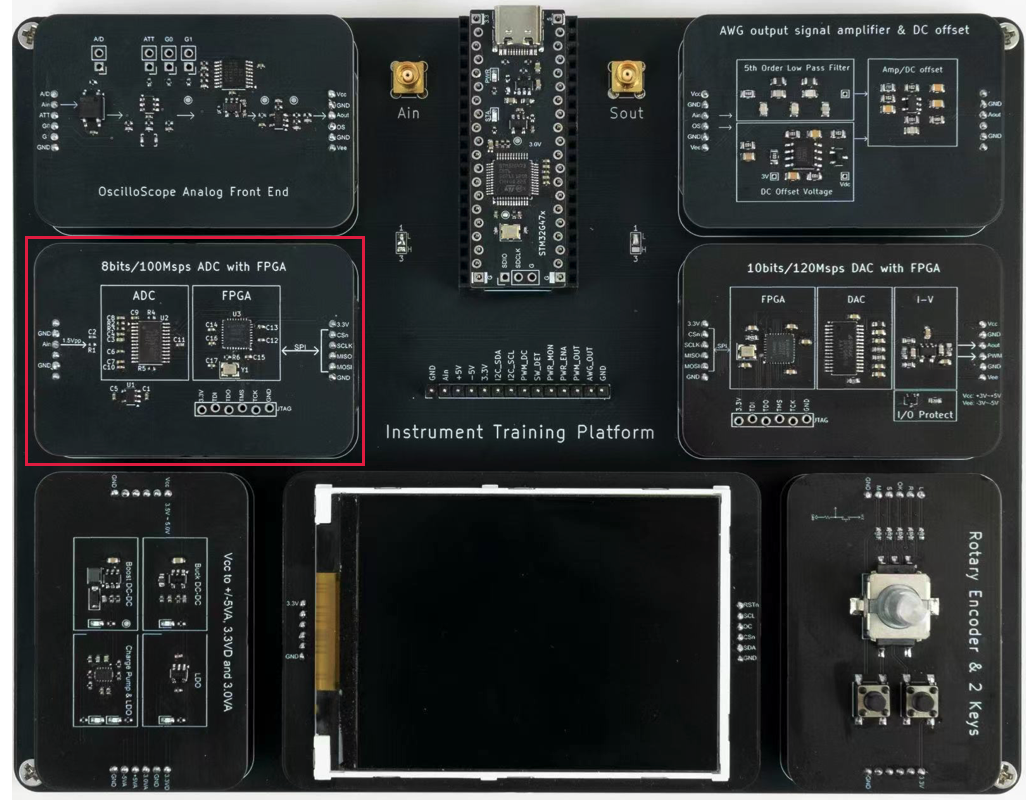

该模块为我们的模块化仪器系统的高速ADC部分,见下图左侧中间部分的一个模块。

模块化仪器的构成

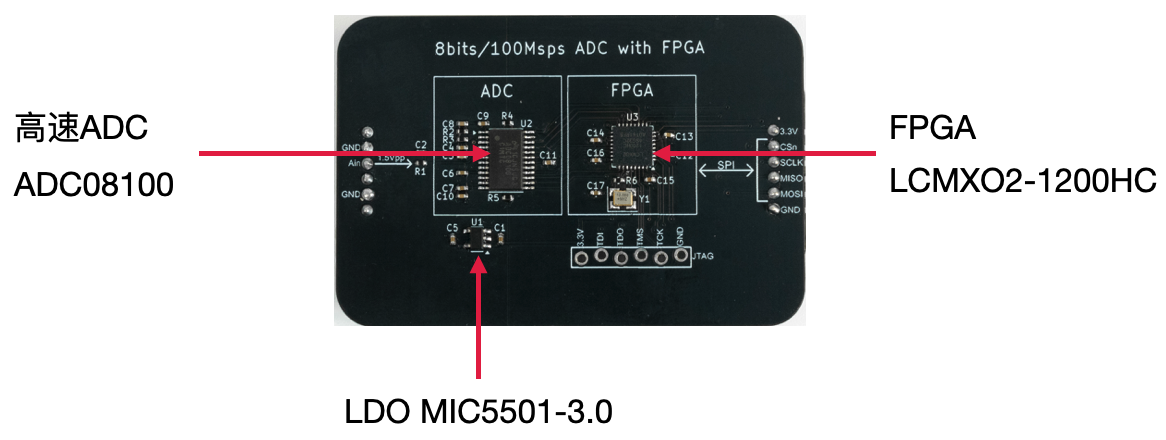

这是一款可用于电赛或简易示波器/便携仪器设计的ADC模块,使用TI的8位/100Msps ADC芯片ADC08100,搭配Lattice Semi公司的XO2-1200HC FPGA,以SPI的方式输出采集到的数据。ADC接收的信号幅度为0-1.5V,单端输入。

工作原理:

在测试测量以及通信领域,高速ADC被用来将模拟信号转换为数字信号,在这种数据转换的系统中,一般都会通过FPGA将ADC变换好的数据进行缓存,以便后续不同时钟域的处理器对这些数据进行处理。在设计中会根据对数据存储深度的需求以及采集后数据的处理功能的需求来选择合适的FPGA器件,FPGA的时钟速率、逻辑单元数以及内部存储的容量都是一些关键的因素,如果需要更大的存储,可以外挂SRAM或DRAM,当然这些外挂的存储器需要更多的管脚。

高速ADC数据转换及存储模块构成

我们的这个模块主要用于教学以及电赛使用,对ADC转换后的数据的存储深度要求不高,也不会对采集后的数据做太多的数字信号处理的工作,因此选择了一颗有1200个查找表、内部块RAM为96Kbits的FPGA芯片 - 来自Lattice Semi公司的LCMXO2-1200HC,支持3.3V的单一电压供电。这颗FPGA虽然管脚比较少,32Pin的QFN封装的器件,但它内部有Flash,无需外挂任何器件,单一3.3V电压供电,外接低频率的时钟(比如12MHz),可以通过内部的PLL得到较高的时钟频率,比如可以工作在96Msps、120Msps、192Msps等12MHz的整数倍的频率点上。在我们的这个模块上ADC的转换率最高100Msps,我们可以选择96Msps,或更换外接的晶体振荡器为10MHz,就可以让ADC和FPGA的内部时钟工作在100Msps了。

模块上的主要器件

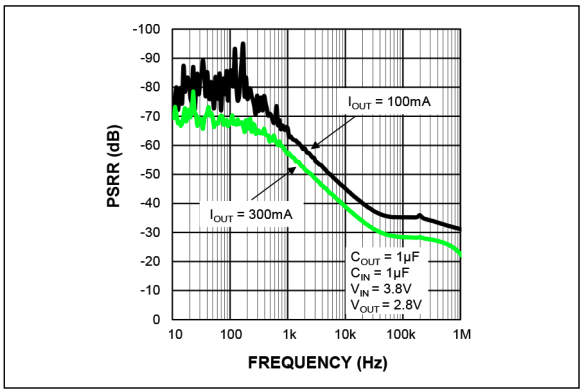

由于ADC芯片可以支持3.0V的模拟供电,可以从3.3V的数字供电电压上通过LDO来获取,LDO一般都有40dB以上的电源噪声抑制比,通过LDO转换得到的3.0V噪声会大大降低。

MIC5501-3.0的PSRR指标,对于1KHz以内的低频噪声有超过60dB(1000倍)的抑制作用

关键特性:

类型 | 高速ADC数据采集 |

应用 | 测量仪器中的模数变换、通信系统中的中频解调 |

关键性能 | 8位精度/100Msps、12KB存储深度、SPI数据通信 |

接口方式 | 6pin 2.00mm 磁吸连接器 |

板卡尺寸 | 60mm x 40mm |

输入电压 | 0-1.5Vpp |

管脚命名:

说明 | 管脚名 | 管脚编号(左) | 管脚编号(右) | 管脚名 | 说明 |

- | - | 1 | 1 | 3.3V | 调理信号输出 |

接地 | GND | 2 | 2 | CSn | SPI总线片选 |

模拟输入电压 | Ain | 3 | 3 | SCLK | SPI总线时钟 |

- | - | 4 | 4 | MISO | SPI总线数据输出 |

接地 | GND | 5 | 5 | MOSI | SPI总线数据输入 |

- | - | 6 | 6 | GND | 接地 |

电气指标:

描述 | 最小值 | 典型值 | 最大值 | 单位 |

输入电压幅度 | 0 | - | 1.5 | Vpp |

供电电压 | - | 3.3 | - | V |

供电电流 | - | 50 | - | mA |