任务介绍

本项目旨在设计并实现一款紧凑、高可靠性的12V四路电源分配器模块,能够为后端负载提供四路独立开关控制的500mA电源输出。该模块集成了过流与短路保护功能,拥有稳定可靠的数字控制接口与主控MCU连接,并提供清晰的电源输入/输出端子,便于在各种嵌入式系统或自动化设备中进行快速集成与应用。

模块介绍

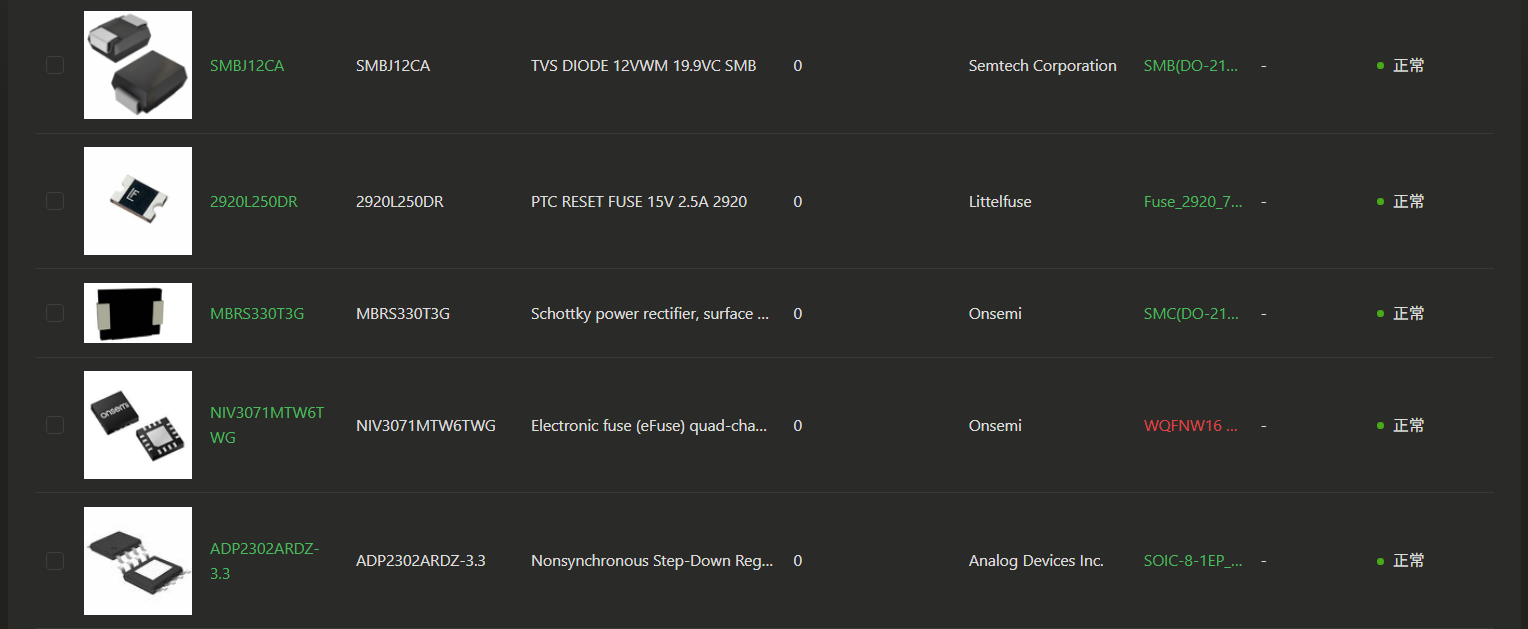

本模块的核心器件为NIV3071MTW6TWG(DigiKey网址:NIV3071MTW6TWG onsemi | 集成电路(IC) | DigiKey)电子保险丝eFuse。该芯片内部集成了四个独立的高边电源开关通道,每个通道均能提供高达2.5A的电流能力,并具备可编程的过流保护、短路保护及热关断保护功能。通过其独立的ENx使能引脚,可以实现对四路输出的独立软件开关控制,并通过一个通用的FAULT引脚向主控MCU报告故障状态,极大地简化了保护电路的设计并提升了系统的智能化水平与可靠性。

为了满足控制逻辑对供电及信号电平的要求,模块在硬件设计上引入了功能电路:首先,采用ADP2302ARDZ-3.3(DigiKey网址:ADP2302ARDZ-3.3 Analog Devices Inc. | 集成电路(IC) | DigiKey)作为BUCK降压稳压器,将外部输入的12V电源高效地转换为稳定的3.3V,为外部MCU接口的逻辑电平提供参考电源。另外在12V电源输入端加入PTC可复位保险丝2920L250DR(DigiKey网址:2920L250DR Littelfuse Inc. | 电路保护 | DigiKey)作为一级保护,并在电源端口配置了TVS二极管进行ESD防护,有效提升了模块的抗静电能力与环境适应性。

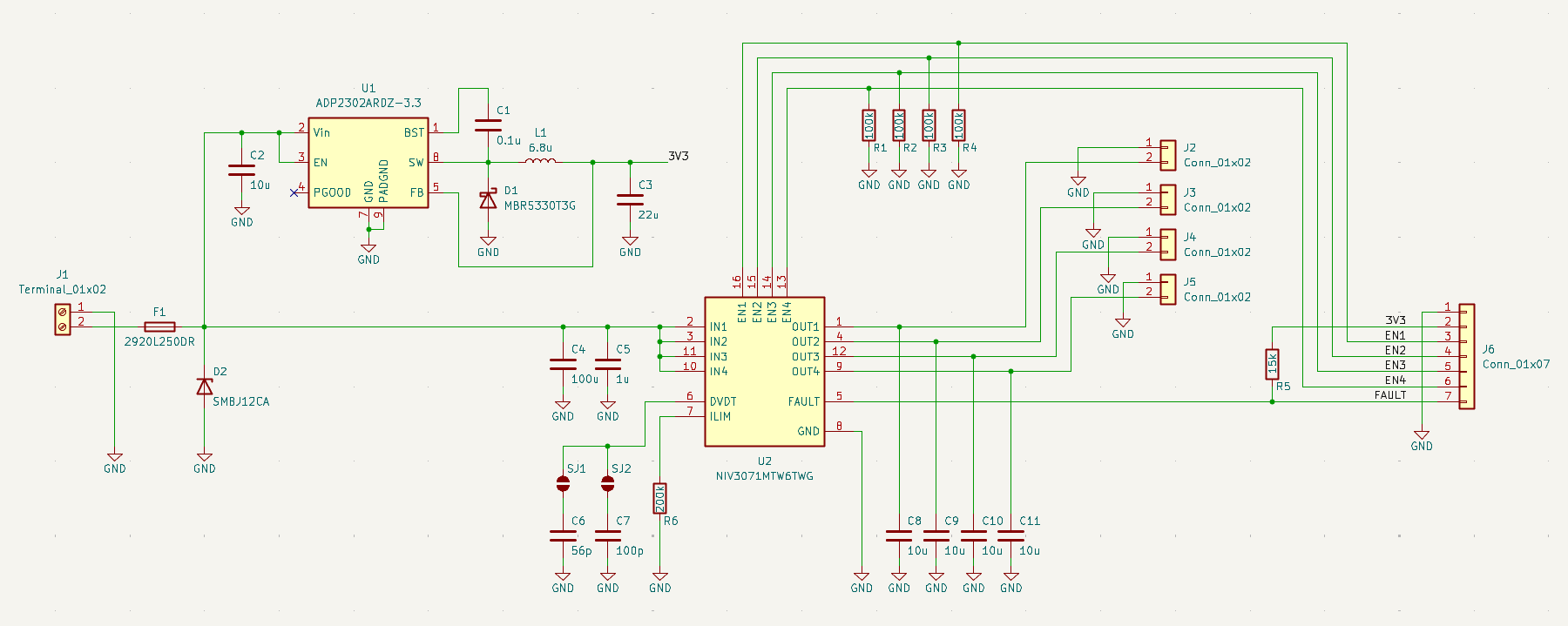

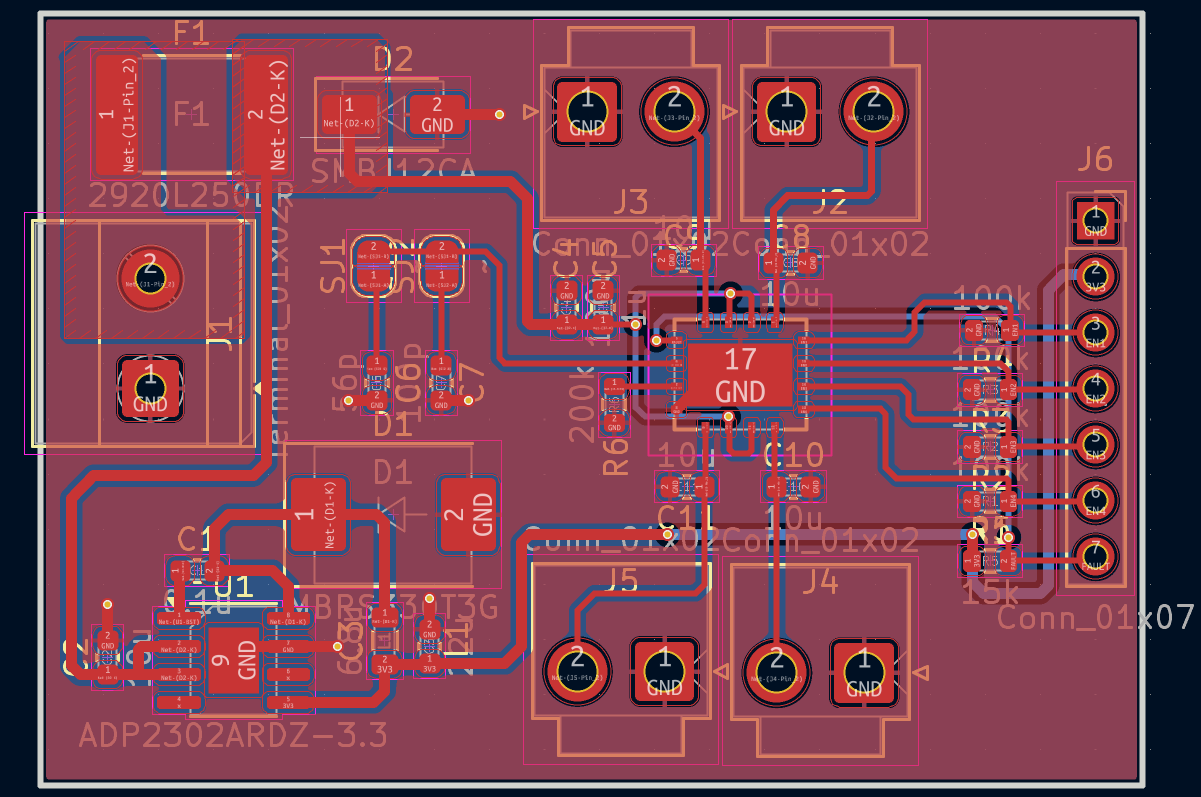

原理图与PCB设计

电源部分为了确保其在稳定可靠的环境下工作,主12V输入端和3.3V逻辑电源输出端均布置了去耦电容,以减小电源纹波与瞬态干扰。PTC保险丝串联在12V输入的最前端,为整个模块提供基础保护。

信号接口方面,四路使能信号 (EN1-EN4) 直接从接口引出至NIV3071,允许MCU直接控制。FAULT故障信号引脚为开漏输出,因此在3.3V侧配置了上拉电阻,确保在无故障时输出稳定高电平。NIV3071的电流限值通过ILIM引脚外接的单个电阻统一设定为500mA,简化了多通道的参数配置。

性能指标

项目类别 | 指标参数 | 说明 |

供电 | 主供电:+12V (DC) | 3.3V由板载ADP2302稳压器生成 |

输出通道 | 数量:4路 | 通过EN1-EN4引脚控制 |

输出电流 | 额定电流:500mA/路 | 所有通道共用一个电流限值设定 |

保护功能 | 过流保护:ITH=500mA, ICB≈1A | 集成保护功能 |

控制接口 | 4使能输入(ENx) | 兼容3.3V TTL/CMOS电平 |

ESD防护 | 接触放电:±8kV | - |

管脚定义

接线端子定义

管脚编号 | 名称 | 属性 | 说明 |

1 | GND | P | 模块地 |

2 | VIN_12V | P | 12V输入 |

JST接口定义

管脚编号 | 名称 | 属性 | 说明 |

1 | GND | P | 模块地 |

2 | OUTx | P | 独立通道电源输出 |

通孔焊盘定义

管脚编号 | 名称 | 属性 | 说明 |

1 | GND | P | 模块地 |

2 | 3V3 | P | BUCK提供3V3逻辑电源,为MCU供电 |

3 | EN1 | I/O | 使能端口1(高有效) |

4 | EN2 | I/O | 使能端口2(高有效) |

5 | EN3 | I/O | 使能端口3(高有效) |

6 | EN4 | I/O | 使能端口4(高有效) |

7 | FAULT | I/O | 输入通用故障输出(开漏,低有效) |

板上设置与使用方法

上电后,模块内部的ADP2302将首先工作,为控制逻辑提供稳定的3.3V电源。模块的四路输出默认状态由EN1-EN4的电平决定。NIV3071的ENx引脚高电平有效,为确保上电时所有输出保持关闭,模块内预设了100k弱下拉,MCU也应在初始化时将控制ENx的GPIO引脚配置为推挽输出并拉低。向ENx引脚输入高电平(大于1.2V)即可开启对应通道,输入低电平(小于0.4V)则关闭通道。MCU可通过GPIO直接驱动。

FAULT引脚为开漏、低电平有效。正常工作时,因外部上拉到3V3网络的存在,此引脚为高电平。当任意一个通道发生过流或过热故障时,此引脚会被NIV3071内部电路拉至低电平。MCU可将连接此引脚的GPIO配置为下降沿触发的外部中断,以实现实时的故障响应。

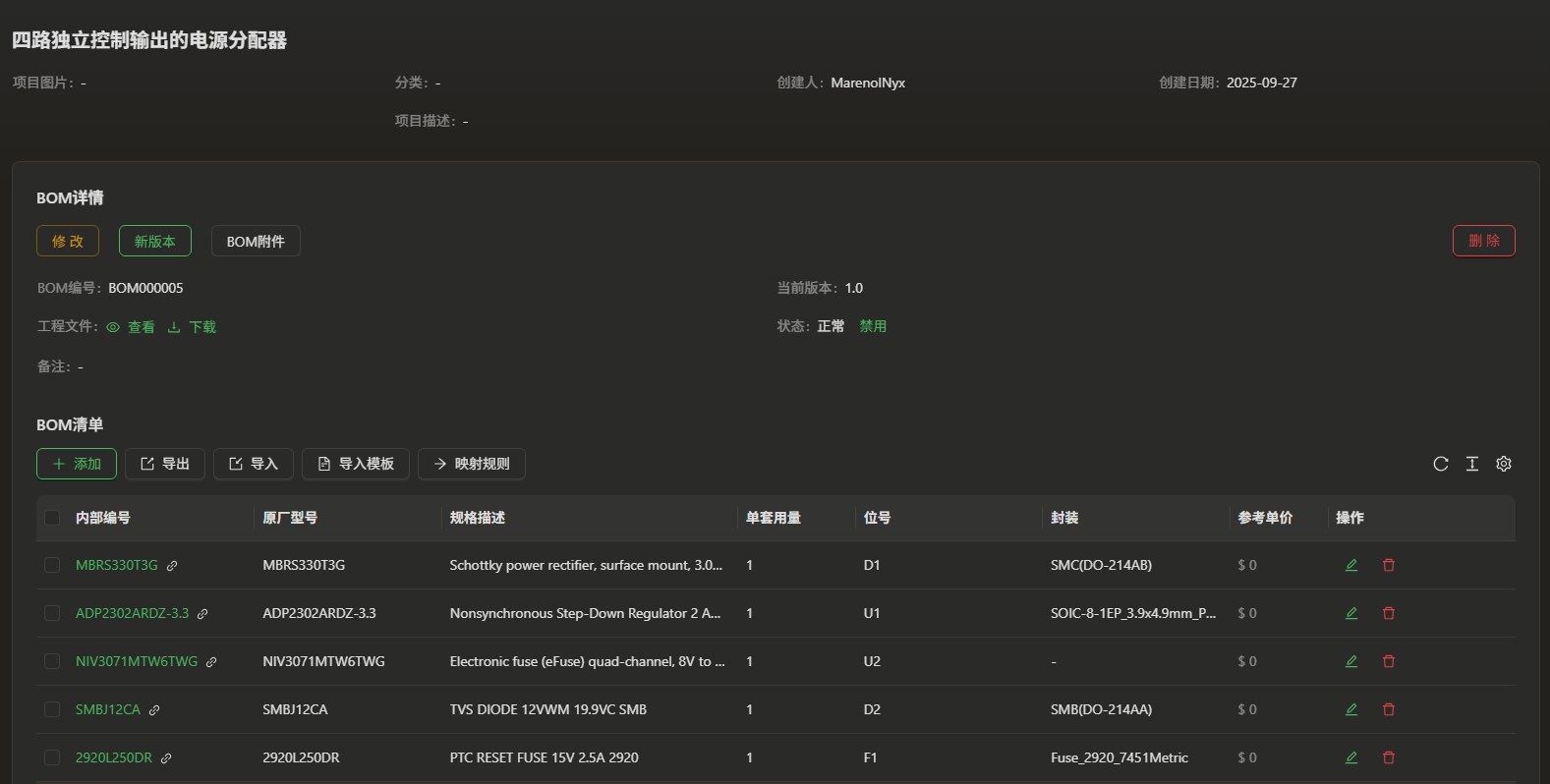

eZ-PLM项目

已于eZ-PLM系统中上传了自己的工程文件,方便保存记录各个版本,也可随时查阅,系统里查阅不到的物料也支持手动添加。

心得体会

本次设计让我对现代智能功率器件(如eFuse)的应用有了深刻的认识。从需求分析到选型再到原理图设计和考虑大电流路径的PCB布局,整个过程让我对模块化硬件的设计流程有了更全面的掌握。