任务介绍

本项目为参赛任务所选方案:设计一块用于竞赛与教学的光敏阈值触发数字输出模块,功能是把外界光强(通过光敏电阻 LDR)转成稳定的数字输出信号,并提供阈值调节、抖动抑制与调试友好接口,方便与 MCU、实验板或控制系统直接对接。

模块介绍

本模块基于 LM393 双路比较器 与 光敏电阻(LDR) 组成阈值比较回路。主要用途与特点如下:

- 将光敏分压模拟信号与可调参考电压比较,,便于与 MCU 或逻辑电路直接接口;

- 阈值通过板载 10 kΩ 可调电位器(RV1) 手动调节;

- 为避免阈值附近抖动,预留 迟滞(正反馈)电阻 R_hyst 位,可配置约 47k~200k;

- LM393 输出为 开集电极,模块外带上拉电阻(默认 10 kΩ),上拉电压 5V,以匹配下游设备电平;

- 模块可选通孔 LDR 放板边或用短引线做探头,便于放到被测环境获取光照;

- 模块体积小、设计简单,适合竞赛、教学与原型开发使用。

关键器件与参考:

- 比较器:LM393(DIP-8)

- 光敏电阻:CdS LDR(通孔)

- 电位器:10 kΩ trimmer(板上顶调或面板式)

- 去耦电容:0.1 µF 陶瓷(贴近 LM393 VCC/GND)

- 上拉电阻:10 kΩ;迟滞电阻:100 kΩ

- 输出接头:J1(3-pin 2.54 mm pinheader)

- 原理图和 PCB 模块介绍

LM393 双路比较器在DigiKey官网的链接:https://www.digikey.cn/zh/products/detail/shenzhen-slkormicro-semicon-co-ltd/LM393/26601007

光敏电阻(LDR)在Digikey官网的连接:https://www.digikey.cn/zh/products/detail/advanced-photonix/PDV-P8103/480610

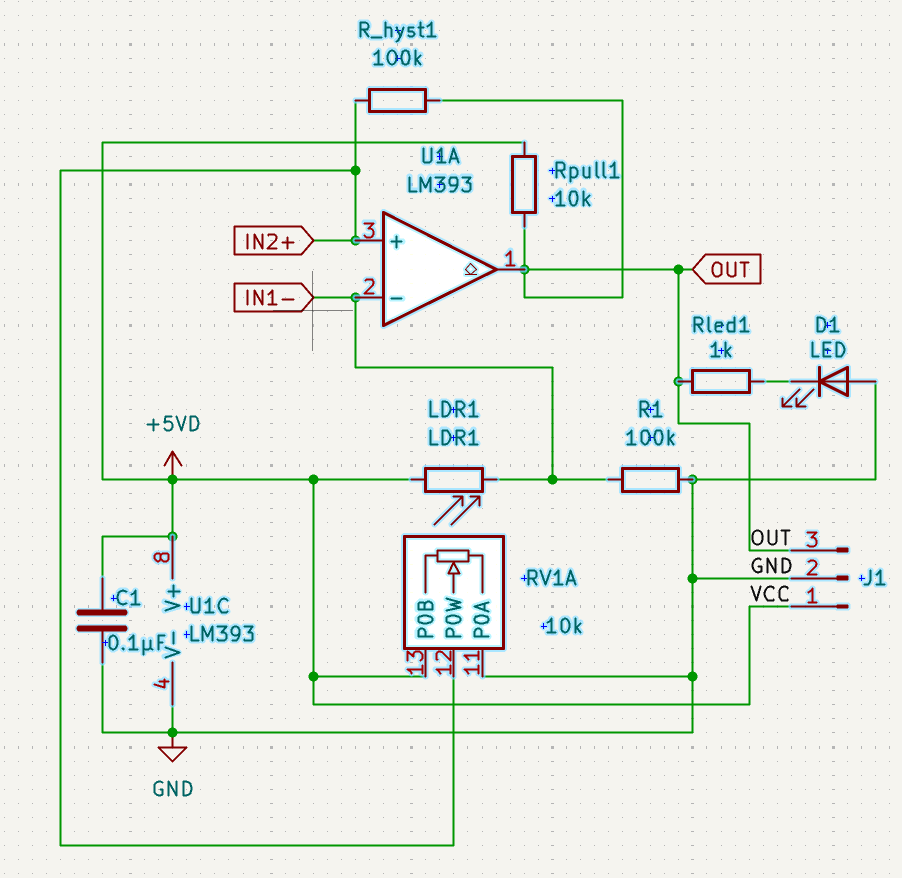

原理图

- 电源:模块工作电源为 5 V。模块不含主供电转换器,通常由上级板或外部电源提供 5 V。LM393 的 VCC 连接到

VCC,并在 VCC 与 GND 之间贴近放置C1 = 0.1 µF去耦。 - LDR 分压:LDR 与固定电阻 R_div(推荐 100 kΩ)构成分压,分压中点为

V_LDR。例如:VCC — LDR —(V_LDR)— R_div — GND。根据 LDR 的亮/暗阻值确定 R_div 最佳值(100k 为起点)。 - 参考电压:

V_REF来自RV1(10k 电位器)滑动端,电位器两端接 VCC/GND,滑端输出 0~VCC 的可调参考。 - 比较器接法:把

V_LDR接到 LM393 的IN-,把V_REF接到IN+(或反接以改变触发极性);LM393 的OUT外接上拉电阻 R_pull(10k)到 VCC,并作为模块数字输出V_OUT。 - 迟滞:从

OUT通过R_hyst反馈到IN+,实现少量迟滞,减少阈值附近抖动。 - LED 指示:

V_OUT通过R_led(1k)驱动LED1指示输出状态(若V_OUT为高,LED 点亮;若为低则熄灭;注意开集电极输出需要配置逻辑极性或接到合适位置)。 - 接口:J1(3-pin)定义:Pin1=VCC,Pin2=GND,Pin3=OUT(上拉电阻可让 OUT 在断开时为高)。

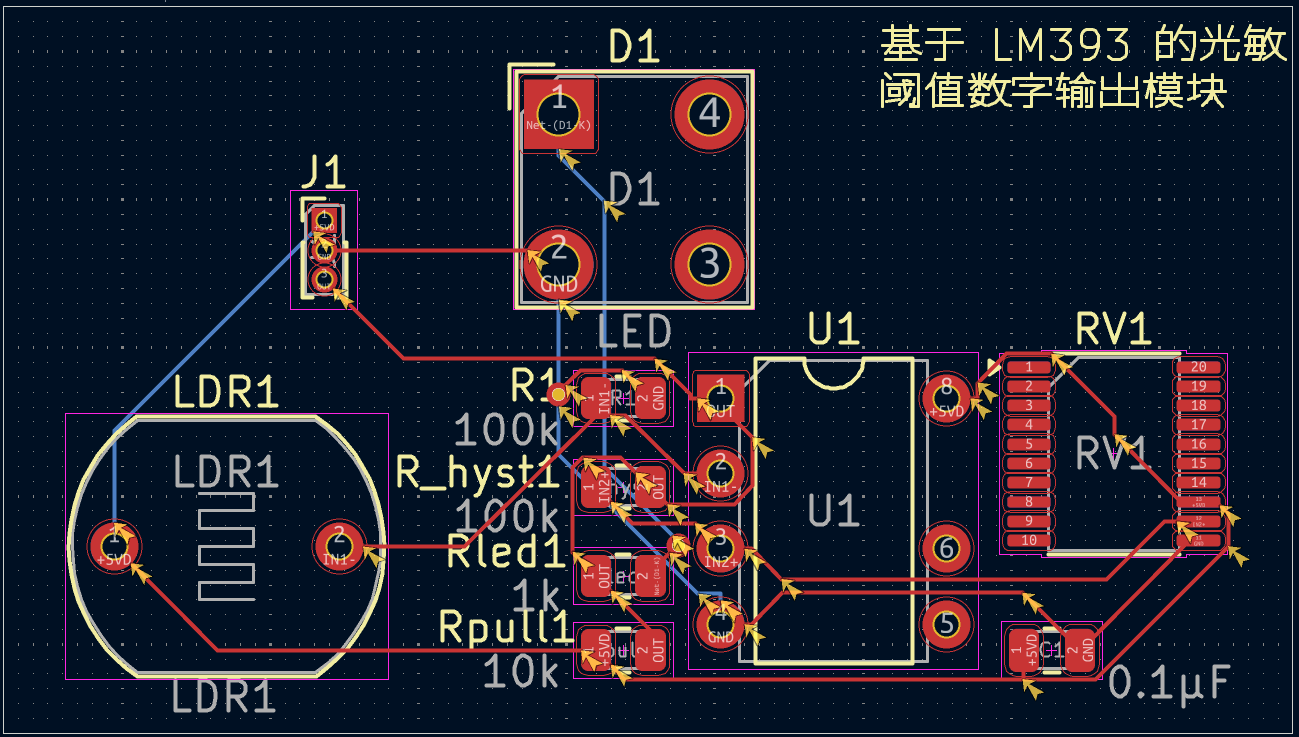

PCB(平面 / 布局)说明

- PCB 层数:双层板(Top: 器件与信号;Bottom: GND 覆铜)。

- 关键布局要点:

C1 (0.1 µF)必须贴近 LM393 的 VCC 与 GND 脚,走线尽量短,回路面积最小;RV1(调节器)应放在板边或易于操作位置;LDR放在板边或使用短引线做独立探头,PCB 上为其预留开窗或孔位;R_div(分压固定电阻)靠近 LDR 与 LM393 输入,形成短连接,减少噪声耦合;OUT上拉电阻 R_pull 靠近 LM393 OUT 引脚放置,并尽量短线到 J1 的 OUT 引脚;- 在 Bottom 层做大面积 GND 覆铜,并在关键点做过孔缝合(via stitching)以降低地阻抗。

- 机械 / 接口:J1 放在板边,Pin1(VCC)处用丝印标注小圆点或数字 1;TP 放在板边,便于探表或示波器夹持。

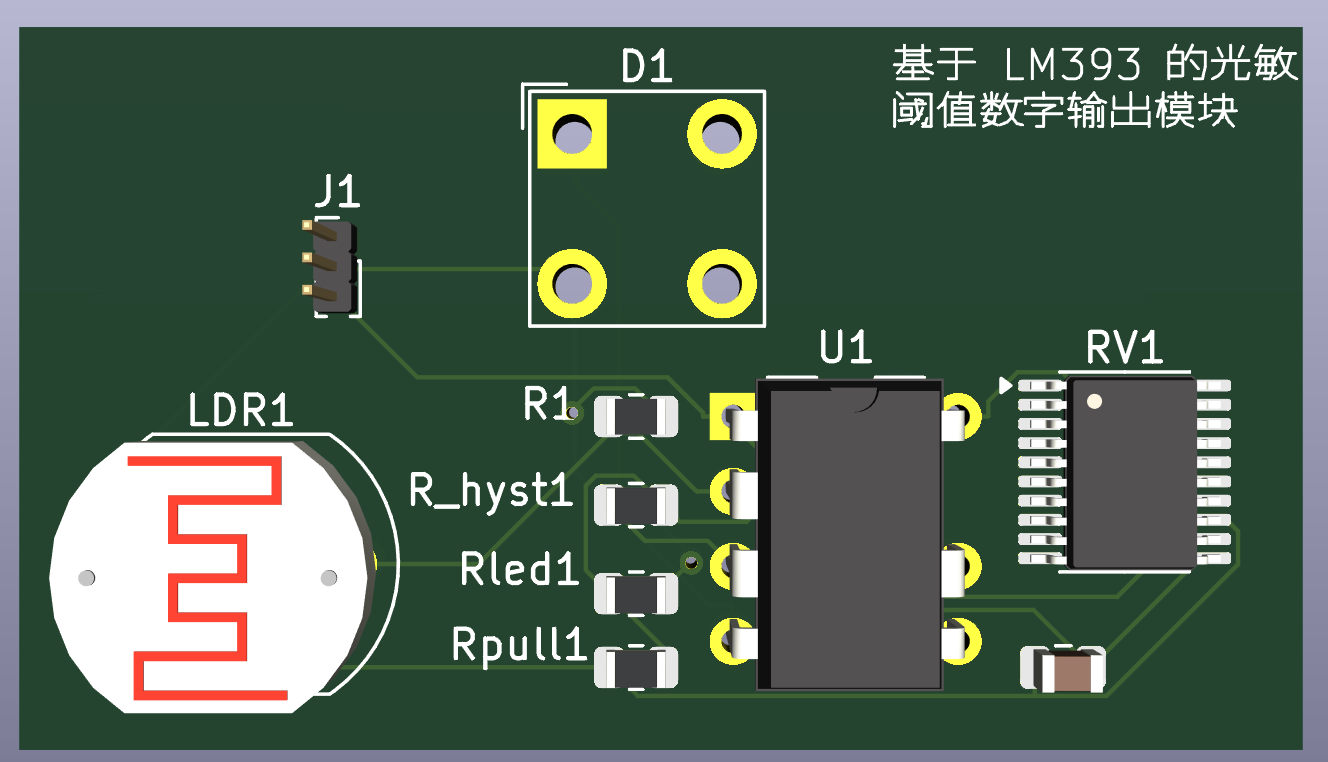

3D 效果图

- 3D 视图用于检查电位器旋钮、LDR 位置、J1 外形与板边间隙是否有冲突;

- 在 3D 中确认 LDR 是否可以伸出板边或保持平面放置;确认 LED 指示灯方向与可视面朝向一致;

模块主要性能指标和管脚定义

主要性能指标:

项目 | 说明 / 参数 |

工作电源 | 3.0 V ~ 5.5 V(推荐 3.3 V 或 5.0 V;LM393 与外部上拉电压需兼容) |

模块静态功耗 | 典型 < 5 mA(视 LED / 上拉电阻而定) |

扩展供电能力 | 板上 3.3 V(若由上级板提供)可为扩展板提供 最多约 500 mA(受温升与实际器件限制,请在高负载下评估热量) |

输出类型 | 开集电极(open-collector),必须外接上拉电阻(板载默认上拉 10 kΩ,可改为 3.3 V 或 5 V 上拉) |

阈值调节 | 电位器 RV1 = 10 kΩ,滑动端 V_REF 范围 0 ~ VCC |

输入分压参考 | LDR + R_div(建议 R_div 初值 100 kΩ,实测后调整) |

迟滞(Hysteresis) | 通过 R_hyst (建议 47k–200k,典型 100k)实现;典型迟滞量 约 0.05 V ~ 0.2 V(取决于分压与反馈阻值) |

响应时间 | 依 LM393 与并联滤波:微秒 — 毫秒 级;并联滤波电容会显著增加响应延迟 |

指示 / 报警 | 板载 LED(OUT 指示)和 PWR 指示(VCC 存在) |

PCB 尺寸(建议) | 示例:50 mm × 25 mm(可按项目调整) |

TestPoint | TP_VLDR, TP_VREF, TP_OUT, TP_VCC, TP_GND(便于波形/电压测量) |

推荐上拉 | 若对接 MCU,建议上拉到 MCU VCC(通常 3.3 V),上拉阻值常用 10 kΩ(根据速率/抗干扰可改为 4.7k/2.2k) |

保护建议 | 若用于户外或长线缆,建议在输入/输出加入 ESD/T TVS 及串联限流/RC 滤波元件 |

管脚定义:

引脚/标识 | 类型 | 名称 / 标签 | 功能说明 | 默认状态 / 备注 |

J1-Pin1 | 电源 | VCC | 模块供电正极(3.0–5.5 V)。同时为上拉电源参考(若上拉接此脚)。 | 供电:接 3.3V 或 5V;上电后 D_PWR 指示灯点亮 |

J1-Pin2 | 电源地 | GND | 模块公共地(0 V)。 | — |

J1-Pin3 | 数字输出 | OUT | 比较器数字输出(开集电极)。外部必须上拉到目标逻辑电平(VCC 或 MCU Vcc)。 | 开集电极输出;逻辑高由外部上拉决定,逻辑低由 LM393 导通拉低。 |

TP_VLDR | 测试点 | TP_VLDR | LDR 与分压电阻中点电压(模拟输入)。用于测量光照对应电压。 | 用万用表或示波器测量;常态范围:0 ~ VCC(取决分压与 LDR) |

TP_VREF | 测试点 | TP_VREF | 电位器滑动端(阈值参考电压)。 | 用于调节阈值;旋动 RV1 改变此点电压 |

TP_OUT | 测试点 | TP_OUT | 数字输出点(等同于 J1-Pin3,经上拉后的逻辑电平)。 | 可直接观测输出波形 |

TP_VCC | 测试点 | TP_VCC | 电源检测点(3.3V 或 5V)。 | 用于上电检查 |

TP_GND | 测试点 | TP_GND | 地检测点 | 用于示波器参考/测量 |

RV1 | 可调元件 | RV1 (10k) | 阈值电位器,端子两端接 VCC/GND,滑动端输出 V_REF。 | 推荐板上顶调器或面板微调器 |

LDR | 传感器 | LDR | 光敏电阻,构成分压回路的一个端。 | 推荐放板边或外引线做探头 |

R_div | 被动元件 | R_div (建议 100k) | 与 LDR 配合做分压(V_LDR = VCC * R_div/(R_LDR+R_div) 或相反,视接法) | 实测后可改值以获得最佳灵敏度 |

R_pull | 被动元件 | R_pull (10k) | OUT 的上拉电阻(板载,若不需可外接不同阻值) | 上拉到 VCC 或 MCU Vcc |

R_hyst | 被动元件(可选) | R_hyst (建议 100k) | OUT→IN(正反馈)迟滞电阻位置(可选装) | 可通过更换阻值调节迟滞幅度 |

LED_PWR | 指示 | D_PWR | 电源指示 LED(VCC 存在时亮) | 串联限流电阻 R_led(默认值 1k) |

LED_OUT | 指示 | D_OUT / STA | 输出状态指示 LED(由 V_OUT 控制) | 注意开集电极极性,若需反向请调整接法 |

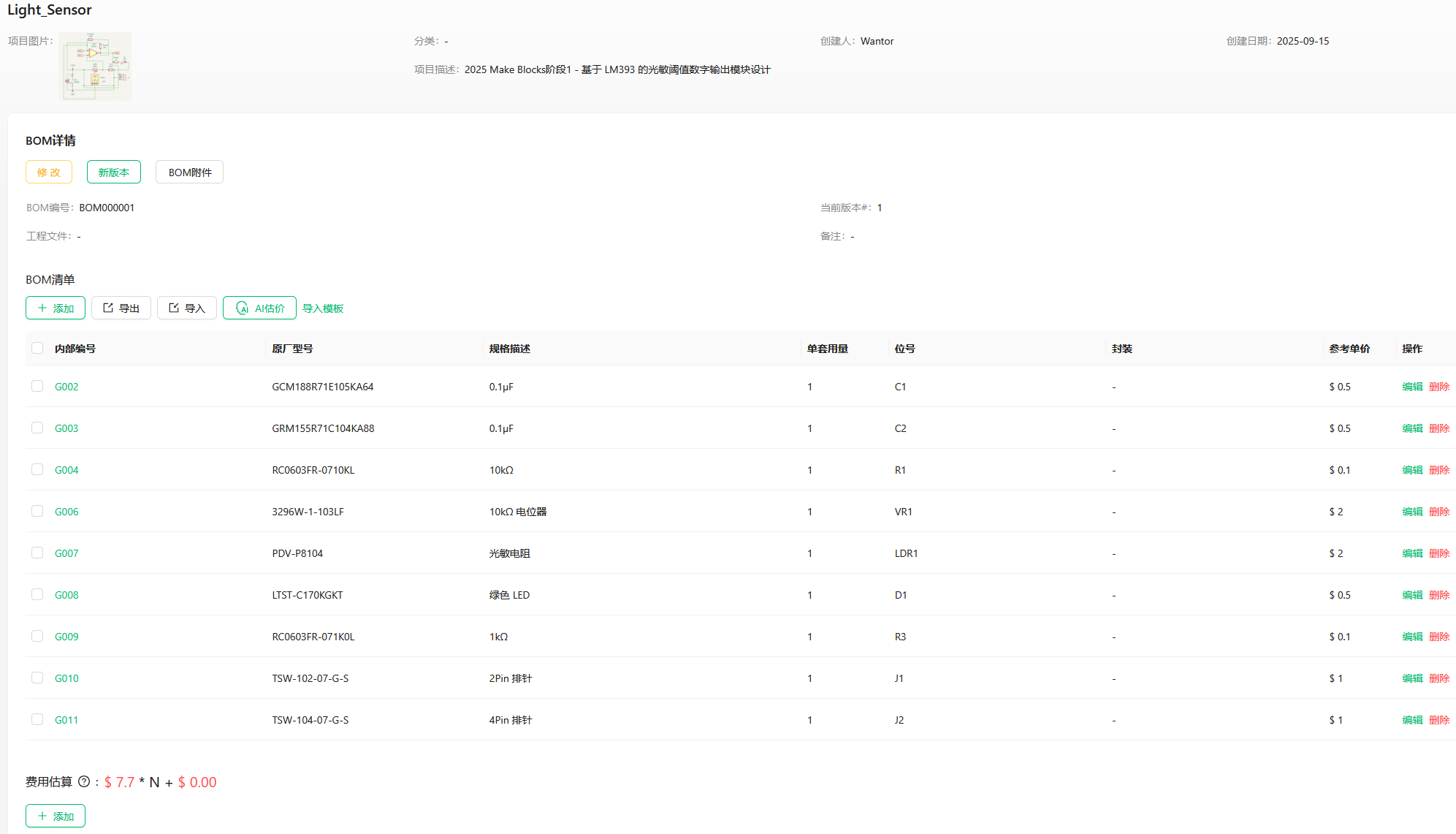

eZ-PLM上新建物料和项目的截图

使用了eZ-PLM系统上传了自己的工程文件,方便保存记录各个版本,也可随时查阅,系统里查阅不到的物料也支持手动添加:

项目详情图:

心得体会

在本次任务三的设计中,我完成了基于 LM393 比较器 的光敏电阻阈值检测电路。通过光敏电阻与电位器分压实现参考电压比较,并输出数字信号。

在设计过程中,我体会到 器件选型、去耦电容布局以及接口位置 的重要性。通过实际调试,进一步理解了比较器的应用及 PCB 设计的基本原则。本项目让我熟悉了从 电路原理 → 原理图 → PCB → BOM 的完整流程,为后续更复杂的电路设计打下了基础。