双通道50Msps/10MHz口袋示波器

1 主要功能及特性

2 相关设计文档

- BOM文件

- KiCad设计文件 - ZIP格式

- Gerber文件 - ZIP格式

3 核心器件技术资料及数据手册

4 参考代码

数据ADC读出、LCD写入的状态控制

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // Module: Arbiter // // Author: Step // // Description: Control sample and display in different time // // Web: www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.1 |2016/10/30 |Initial ver // -------------------------------------------------------------------- module Arbiter ( input clk_in, // system clock input rst_n_in, //system reset, active low input sample_done, input display_done, output reg sample_en, output reg display_en ); localparam IDLE = 2'd0; localparam SAMPLE = 2'd1; localparam DISPLAY = 2'd2; reg [1:0] state; always@(posedge clk_in or negedge rst_n_in) begin if(!rst_n_in) begin state <= IDLE; sample_en <= 1'b0; display_en <= 1'b0; end else begin case(state) IDLE:begin sample_en <= 1'b0; display_en <= 1'b0; state <= SAMPLE; end SAMPLE:begin if(sample_done) begin sample_en <= 1'b0; display_en <= 1'b1; state <= DISPLAY; end else begin sample_en <= 1'b1; display_en <= 1'b0; end end DISPLAY:begin if(display_done) begin sample_en <= 1'b1; display_en <= 1'b0; state <= SAMPLE; end else begin sample_en <= 1'b0; display_en <= 1'b1; end end default:state <= IDLE; endcase end end endmodule

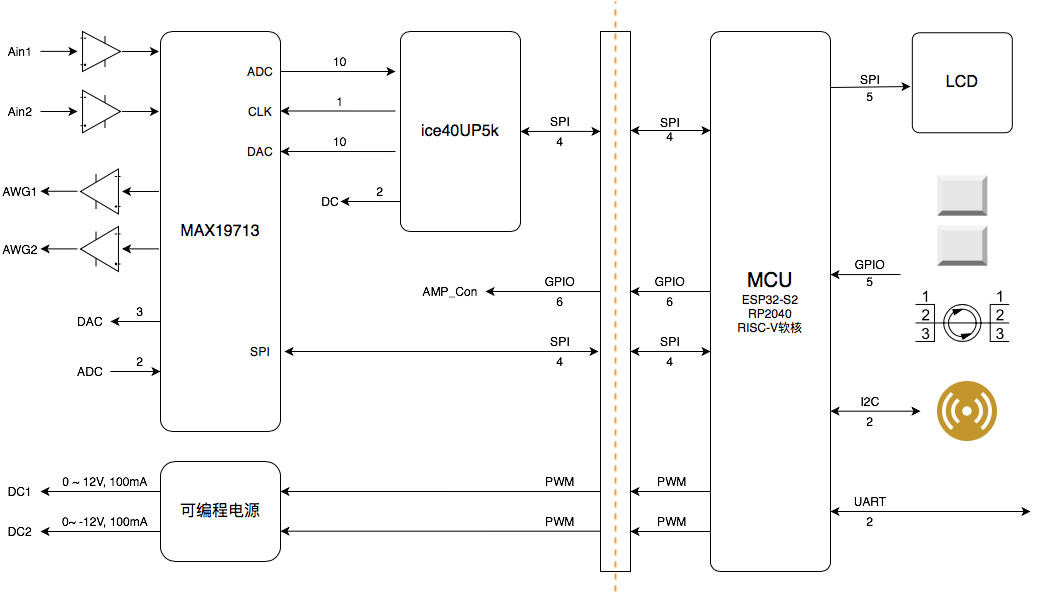

口袋仪器接口模块

- 树莓派HAT的尺寸并兼容树莓派的管脚定义

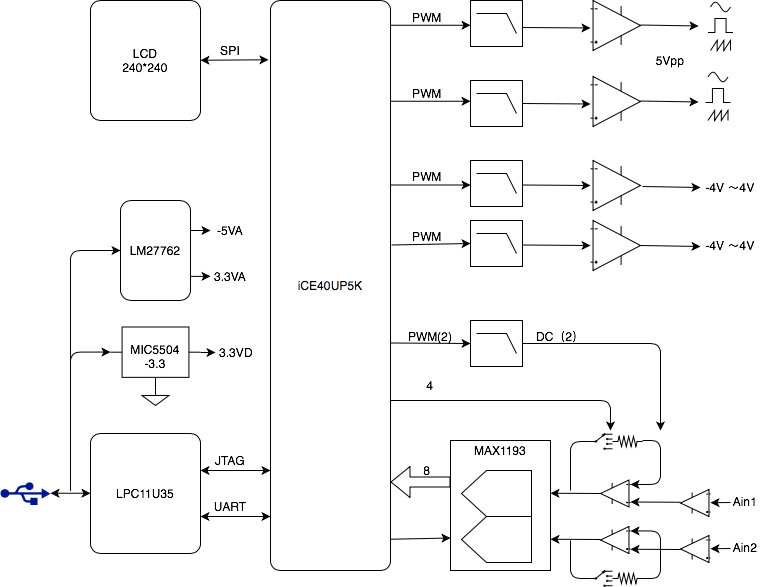

- 基于MAX19713 + ICE40UP5K

MAX19713 AFE

MAX19713 AFE

- 双10bit,45Msps Rx ADC

- 双10bit,45Msps Tx DAC

- 可编程Tx DAC共模 DC电平和I/Q偏移调节

- 3路12位,1us辅助DAC

- 10位,333Ksps辅助ADC以及4:1 Mux和数据平均, 外接两路 + Vdd/2 + OVdd/2

- 56 TQFN封装(7mm x 7mm)

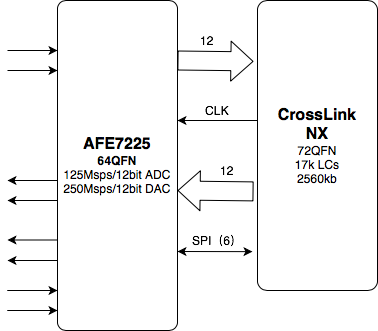

AFE7225 AFE

- 双12位250Msps Tx DACs

- 双12位125Msps Rx ADCs

- 双12位备用DACs

- 双输入12位备用ADCs

- 64 QFN封装(9mm*9mm)

- 串行LVDS或交叉并行CMOS接口

- 2个或4个Tx内插路径

- 2个Rx抽取路径

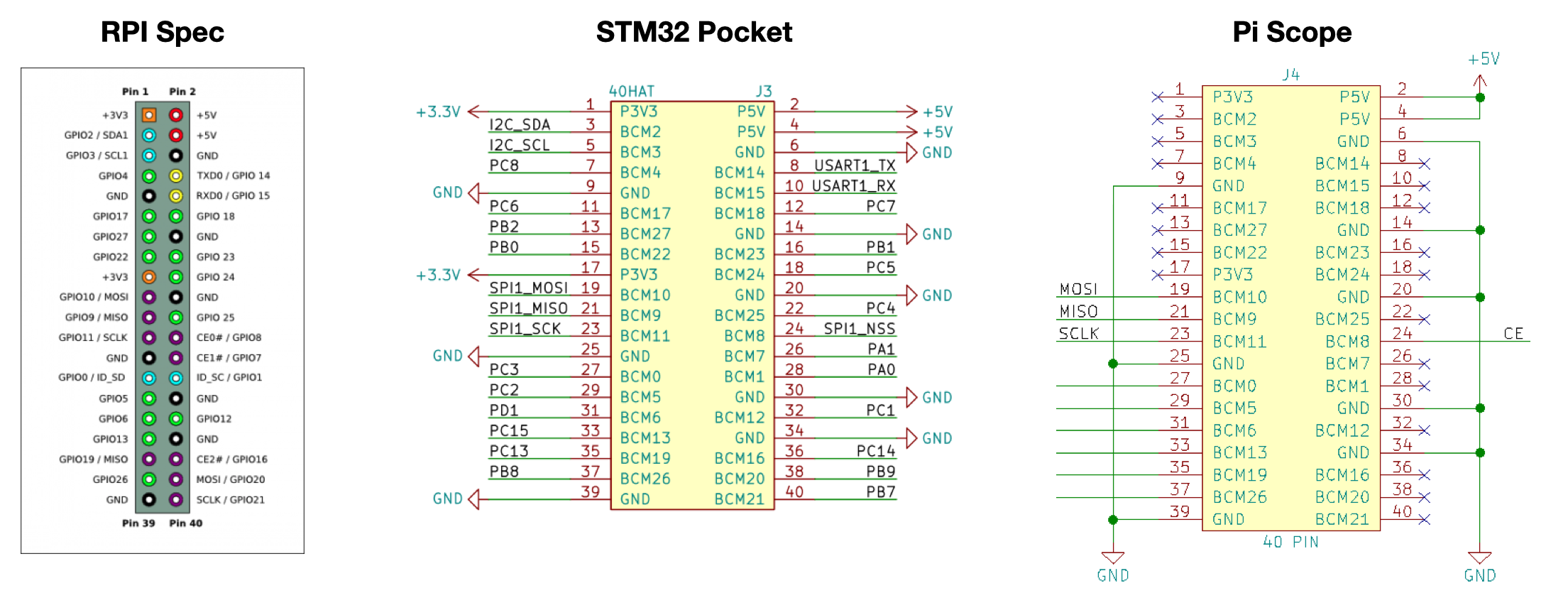

| 插座管脚 | 树莓派 | STM32Pocket | Pi Instrument |

| 1 | 3.3V | 3.3V | x |

| 2 | 5V | 5V | 5V |

| 3 | GPIO2 SDA1 | I2C SDA | x |

| 4 | 5V | 5V | 5V |

| 5 | GPIO3 SCL1 | I2C SCL | x |

| 6 | GND | GND | GND |

| 7 | GPIO4 | PC8 | x |

| 8 | TXD0 GPIO14 | USART1 TX | x |

| 9 | GND | GND | GND |

| 10 | RXD0 GPIO15 | USART1 RX | x |

| 11 | GPIO17 | PC6 | x |

| 12 | GPIO18 | PC7 | x |

| 13 | GPIO27 | PB2 | x |

| 14 | GND | GND | GND |

| 15 | GPIO22 | PB0 | x |

| 16 | GPIO23 | PB1 | x |

| 17 | 3.3V | 3.3V | x |

| 18 | GPIO24 | PC5 | x |

| 19 | GPIO10 MOSI | SPI1 MOSI | MOSI |

| 20 | GND | GND | GND |

| 21 | GPIO9 MISO | SPI1 MISO | MISO |

| 22 | GPIO25 | PC4 | x |

| 23 | GPIO11 SCLK | SPI1 SCK | SCLK |

| 24 | CE0# GPIO8 | SPI1 NSS | CS |

| 25 | GND | GND | GND |

| 26 | CE1# GPIO7 | PA1 | x |

| 27 | GPIO0 IDSD | PC3 | DIO |

| 28 | IDSC GPIO1 | PA0 | x |

| 29 | GPIO5 | PC2 | DIO |

| 30 | GND | GND | GND |

| 31 | GPIO6 | PD1 | DIO |

| 32 | GPIO12 | PC1 | x |

| 33 | GPIO13 | PC15 | DIO |

| 34 | GND | GND | GND |

| 35 | GPIO19 MISO | PC13 | MAX19713 MISO |

| 36 | CE2# GPIO16 | PC14 | MAX19713 CSn |

| 37 | GPIO26 | PB8 | DIO |

| 38 | MOSI GPIO20 | PB9 | MAX19713 MOSI |

| 39 | GND | GND | GND |

| 40 | SCLK GPIO21 | PB7 | MAX19713 SCLK |