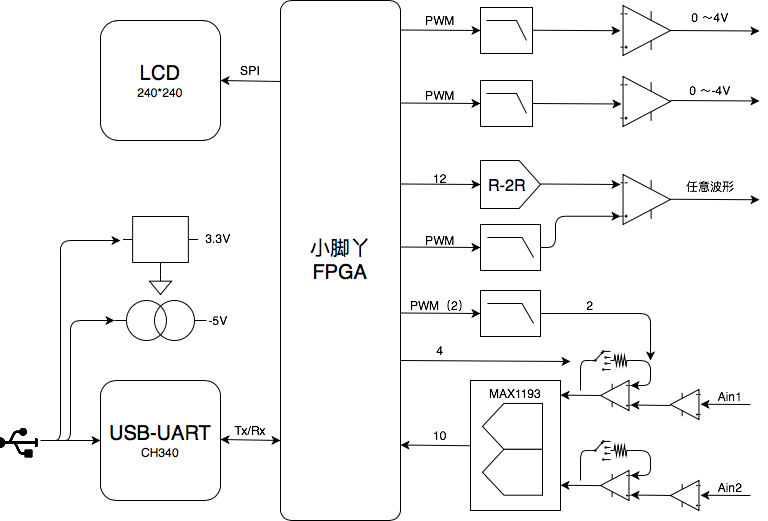

基于小脚丫FPGA的口袋仪器

1 主要功能及特性

2 相关设计文档

- BOM文件

- KiCad设计文件 - ZIP格式

- Gerber文件 - ZIP格式

3 核心器件技术资料及数据手册

4 参考代码

数据ADC读出、LCD写入的状态控制

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // Module: Arbiter // // Author: Step // // Description: Control sample and display in different time // // Web: www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.1 |2016/10/30 |Initial ver // -------------------------------------------------------------------- module Arbiter ( input clk_in, // system clock input rst_n_in, //system reset, active low input sample_done, input display_done, output reg sample_en, output reg display_en ); localparam IDLE = 2'd0; localparam SAMPLE = 2'd1; localparam DISPLAY = 2'd2; reg [1:0] state; always@(posedge clk_in or negedge rst_n_in) begin if(!rst_n_in) begin state <= IDLE; sample_en <= 1'b0; display_en <= 1'b0; end else begin case(state) IDLE:begin sample_en <= 1'b0; display_en <= 1'b0; state <= SAMPLE; end SAMPLE:begin if(sample_done) begin sample_en <= 1'b0; display_en <= 1'b1; state <= DISPLAY; end else begin sample_en <= 1'b1; display_en <= 1'b0; end end DISPLAY:begin if(display_done) begin sample_en <= 1'b1; display_en <= 1'b0; state <= SAMPLE; end else begin sample_en <= 1'b0; display_en <= 1'b1; end end default:state <= IDLE; endcase end end endmodule