任务介绍

题目要求:

- 设计一款以太网SPI模块

- 实现MCU通过SPI接口连接以太网

- 包含:RJ45磁性插座(建议使用集成变压器的)、25MHz晶振和状态LED。

- 主要器件:需在DigiKey官网上有货且正常售卖

请注意:PCB设计工具需用KiCad(官方邮件赠送了课程),或最终提交的文件需是KiCad文件,详见大赛主页阶段1要求和项目提交内容。

模块介绍

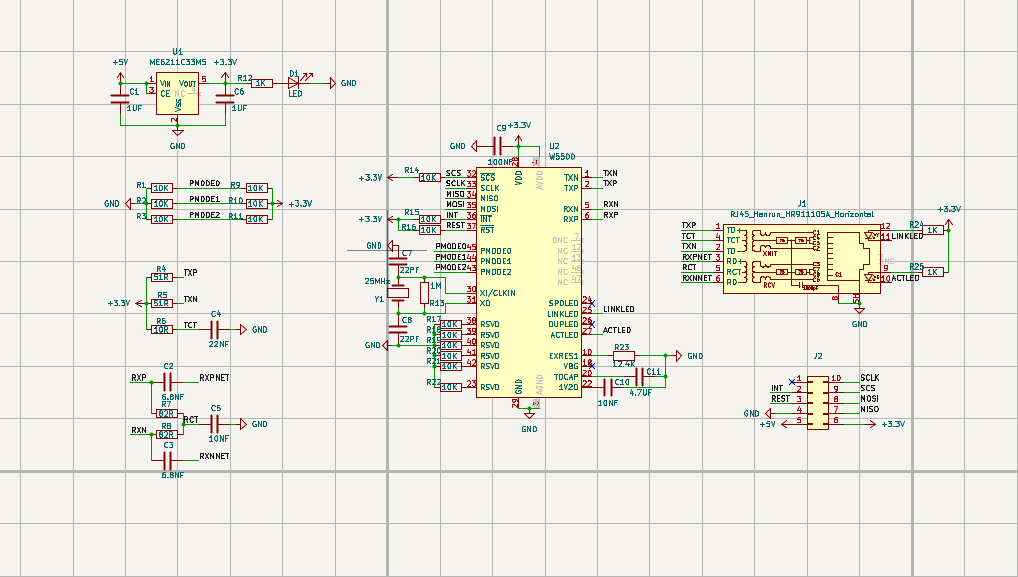

根据任务要求本次我选用的是W5500芯片设计了一款以太网SPI模块,本电路模块基于W5500芯片,主要实现以太网物理层和网络层的硬件接口,适用于嵌入式系统的以太网通信扩展。模块核心架构如下:

1. 电源管理

- 通过U1(ME6211C33M5)将+5V降压至+3.3V,为W5500及相关外围电路供电。

- 多颗去耦电容(C1、C6、C9等)分布在电源输入和芯片附近,确保电源稳定,抑制高频噪声。

2. 以太网接口

- 采用RJ45带变压器接口(J1: Hanrun HR911105A),实现与以太网物理层的连接。

- 差分信号(TXP/TXN、RXP/RXN)通过匹配电阻(R4、R5、R7、R8)和耦合电容(C2、C3、C4、C5)与RJ45连接,保证信号完整性和抗干扰能力。

3. W5500主控芯片

- W5500(U2)为硬件TCP/IP协议栈芯片,支持SPI接口与主控MCU通信。

- SPI信号(/SCS, /SCLK, /MOSI, /MISO)通过J2(2x5排针)引出,便于与主控板连接。

- 复位、模式选择、外部中断等控制信号均有上拉/下拉电阻,确保上电状态可控。

4. 时钟电路

- 采用25MHz有源晶振(Y1)及其负载电容(C7、C8),为W5500提供主时钟。

5. 指示与辅助功能

- 板载LED(D1)用于状态指示,通过限流电阻(R12)与W5500的LED控制引脚连接。

- 其他辅助电路如外部电阻(R23)用于芯片内部参考,滤波电容(C10、C11)用于内部稳压和参考电压稳定。

6. 扩展与调试接口

- J2排针引出SPI、复位、中断等信号,方便与主控MCU或调试工具连接。

设计目标

- 提供稳定可靠的以太网接口,便于嵌入式系统快速实现网络通信。

- 电路布局紧凑,适合小型化、低功耗应用。

- 兼容主流MCU的SPI接口,便于集成到各类项目中。

W5500芯片DigiKey链接:https://www.digikey.cn/zh/products/detail/wiznet/W5500/4425702?s=N4IgTCBcDaIOoFYEAZkgLoF8g

原理图和PCB模块介绍

原理图模块介绍

本模块原理图围绕W5500以太网控制芯片展开,主要分为以下几个功能单元:

- 电源管理单元

- 通过U1(ME6211C33M5)将+5V输入降压为+3.3V,供W5500及外围电路使用。

- 多颗去耦电容(C1、C6、C9等)分布在电源输入和芯片电源引脚附近,提升电源稳定性,降低噪声。

- 以太网物理接口单元

- RJ45接口(J1)带集成网络变压器,负责与外部以太网连接。

- 差分信号(TXP/TXN、RXP/RXN)通过匹配电阻和耦合电容与RJ45连接,保证信号完整性和抗干扰能力。

- 主控芯片单元

- W5500(U2)为核心芯片,负责以太网协议处理和数据收发。

- SPI接口(/SCS, /SCLK, /MOSI, /MISO)通过J2排针引出,便于与主控MCU连接。

- 复位、模式选择、外部中断等信号均有上拉/下拉电阻,确保上电状态可控。

- 时钟电路单元

- 25MHz晶振(Y1)及其负载电容(C7、C8)为W5500提供主时钟。

- 指示与辅助单元

- 板载LED(D1)用于网络状态指示,通过限流电阻(R12)与W5500的LED控制引脚连接。

- 其他辅助电路如外部参考电阻(R23)、滤波电容(C10、C11)等,保证芯片内部参考和稳压电路的稳定。

原理图

PCB模块介绍

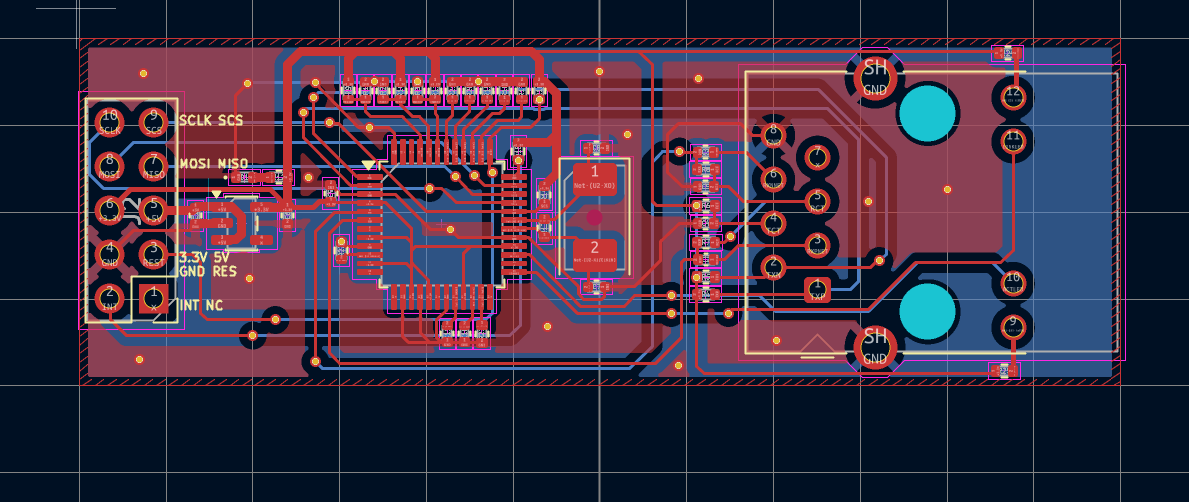

PCB设计遵循信号完整性和电源完整性原则,主要布局特点如下:

- 分区布局

- 电源、W5500主芯片、RJ45接口、时钟电路、指示灯等功能区块分明,便于信号流向和EMC控制。

- 电源与地平面

- 采用大面积地平面,所有电源引脚附近均布置去耦电容,降低高频噪声。

- 电源走线尽量短粗,关键芯片电源引脚优先布线,保证供电稳定。

- 高速信号布线

- 以太网差分信号(TXP/TXN、RXP/RXN)严格等长、等宽布线,走线间距和阻抗控制,减少信号反射和串扰。

- SPI信号线短且直,避免与高噪声电源线平行布线。

- 时钟与敏感信号处理

- 晶振靠近W5500布置,负载电容对称,时钟线尽量短,避免跨分区走线。

- 复位、模式选择等控制信号远离高速信号线,防止干扰。

- 接口与调试

- J2排针、RJ45接口等均布置在PCB边缘,便于外部连接和调试。

- LED指示灯靠近板边,便于观察。

PCB

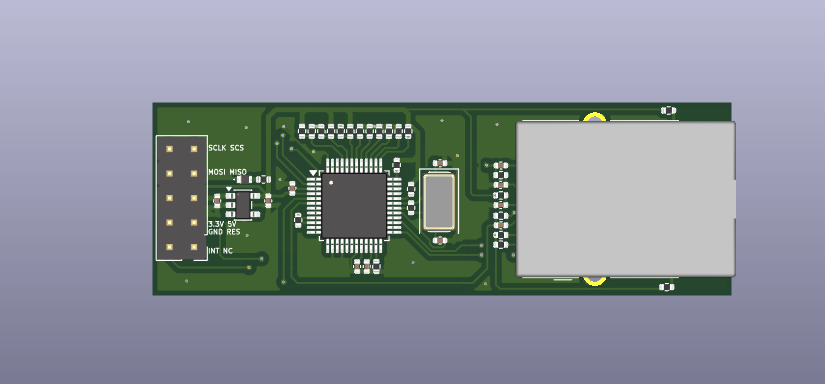

3D效果图

模块主要性能指标和管脚定义

主要性能指标

- 以太网接口

- 支持10/100Mbps自适应以太网通信(IEEE 802.3标准)

- 采用RJ45接口,带集成网络变压器,支持标准网线直连

- 通信协议

- 内置硬件TCP/IP协议栈(支持TCP、UDP、ICMP、IPv4、ARP、IGMP、PPPoE等)

- 支持多达8个独立Socket并发通信

- 主控接口

- SPI总线接口,最高支持80MHz时钟速率

- 兼容3.3V逻辑电平

- 电源参数

- 输入电压:+5V(通过LDO降压至3.3V供芯片使用)

- 工作电流:典型值约100mA(视网络负载而定)

- 时钟

- 采用25MHz有源晶振,保证以太网通信时序精度

- 物理尺寸

- 采用0402封装元件,适合小型化设计

- PCB尺寸可根据实际项目需求调整

- 其他特性

- 板载网络状态LED指示

- 具备复位、外部中断、模式选择等控制功能

管脚定义板上设置及标识

主要管脚定义(以J2和J1为例)

J2(2x5 2.54mm排针,主控接口)

引脚号 | 信号名 | 功能说明 |

|---|---|---|

1 | NC | 预留/未连接 |

2 | /INT | W5500中断输出 |

3 | /REST | W5500复位输入 |

4 | GND | 地 |

5 | +5V | 电源输入 |

6 | +3.3V | 3.3V输出 |

7 | /MISO | SPI主输入从输出 |

8 | /MOSI | SPI主输出从输入 |

9 | /SCS | SPI片选 |

10 | /SCLK | SPI时钟 |

J1(RJ45以太网接口,Hanrun HR911105A)

引脚号 | 信号名 | 功能说明 |

|---|---|---|

1 | TXP | 以太网差分发送正 |

2 | TXN | 以太网差分发送负 |

3 | RXPNET | 以太网差分接收正 |

4 | TCT | 变压器中心抽头 |

5 | RCT | 变压器中心抽头 |

6 | RXNNET | 以太网差分接收负 |

7 | NC | 未连接 |

8 | GND | 地 |

9 | 用户自定义 | 可接地或其他功能 |

10 | /ACTLED | 网络活动LED控制 |

11 | /LINKLED | 网络连接LED控制 |

12 | 用户自定义 | 可接地或其他功能 |

SH | 屏蔽层 | 接地 |

W5500主要功能引脚(部分)

- 1,2,5,6:以太网差分信号(TXP/TXN, RXP/RXN)

- 11,15,17,21,28,4,8:电源3.3V

- 14,16,19,29,3,9,48:地

- 32:SPI片选(/SCS)

- 33:SPI时钟(/SCLK)

- 34:SPI MISO

- 35:SPI MOSI

- 36:中断输出(/INT)

- 37:复位输入(/REST)

- 30,31:晶振输入/输出(XI/CLKIN, XO)

- 27,25,26,24:LED控制(/ACTLED, /LINKLED, DUPLED, SPDLED)

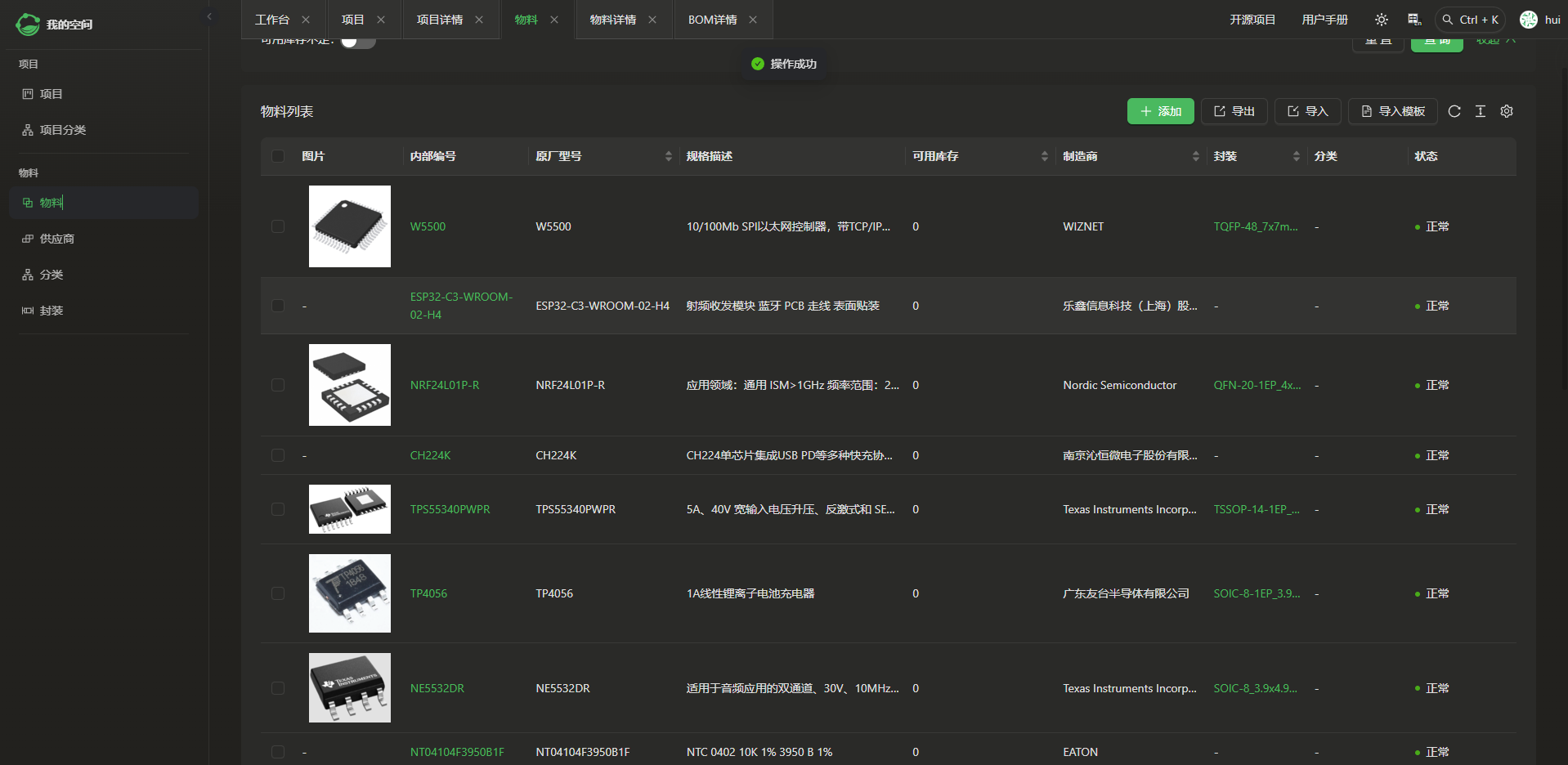

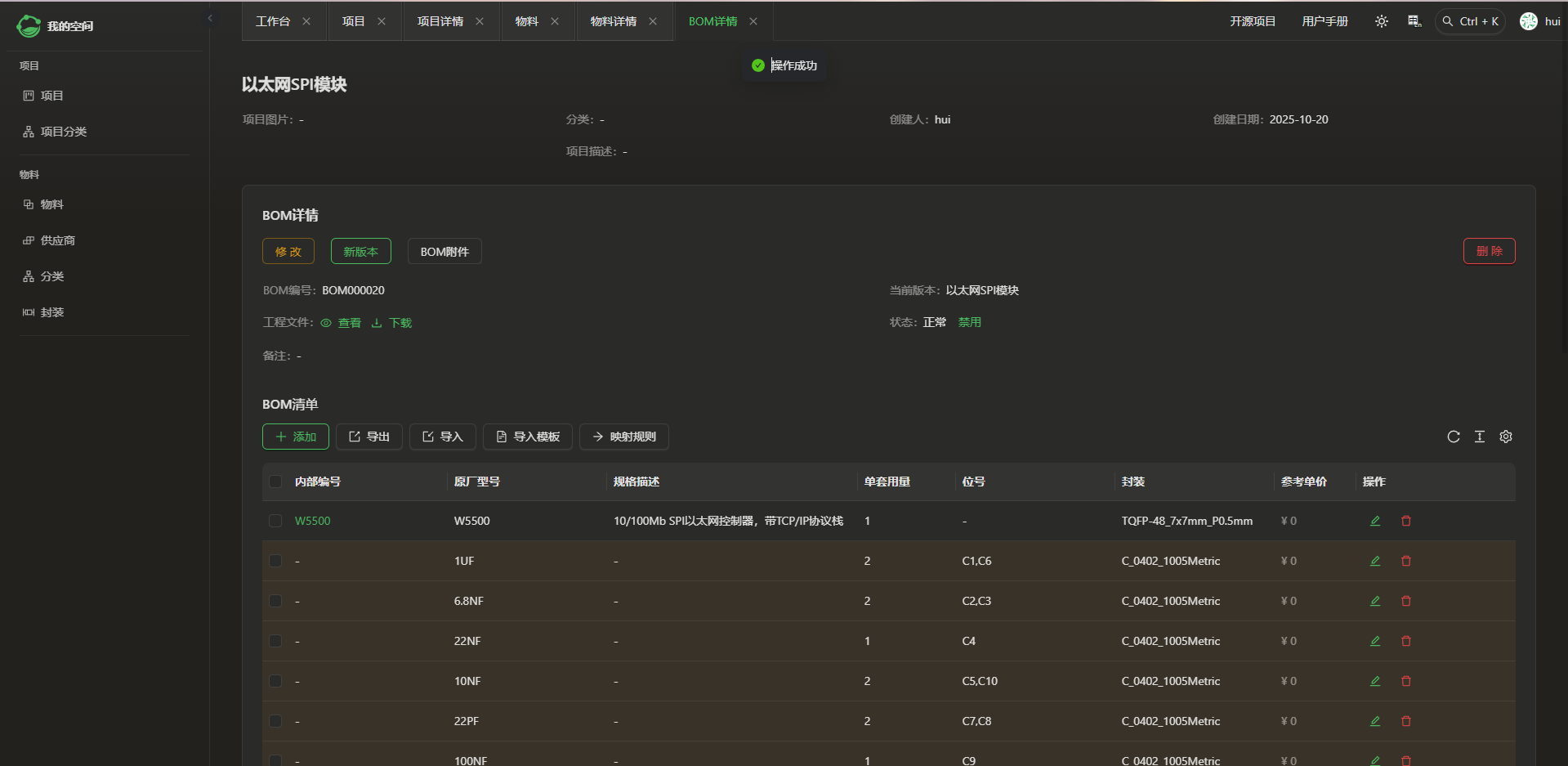

eZ-PLM上新建物料和项目的截图

使用了eZ-PLM系统上传了自己的工程文件,方便保存记录各个版本,也可随时查阅,系统里查阅不到的物料也支持手动添加。

物料添加展示图

项目详情图

心得体会

本次以W5500为核心的以太网模块设计,让我深入理解了高速信号布线、电源完整性和接口兼容性的重要性。通过合理的原理图分区和PCB布局,保证了信号的完整性和系统的稳定性。实际调试过程中,SPI通信和网络连接均表现良好,验证了设计的可靠性。此次项目不仅提升了我的硬件设计能力,也加深了对以太网通信协议和嵌入式系统集成的理解,为后续更复杂的网络应用开发打下了坚实基础。