项目报告

一、任务介绍

以太网SPI模块

题目要求:

- 设计一款以太网SPI模块

- 实现MCU通过SPI接口连接以太网

- 包含:RJ45磁性插座(建议使用集成变压器的)、25MHz晶振和状态LED。

二、模块介绍

根据任务要求,本次我选用了 WIZnet W5500 芯片设计了一款以太网 SPI 接口模块。

该模块可实现 MCU 通过 SPI 接口快速访问 TCP/IP 硬件栈,从而支持 TCP、UDP、ICMP 等多种网络协议,广泛应用于工业物联网、远程监测和嵌入式服务器系统。

模块采用 带集成变压器的 RJ45 磁性插座,内置 LED 指示功能,并配合 25 MHz 有源晶振、差分网络阻抗匹配、3.3 V 稳压供电等外围电路,确保网络信号稳定可靠。

主要供电接口如下:

- VCC(3.3 V):由主控板提供;

- GND:信号与电源地;

- SPI 接口信号: MOSI、MISO、SCLK、CS;

- RST、INT:模块复位与中断引脚;

- RJ45:标准 10/100 M 以太网口。

W5500芯片DigiKey链接:W5500 WIZnet | 集成电路(IC) | DigiKey

三、原理图与 PCB 模块介绍

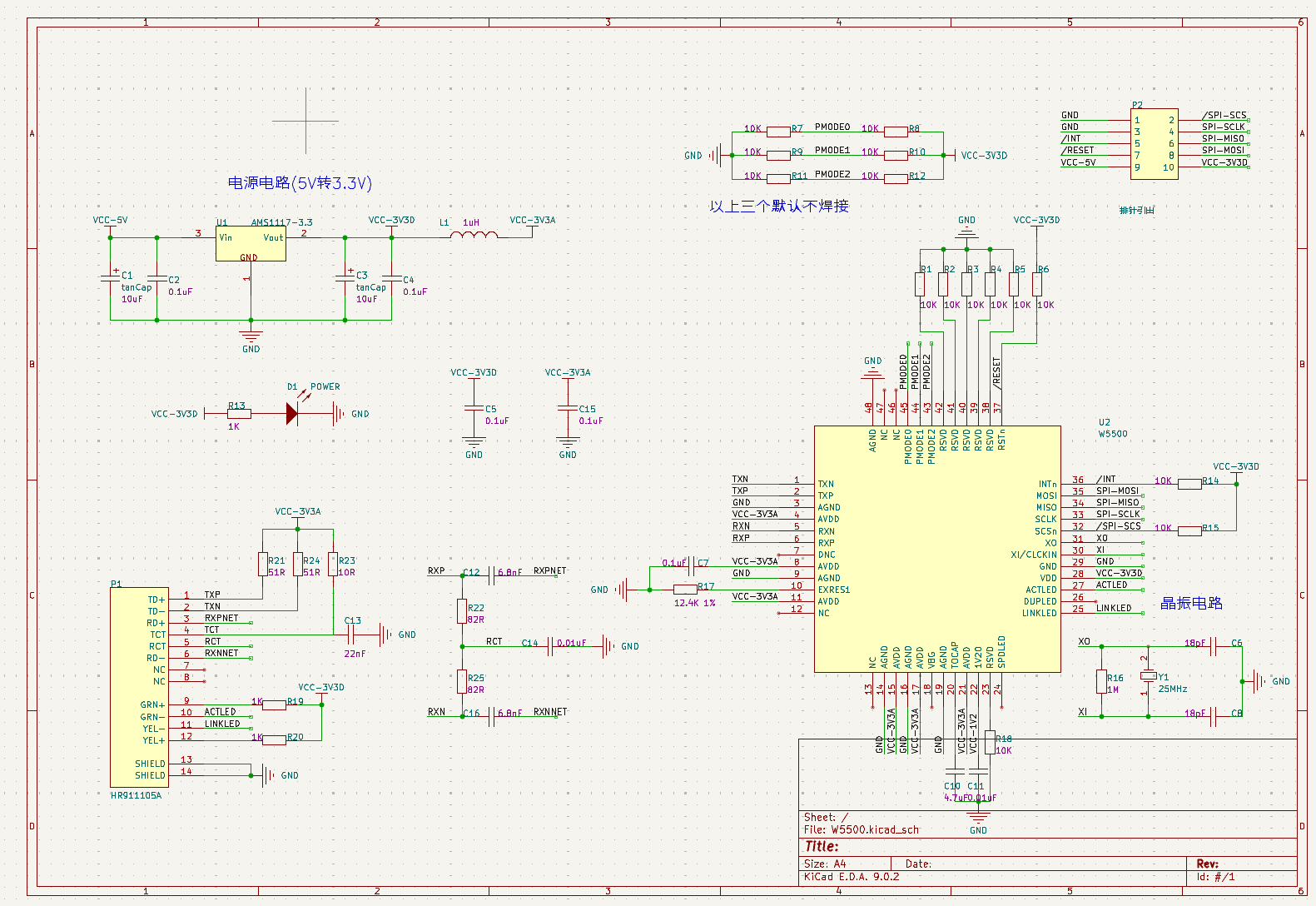

1️⃣ 原理图

主要电路部分:

- W5500 主芯片:提供 SPI 接口与 MAC/PHY 功能;

- RJ45 磁性插座(带 LED):完成网络差分隔离与指示;

- 25 MHz 晶振:为 W5500 提供系统时钟;

- 电源电路:3.3 V 稳压、去耦、电源滤波磁珠;

- 调试与复位电路:RST 上拉、电平检测、可外接 MCU 控制;

- LED 状态电路:链接 LINK 与 ACT 指示灯;

- 终端阻抗网络:49.9 Ω 匹配与 Bob-Smith 终端抑制共模干扰。

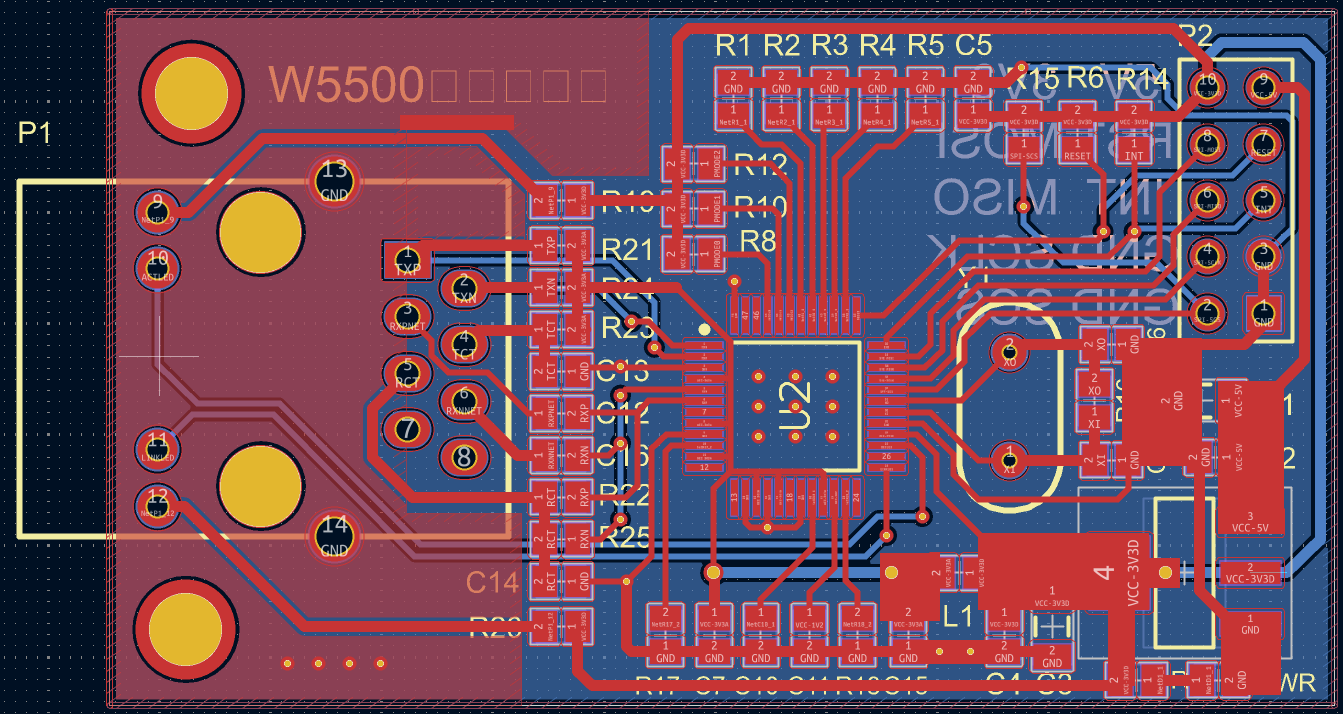

2️⃣ PCB 设计

PCB 采用 双面板设计,板卡尺寸约 55 mm × 31 mm。

布局要点:

- RJ45 接口 靠近板边,便于插拔;

- W5500 与 RJ45 差分线长度匹配,100 Ω 差分阻抗控制;

- 数字与模拟电源分区, AVDD 与 DVDD 之间通过磁珠连接;

- 电源去耦 就近放置 0.1 µF + 10 µF 组合电容;

- 机壳地 (Chassis GND) 独立铺铜;

- LED、RST、INT 接口 引出至排针,方便主控控制。

3️⃣ 模块结构说明

W5500 模块通过标准 2 × 5 Pin 排针接口与 MCU 相连,可直接插接到主控板扩展口中。

SPI 时钟可达 80 MHz,模块内部具备 32 KB 缓冲区,可同时支持 8 个 Socket 连接。

模块上配有两颗 LED:

- LINK (绿) — 网络连接指示;

- ACT (黄) — 数据活动指示。

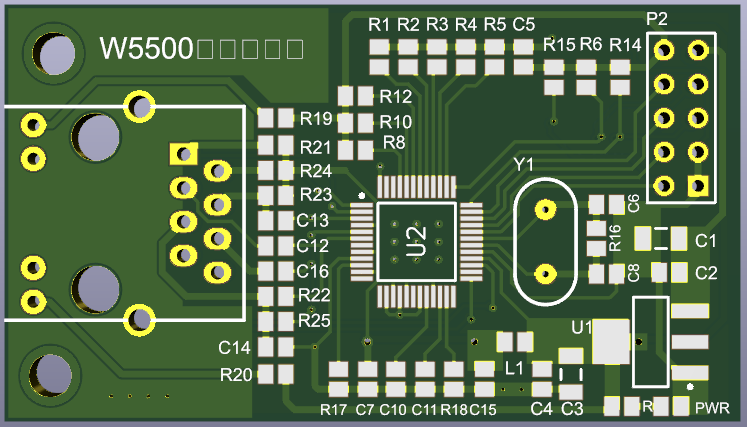

4️⃣ 3D 效果图

RJ45 接口采用垂直安装方式,利于外壳预留窗口。

模块整体布局紧凑,电源与高速区分离,信号走线平衡,适用于教学、实验与工业嵌入系统。

四、模块主要性能指标与管脚定义

1️⃣ 主要性能指标

项目 | 参数 |

|---|---|

模块类型 | 以太网 SPI 接口模块 |

核心芯片 | WIZnet W5500 |

协议支持 | TCP、UDP、ICMP、IPv4、ARP、IGMP、PPPoE |

通信接口 | SPI(最高 80 MHz) |

缓冲区 | 32 KB (8 Socket 共享) |

网络接口 | RJ45 10/100 Mbps(带变压器与 LED) |

时钟源 | 25 MHz 晶振 |

供电电压 | 3.3 V ± 5% |

工作电流 | 约 180 mA @ 满负载 |

模块尺寸 | 55 mm × 31 mm |

工作温度 | −40 °C ~ 85 °C |

2️⃣ 管脚定义

引脚编号 | 引脚名 | 类型 | 功能描述 |

|---|---|---|---|

1 | 3.3 V | P | 电源输入 |

2 | GND | P | 地 |

3 | SCSn | I | SPI 片选信号 |

4 | SCLK | I | SPI 时钟 |

5 | MISO | O | SPI 主输入从输出 |

6 | MOSI | I | SPI 主输出从输入 |

7 | RSTn | I | 模块复位 |

8 | INTn | O | 中断输出 |

9 | LINKLED | O | 网络连接指示 |

10 | ACTLED | O | 网络活动指示 |

五、板上设置及标识

标记 | 名称 | 默认状态 | 描述 |

|---|---|---|---|

D1 | LINK LED | 绿灯亮 | 表示网络连接正常 |

D2 | ACT LED | 闪烁 | 表示有网络数据传输 |

FB1 | 磁珠 | 安装 | 分离 AVDD / DVDD 供电 |

C27 | 1 nF Y 电容 | 安装 | 机壳地与系统地高频跨接 |

R11 ~ R14 | 49.9 Ω 电阻 | 安装 | 差分线匹配 |

R15 ~ R16 | 75 Ω × 2 + 1 nF / 2 kV | 安装 | Bob-Smith 终端 |

Y1 | 25 MHz 晶振 | 安装 | 系统主时钟 |

J1 | RJ45 | 安装 | 带集成磁性与 LED 接口 |

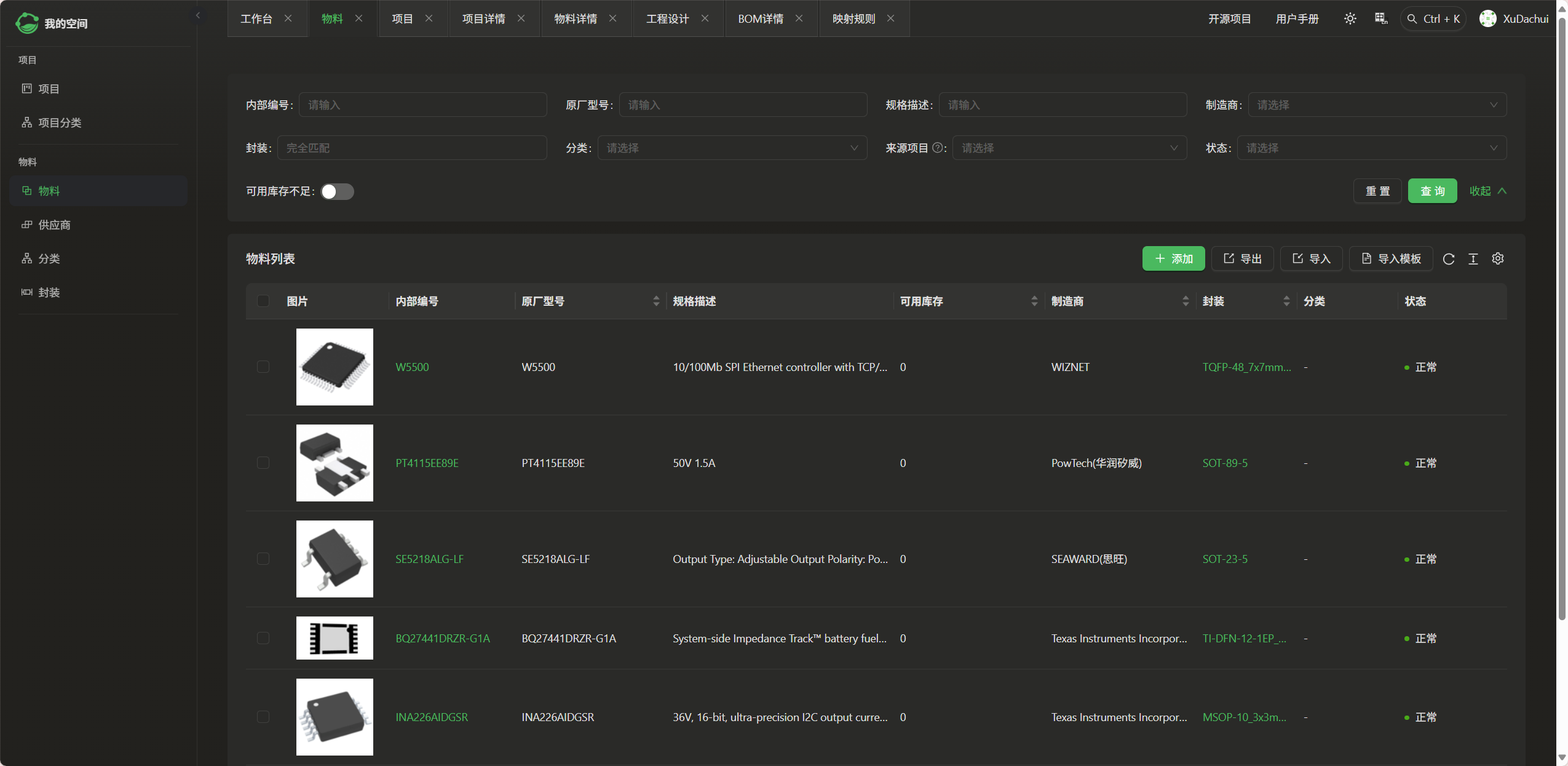

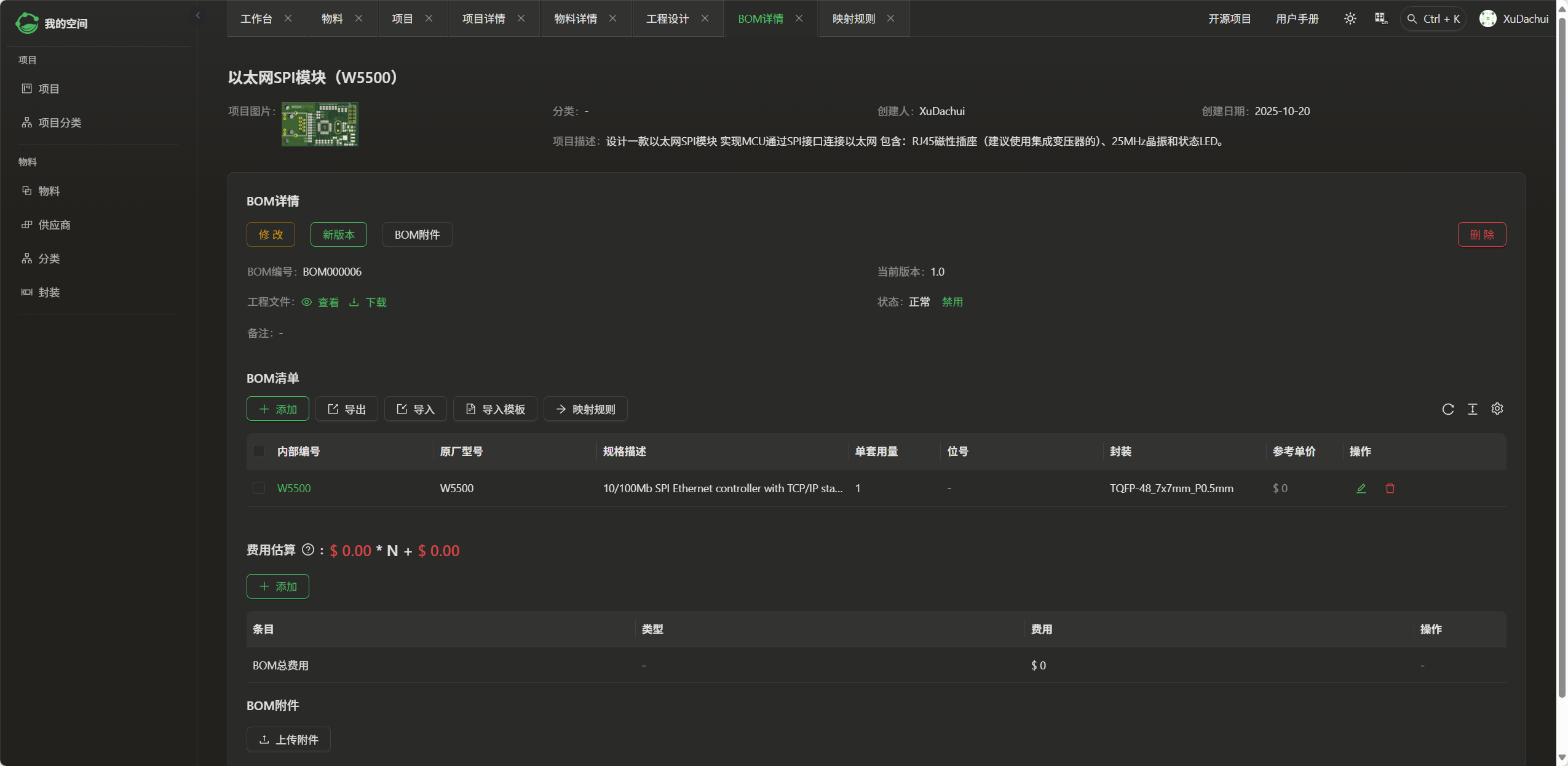

六、eZ-PLM 系统管理截图说明

使用了eZ-PLM系统上传了自己的工程文件,方便保存记录各个版本,也可随时查阅,系统里查阅不到的物料也支持手动添加。

七、心得体会

通过本次以太网 SPI 模块设计,我系统掌握了 W5500 芯片的外围电路结构和高速 SPI 布线原则。

在设计中,我重点学习了以下经验:

- 差分阻抗控制:RJ45 与 W5500 间差分线保持 100 Ω 阻抗、等长、同层;

- 机壳地隔离:RJ45 金属外壳采用独立 Chassis GND,有效抑制 EMI 干扰;

- 电源净化:采用 磁珠+多级去耦电容 为 AVDD 提供低噪声电源;

- 模块化封装:标准 2×5 SPI 接口便于与 STM32、ESP32 等主控配合使用。