消抖

翻译自:Debouncer

我们将一个开关连接到FPGA上,连接方式如下图:

机械开关的问题就是有抖动,每次按一下开关,你会得到下面的信号:

机械开关的问题就是有抖动,每次按一下开关,你会得到下面的信号:

这种信号很少碰到,多数情况是下面的这种:

这种信号很少碰到,多数情况是下面的这种:

我们可以用FPGA的计数器来记录按键的次数,并通过数码管显示出来:

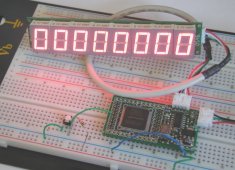

上电的时候,一起是好的:

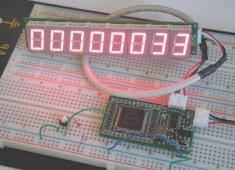

如果按十次键,得到下面的结果:

如果按十次键,得到下面的结果:

显然不对。

显然不对。

那如何解决呢?

一种方式是添加一个R/C滤波器,再跟一个施密特触发器之后送给FPGA,当然还有更简单的方式,就是在FPGA内部进行消抖动。

FPGA擅长简单的运算,让我们使用FPGA中的计数器来查看按下或释放按钮的时间。只有当计数器达到最大值时,我们才确定按钮已经改变了状态。

PB是按钮信号(在本例中为低电平有效)。它可能包含毛刺,并且对任何时钟都是异步的,所以它基本上是不可用的。我们将使PB与时钟(本例中为20MHz)同步,然后创建三个无毛刺、与时钟同步的按钮输出。每个输出都将是高电平有效的,并指示按钮的不同状态(按钮状态,刚刚按下,刚刚释放)。

module PushButton_Debouncer( input clk, input PB, // "PB" is the glitchy, asynchronous to clk, active low push-button signal // from which we make three outputs, all synchronous to the clock output reg PB_state, // 1 as long as the push-button is active (down) output PB_down, // 1 for one clock cycle when the push-button goes down (i.e. just pushed) output PB_up // 1 for one clock cycle when the push-button goes up (i.e. just released) ); // First use two flip-flops to synchronize the PB signal the "clk" clock domain reg PB_sync_0; always @(posedge clk) PB_sync_0 <= ~PB; // invert PB to make PB_sync_0 active high reg PB_sync_1; always @(posedge clk) PB_sync_1 <= PB_sync_0; // Next declare a 16-bits counter reg [15:0] PB_cnt; // When the push-button is pushed or released, we increment the counter // The counter has to be maxed out before we decide that the push-button state has changed wire PB_idle = (PB_state==PB_sync_1); wire PB_cnt_max = &PB_cnt; // true when all bits of PB_cnt are 1's always @(posedge clk) if(PB_idle) PB_cnt <= 0; // nothing's going on else begin PB_cnt <= PB_cnt + 16'd1; // something's going on, increment the counter if(PB_cnt_max) PB_state <= ~PB_state; // if the counter is maxed out, PB changed! end assign PB_down = ~PB_idle & PB_cnt_max & ~PB_state; assign PB_up = ~PB_idle & PB_cnt_max & PB_state; endmodule

我们使用了一个16位计数器。如果使用20MHz的系统时钟,则需要3ms才能达到最大值。从用户的角度来看,3ms是很短暂的,但毛刺已经消失了。根据你的按钮的毛刺程度和你的系统时钟速度,你可能需要调整计数器的宽度。