基于小脚丫FPGA的综合技能训练平台

1 平台简介:

- 能够通过R-2R阶梯网络生成0 - 2MHz的任意波形,包括正弦波、三角波、锯齿波、方波等,信号幅度为3Vpp;

- 能够通过PWM生成0-20KHz的任意波形;

- 能够采集温度传感器的数据并显示出来

- OLED显示;

- 单路串行ADC;

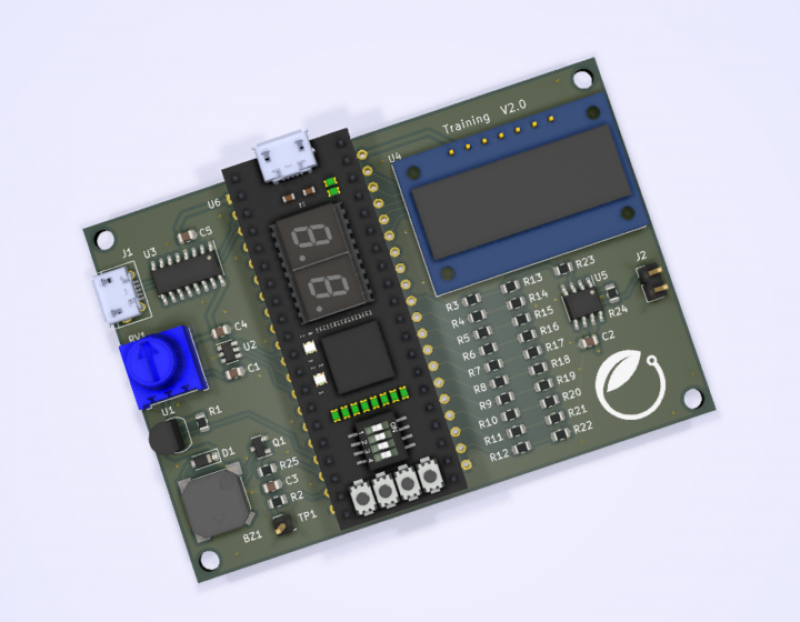

基于小脚丫FPGA的综合技能训练板3D效果图

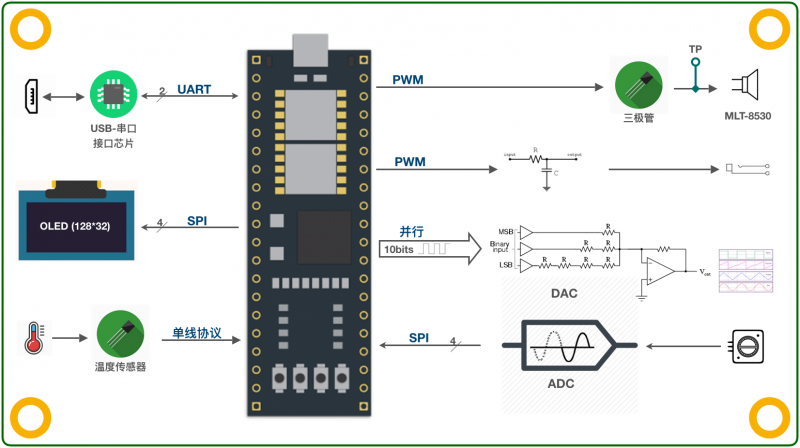

基于小脚丫FPGA的综合技能训练板的功能框图

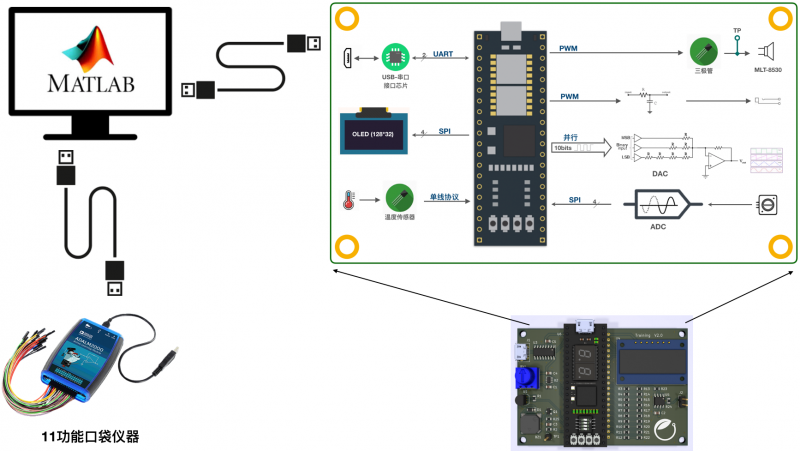

基于小脚丫FPGA的综合训练口袋实验系统沟通

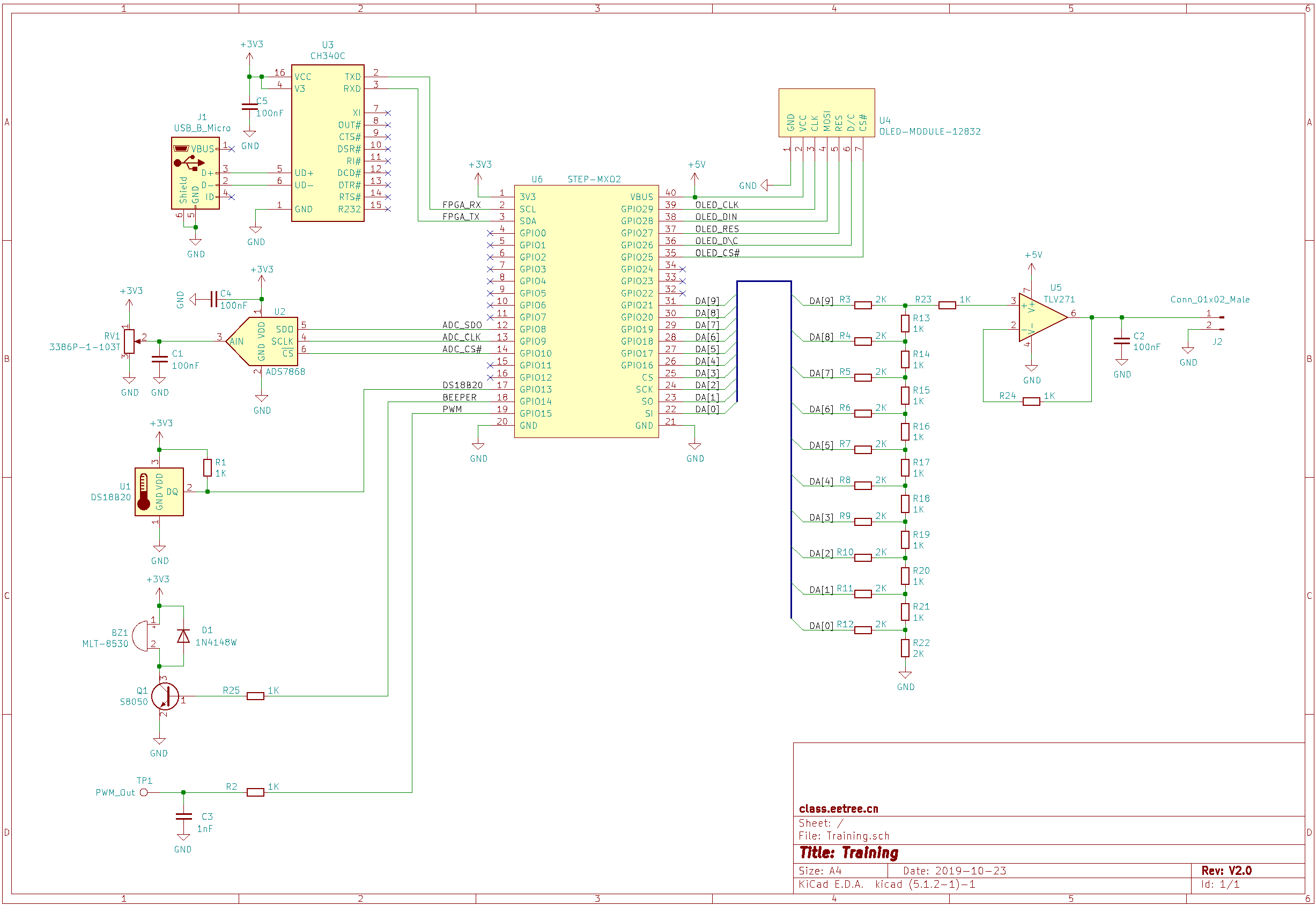

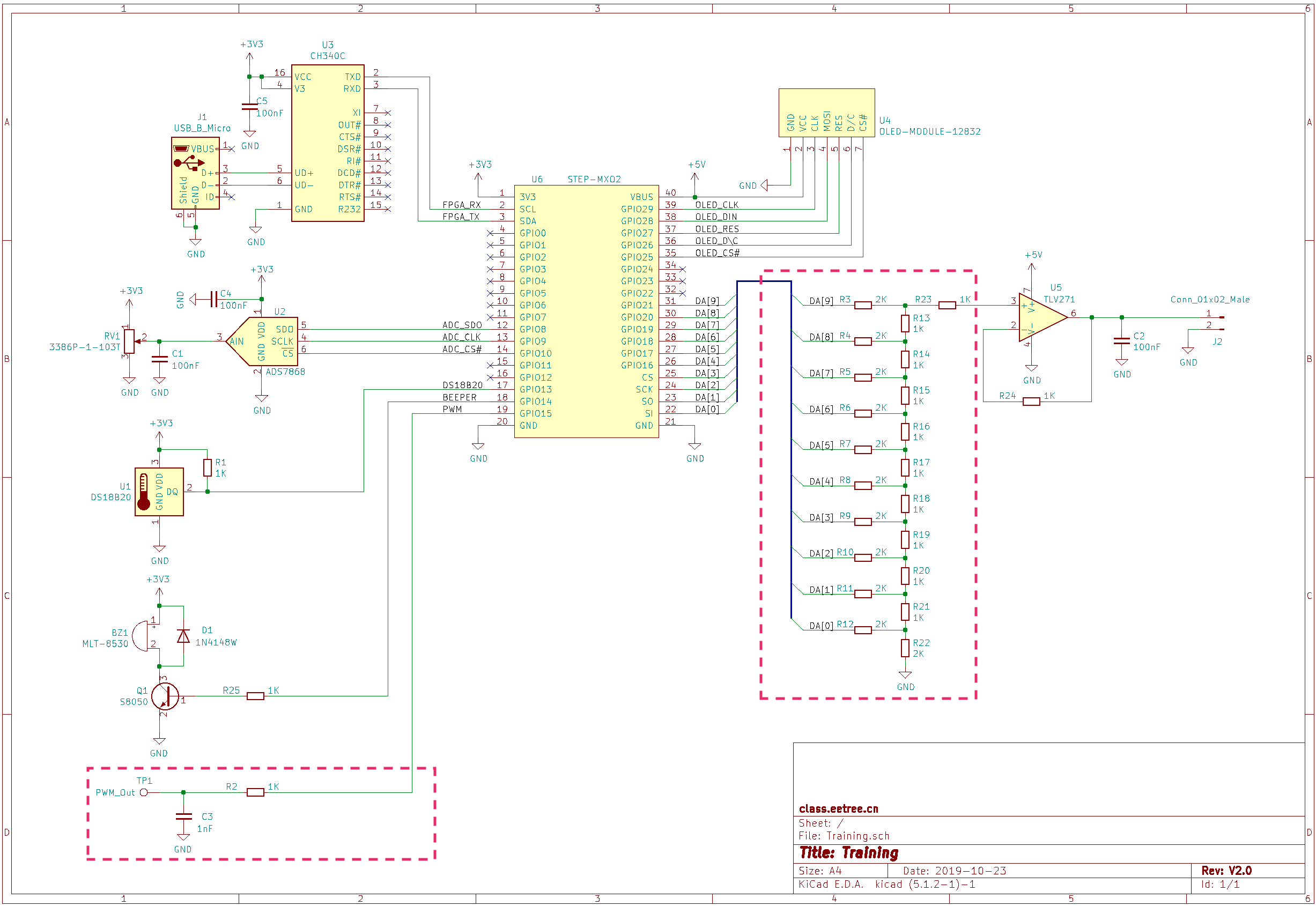

2 原理图

3 用于DDS信号源的DAC

在本平台上有两种方式可以实现DAC的功能,见图中红色虚线标记的部分。

综合技能训练板上的DAC功能

- 由R-2R构成的高速10位并行DAC - 上图中右侧红色虚线的部分

- 由PWM构成的简易DAC - 上图中左侧红色虚线的部分, 关于PWM的使用方法可以参见pwm_verilog中的详细介绍以及相关的技术文章。

4 FPGA编程的管脚分配文件

1 使用基于Lattice XO2-4000HC的小脚丫FPGA, 使用diamond工具

| FPGA管脚 | 小脚丫FPGA模块的管脚 | DAC的数据位 |

|---|---|---|

| C1 | x | ClkIn |

| J13 | Pin 31 | DA[9] |

| J14 | Pin 30 | DA[8] |

| K12 | Pin 29 | DA[7] |

| K14 | Pin 28 | DA[6] |

| K13 | Pin 27 | DA[5] |

| J12 | Pin 26 | DA[4] |

| P3 | Pin 25 | DA[3] |

| M4 | Pin 24 | DA[2] |

| N4 | Pin 23 | DA[1] |

| P13 | Pin 22 | DA[0] |

| N8 | Pin 19 | PWM_Out |

| E12 | Pin 39 | OledClk |

| F12 | Pin 38 | OledDin |

| G12 | Pin 37 | OledRes |

| F13 | Pin 36 | OledDc |

| F14 | Pin 35 | OledCs |

| C8 | Pin 2 | UartRx |

| B8 | Pin 3 | UartTx |

| L3 | Pin 12 | AdcSdo |

| N5 | Pin 13 | AdcClk |

| P6 | Pin 14 | AdcCs |

| N7 | Pin 17 | DS18B20 |

| P8 | Pin 18 | Beeper |

2 基于Intel MAX10M02/08的小脚丫FPGA模块,使用Quartus工具

| FPGA管脚 | 小脚丫FPGA模块的管脚 | DAC的数据位 |

|---|---|---|

| J5 | x | ClkIn |

| B8 | Pin 31 | DA[9] |

| D10 | Pin 30 | DA[8] |

| A9 | Pin 29 | DA[7] |

| A11 | Pin 28 | DA[6] |

| A13 | Pin 27 | DA[5] |

| B11 | Pin 26 | DA[4] |

| A14 | Pin 25 | DA[3] |

| B13 | Pin 24 | DA[2] |

| B14 | Pin 23 | DA[1] |

| B15 | Pin 22 | DA[0] |

| P15 | Pin 19 | PWM_Out |

| B4 | Pin 39 | OledClk |

| A5 | Pin 38 | OledDin |

| A7 | Pin 37 | OledRes |

| B6 | Pin 36 | OledDc |

| E7 | Pin 35 | OledCs |

| M4 | Pin 2 | UartRx |

| P3 | Pin 3 | UartTx |

| P7 | Pin 12 | AdcSdo |

| P8 | Pin 13 | AdcClk |

| P9 | Pin 14 | AdcCs |

| P12 | Pin 17 | DS18B20 |

| R14 | Pin 18 | Beeper |