**这是本文档旧的修订版!**

教程 - DDS信号源的制作

教程中用到的硬件平台

基于FPGA + 高速DAC的DDS AWG任意波形/信号发生器

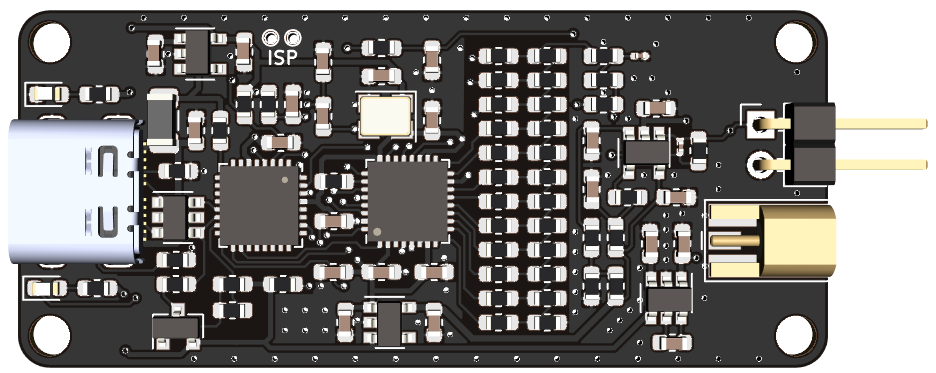

基于FPGA+R-2R DAC的简易信号发生器3D效果图1

教程大纲

- 第1章 - 信号源及电信号的基本特征

- 第2章 - 口袋仪器中的DDS信号源

- 第3章 - DDS构成初体验

- 第4章 - 频域处理

- 第5章 - 输出信号幅度的处理

- 第6章 - DAC的选用及关键指标

- 第7章 - FPGA及其资源的有效利用

- 第8章 - 集成化DDS的使用

- 第9章 - DDS系统设计

- 第10章 - DDS信号源在电赛和通信系统中的应用

知识点短视频

- 关于DDS

- 第1节 - DDS的概念及系统构成

- 什么是DDS?

DDS:Director Digital Synthesis,直接数字合成

是一种用于通过单个固定频率的参考时钟信号生成任意波形的频率合成器 在数字域进行信号处理,生成任意你需要的信号 通过DAC变成电信号 通过模拟信号链路对生成的信号做进一步处理 功能可以超级简单,也可以非常复杂 直流电压生成 调制、测试信号生成 频率和相位都可编程,不需要改变外围器件,全软件控制 幅度、直流偏移、变频等也可以在数字域进行调节,可以省去外部复杂的模拟链路 通过DDS产生三种常用的信号 正弦波:通过查找波表 锯齿波: 相位累加器 方波:相位累加器的最高位 DDS有什么用? 信号分析、测量:信号发生器、函数发生器 AFG - 任意函数发生器 AWG - 任意波形发生器 控制及显示 通信系统:通信系统的本地振荡器、混频器、调制器 语音合成 数字锁相环 DPLL 生物医疗 电源 DDS的优势 数字域几乎无所不能,DDS充分利用了数字信号处理的优势 可以便捷地生成“任意”波形 精细的频率调整分辨率以及更高的频率捷变性能 输出频率切换时可以保证精确的相位控制 比参考源晶振相位噪声小的相位噪声 它是一个前馈系统,所以有很好的近载波相位噪声性能,DDS将参考时钟的相位噪声降低了Fclk/Fo 参考时钟的抖动直接影响了输出信号的抖动,此抖动相对于输出信号的周期比例很小 DDS的最高输出频率为Fclk/2,输出信号的相位噪声永远会比参考时钟信号的相位噪声低至少6dB 在远离载波的频率区间,DDS的相位噪声本地为DAC量化噪声本底和参考时钟相位噪声本底的幂和 要注意DDS存在的问题 NCO位数截断导致的杂波 相位截断误差 相位轮 截断导致的结果 高阶奈奎斯特镜像导致的交互杂散 DAC的性能限制带来的在大的频率偏移情况下比较高的噪声底线 第2节 - DDS的关键指标 Tek仪器的AFG功能介绍 M2K口袋仪器的AWG功能演示 波形 常用波形 任意函数(AFG) 正弦波 - 是否存在失真、非线性、谐波? 方波 - 重复方波脉冲,用作时钟或测试运放的快速转换特性 锯齿波 - 缓慢上升、快速下降,用于控制模拟示波器或电视扫描 三角波 - 上升、下降时间相同 阶梯波 - 从一个电平快速变化到另一个电平 脉冲信号 - 快速上升时间、持续幅度、快速下降 调制波形 模拟调制 数字调制 其它波形 任意波形(AWG) - 一般是包括无法用函数表示的其它波形 模拟信号波形特征 表达式 脉冲信号特征 上升时间: 脉冲边沿从低电平到高电平的时间 下降时间:脉冲边沿从高电平到低电平的时间 脉冲宽度: 脉冲从低到高,再从高到低的时间,以全电压的50%为测量基准 脉冲信号占空比/延时 信号幅度特性 参数 幅度 动态范围 直流偏移 输出阻抗 与幅度测量相关的一些指标 信号时间特性 - 频率 参数 频率范围 频率准确度 频率稳定度 可调频率精度 信号时间特性 - 相位 复合信号 调制波形 模拟调制 数字调制 脉宽调制 正交调制 数字模式和格式 伪随机数据流 DDS在电赛中的应用 第3节 - DDS在信号源类的题目中的应用 产生激励信号: 模拟波形 数字数据模式 调制信号 刻意产生的噪声 作用 检查每一级电路的增益、频率响应,对接收端进行校准 信号源提供用于测试电路的各种波形,一般来讲都是低功率的 验证( Verification) - 分析数字调制 定标(Characterization)- 测试D/A和A/D转换器 压力/临界点 测试 - 通信接收机的压力测试 第4节 - DDS在电路特性分析类题目中的应用 信号时域响应举例 频域响应 第5节 - DDS在通信/高频电路类题目中的应用 第6节 - DDS在开关电源类题目中的应用 DDS的频谱处理 第7节 - DDS系统的频谱含量及分析工具 DDS的输出频谱成分 DDS系统构成 频谱含量 合成信号及混叠 公式 杂散 相位截断 有限幅度分辨率 信号电平/量化噪声功率比SQR = 1.76 + 6.02B(dB) 时钟抖动 谐波失真 DAC谐波 谐波的幅度主要取决于输出频率与时钟频率的比值 DAC量化噪声的频谱成分会随着该比值的变化而变化 运放谐波 改变频率的方法 改变相位控制字 改变主频率 无法做到“任意频率” 无法去除干扰频率 第8节 - DDS系统的频谱处理及利用 频谱构成 镜像 杂波 非线性 有效信息的提取 滤波器 低通 带通 高通 镜像信号的巧妙利用 变频 第9节 - 模拟滤波器的设计及工具 滤波器的类型及设计工具 对滤波器的要求 理性的滤波器:带内衰减为零,带外抑制度最高,线性相移 实际的效果 滤波器的关键指标 幅度 相位 截止频率:DAC转换频率的40% 带外抑制度:尽可能高 带内平坦度:带内波动尽可能小 相位移动:线性 常用的滤波器类型、构成及对比 有源 无源 常用的无源滤波器类型及构成方式 特性对比 效果举例 设计工具 免费使用的一些滤波器设计工具 仿真工具 - LTSpice Mathworks的Matlab Keysight的ADS TI的Webench NI的MultiSim ADI的设计工具 DDS仿真工具 有缘滤波器设计工具 用ADI的Filter Wizard设计低通滤波器举例 常用口袋仪器中的滤波器简易实现方式 ADI的M2k 仿真结果 NI的AD2 参考文档 关于滤波器的一些基本概念(英文) 滤波器设计资源 DDS信号发生器中常用到的滤波器参数 FPGA构成DDS 第10节 函数生成 - 方波/锯齿波/三角波 Verilog生成模拟直流 D9-D0设定为固定值:1023对应于3.3V Verilog生成模拟方波 D9-D0设定为计数器的某一bit Verilog生成模拟锯齿波 累加器生成三角波 Verilog生成模拟三角波 锯齿波折叠 Verilog生成数字方波 取计数器/相位累加器中的一位 正弦波生成 第11节 - 逻辑构成波表 生成正弦波波表的机制 时间分辨率 - 多少个点?- 512个点 幅度分辨率 - 每个点需要多少位?- 10位 生成波表的方式举例 - xls 1/4周期波形的使用 第12节 - ROM配置波表 FPGA内部的块RAM的使用 - IP核的例化及使用 例化ROM 正弦波表的填写和调用 第13节 - NCO内核 第14节 - SINE/COSE内核 第15节 - 任意频率生成 任意频率 - 相位累加器/可调频率的精度 相位截断 任意频率 实时改变频率 输出波形验证 第16节 - 关于DDS的时钟及时序关系 第17节 - 任意波形生成 生成任意波形 调制波形 FSK、BPSK 手绘波形 各种噪声 Matlab产生并传输系统演示 第18节 - 幅度及直流偏移的调整 要求 幅度可调范围 - dB 直流偏移 可以调整幅度的几个环节 幅度的调整 可变增益放大器 - VCA dB/V线性 改变DAC的参考电流 - 4x ~ 10x 高分辨率DAC + 数字处理方式 直流偏移的调整 宽带运算放大器 直流电压生成 PWM + RC 串行DAC 几款口袋仪器的指标 ADI的M2k & Digilent的AD2 采用12bit 高速DAC - AD9963 幅度可调范围:+/-5mV ~ +/-5V 直流偏移范围:-5V ~ +5V 采用的方案 DAC的基准电流:1mA ~4mA Digilent的AD2 采用14bit的高速DAC - AD9717 幅度可调范围:~ +/-5V 直流偏移范围:-5V ~ +5V 采用的方案 DAC的基准电流1mA ~4mA 开关切换电路 运放部分电路 Digilent的OpenScope 采用10bit R-2R DAC 幅度可调范围:+/-50mV ~ +/-1.5V 直流偏移范围:-1.5V ~ +1.5V 采用的方案 Tek的混合域示波器的AWG 20mVpp ~ 5Vpp 系统设计 拓扑结构 成本考虑 DAC的位数 供电电压 DAC的选用 第20节 - 高速并行DAC的使用 DAC的关键指标 转换率 分辨率 时钟 接口方式 基准源 供电电压 通道数 主要供应商 Analog Devices Texas Instruments Maxim Integrated 常用型号(100Msps/10bits以上) 第21节 - R2R电路的使用 构成原理 使用场景 能够产生20MHz的模拟信号 优缺点 只需要两种阻值的电阻,且不需要电阻值非常精确 生产起来方便、成本极低 第22节 - 串行接口DAC、(SPI)、时序关系 接口方式 SPI 最高50MHz 3Msps I2C 时序关系 主时钟:Hz 转换率:SPS 生成信号的频率:Hz 常用器件 DAC7612:双通道、12位、单电源、轨到轨输出 第23节 - 用PWM构成DAC 构成原理 产生100KHz以内的模拟信号 20KHz正弦波波形 20kHz正弦波频谱(96MHz主频) PWM方式 R-2R方式 优缺点 超级简单,对于DC-低频的信号非常方便 使用FPGA可以达到比较高的输出频率 上限频率取决于主时钟和分辨率 相关文章 漫谈“独臂神通”PWM(1):用1根管脚、1个电阻和1个电容实现DAC 漫谈“独臂神通”PWM(2):DAC的低通滤波器设计 专用DDS芯片 第24节 - 功能构成及选型 ADI器件系列选型 ADI直接数字合成器件选型页面 DDS 波形发生器 特殊功能应用 DDS设计界面 ADIsimDDS 第25节 - 控制接口 - SPI 第26节 - 外围电路 第27节 - 专用DDS芯片AD9837及使用 AD9837/AD9838/AD9833/AD9834:低功耗、2.3 V至5.5 V可编程波形发生器 AD9837: 8.5mW 芯片特性: 数字可编程频率和相位 功耗:8.5 mW(2.3 V时) MCLK速率:16 MHz(B级),5 MHz(A级) 28位分辨率:0.06 Hz(16 MHz参考时钟) 正弦波/三角波/方波输出 2.3 V至5.5 V电源供电 三线式SPI接口 扩展温度范围:–40°C至+125°C 关断选项 10引脚LFCSP封装 应用场景: 频率激励/波形发生 液体和气流测量 传感器应用:接近度、运动和缺陷检测 线路损耗/衰减 测试与医疗设备 扫描/时钟发生器 时域反射(TDR)应用 模块图片 模块框图 原理图 第28节 - 专用DDS/AWG芯片AD9102及使用 AD9102/6:低功耗、14位、180MSPS、数模转换器和波形发生器 特性 片内4,096 x 14位模式存储器 片内DDS 3.3 V、4 mA输出时功耗: 96.5 mW @ 180 MSPS 休眠模式: < 5 mW @ 3.3 V 电源电压:1.8 V至3.3 V SFDR至奈奎斯特频率: 87 dBc(10 MHz输出) 相位噪声(1 kHz偏移、 180 MSPS、8 mA):-150 dBc/Hz 差分电流输出: 8 mA(最大值,3.3 V) 小尺寸、32引脚5mm x 5mm LFCSP无铅封装,3.6 mm × 3.6 mm裸露焊盘 应用: 医疗仪器 便携式仪器 信号发生器、任意波形发生器 汽车雷达 模块 3D图片 原理图 单片机实现DDS功能 第29节 - 串行DAC 第30节 - 定时器 + PWM + LPF