**这是本文档旧的修订版!**

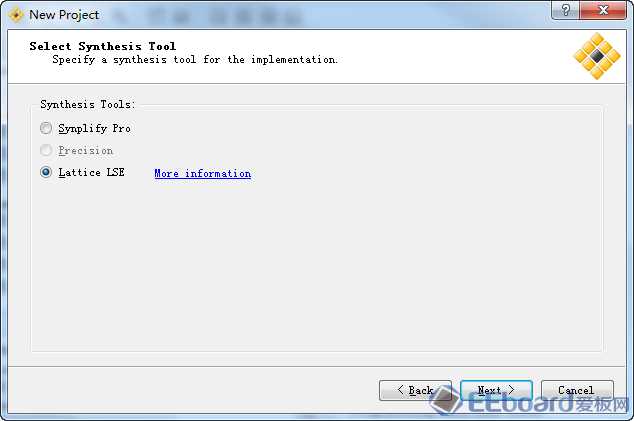

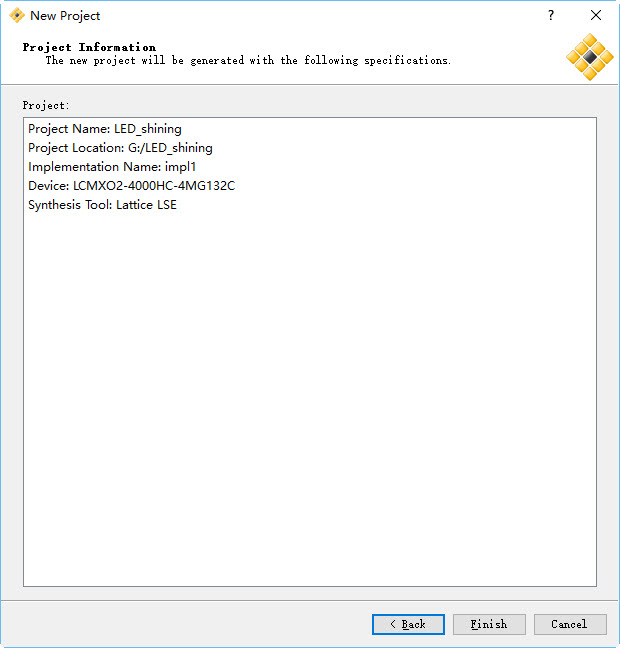

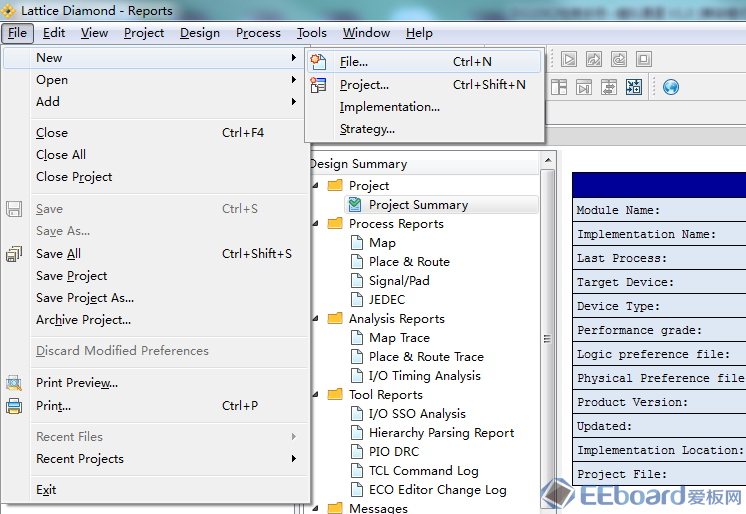

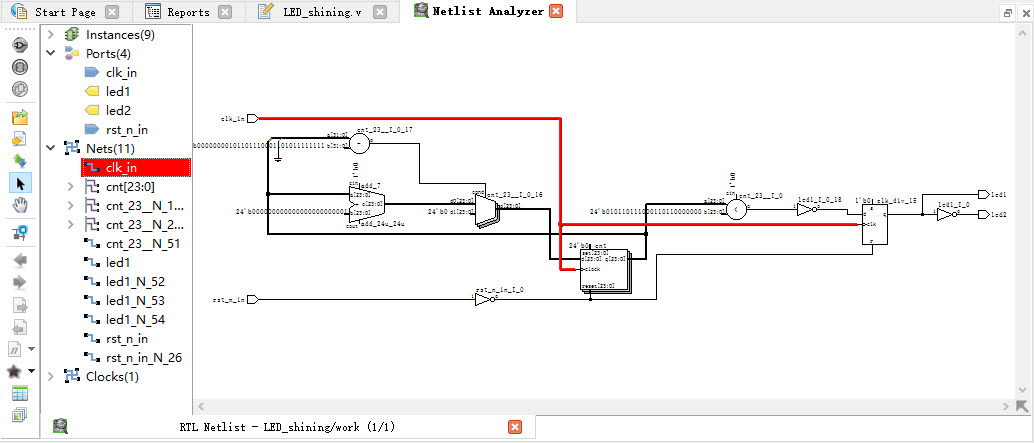

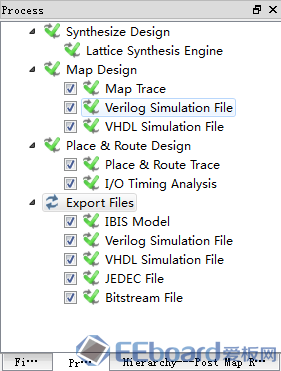

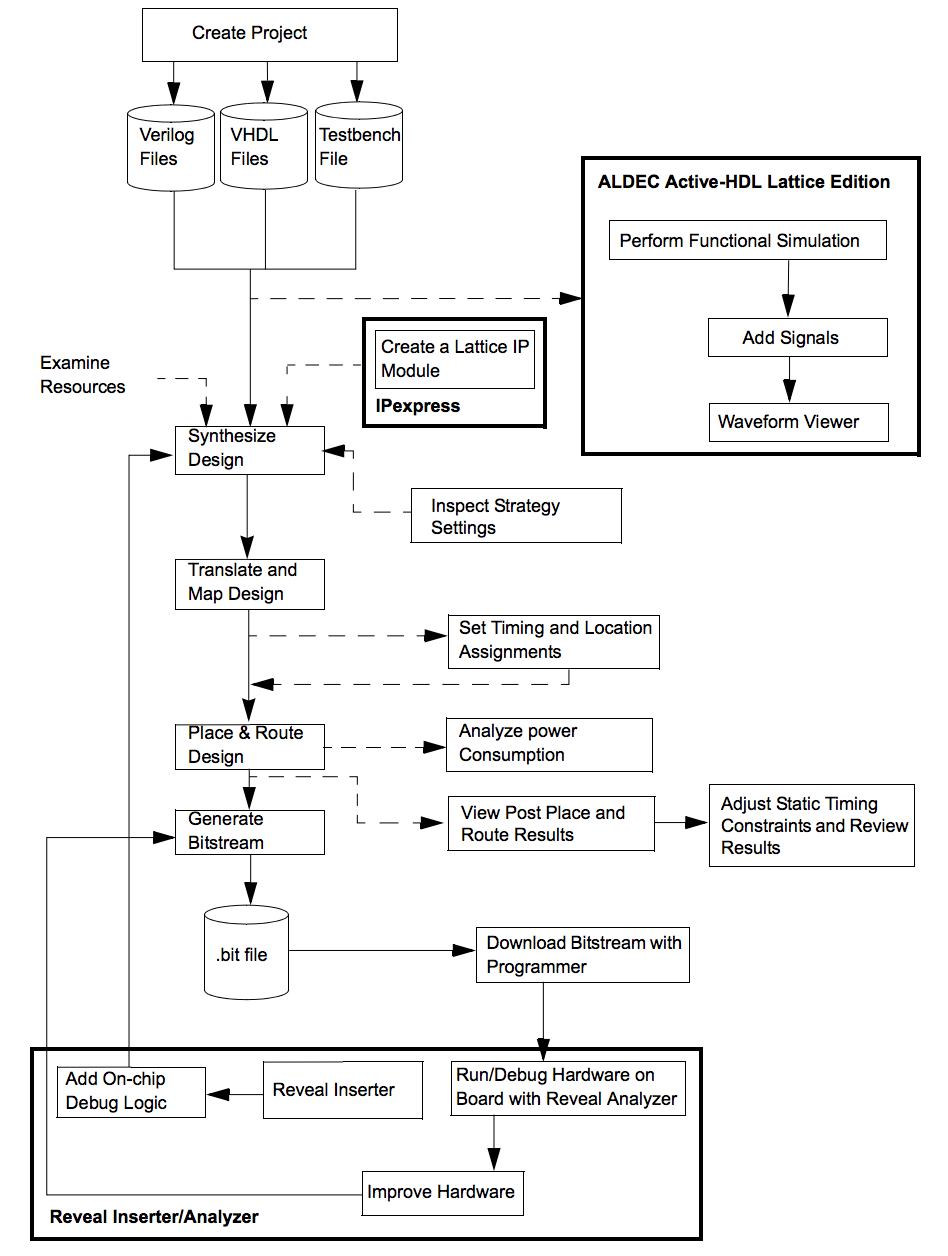

Diamond安装好,我们就可以使用Diamond软件开始FPGA的设计了,整个设计流程参照下图。

采用Diamond设计FPGA逻辑的基本流程

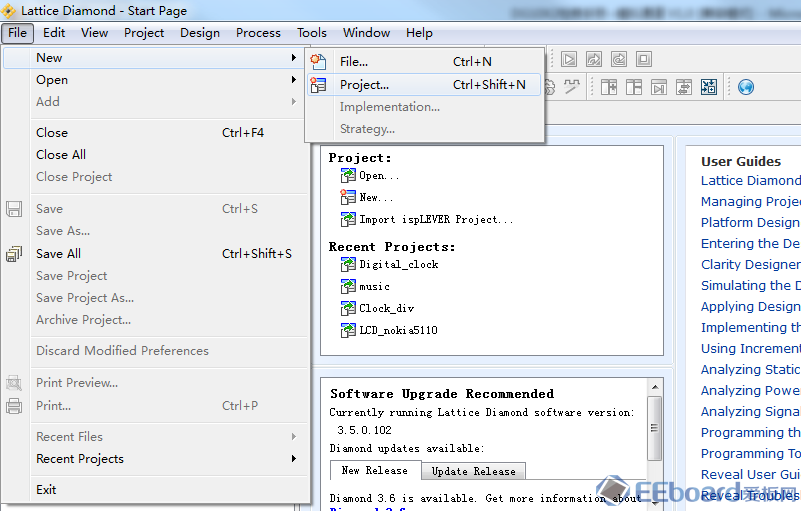

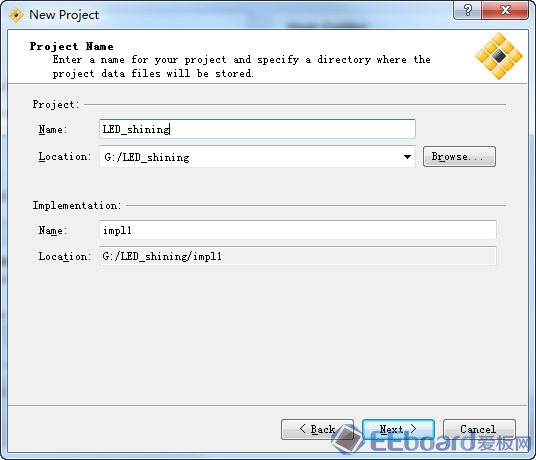

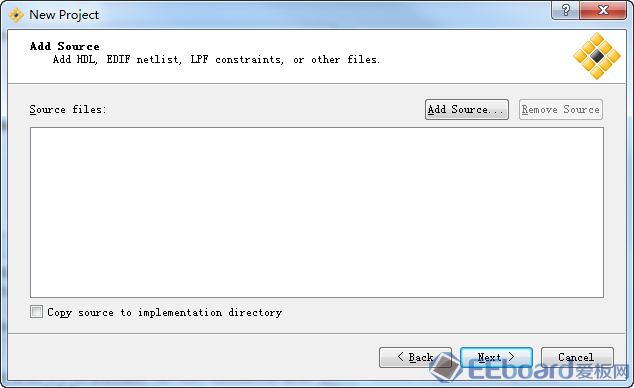

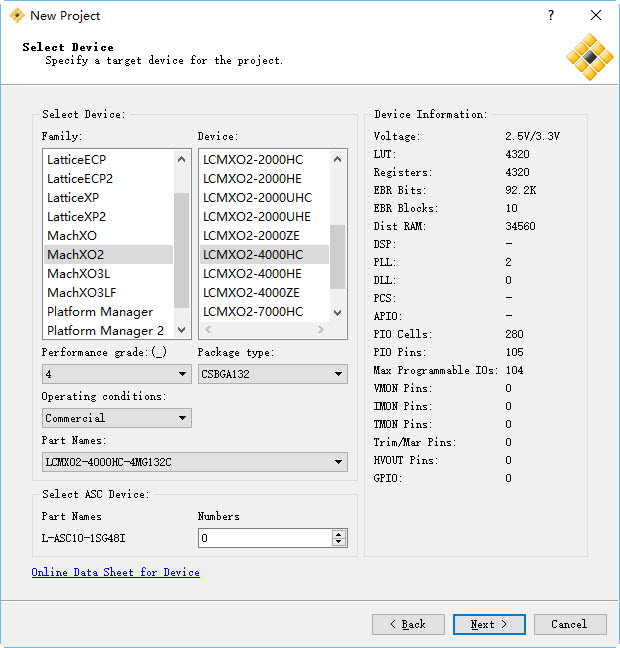

1 运行第一个例程

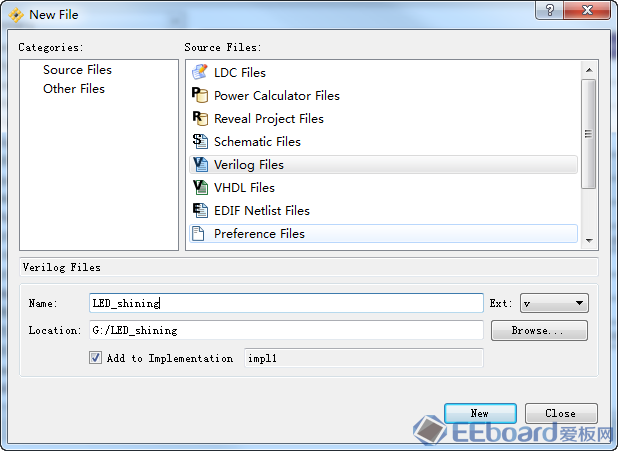

下面我们可以开始可编程逻辑的开发,我们以控制LED交替闪烁为例,完成自己的第一个程序:

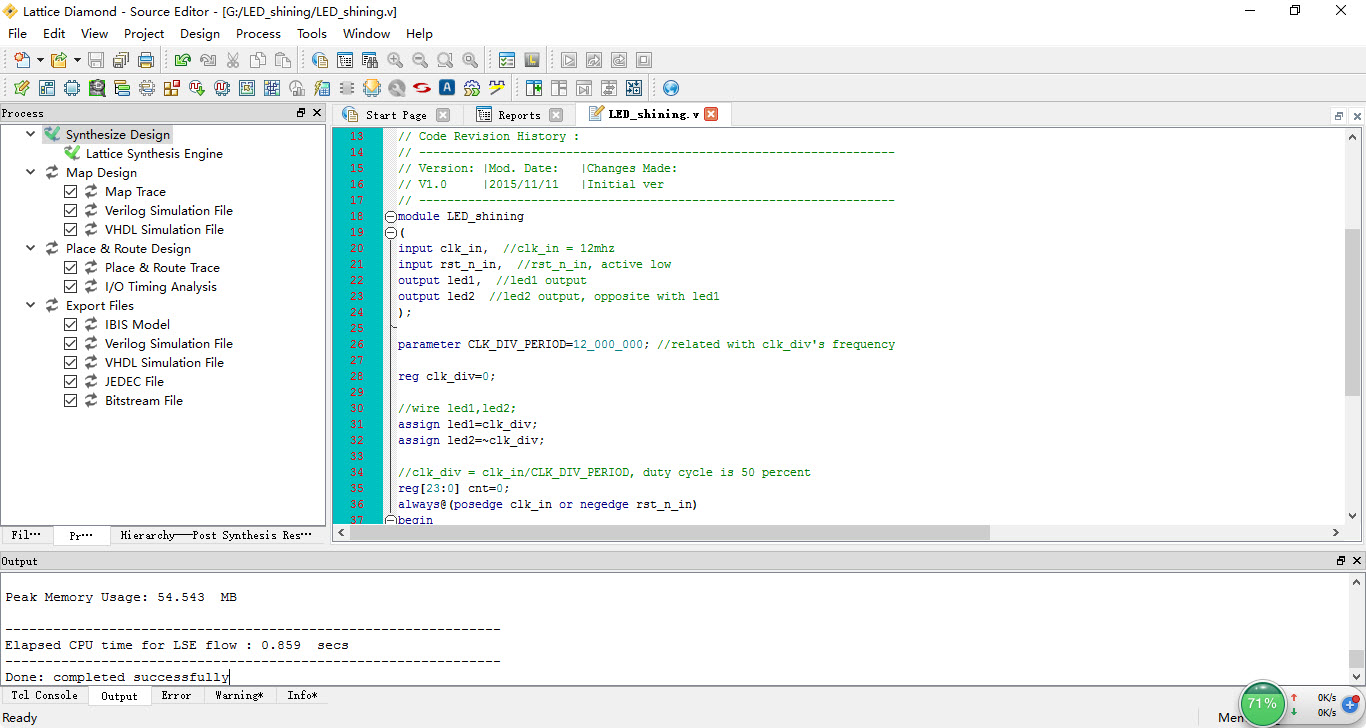

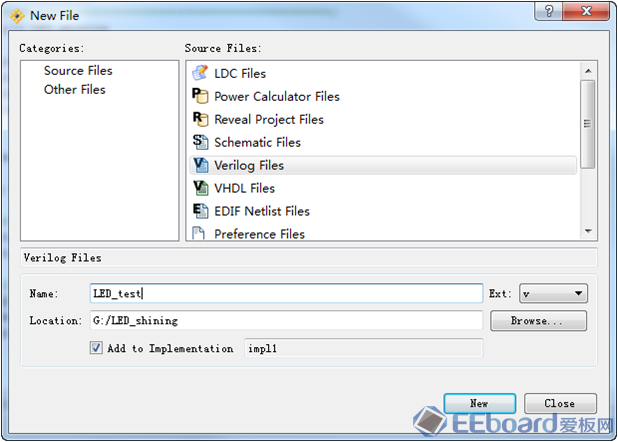

- 程序源码已经准备好,如下,将代码复制到设计文件LEDshining.v中,并保存。<code verilog> ——————————————————————– »»»»»»»»»»»»> COPYRIGHT NOTICE ««««««««««««< ——————————————————————– Module: LEDshining

Author: Step Description: LEDshining Web: www.ecbcamp.com ——————————————————————– Code Revision History : ——————————————————————– Version: |Mod. Date: |Changes Made: V1.0 |2015/11/11 |Initial ver ——————————————————————– module LEDshining ( input clkin, clkin = 12mhz input rstnin, rst_n_in, active low output led1, led1 output output led2 led2 output, opposite with led1 ); parameter CLKDIVPERIOD=12000000; related with clk_div's frequency

reg clk_div=0;

wire led1,led2; assign led1=clkdiv; assign led2=~clkdiv; clkdiv = clkin/CLKDIVPERIOD, duty cycle is 50 percent reg[23:0] cnt=0; always@(posedge clkin or negedge rstnin) begin if(!rstnin) begin cnt⇐0; clkdiv⇐0;

end else begin if(cnt==(CLK_DIV_PERIOD-1)) cnt<=0; else cnt<=cnt+1'b1; if(cnt<(CLK_DIV_PERIOD>>1)) clk_div<=0; else clk_div<=1; end

end

endmodule

</code>

到这里完成了第一个程序流文件的生成,下面可以下载到FPGA中。

2 工程仿真

上面我们走了整个工程开发的过程,例程较为简单,对于复杂的工程开发需要预仿真和后仿真等,保证最终的程序设计逻辑和时序符合我们的设计要求。 仿真软件很多,这里我们使用软件自带的Active-HDL软件进行仿真:

- 测试源码如下,复制到LEDtest.v文件并保存,为了方便仿真,我们在LEDtest.v调用LEDshining模块时将CLKDIVPERIOD重新赋值为20:<code verilog> ——————————————————————– »»»»»»»»»»»»> COPYRIGHT NOTICE ««««««««««««< ——————————————————————– Module: LEDtest

Author: Step

Description: Testbench for LED_shining

Web: www.ecbcamp.com

——————————————————————–

Code Revision History :

——————————————————————–

Version: |Mod. Date: |Changes Made:

V1.0 |2015/11/11 |Initial ver

——————————————————————–

`timescale 1ns / 100ps

module LED_test;

parameter CLKPERIOD = 40; CLKPERIOD=40ns, Frequency=12MHz

parameter CLKDIVPERIOD=20; related with clk_div's frequency

reg sysclk;

initial

sysclk = 1'b0;

always

sysclk = #(CLKPERIOD/2) ~sys_clk;

reg sysrstn; active low

initial

begin

sysrstn = 1'b0;

#100;

sysrst_n = 1'b1;

end

wire led1,led2;

LEDshining #

(.CLKDIVPERIOD(CLKDIVPERIOD))

LEDshininguut

(

.clkin(sysclk), clkin = 12mhz

.rstnin(sysrstn), rst_n_in, active low

.led1(led1), led1 output

.led2(led2) led2 output, opposite with led1

);

endmodule

</code>

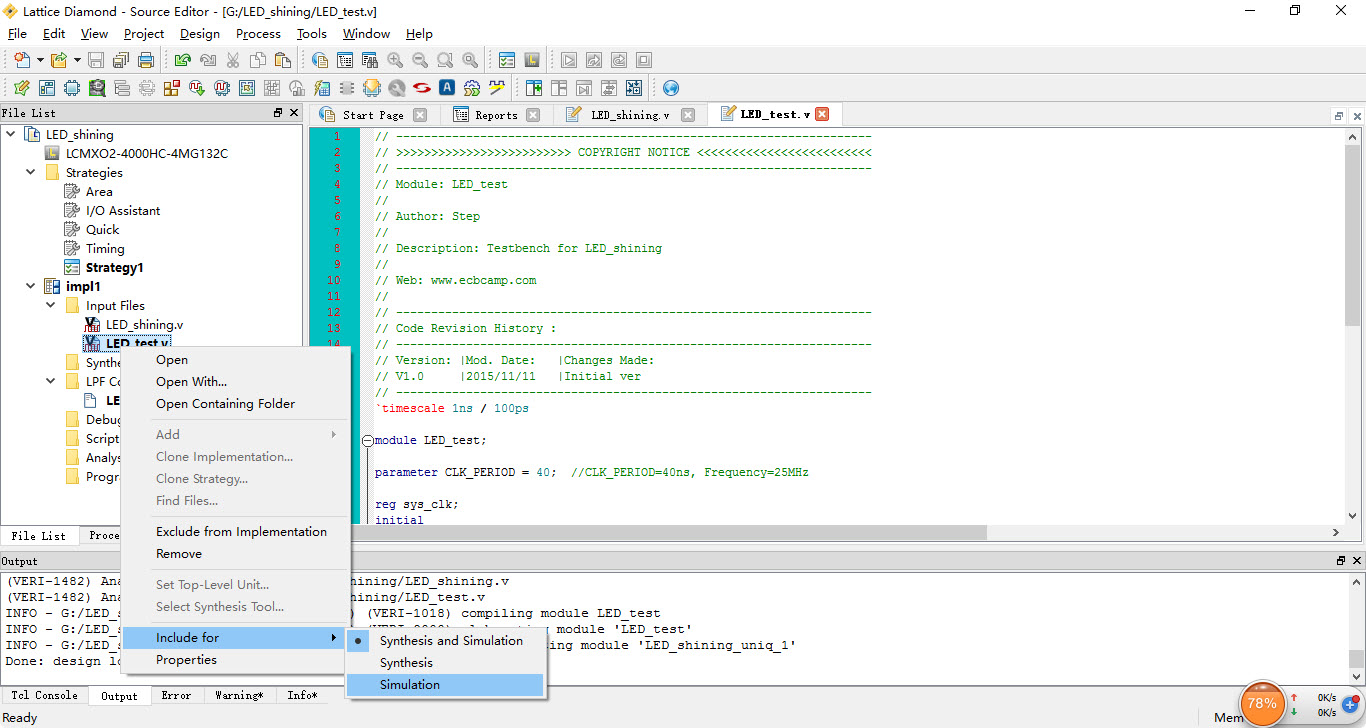

- 然后在软件左侧Process栏,选择File List,找到LEDtest.v,点击右键,选择Include for →Simulation  - 准备工作完成,我们选择Tools →SimulationWizard →Next,

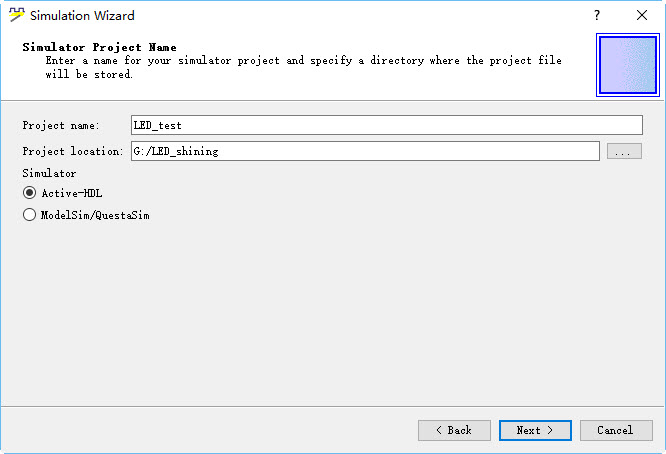

- 建立仿真工程,ModelSim和QuestaSim需要自行安装并与Diamond关联,才能直接调用,这里我们选择Active-HDL(默认),工程名称:LEDtest,工程路径默认即可:然后点击Next,

- 准备工作完成,我们选择Tools →SimulationWizard →Next,

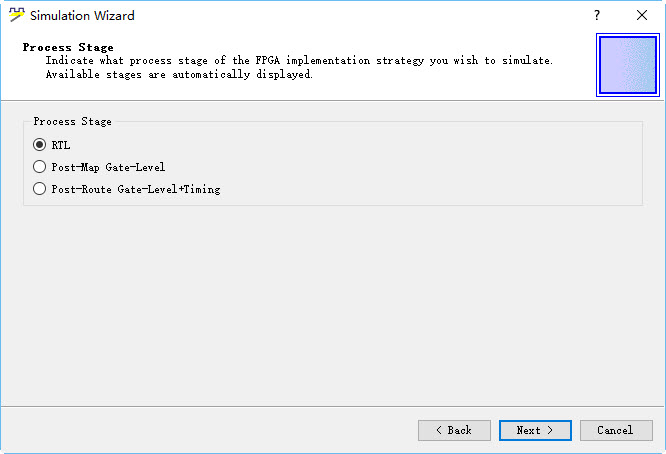

- 建立仿真工程,ModelSim和QuestaSim需要自行安装并与Diamond关联,才能直接调用,这里我们选择Active-HDL(默认),工程名称:LEDtest,工程路径默认即可:然后点击Next, - 选择RTL,然后Next

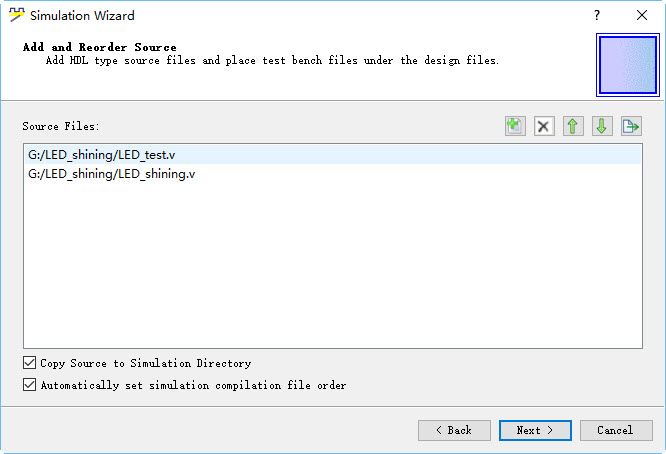

- 选择RTL,然后Next - 勾选Copy Source toSimulation Directory,然后Next

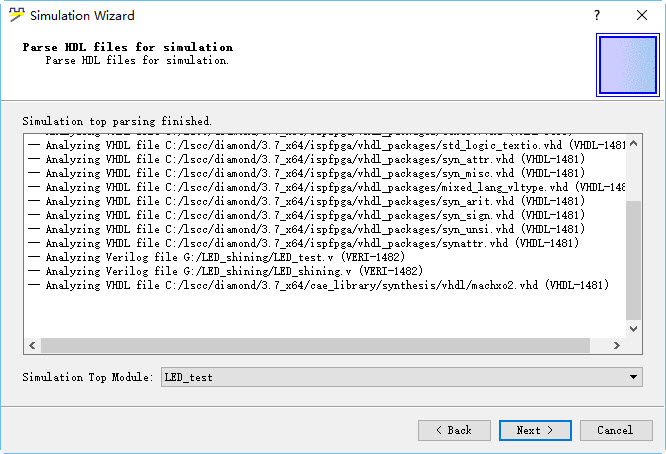

- 勾选Copy Source toSimulation Directory,然后Next - 点击Next

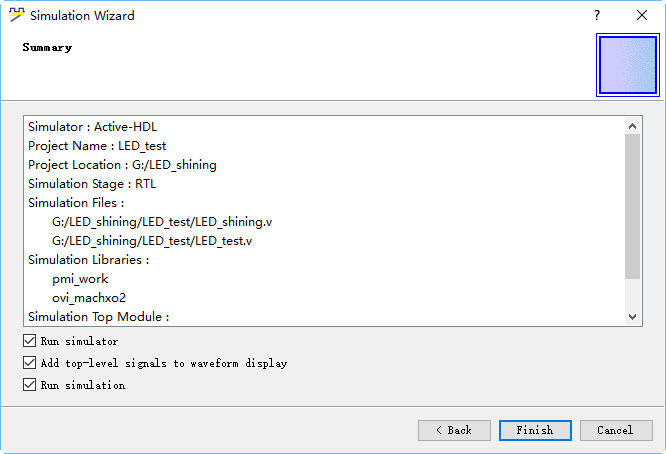

- 点击Next - 点击Finish,等待仿真软件的自动运行并显示仿真时序

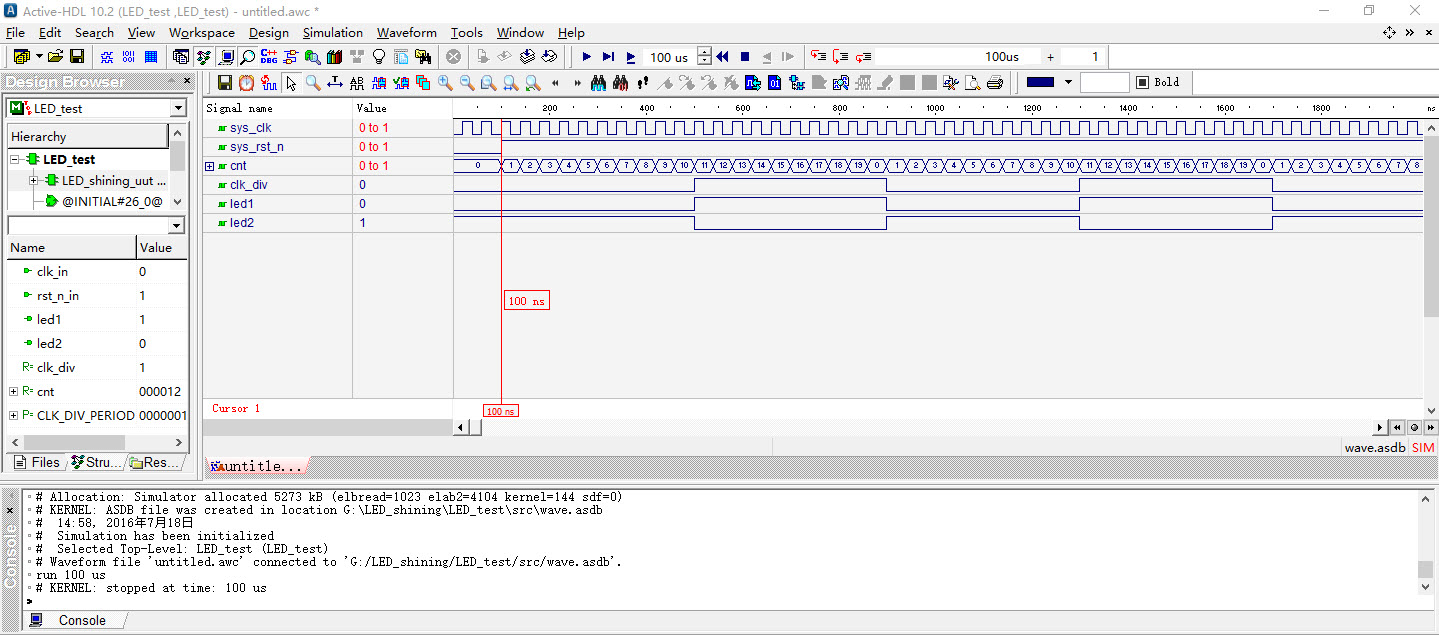

- 点击Finish,等待仿真软件的自动运行并显示仿真时序 - 查看仿真结果

- 查看仿真结果 === 3 下载程序到FPGA ===

Step FPGA V2.1的编程芯片已经集成到小脚丫开发板上,因此只需要一根Micro USB线和电脑相连,就可以完成供电和编程的功能,驱动安装好以后就可以开始编译下载程序了。

将编译完成的程序加载到Step FPGA开发板:

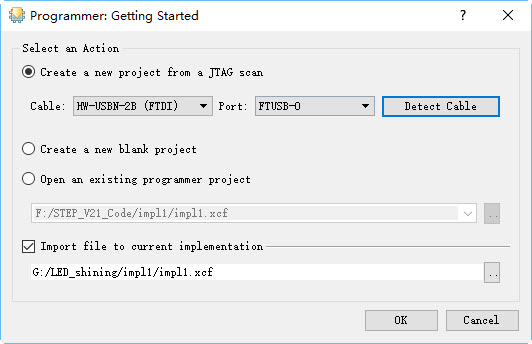

- 选择Tools →Programmer,选择下载器HW-USBN-2B(FTDI),然后点击OK,

=== 3 下载程序到FPGA ===

Step FPGA V2.1的编程芯片已经集成到小脚丫开发板上,因此只需要一根Micro USB线和电脑相连,就可以完成供电和编程的功能,驱动安装好以后就可以开始编译下载程序了。

将编译完成的程序加载到Step FPGA开发板:

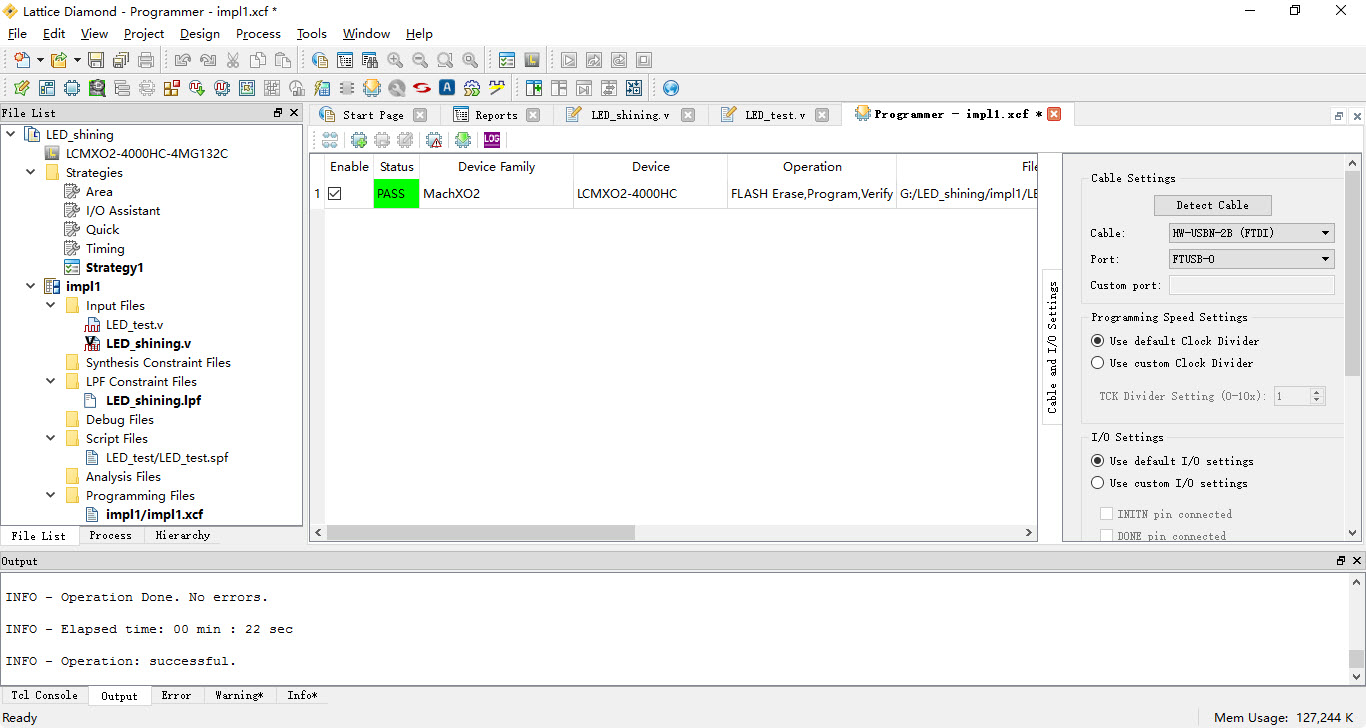

- 选择Tools →Programmer,选择下载器HW-USBN-2B(FTDI),然后点击OK, - 进入Programmer界面

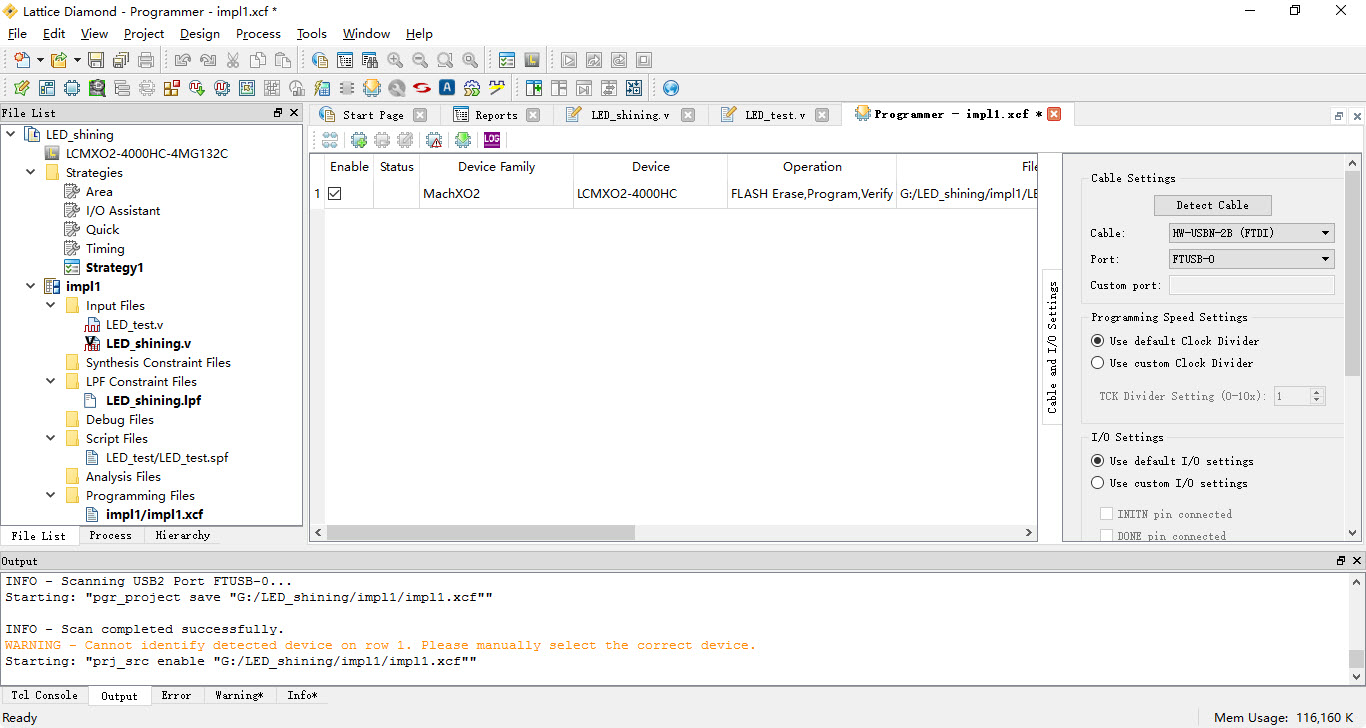

- 进入Programmer界面 - 将Step FPGA开发板、下载器和电脑连接,如图

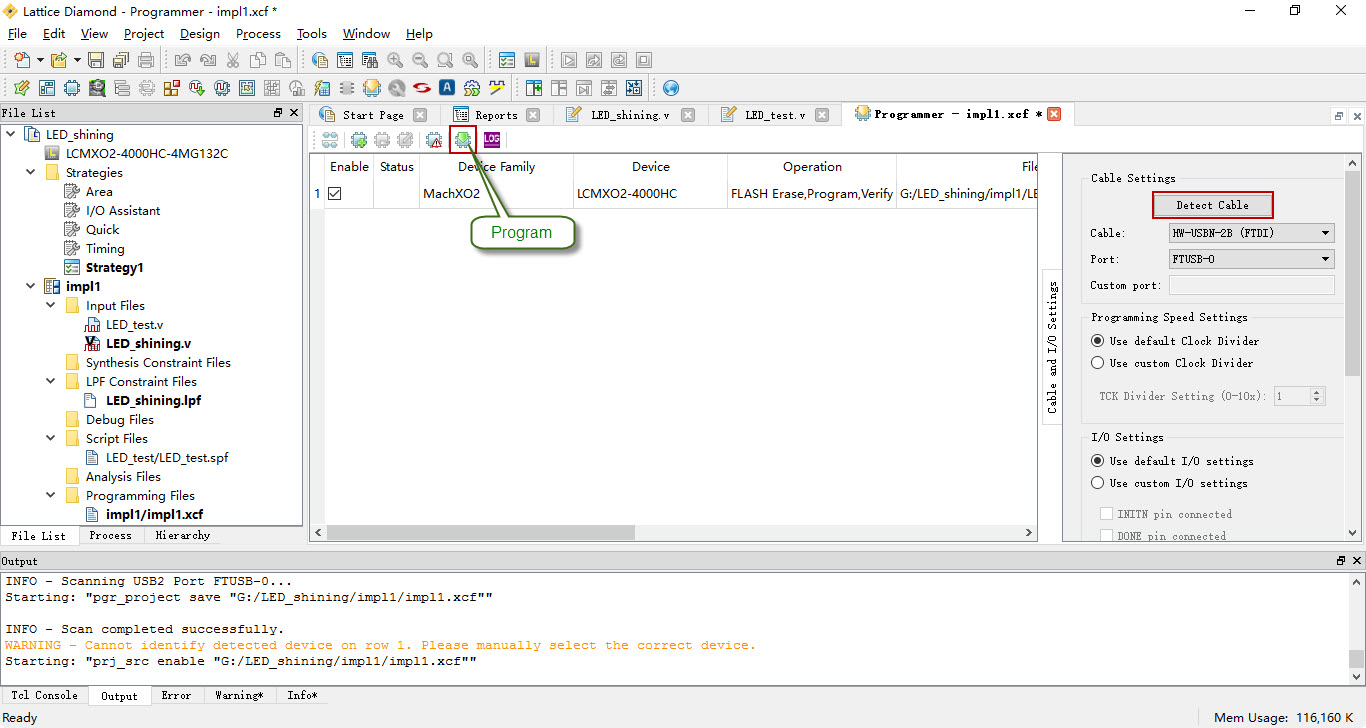

- 将Step FPGA开发板、下载器和电脑连接,如图 - 在Programmer界面,点击右侧Detect Cable,自动检测Cable 显示HW-USBN-2B(FTDI),然后点击下图中Program

- 在Programmer界面,点击右侧Detect Cable,自动检测Cable 显示HW-USBN-2B(FTDI),然后点击下图中Program - 显示PASS,加载完成,观察StepFPGA的LED交替闪烁,成功了。

- 显示PASS,加载完成,观察StepFPGA的LED交替闪烁,成功了。 —-

实验案例–时钟分频

这是一个基础的模块,可以作为后续编程中的子模块使用

本程序实现时钟分频,输出两路不同占空比的分频信号

* 程序源码如下:

* 测试源码如下:

* 仿真结果如下图所示:

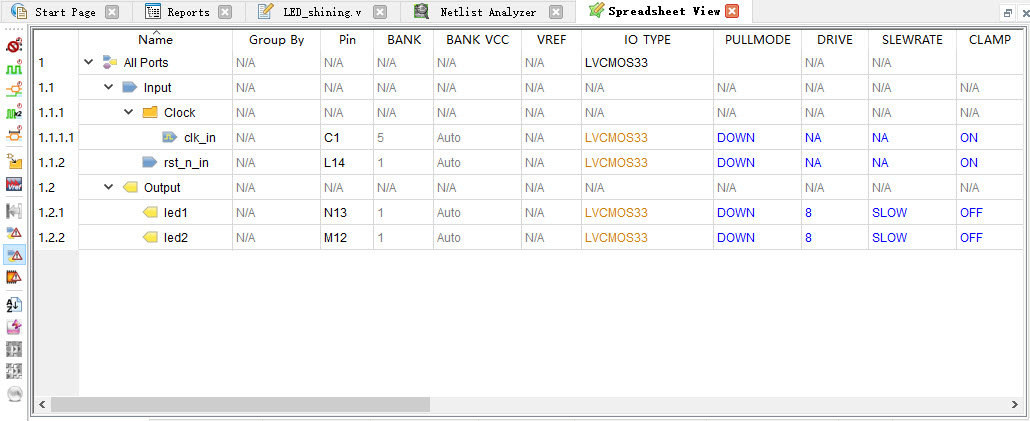

* 实际编译分配管脚信息如下:

* 最后加载到开发板上,因为占空比较小的信号不易使用LED等效果观察,我们这里分配给了N3(GPIO1)和P2(GPIO2)管脚,我们使用示波器测量开发板标注1和2的管脚,观察波形。

—-

实验案例–时钟分频

这是一个基础的模块,可以作为后续编程中的子模块使用

本程序实现时钟分频,输出两路不同占空比的分频信号

* 程序源码如下:

* 测试源码如下:

* 仿真结果如下图所示:

* 实际编译分配管脚信息如下:

* 最后加载到开发板上,因为占空比较小的信号不易使用LED等效果观察,我们这里分配给了N3(GPIO1)和P2(GPIO2)管脚,我们使用示波器测量开发板标注1和2的管脚,观察波形。