实验目的

- (1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;

- (2)通过实验理解和掌握计数器原理;

- (3)掌握用Verilog HDL数据流和行为级描述寄存器单元的方法。

实验任务

设计简单秒表(60进制),并要求带启动、复位、暂停功能。

实验原理

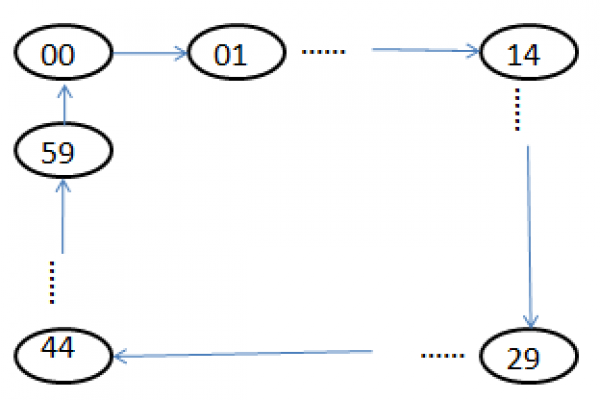

如下所示,秒表(60进制)即显示从00到59循环跳转计数。并且通过开关设置,达到复位至00,任意时刻暂停和启动的功能。我们通过将开发板的12M晶振分频(参考分频程序)出1Hz的计时频率,实现秒钟的效果。将clk_1s的上升沿作为触发信号计时。通过开发板上的按键开关置零,实现复位功能。通过拨码开关置1或0,实现暂停和启动的功能。

Verilog HDL建模描述

秒表计数器程序清单counter60.v

module counter60 ( input wire clk,rst, //时钟和复位输入 input wire key, //启动暂停按键 output wire [8:0] segment_led_1,segment_led_2 //数码管输出 ); wire clk1h; //1秒时钟 reg [7:0] cnt; //计时计数器 reg flag; //启动暂停标志 divide # //例化分频器产生1秒时钟信号 ( .WIDTH(24), .N(12_000_000) ) u1 ( .clk(clk), .rst_n(rst), .clkout(clk1h) ); always @(posedge clk) //产生标志信号 if(!rst) flag = 1'b0; else if(!key) flag = ~flag; else flag = flag; always @(posedge clk1h ) //产生60进制计数器 begin //数码管显示要按照十进制的方式显示 if(!rst) cnt <= 8'h00; //复位初值显示00 else if(flag) begin if(cnt[3:0] == 4'd9) //个位满九? begin cnt[3:0] <= 4'd0; //个位清零 if(cnt[7:4] == 4'd5 ) //十位满五? cnt[7:4] <= 4'd0; //个位清零 else cnt[7:4] <= cnt[7:4] + 1'b1; //十位加一 end else cnt[3:0] <= cnt[3:0] + 1'b1; //个位加一 end else cnt <= cnt; end segment u2 ( .seg_data_1 (cnt[7:4]), //seg_data input .seg_data_2 (cnt[3:0]), //seg_data input .segment_led_1 (segment_led_1), //MSB~LSB = SEG,DP,G,F,E,D,C,B,A .segment_led_2 (segment_led_2) //MSB~LSB = SEG,DP,G,F,E,D,C,B,A ); endmodule

其中例化的模块还包括分频模块程序divide.v和数码管segment.v

实验步骤

- 打开Lattice Diamond,建立工程。

- 新建Verilog HDL设计文件,并键入设计代码。

- 根据逻辑综合并分配管脚,在本实验中引脚分配如下:clkin —C1,rstnin—L14,key1—M13,[8:0] segmentled1 — A10~C9,[8:0] segmentled2 —C12~A12

- 构建并输出编程文件,烧写至FPGA的Flash之中。

- 观察输出结果。

开发板上的两个显示数码管从00至59循环累加。当按键开关L14按下时,计数器复位。在计数过程中,按一次M13计数暂停,再按一次M13正常计数。我们可以通过暂停清零启动的过程达到秒表计数功能。