薄膜压电MEMS

1、压电(Piezo)

何谓压电?

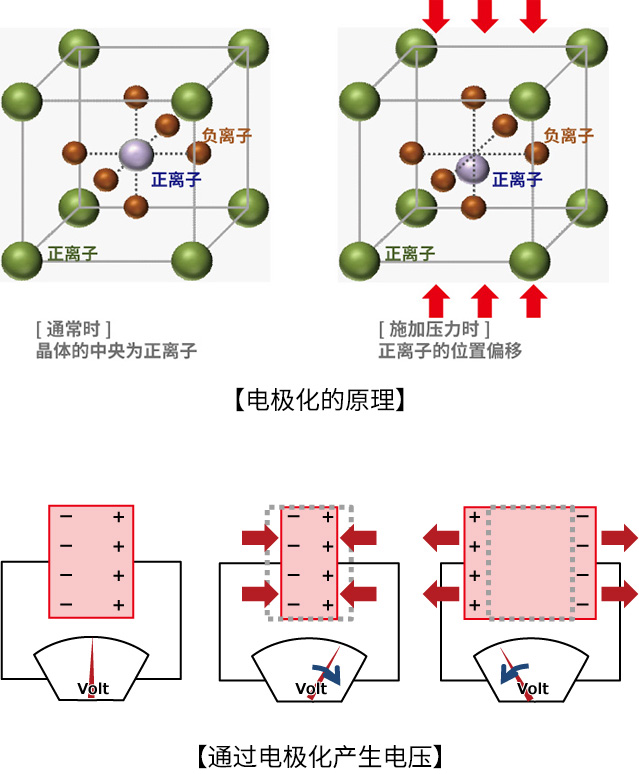

压电表示压电元件(Piezoelectric Element、Piezoelectric Device),压电元件是指通过施加力(压力)产生电压(压电效应),或与之相反,通过施加电压产生变形(逆压电效应)的元件。

压电元件使用具有压电效应的压电材料。施力时,(+)正离子、(-)负离子的位置会移动,产生(+)和(-)电荷的偏移(电极化),从而产生电压。

利用压电效应的主要用途是传感器,利用逆压电效应的主要用途是执行机构。

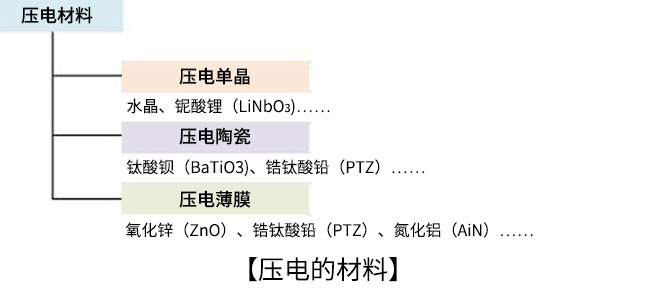

压电材料的种类

薄膜压电和块体压电

大致将厚度约为几μm的叫作薄膜压电(压电薄膜),几十μm以上的叫作块体压电(厚膜压电)。 利用薄膜压电可以实现元件的小型化、集成化、高精度化、低功耗化。

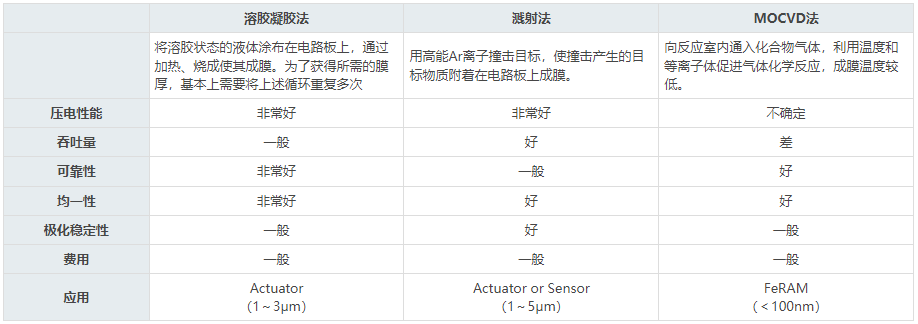

薄膜PZT的成膜方法

生成薄膜PZT的方法有溶胶凝胶法、溅射法、MOCVD法等。下表汇总了其各自的特点。

罗姆的薄膜压电MEMS代工为实现融合自有薄膜压电和LSI微细加工技术的小型、节能、高性能产品,提供从试制、开发到量产的全程支持。

2、压电相关术语

压电(Piezo):指压电元件(piezoelectric element、piezoelectric device)

压电效应:通过施加力(压力)产生电压的现象

逆压电效应:通过施加电压产生变形的现象

压电元件:利用压电效应、逆压电效应的零件、元件

传感器:利用科学原理将现象和信息等转换为电信号等的装置

执行机构:将电等能源转换为机械运动,用于运行设备的驱动装置

离子:指因电子过剩或缺失而携带电荷的原子

压电材料:表现压电性的结晶性物质的统称

压电单晶:材料内部的晶体结构均匀连续的压电材料

压电陶瓷:拥有晶粒结构或畴壁结构的压电体

晶粒结构:在多晶体中,2个以上的小晶体之间存在的界面

畴壁结构:晶体内存在极化方向不同的边界的结构

极化:置于电场或磁场时产生正负电化,或是产生磁极的现象

PZT:指锆钛酸铅(PbZrxTi1-xO3)(0<x<1)

溅射:使高能粒子撞击金属表面,利用飞出的原子进行制膜的方法

CSD:通过涂布、烧成金属有机酸盐或化合物溶液形成薄膜的方法

溶胶凝胶法:CSD的一种。通过对溶胶状态的液体进行加热、烧成来得到薄膜的方法

溶胶状态:以液体为分散介质的胶体(例:肥皂水、浆糊、蛋清、牛奶、蛋黄酱等)

凝胶状态:溶胶状态丧失流动性后的状态

MOCVD:有机金属气相沉积法,使用有机金属和气体作为原料的晶体生长方法

占板面积:占有面积,这里指设置装置时使用的面积

压电体:指通过施加应力产生极化(电压)的介电体

热释电体:即使不从外部施加电场,也可以自发极化的压电体

铁电体:从外部施加电场可以使极化方向反转的热释电体

薄膜压电:指压电材料的厚度约为几μm的压电元件

块体压电:指压电材料的厚度为几十μm以上的压电元件

3、MEMS

何谓MEMS?

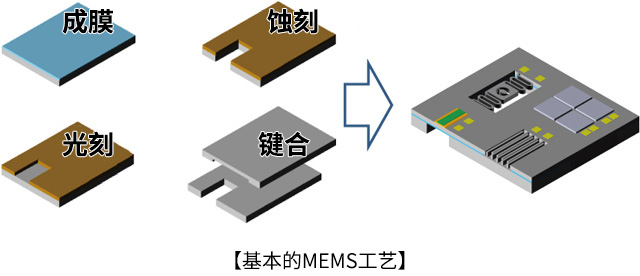

MEMS是Micro Electro Mechanical Systems(微机电系统)的缩写,具有微小的立体结构(三维结构),是处理各种输入、输出信号的系统的统称。 是利用微细加工技术,将机械零零件、电子电路、传感器、执行机构集成在一块电路板上的高附加值元件。

MEMS工艺

晶圆

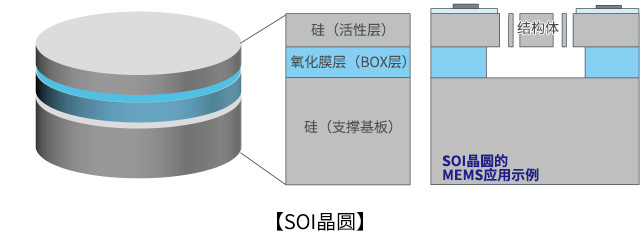

SOI晶圆

SOI是Silicon On Insulator的缩写,是指在氧化膜上形成了单晶硅层的硅晶圆。已广泛应用于功率元件和MEMS等,在MEMS中可以使用氧化膜层作为硅蚀刻的阻挡层,因此能够形成复杂的三维立体结构。

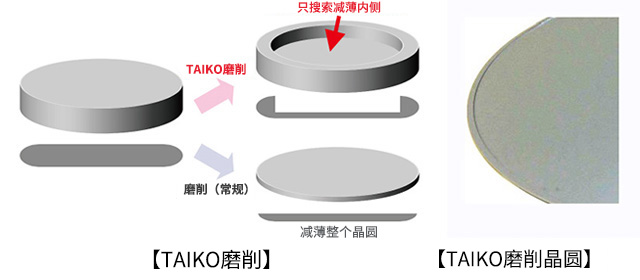

TAIKO磨削 “TAIKO”是DISCO株式会社的商标

TAIKO磨削是DISCO公司开发的技术,在磨削晶圆时保留最外围的边缘,只对其内侧进行磨削。

TAIKO磨削与通常的磨削相比,具有“晶圆曲翘减少”、“晶圆强度更高”、“处理容易”、“与其他工艺的整合性更高”等优点。

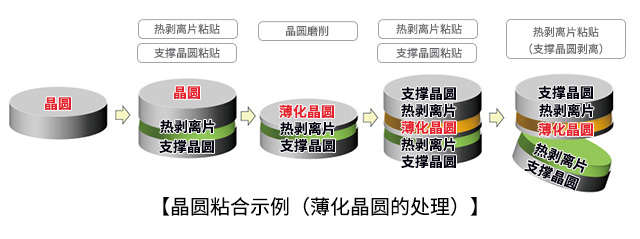

晶圆粘合/热剥离片工艺

通过使用支撑晶圆和热剥离片,可以轻松对薄化晶圆进行处理等。

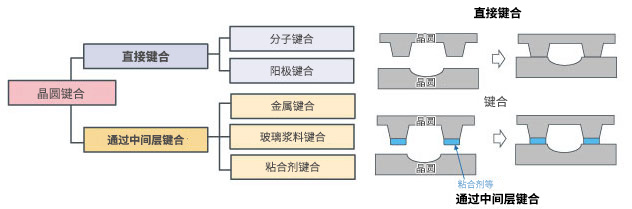

晶圆键合

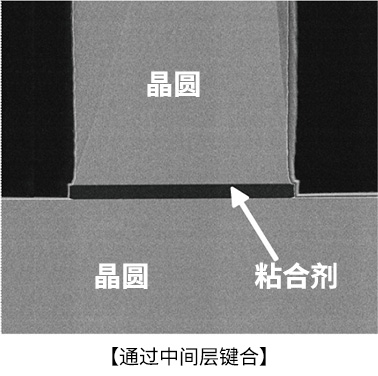

晶圆键合大致分为“直接键合”、“通过中间层键合”2类。

直接键合不使用粘合剂等,是利用热处理产生的分子间力使晶圆相互粘合的键合,用于制作SOI晶圆等。 通过中间层键合是借助粘合剂等使晶圆互相粘合的键合方法。

蚀刻

各向同性蚀刻与各向异性蚀刻

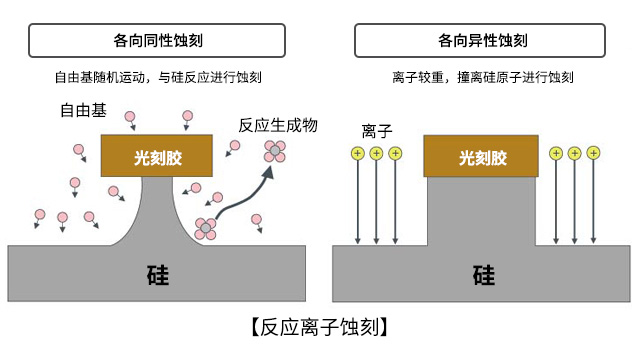

通过在低真空中放电使等离子体产生离子等粒子,利用该粒子进行蚀刻的技术称为反应离子蚀刻。 等离子体中混合存在着携带电荷的离子和中性的自由基,具有利用自由基的各向同性蚀刻、利用离子的各向异性蚀刻两种蚀刻作用。

硅深度蚀刻

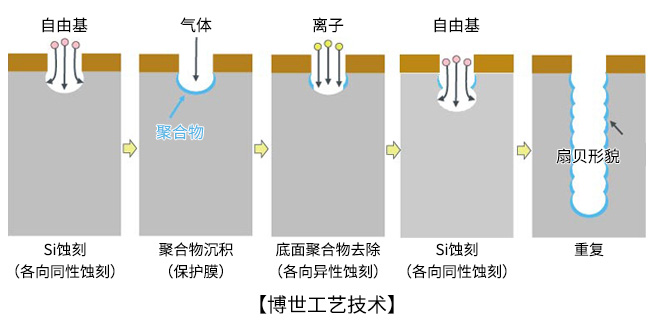

集各向异性蚀刻和各向同性蚀刻的优点于一身的博世工艺技术已经成为了硅深度蚀刻的主流技术。

通过重复进行Si蚀刻⇒聚合物沉积⇒底面聚合物去除,可以进行纵向的深度蚀刻。 侧壁的凹凸因形似扇贝,称为“扇贝形貌”。

成膜

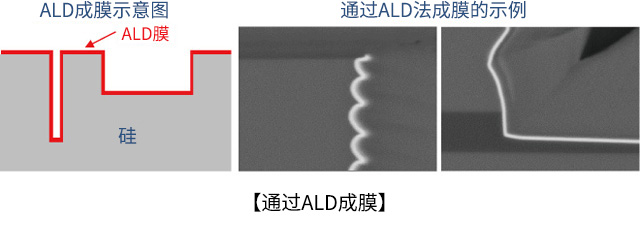

ALD(原子层沉积)

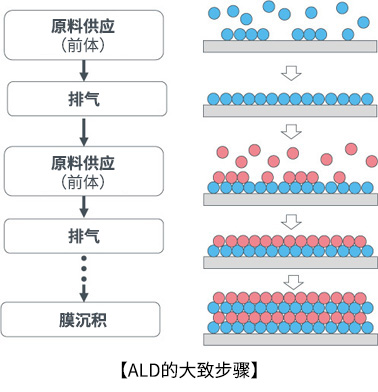

ALD是Atomic Layer Deposition(原子层沉积)的缩写,是通过重复进行材料供应(前体)和排气,利用与基板之间的表面反应,分步逐层沉积原子的成膜方式。 通过采用这种方式,只要有成膜材料可以通过的缝隙,就能以纳米等级的膜厚控制,在小孔侧壁和深孔底部等部位成膜,在深度蚀刻时的聚合物沉积等MEMS加工中形成均匀的成膜。

罗姆的薄膜压电MEMS代工运用自身拥有的先进薄膜压电技术和MEMS加工技术,以及得到了量产业绩印证的先进生产技术,为实现小型、节能、高性能产品,提供从试制、开发到量产的全程支持。

4、MEMS相关术语

关于MEMS相关术语的简要说明。

MEMS:Micro Electro Mechanical Systems的缩写。具有微小的立体结构(三维结构),是处理各种输入、输出信号的元件、系统的统称。

各向同性蚀刻:利用自由基沿深度方向、横向进行的蚀刻

各向异性蚀刻:利用离子沿深度方向进行的蚀刻

博世工艺:Si深度蚀刻的主要技术。组合了各向同性蚀刻与各向异性蚀刻的技术

扇贝形貌:利用博世工艺形成的侧壁的凹凸形状

SOI晶圆:Silicon On Insulator的缩写。在氧化膜上形成了单晶硅层的硅晶圆。

TAIKO磨削:磨削晶圆时保留最外围的边缘,只对其内侧进行磨削的技术 *“TAIKO”是DISCO株式会社的商标

支撑晶圆:为满足薄晶圆的处理和工艺的需要而用作支撑的晶圆

晶圆粘合:为满足薄晶圆的处理和工艺的需要而粘合支撑用基板(支撑晶圆)

晶圆键合:以封装等为目的进行的晶圆之间的键合

ALD(原子层沉积):分步逐层沉积原子的成膜方式。