**这是本文档旧的修订版!**

SRAM接口实验

实验内容

本实验的目的是熟悉SRAM的工作原理,并能够通过编程来访问SRAM。本实验利用VHDL或Verilog编程访问开发系统核心板上的SRAM IS61LV24516,要求:

1. 依次向SRAM中的每个地址写入一个数,然后将此数从该地址中读出,判断写入的数和读出的数是否正确;向每个地址中写入的数从0开始依次加1。

2. 如果对某个地址写入的数和读出的数相同,则LED0缓慢闪烁,每2秒闪烁一次,表示读写正确;如果对某个地址写入的数和读出的数不同,则LED7快速闪烁,每0.4秒闪烁一次,表示读写错误。

实验原理

SRAM是英文Static RAM的缩写,即静态存储器。它是一种具有静态存取功能的存储器,不需要刷新电路即能保存它内部存储的数据。SRAM访问速度快,不必配合内存刷新电路,可提高整体的工作速度。但SRAM集成度低,功耗较大,相同的容量下体积较大,而且价格较高,少量用于关键性系统以提高效率。

SRAM按是否需要时钟又分为同步SRAM和异步SRAM。同步SRAM采用一个输入时钟来启动存储器的所有事务处理(读、写等);而异步SRAM并不具备时钟输入,通过监视输入以获取来自控制器的命令,一旦识别出某条命令,SRAM将立即执行命令。

开发系统核心板上的SRAM IS61LV24516为异步SRAM,无时钟信号,管脚定义如表13-1所示。

表13-1 SRAM管脚定义

| A0~A17 | 访问SRAM的地址,18位,地址空间为256K。 |

| I/O0~I/O1L12,L11 | 数据线,16位宽,SRAM的总容量为512K字节。 |

| CE | 片选信号,低电平有效。 |

| OE | 读使能信号,低电平有效。 |

| WE | 写使能信号,低电平有效。 |

| LB | 低8位访问控制信号,低电平有效。如果LB为0则表示访问16位数据的低8位。 |

| UB | 高8为访问控制信号,低电平有效。如果UB为低则表示访问16为数据的高8位。 |

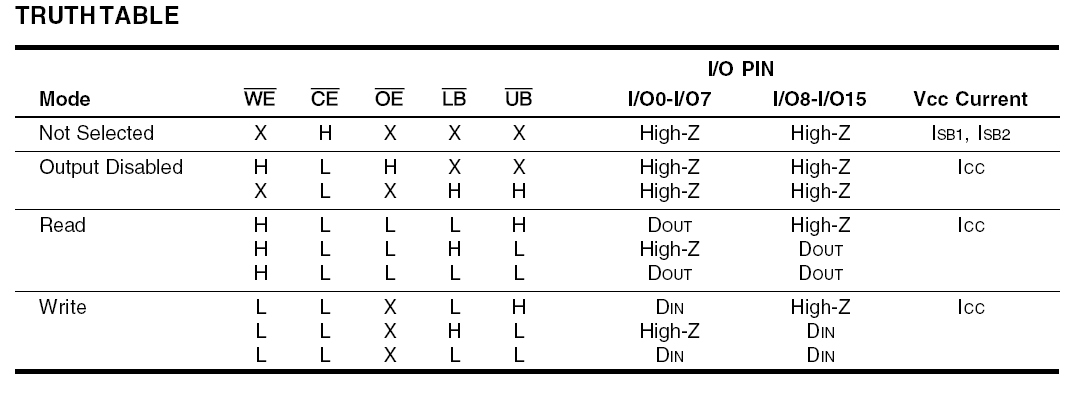

图13-1 管脚详细功能定义

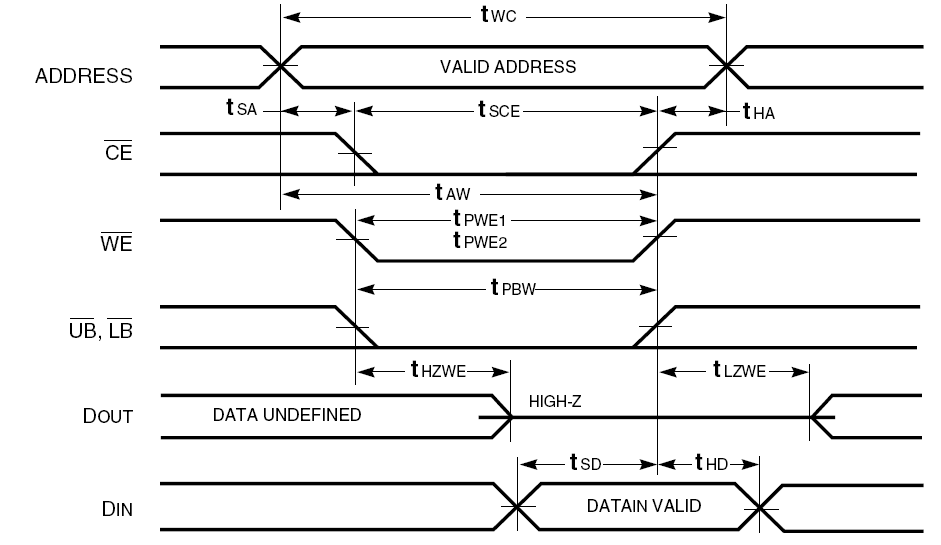

图13-2 SRAM写入时序

程序设计

仿真结果

演示程序文件说明