**这是本文档旧的修订版!**

串行接口实验

1. 实验内容

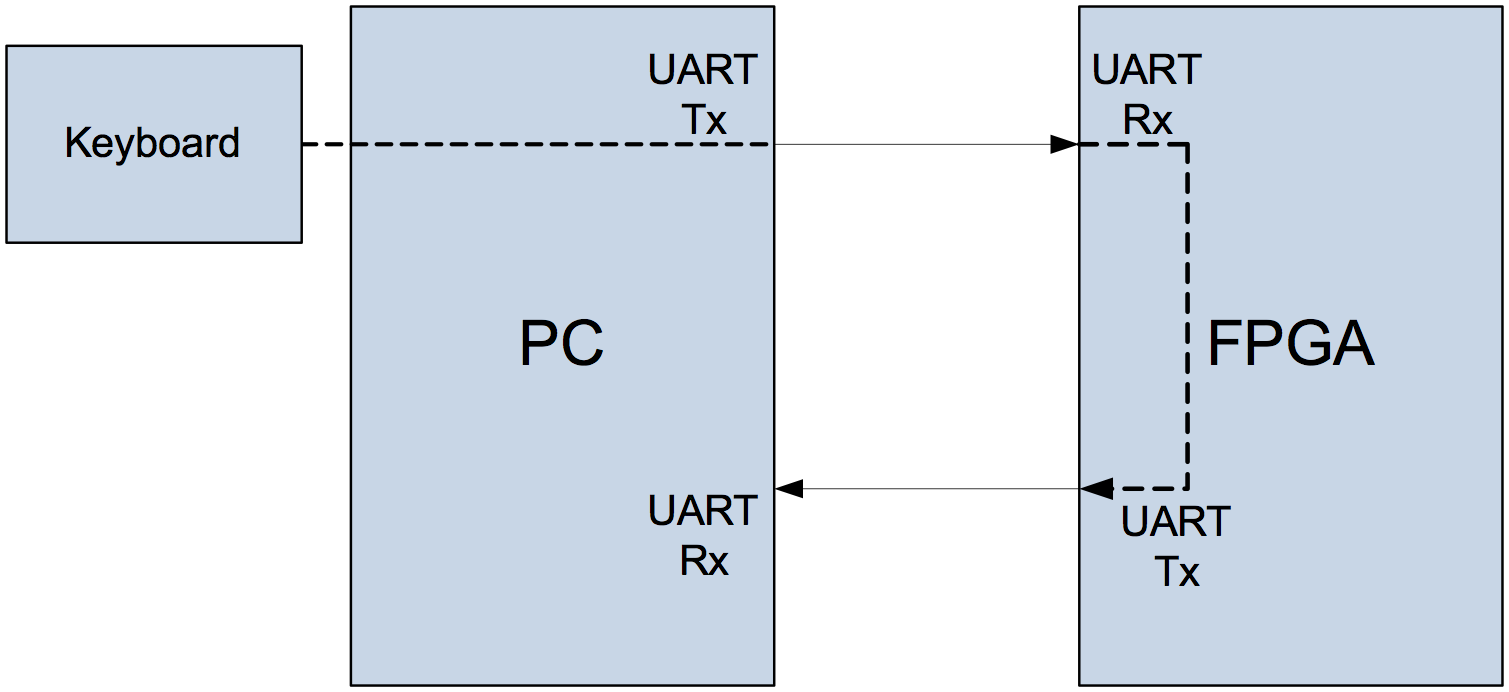

本实验要求熟悉串行接口通信的基本原理,实现利用串行接口与计算机的通信,通过键盘输入的数据通过PC上的串行接口发送给FPGA,FPGA收到数据以后再将该数据通过串行接口发送给计算机,并通过超级终端显示出来,如图所示。

图14-1 串口通信实验要求

2. 实验原理

串行接口(简称串口)通信是目前最常用的一种低速短距离通信方式,常用于对各种设备进行操作的控制台,是UART(Universal Asynchronous Receiver/Transmitter,通用异步接收/发送装置)的一种具体实现方式,最常用的就是计算机上具备的RS232接口(图14-1)。本实验的采用的就是RS232接口,RS232接口由9针,其各引脚定义如表14-1所示。通常只使用其中的2、3、5三个管脚。

图14-2 RS232接口

表14-1 RS232管脚定义

| 1 | 载波检测 DCD |

| 2 | 接收数据 RXD |

| 3 | 发送数据 TXD |

| 4 | 数据终端准备好 DTR |

| 5 | 信号地 SG |

| 6 | 数据准备好 DSR |

| 7 | 请求发送 RTS |

| 8 | 清除发送 CTS |

| 9 | 振铃提示 RI |

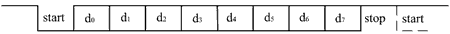

串口是异步通信方式,通信的发送方和接收方各自有独立的时钟,传输的速率由双方约定。UART的通信协议十分简单,以低电平作为起始位,高电平作为停止位,中间可传输5~8比特数据和1比特奇偶校验位,奇偶校验位的有无和数据比特的长度由通信双方约定。一帧数据传输完毕后可以继续传输下一帧数据,也可以继续保持为高电平,两帧之间保持高电平,持续时间可以任意长。本实验采用不添加校验位的方法,以提高数据传输效率。发送端发送数据时先发一低电平,然后发送8比特数据,之后马上把信号拉高,从而完成一帧数据传送。接收端接收到低电平时开始计数,然后接收8比特信息位后如果检测到高电平即认为已接收完一帧数据,继续等待下一帧起始信号低电平的到来,若接收完8比特数据后没有检测到高电平则认为这不是一帧有效数据,将其丢弃,继续等待起始信号。时序关系如图14-3所示,收发可同时进行,互不干扰。本实验的波特率设为9600。

图14-3 RS-232接口的工作时序

3. 程序设计

4. 仿真结果

5. 演示程序文件说明