**这是本文档旧的修订版!**

BCH编码实验

1. 实验内容

通过本实验了解BCH编译码原理,能够用Verilog HDL或者VHDL编写BCH编译码程序。本实验要求实现BCH(15,7,2)编译码功能,加入信道噪声进行,比较译码结果。

2. 实验原理

(1)BCH编码原理

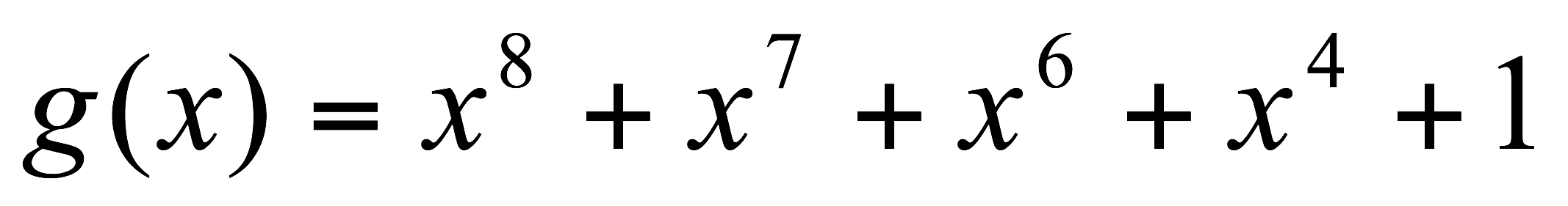

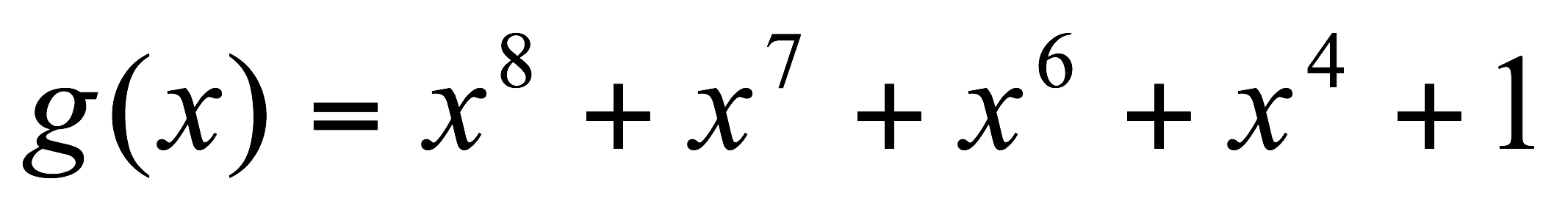

BCH是一种线性分组码,它是循环码的一种。一个(15,7,2)的BCH码的含义是,一组码的码长为15,信息位为7位,效验位为8位,纠错能力为2。它的本原多项式为

;

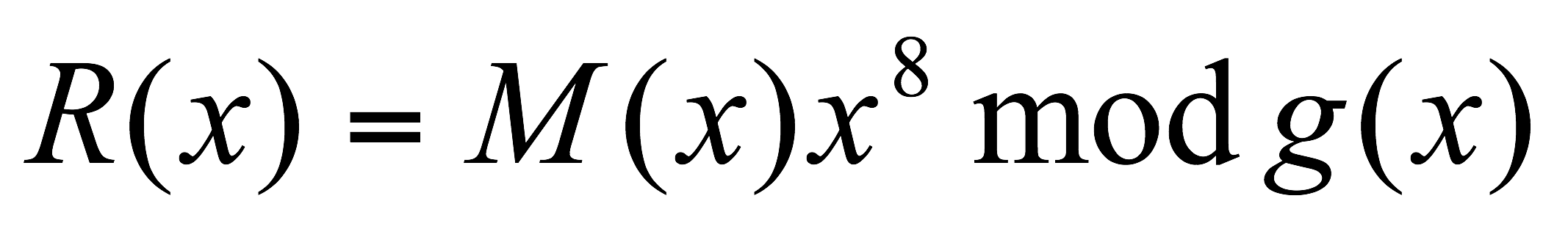

本实验采用系统BCH码,即码的前7位为信息位不变,而后8位校验位多项式为码的信息位多项式与生成多项式相除的余数得到。具体公式如下:

;

本实验采用系统BCH码,即码的前7位为信息位不变,而后8位校验位多项式为码的信息位多项式与生成多项式相除的余数得到。具体公式如下:

;

其中R(x)为效验位多项式,M(x)为信息位的多项式

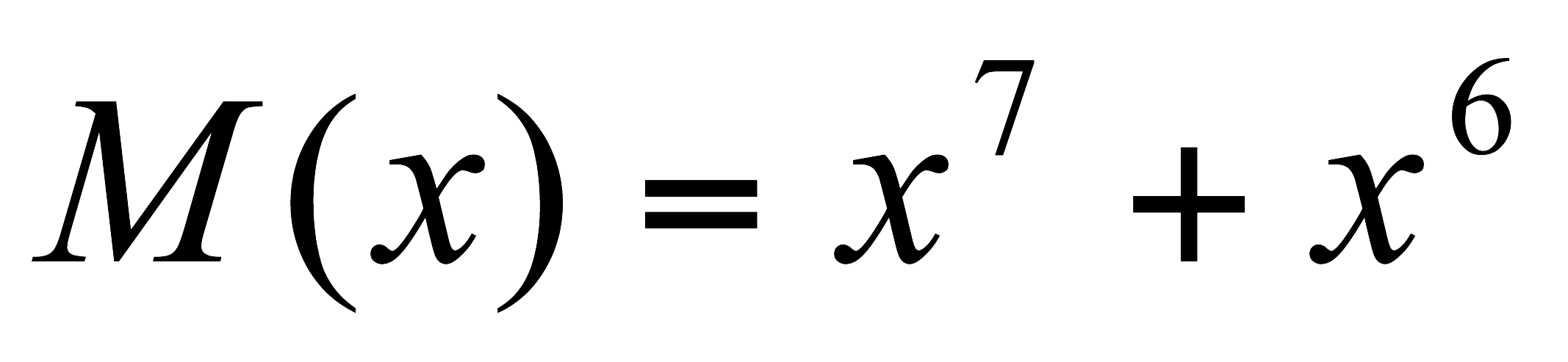

例如信息位为1100000,则

;

其中R(x)为效验位多项式,M(x)为信息位的多项式

例如信息位为1100000,则 ,

,

校验位多项式 {{ :图16-164.png |}}

编码多项式 {{ :图16-165.png |}}

因此,编码输出为110000010011100。

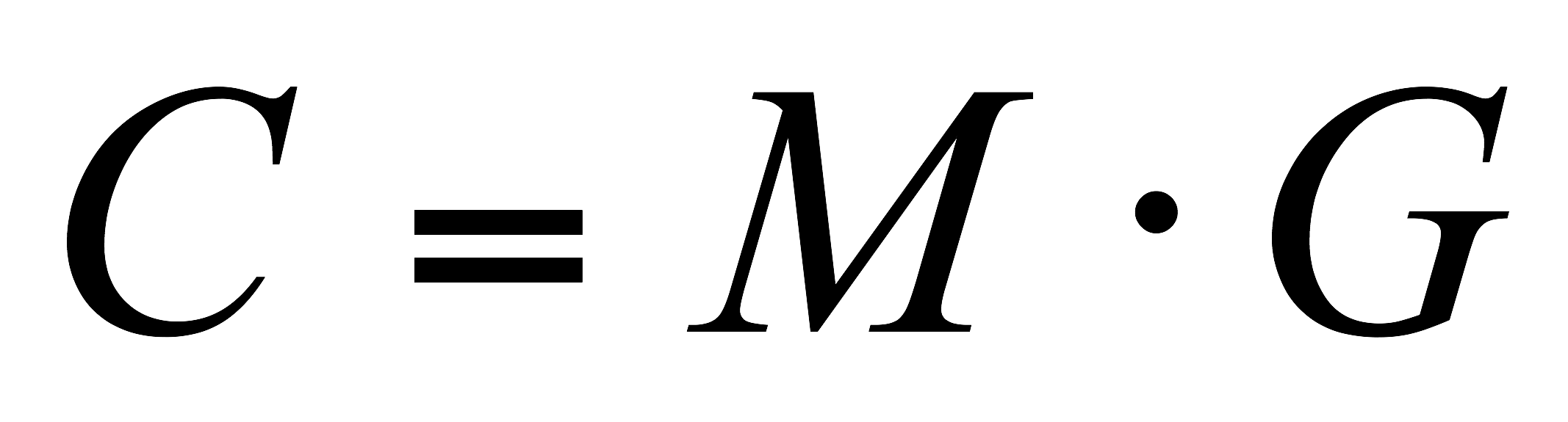

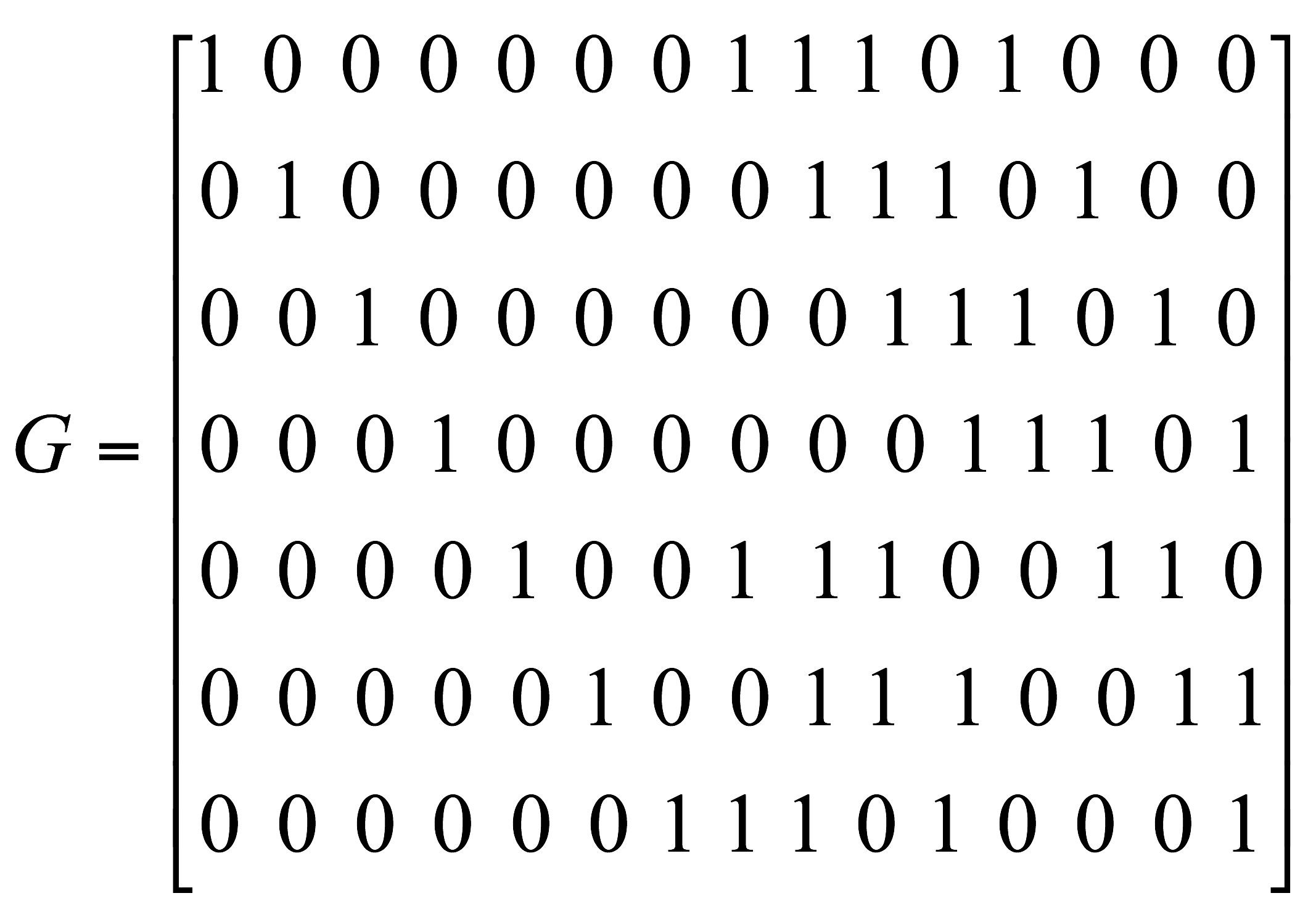

BCH码各个码位的系数,也可以通过生成矩阵G求得:

生成多项式

生成多项式 的生成矩阵为:

的生成矩阵为:

生成矩阵的构造原理可以参看数字通信相关书籍。

(2)BCH码译码原理

BCH译码分为三步:

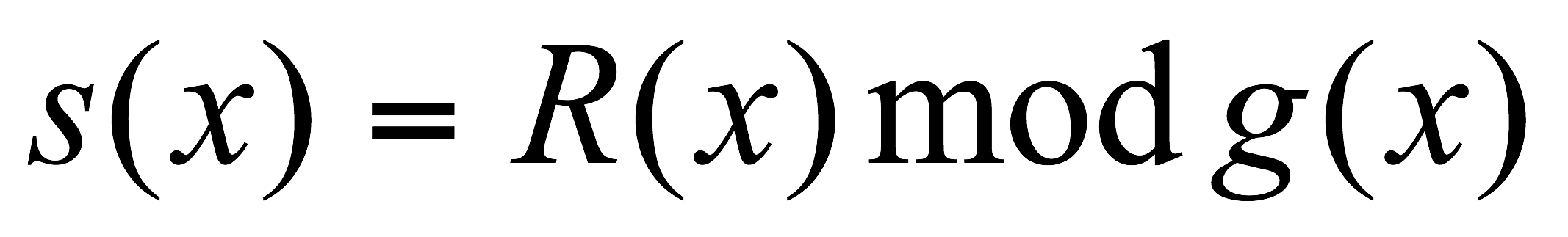

1) 由接收到的码的多项式R(x)计算出伴随多项式S(x)

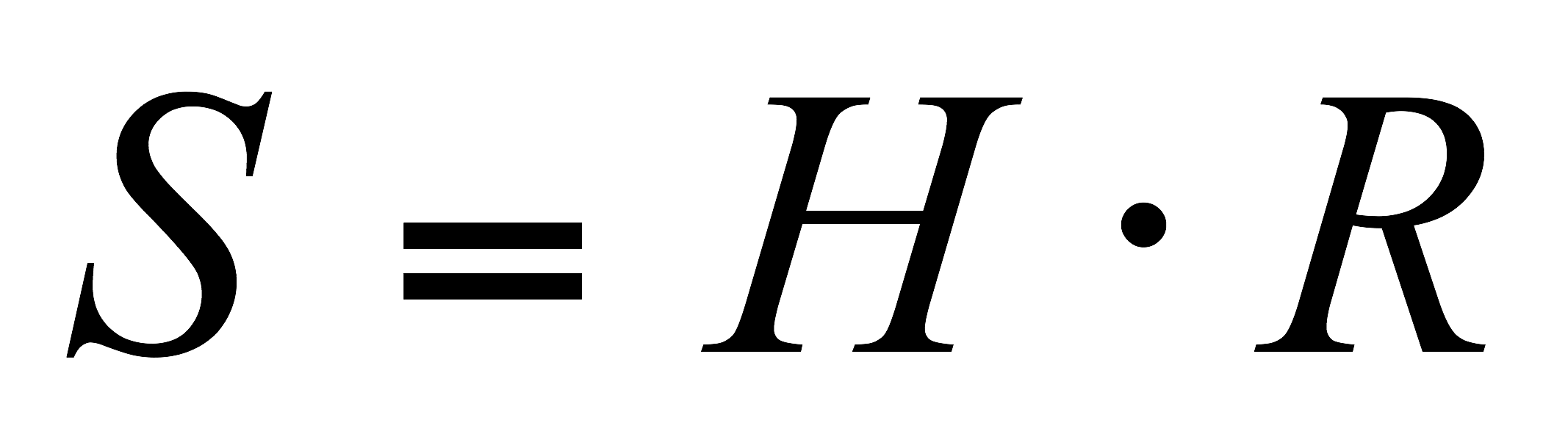

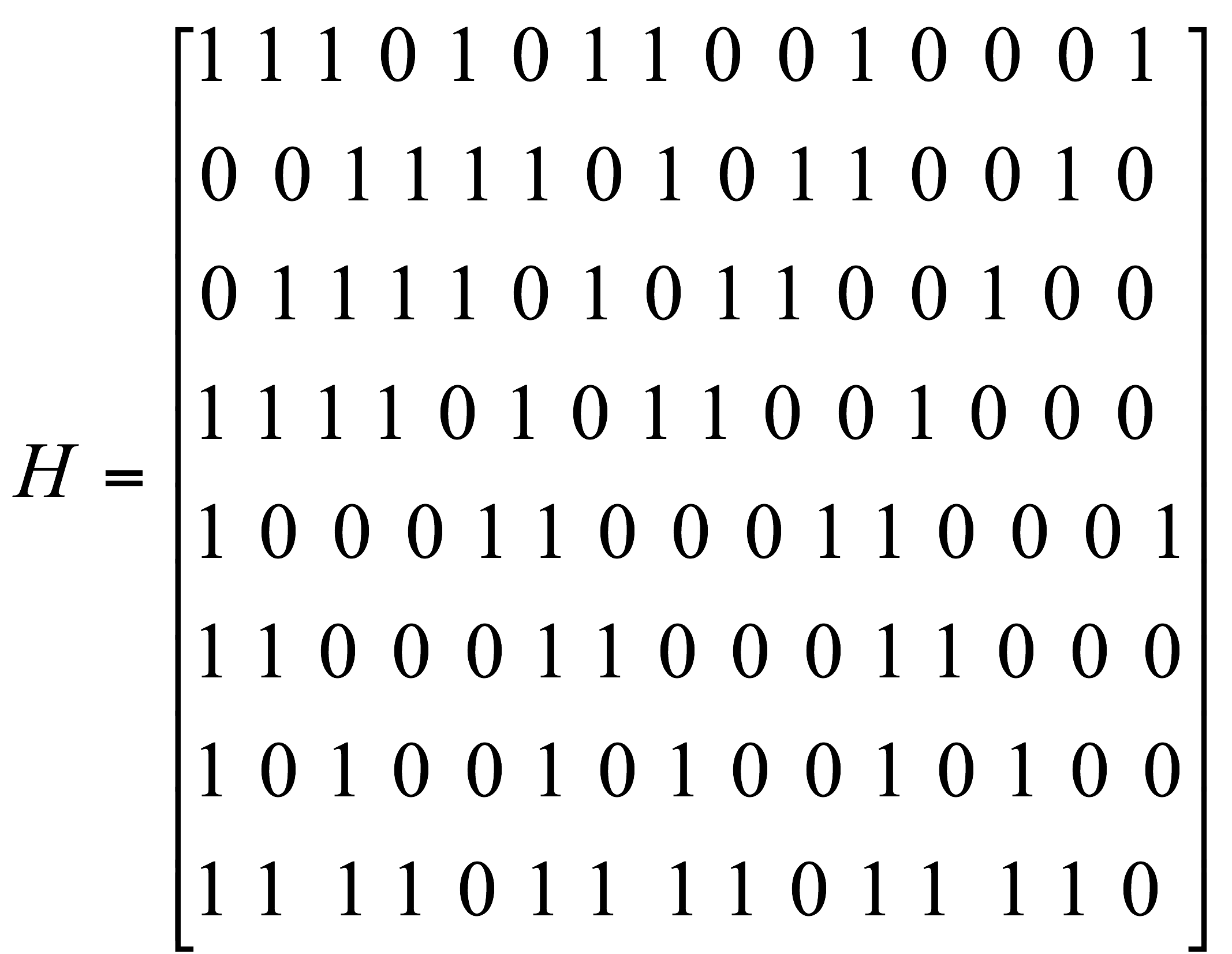

同样地,伴随多项式系数也可以由矩阵运算得到。公式如下:

同样地,伴随多项式系数也可以由矩阵运算得到。公式如下:

其中H被称为校验矩阵。

2)根据伴随多项式计算找到对应的错误图样E(x)。

2)根据伴随多项式计算找到对应的错误图样E(x)。

本实验使用查表法计算错误图样。

3)计算出译码输出C(x)=R(x)-E(x)

3. 实验设计

3.1 总体架构

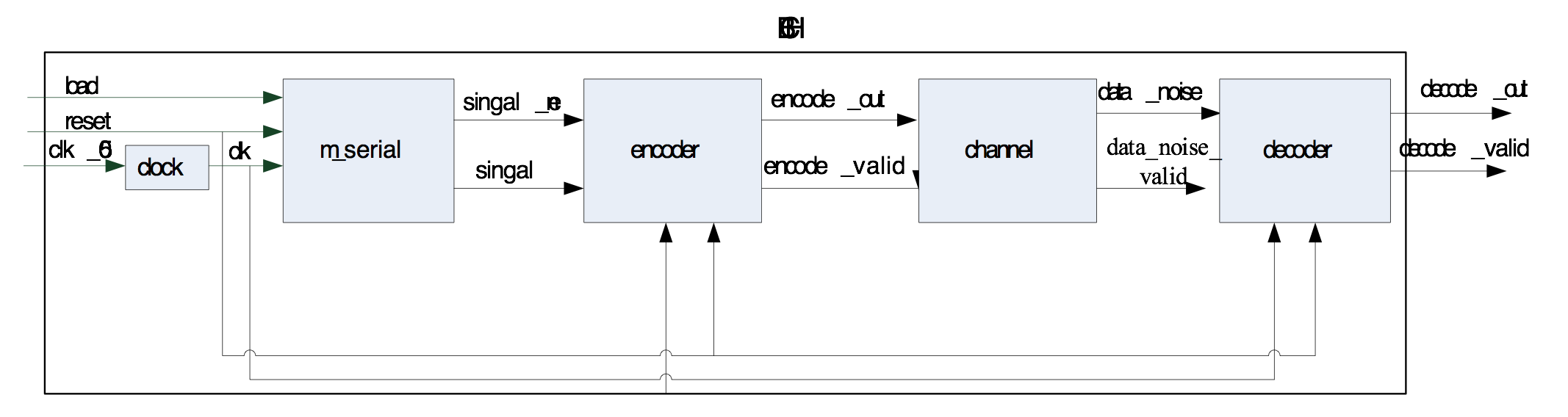

程序由5个模块组成(图 16 1):

1. BCH为顶层模块,完成各模块之间的连接;

2. clock模块实现50M时钟clk50的4分频clk,clk50作为signaltap的采样时钟。clk作为其它四个模块的主时钟;

3. mserial产生一个M序列作为数据作为编码模块的输入。

4. encoder是BCH的编码模块。

5. channel模块模拟信道,加入误码。

6. decoder是BCH的译码模块。

4. 仿真结果

5. 演示程序文件说明