以下为板卡介绍:

1、板卡简介:

本设计基于Lattice的ICE40UP5K FPGA和STM32G031 MCU,板载LPC11U35下载器,可以通过USB-C接口进行FPGA的配置,并通过虚拟串口通信配置STM32G031,支持在ICE40UP5K上对RISC-V软核的移植以及开源的FPGA开发工具链,板上RGB三色LED灯用于简单的调试,总计36个IO用于扩展使用,其中14个连接STM32G031 芯片,另外的22根连接ICE40UP5K FPGA芯片。

搭配电赛扩展板,帮助信号源、仪器仪表、控制以及信号处理类题目的训练。板上有通过两个16Pin的插座可以安装高速ADC(16Pin可再用模块/同时支持DIP和邮票孔)、高速DAC(16Pin可再用模块/支持DIP和邮票孔)、板上安装了高速比较器、姿态传感器、旋转编码器以及按键等。

2、平台包含:

- 电赛扩展板 x1

- ADC模块 x1

- DAC模块 x1

- STM32+iCE40核心板 x1

- Type-C数据线 x1

3、板卡适用范围:

- 大二学生、FPGA学习者做与FPGA相关的数字系统实验

- 备战全国大学生电子设计竞赛

- 通过完成历年电赛中的相关题目来掌握FPGA的应用

- 适用于电赛中测试测量、无线通信、控制类的题目

4、关键器件

- 核心模块: 硬禾学堂提供两种模块

- 全FPGA的核心模块,比如小脚丫FPGA核心板,支持Lattice版本和Intel/Altera版本的小脚丫FPGA核心板

- FPGA + MCU混合的模块 - 采用STM32G031进行控制输入响应、信息在OLED上的显示、数据的处理;采用FPGA进行高速数据采集、高速DDS信号产生、高速频率计/计数器、数字信号处理(FFT、数字滤波等)

- 信息显示:128 * 64 OLED,通过SPI总线驱动

- 控制输入: 旋转编码器/按键

- 信号采集:10bit/50Msps 高速ADC

- 信号生成:10bit/120Msps 高速DAC

- 频率测量:高速比较器

- 控制输出:PWM

- 传感器:三轴姿态感知

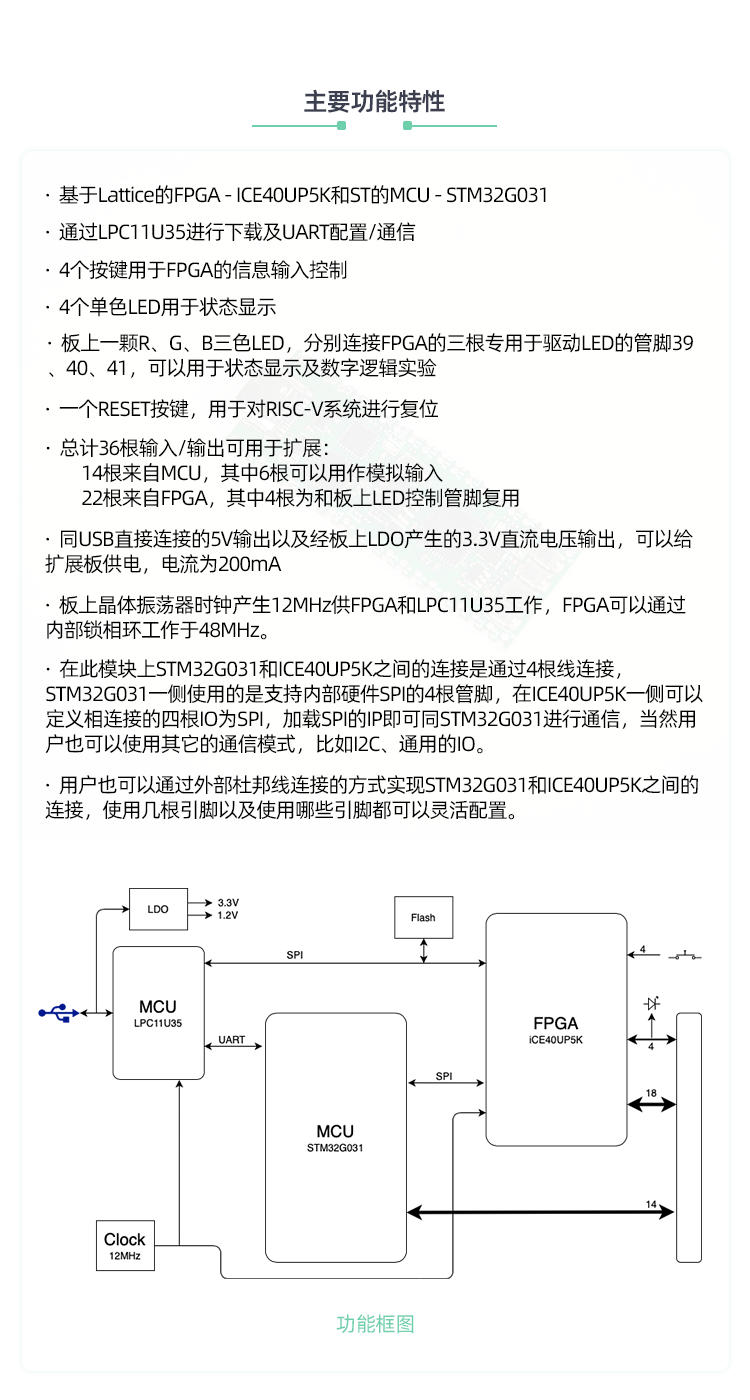

5、系统框图:

6、核心板介绍

核心板支持小脚丫或MCU+FPGA混合架构,本次活动是搭配基于STM32G031 + iCE40UP5K的MCU+FPGA核心板使用:

参考资源:

几种开源的RISC-V软核:

- PicoRV32 - A Size-Optimized RISC-V CPU

- SERV - 一个获奖的RISC-V软核,最小的RISC-V软核

- biriscv和VexRiscv - 支持Linux的比较快的软核

- ICE-V

- FEMTORV32 / FEMTOSOC: a minimalistic RISC-V CPU

7、平台可以训练的技能:

- 用OLED显示信息,并掌握SPI总线以及显示屏的驱动原理

- 控制信息的按键输入以及按键消抖的软件/FPGA逻辑处理

- 旋转编码器的输入以及译码 - MCU软件实现/FPGA逻辑实现

- ADC高速数据采集以及缓存处理

- ADC低速数据采集以及数据处理、MCU的响应

- Sigma Delta ADC的实现(通过高速比较器)以及数字滤波器的使用

- FFT - 傅立叶变换,用于频谱分析

- 数字滤波器 - 通过FPGA内部逻辑/乘法器实现,以及通过MCU的程序实现

- 频率计/计数器设计 - FPGA逻辑实现,以及MCU的定时器/代码实现方法

- 高速DAC以及DDS信号发生器的构成及参数控制

- 通过PWM构成DAC实现DDS - 任意波形产生

- 姿态传感器的数据采集、处理以及信息显示

- UART的数据传输

8、管脚映射关系

本平台支持多种核心模块,每一种核心模块的管脚映射关系如下表:

功能管脚 | 核心模块管脚编号 | XO2-4000HC FPGA管脚 | Intel/Altera MAX10 FPGA管脚 | STM32G031 + UP5K FPGA管脚 |

OLED_SCK | 39 | E12 | B4 | PA0/ADC0 - Pin 6 |

OLED_SDA | 37 | G12 | A7 | PA4/ADC4 - Pin 10 |

OLED_DC | 4 | E3 | M5 | PA8/MCO - Pin 16 |

OLED_RST | 36 | F13 | B6 | PA5/ADC5 - Pin 11 |

Encoder_A | 2 | C8 | M4 | PB0/ADC8 - Pin 14 |

Encoder_B | 3 | B8 | P3 | PB1/ADC9 - Pin 15 |

Encoder_S | 5 | F3 | R3 | PC6 - Pin 17 |

SW_S1 | 6 | G3 | L6 | PA11 - Pin 18 |

SW_S2 | 7 | H3 | P4 | PA12 - Pin 19 |

Sensor_SCL | 8 | J2 | L7 | I2C_SCL - Pin 26 |

Sensor_SDA | 33 | G14 | B7 | I2C_SDA - Pin 27 |

Sensor_INT | 34 | G13 | D7 | PA7/ADC7 - Pin 13 |

PWM_OUT | 35 | F14 | E7 | PA6/ADC6 - Pin 12 |

Ain | 38 | F12 | A5 | PA1/ADC1 - Pin 7 |

ADC_D0 | 9 | J3 | R5 | 26 |

ADC_D1 | 10 | K2 | P6 | 27 |

ADC_D2 | 11 | K3 | R7 | 28 |

ADC_D3 | 12 | L3 | P7 | 31 |

ADC_D4 | 13 | N5 | P8 | 32 |

ADC_D5 | 14 | P6 | P9 | 34 |

ADC_D6 | 15 | N6 | R9 | 2 |

ADC_D7 | 16 | P7 | R11 | 36 |

ADC_D8 | 17 | N7 | P12 | 25 |

ADC_D9 | 18 | P8 | R14 | 48 |

ADC_CLK | 19 | N8 | P15 | 47 |

DAC_D9 | 32 | H12 | C8 | 18 |

DAC_D8 | 31 | J13 | B8 | 13 |

DAC_D7 | 30 | J14 | D10 | 12 |

DAC_D6 | 29 | K12 | A9 | 11 |

DAC_D5 | 28 | K14 | A11 | 10 |

DAC_D4 | 27 | K13 | A13 | 9 |

DAC_D3 | 26 | J12 | B11 | 6 |

DAC_D2 | 25 | P3 | A14 | 4 |

DAC_D1 | 24 | M4 | B13 | 3 |

DAC_D0 | 23 | N4 | B14 | 46 |

DAC_CLK | 22 | P13 | B15 | 45 |

9、交流群