1/任务要求与介绍

设计一款USB转JTAG的下载器

- 采用USB Type-C连接器,支持USB2.0数据传输

- 板卡尺寸:小于35mmx18mm

- 包含信号:JTAG信号线、+5V、+3.3V、GND

- 主要器件:需在DigiKey官网上有货且正常售卖

主控芯片:FT2232HL,Channel A配置为MPSSE模式,直接生成JTAG时序。

供电方案:Type-C接口取电(5V),通过LDO3.3V转换为FPGA所需的3.3V/1.8V电平。

接口定义:

8PIN 2.54mm排针:

TCK、TDI、TDO、TMS(JTAG信号)

GND、VREF、5V/3.3V(目标板参考电压)

预留SRST(系统复位)和TRST(JTAG复位)可选信号。

使用的是双面板布线。

2/DGK平台连接:

https://www.digikey.cn/zh/products/detail/ftdi-future-technology-devices-international-ltd/FT232HL-TRAY/4006918

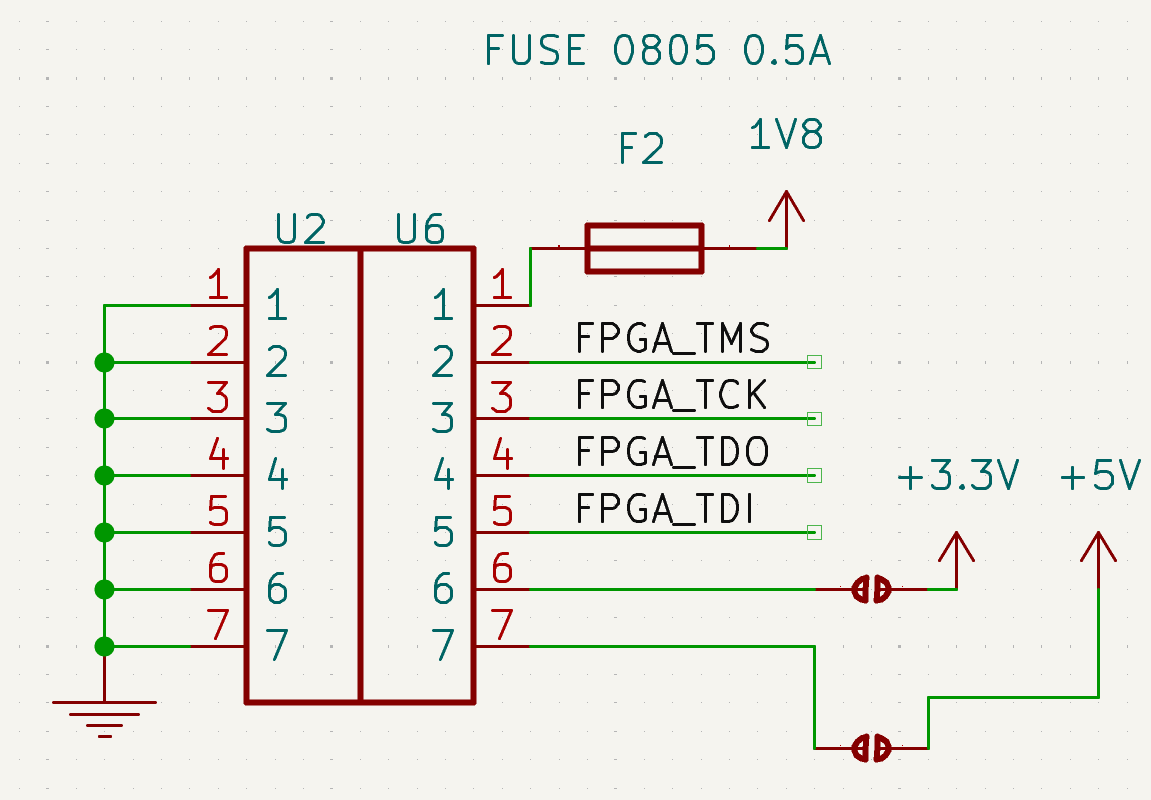

3/图纸

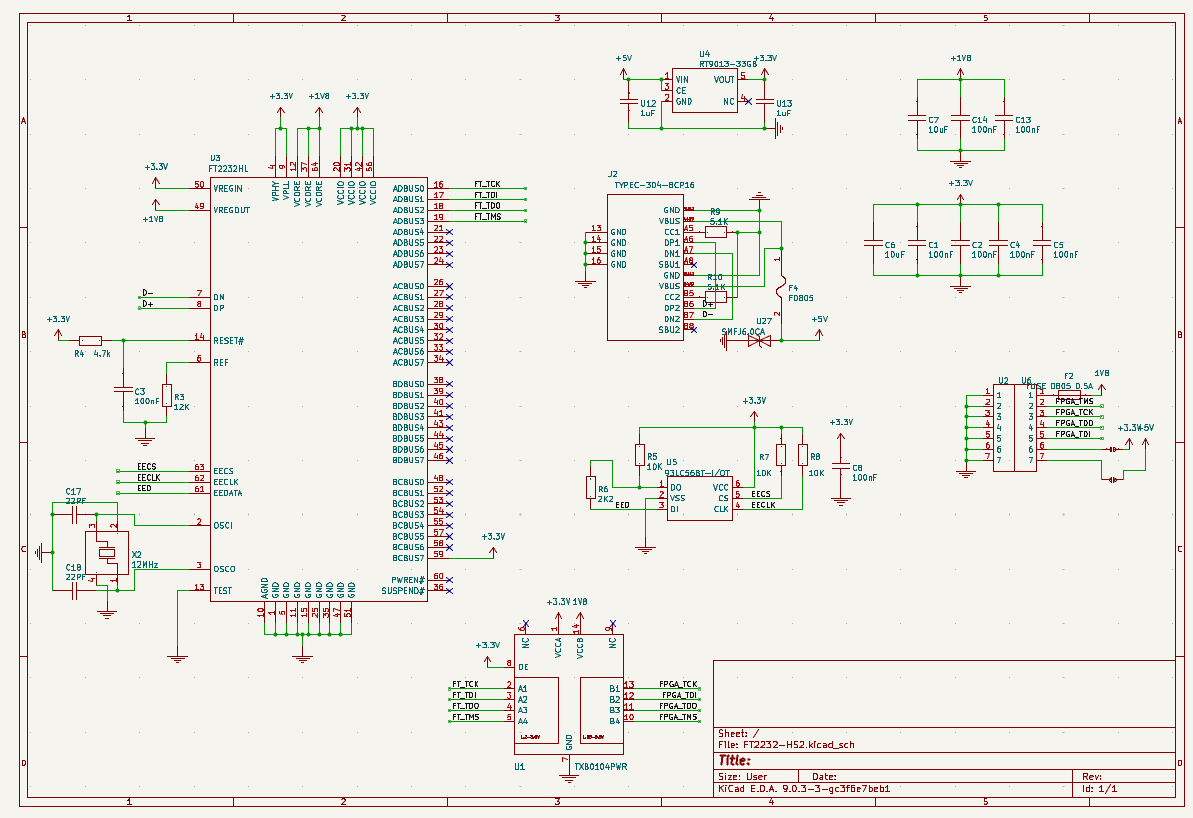

原理图

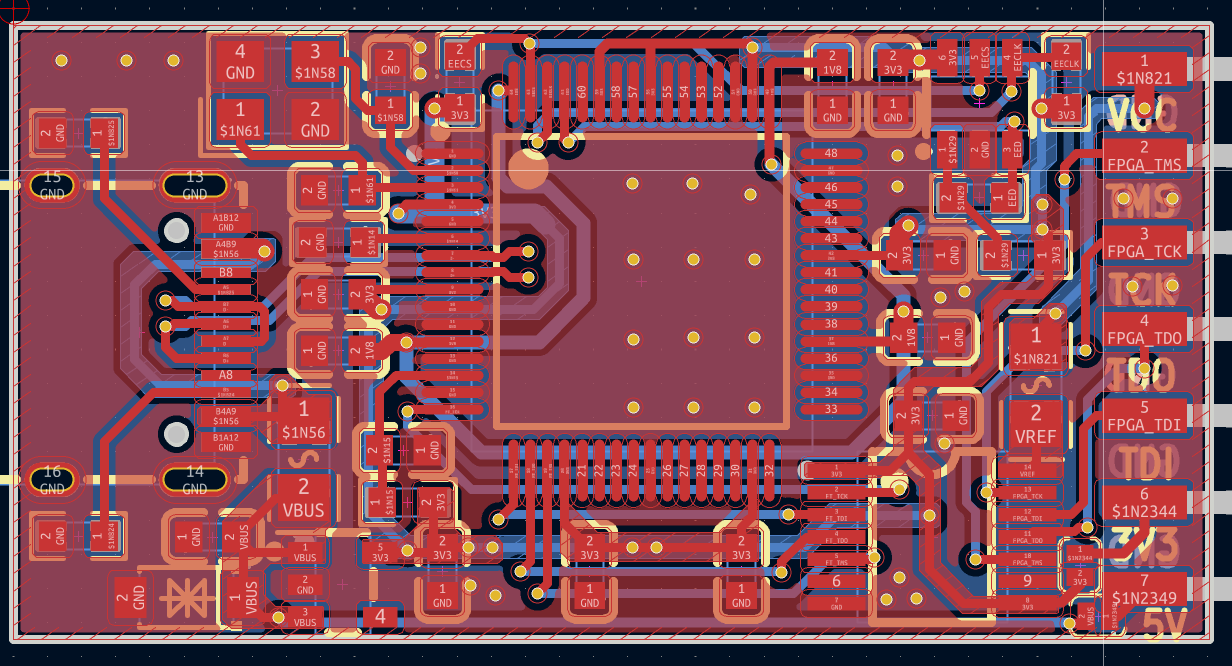

PCB图

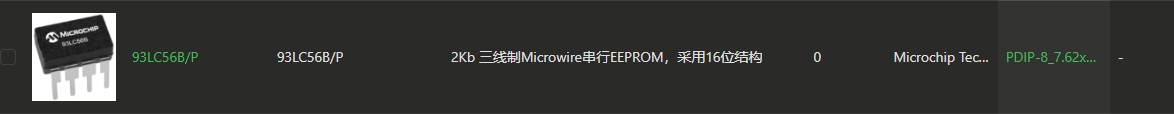

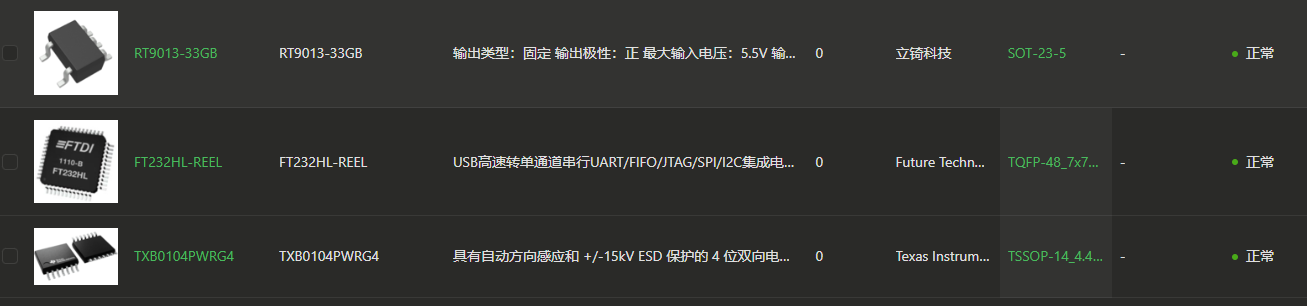

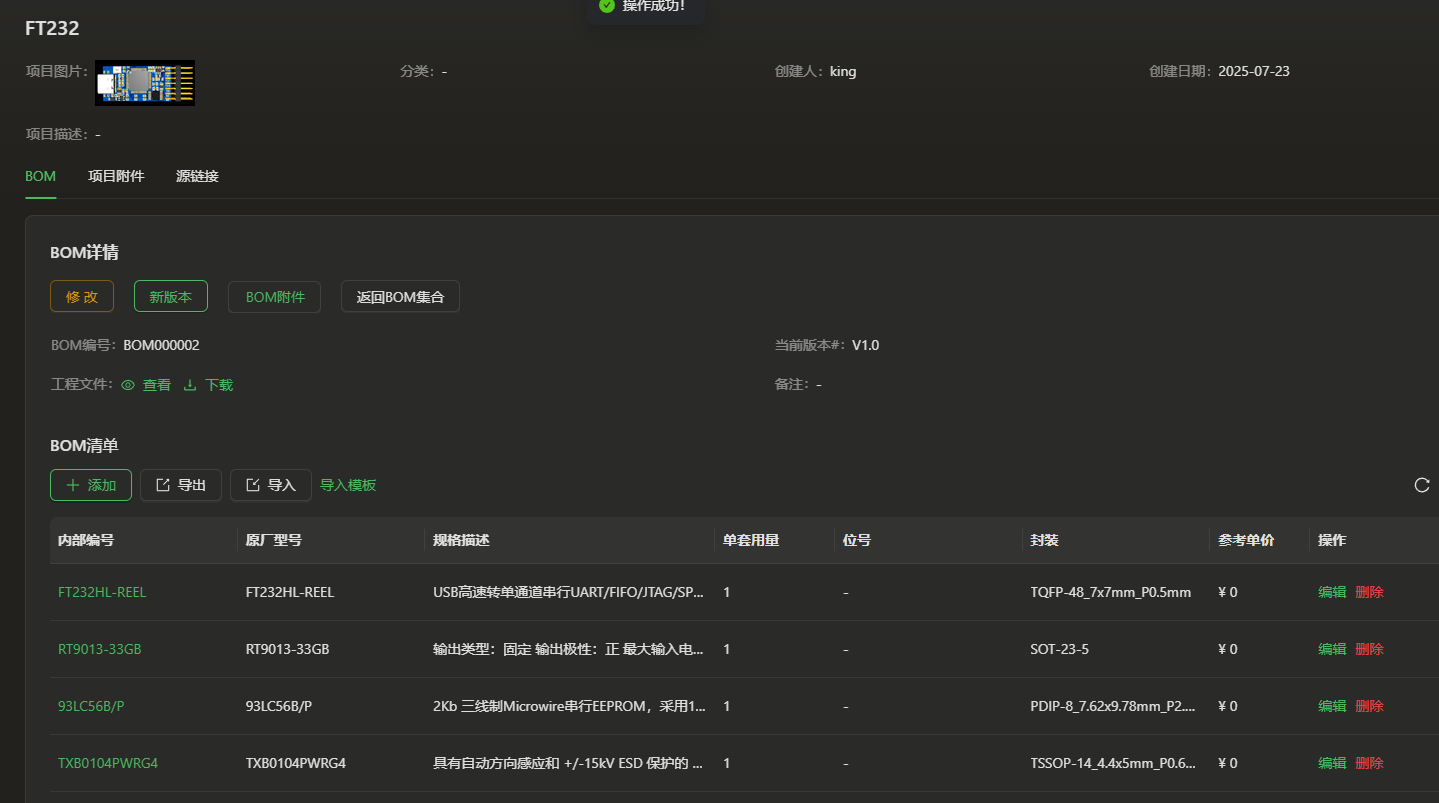

4/eZ-PLM上新建物料和项目的截图

5/物料请单

6/接口引脚定义

7/性能指标

参数 | 规格 | 应用影响 |

|---|---|---|

通信接口 | USB 2.0 High-Speed | 高速数据传输,支持JTAG |

JTAG 时钟频率 | DC – 30 MHz | 高频时钟适配高性能芯片,低频兼容老旧器件 |

电压兼容性 | 1.8V / 3.3V / 5V | 直接连接不同电压目标板,无需电平转换电路 |

通道数量 | 可配置为JTAG | 控制JTAG链调试多芯片 |

驱动支持 | 跨平台Windows/Linux/macOS等工具链 | 即插即用,无需额外开发驱动 |

FIFO 缓冲深度 | 4KB | 减少USB传输延迟,提升大数据量烧录稳定性 |

GPIO 数量 | 8×独立GPIO(可配置为上拉/下拉) | 扩展控制复位信号、LED状态等辅助功能 |

总结:

通过平台的任务,从中学习到了很多的规范与要求,并提高了自身的语言组织水平与PCB布板的要求,细节,进一步加深了我对PCB绘制的印象与熟练。