FPGA+R2R构成的DDS任意波形/信号发生器模块

1. 主要功能特性

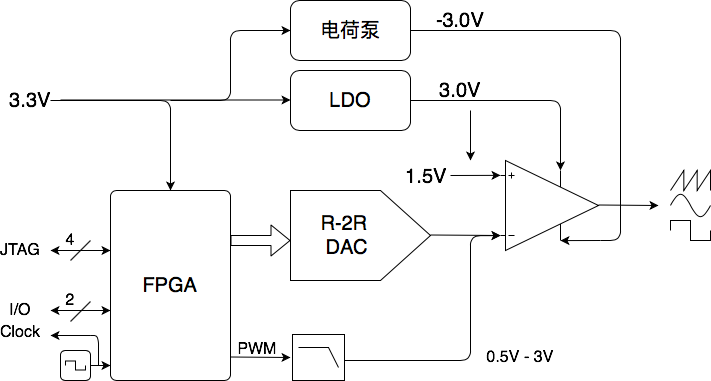

- 由Lattice XO2-1200HC FPGA + R2R DAC构成

- R2R DAC可以工作在200Msps/12bits

- 通过FPGA编程可以生成正弦波、三角波、锯齿波等常用波形,以及任意波形(通过内部RAM存储)

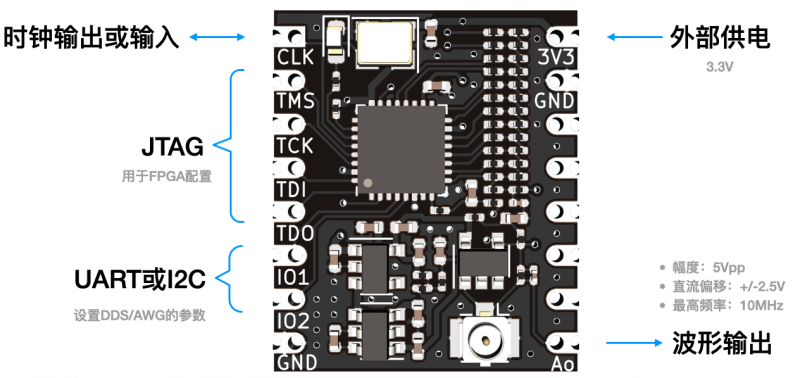

- 最高输出频率为10MHz,信号幅度最高设定为5Vpp,此两项参数可以通过调整输出模拟运放的型号以及电阻来调节

- 信号的频率调节精度以及幅度调节都可以通过FPGA的内部逻辑实现

2. 相关设计资源

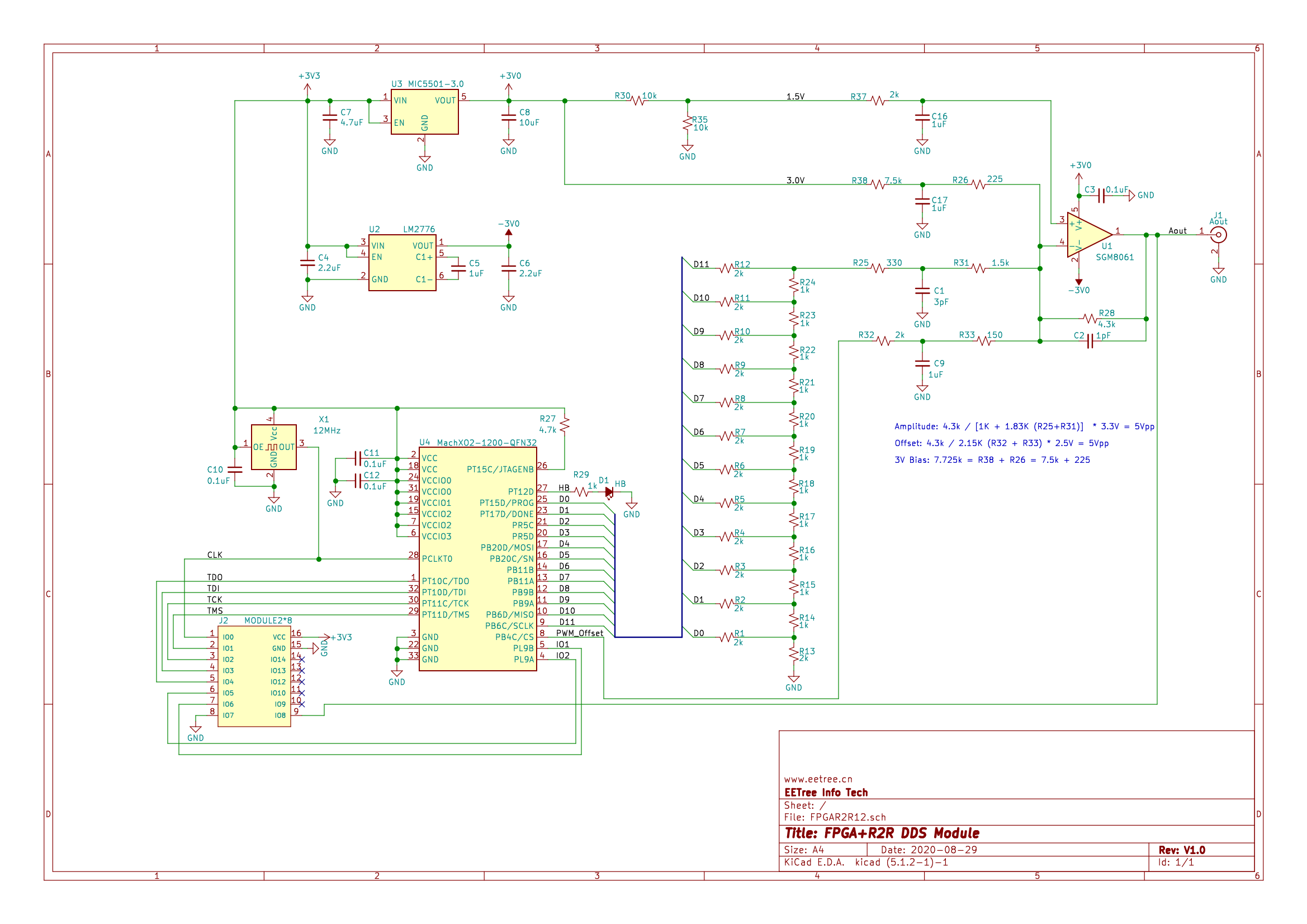

本设计中的模拟电路的参数按照DDS的转换率 > 50Msps来设定的(FPGA内部需要通过PLL进行倍频得到12的整数倍的高倍时钟),由于输出级运放固有的带宽限制,在2级LPF的情况下(通过电路中的C1和C2),20MHz以上的信号被加速滤除。

如果FPGA内部不使用PLL,只用12MHz的时钟作为DAC的转换时钟,则只能得到2MHz以内的模拟信号,C1和C2需要做相应的调节。

3. 相关器件资料

输出级的运算放大器可选为SGM8301、SGM8061、ADA4895等高速运算放大器,测试结果:

- SGM8301输出模拟信号带宽为5MHz

- SGM8061输出模拟信号带宽为10MHz

- ADA4895输出模拟信号3dB带宽为30MHz

以下是本设计中用到的核心器件的资料页面和数据手册: