内容介绍

内容介绍

1. 所选任务介绍

本项目选自电子设计竞赛训练题目。任务核心是设计并实现一个具备信号产生(DDS)、信号采集(ADC)、参数分析以及信号复现功能的闭环系统。主要性能指标包括:

- 输出端: 100Hz ~ 10kHz 正弦波,步进 100Hz,幅值 100mV ~ 500mV 可调。

- 输入端: 采集 1kHz ~ 10kHz 信号,测量幅值、有效值、频率。

- 高级功能: 5次谐波分量分析及原样信号复现。

2. 项目介绍

本项目是一个集成了数字信号处理(DSP)与嵌入式控制的综合系统。通过人机交互界面(旋转编码器与OLED),用户可以实时控制输出信号参数。系统不仅能产生高质量的正弦波,还能对外部输入信号进行实时采样与频谱分析,是典型的“信源+仪表”结合体。

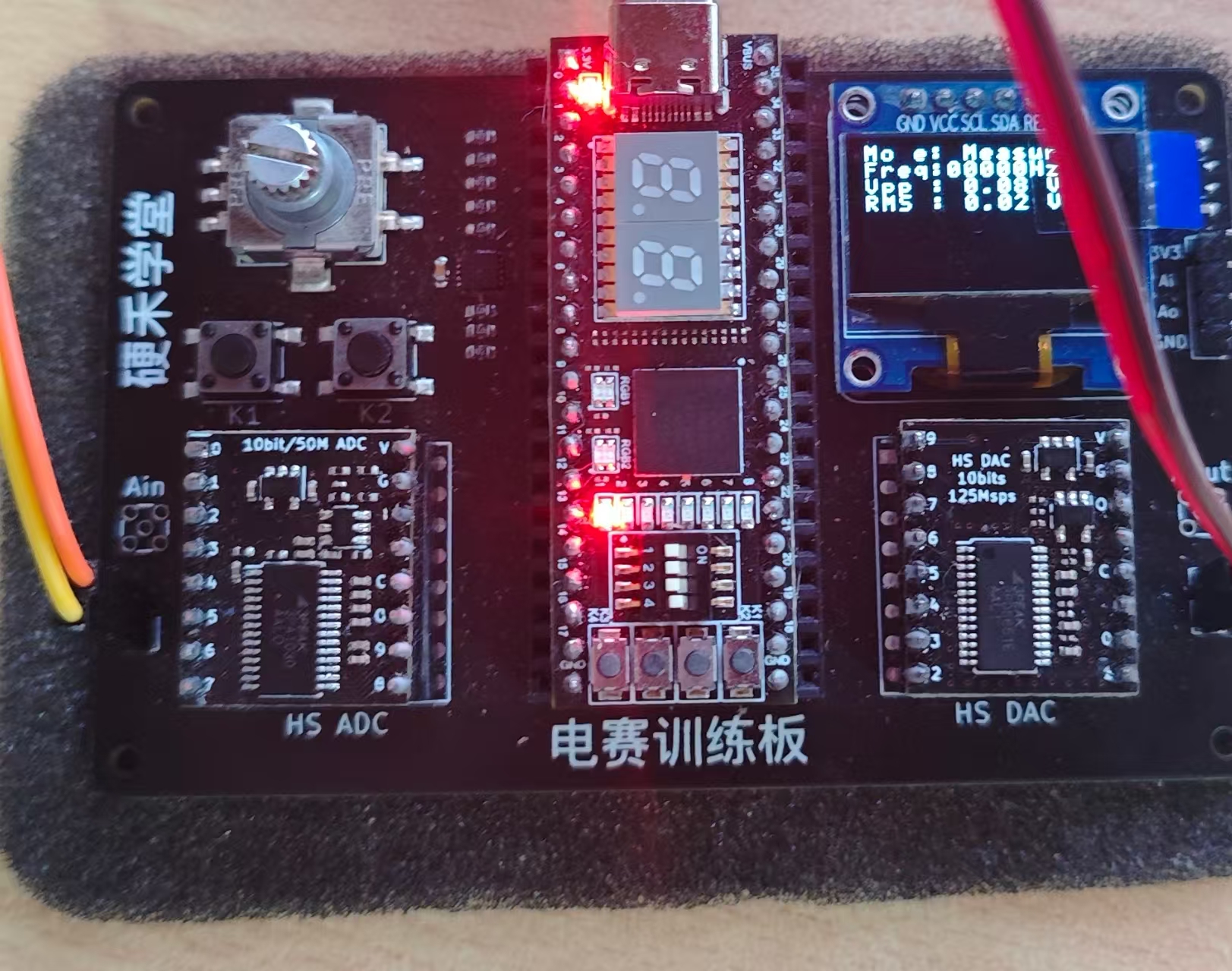

3. 硬件介绍

基于“小脚丫 FPGA”核心模块及配套电赛训练板,硬件主要组成如下:

- 核心模块: STEP-FPGA 核心板(负责高速逻辑、DDS算法及FFT计算)。

- 信息显示: 128*64 OLED 屏幕,用于显示波形参数、频谱分量及菜单。

- 信号发生(DAC): 10-bit/120Msps 高速 DAC,用于将数字波形转化为模拟信号。

- 信号采集(ADC): 10-bit/50Msps 高速 ADC,负责外部信号的实时数字化。

- 控制输入: 旋转编码器,用于调节频率步进和幅值。

- DDS 模块: 通过相位累加器和查找表(ROM)产生数字正弦波。

- ADC 采集模块: 驱动高速 ADC 进行等间隔采样,数据存入 FIFO/RAM。

- 处理模块: 对采集到的数据进行处理,提取基波及 2-5 次谐波的幅值 A。

- 复现逻辑: 将分析出的频率和幅值信息重新反馈给 DDS 模块,实现信号复现。

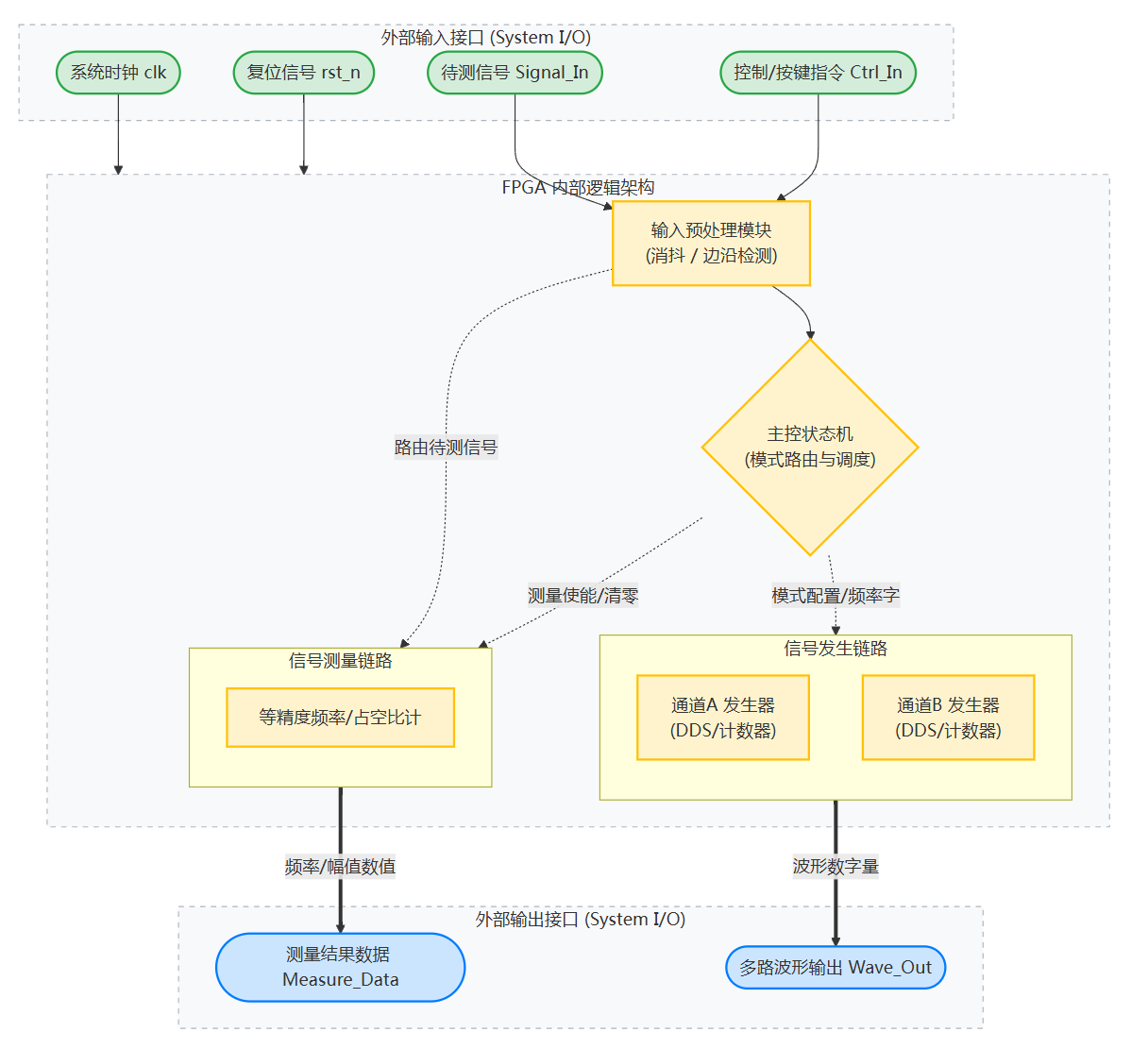

4.方案框图

硬件流程图

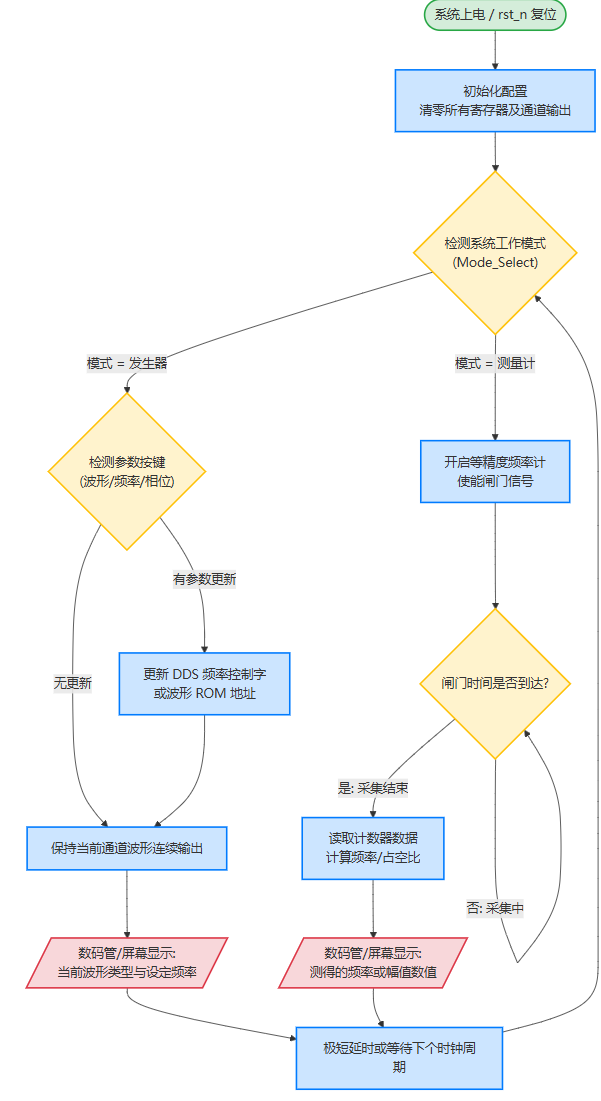

软件流程图

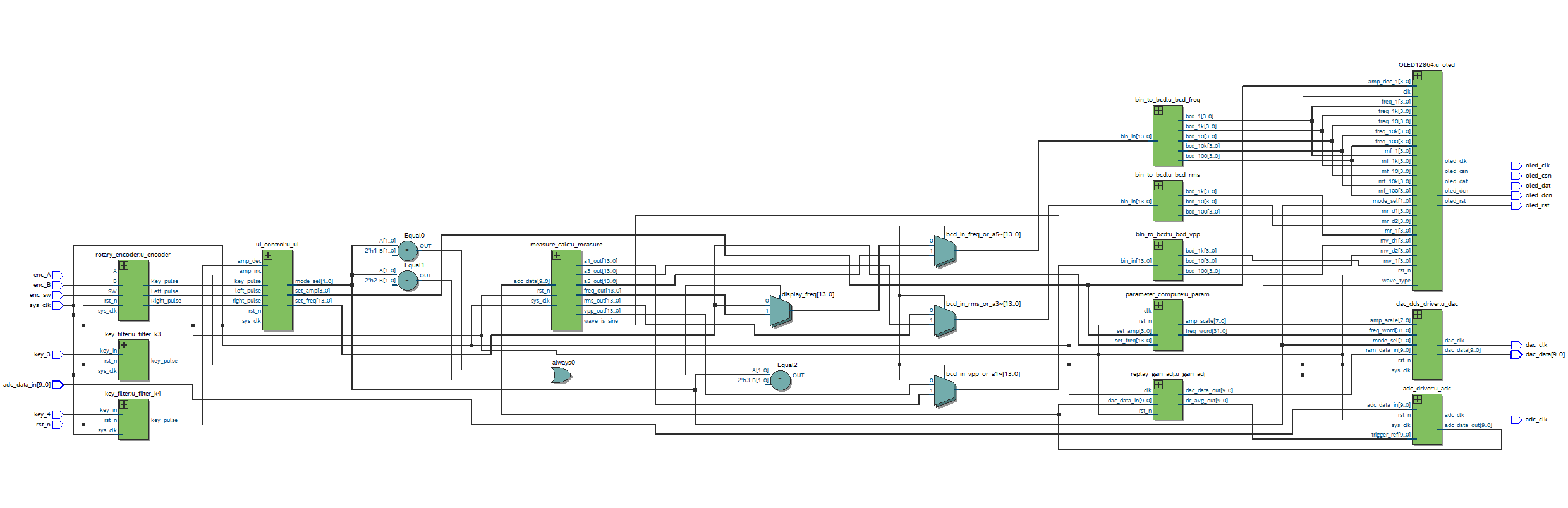

5. 调试软件、编程语言及关键代码

调试软件:Quartus

编程语言: Verilog HDL

下面节选累加器,幅度调节以及数值计算的关键代码。

// 1. 相位累加器 (决定输出频率)

always @(posedge sys_clk or negedge rst_n) begin

if(!rst_n) phase_acc <= 0;

else phase_acc <= phase_acc + freq_word; // freq_word 由外部设定

end

// 2. 幅度调制方法

// lut_out_signed: 查表得到的有符号正弦波

// amp_scale: 幅度缩放因子

always @(posedge sys_clk) begin

mult_temp <= lut_out_signed * $signed({1'b0, amp_scale});

end

// 3. 数据处理方法

// 右移 8 位并加上 512 (中点电压),将有符号数转换为 DAC 码值

wire [9:0] dds_calc_data = (mult_temp >>> 8) + 10'd512;

always @(posedge adc_clk) begin

// 冷却倒计时 (防止高频毛刺误触发)

if(trigger_cooldown > 0) begin

trigger_cooldown <= trigger_cooldown - 1'b1;

trigger_pulse <= 1'b0;

end

else begin

// 1. 下限检测

if (adc_data_out < (trigger_ref - 10'd6))

trigger_armed <= 1'b1;

// 2. 上限检测

// 只有先经过下限(Arming)再冲过上限,才产生触发脉冲

else if ((trigger_armed) && (adc_data_out > (trigger_ref + 10'd6))) begin

trigger_pulse <= 1'b1; // 发射同步脉冲

trigger_armed <= 1'b0; // 重置状态

trigger_cooldown <= 16'd200; // 进入冷却期

end

end

end

6. 功能展示图及说明

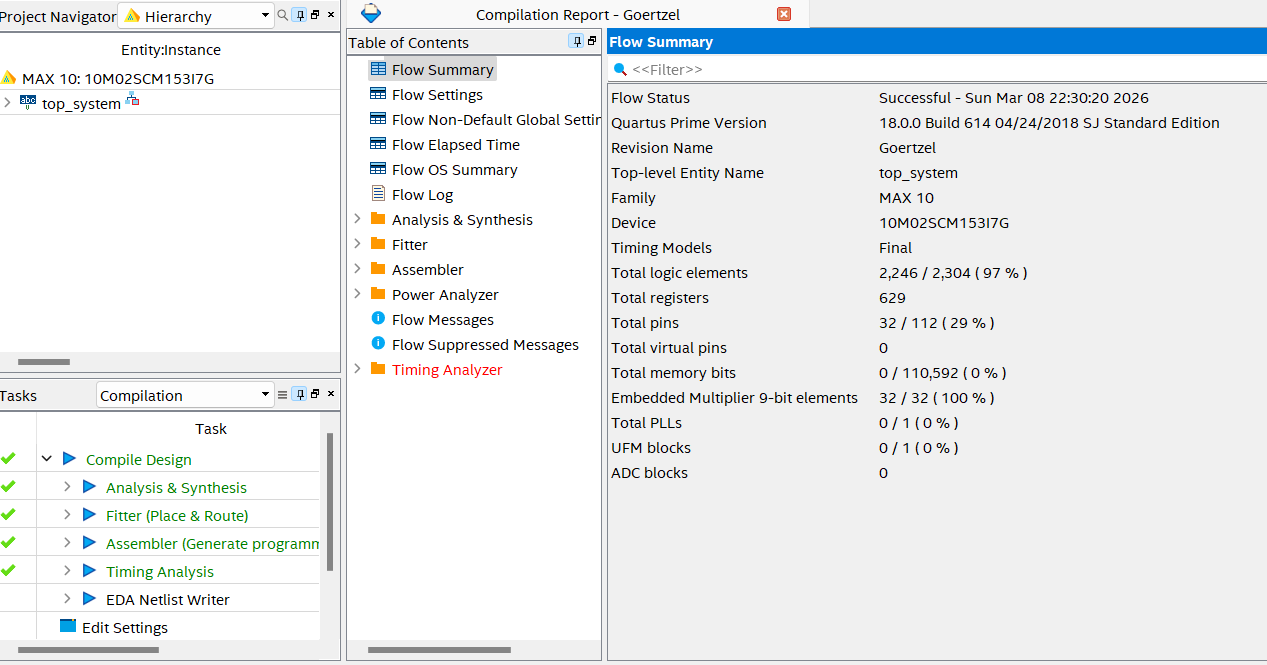

资源占用

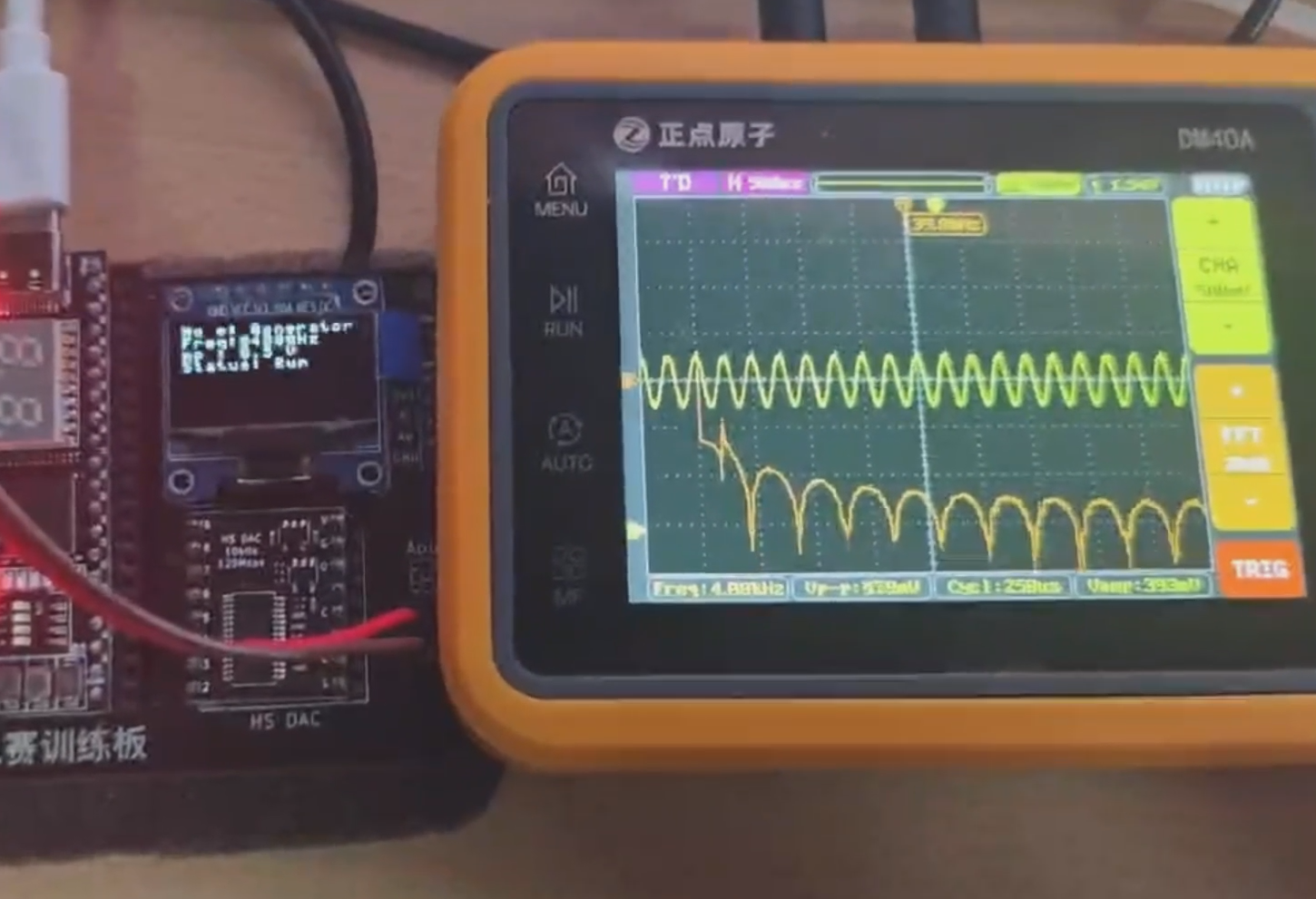

信号发生器:生成4800hz vpp=0.5v的正弦波

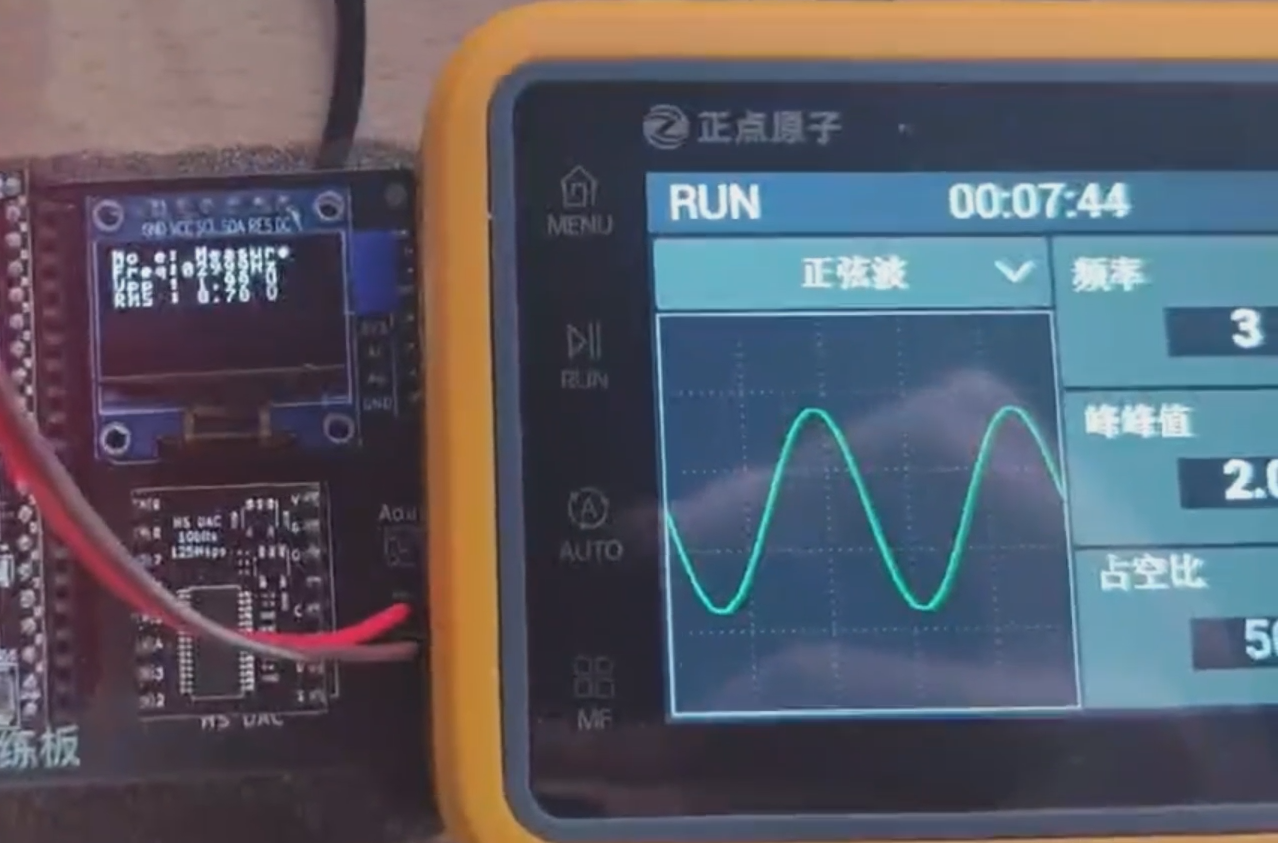

信号测量:测量3khz vpp=2v的正弦波测量到2999hz,vpp=1.99

7. 项目中遇到的难题及解决方法

- 难题 A:低幅值信号的精度问题。 当输出要求 100mV 时,DAC 量化噪声明显。

- 解决: 优化 ROM 表精度,并在硬件后端增加低通滤波电路以平滑波形。

- 难题 B:FFT 运算资源占用过大。

- 解决:试图通过Goertzel方式进行频率解算,但还是无法处理谐波分量,项目中最后选择了直接数值计算。

- 难题 C:信号复现时的失真。

- 解决: 引入校准系数,对 ADC 采集到的幅值进行补偿,确保复现误差在 10% 以内。

- 难题 D:精简OLED字库后,部分字母无法显示

- 解决: 读取地址的偏移量不匹配。

8. 心得体会

通过本次项目,我深入理解了数字信号处理在 FPGA 上的硬件实现过程。从底层的 ADC/DAC 时序驱动,到频谱分析,每一步都要求严谨的逻辑时序。笔者在这之前没有接触过FPGA,面对复杂的Verilog语言 感到颇为吃力,很多代码实现还是依赖Gemini的帮助。

同时,这次FPGA开发经历让我开始“敬畏”硬件限制,以往做过的项目都接触不到开发板的上限,而进行频率处理时,那些复制的计算公式很容易超出开发板的计算能力。

附件下载

信号装置 demo.zip

本项目的quartus工程

团队介绍

陈智海--上海海事大学 2024级电子信息工程

团队成员

Applepie

评论

0 / 100

查看更多

猜你喜欢

制作FPGA电子琴1. 存储一段音乐,并可以进行音乐播放,

2. 可以自己通过板上的按键进行弹奏,支持两个按键同时按下(和弦)并且声音不能失真,板上的按键只有13个,可以通过有上方的“上“、”下”两个按键对音程进行扩展

john

2469

2026寒假练 - 用小脚丫FPGA的电赛训练平台实现基于高速ADC的数字频率计与幅度测量仪该项目使用了小脚丫FPGA的电赛训练平台,实现了基于高速ADC的数字频率计与幅度测量仪的设计,它的主要功能为:高速ADC采样、正弦波/方波频率测量、峰峰值幅度测量、方波占空比测量、七段数码管频率显示、OLED幅值与条形图显示、拨码切换显示模式与量程。。

wuling

49

2026寒假练 - 基于小脚丫FPGA的电赛训练平台实现声波数据通信收发器该项目使用了小脚丫FPGA的电赛训练平台、Verilog语言,实现了声波数据通信收发器的设计,它的主要功能为:实现BFSK声波数据通信收发并在OLED屏上显示。

飞到床头钻你被窝

48