任务介绍

AD9834 75MHz DDS函数发生器

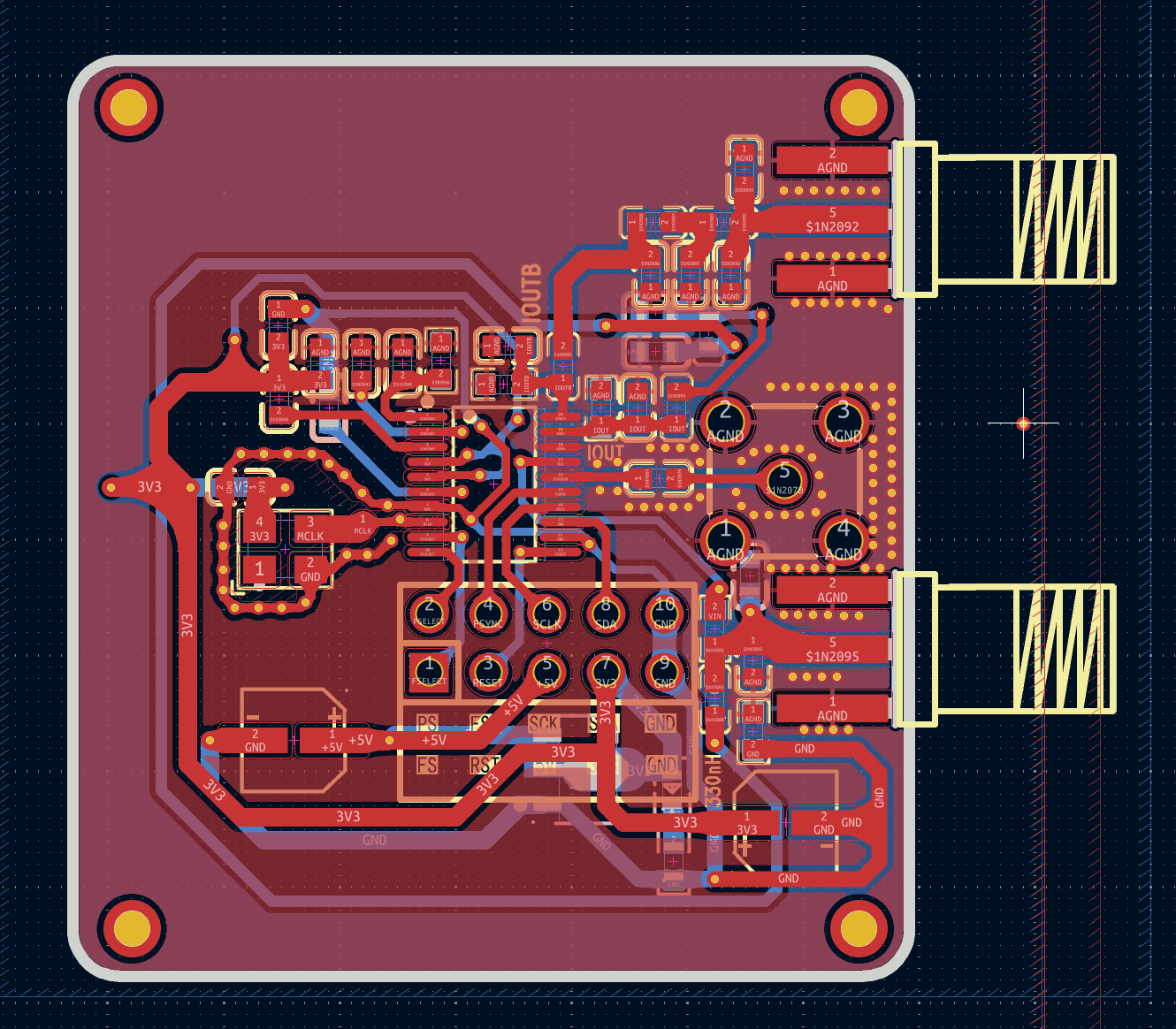

计一款DDS信号产生模块能够生成最高频率不低2MHz的正弦波/三角波/方波信号,板卡尺寸小于40mmx40mm,

输入信号采用2.54mm的插针,输出信号采用采用2.54mm的插针和SMA射频连接器,器件需在DigiKey官网上有货且正常售卖。根据任务要求本次我们选用的是AD9834BRUZ-REEL芯片设计一款AD9834BRUZ-REEL是一款75MHz低功耗直接数字频率合成器,主要用于生成各种波形信号,满足通信、测试、传感器等领域对频率合成及信号产生的需求。具体如下: - 频率刺激与波形产生:可产生高性能正弦波和三角波输出,片内集成比较器还能支持产生方波,用于时钟发生等场景。-频率相位调谐和调制:具备相位调制和频率调制功能,通过串行接口加载寄存器来改变频率和相位,可实现0.28Hz的分辨率(75MHz时钟速率时),能满足一些需要精确频率和相位控制的应用。

模块介绍

主要用于生成各种波形信号,满足通信、测试、传感器等领域对频率合成及信号产生的需求。具体如下: - 频率刺激与波形产生:可产生高性能正弦波和三角波输出,片内集成比较器还能支持产生方波,用于时钟发生等场景。-频率相位调谐和调制:具备相位调制和频率调制功能,通过串行接口加载寄存器来改变频率和相位,可实现0.28Hz的分辨率(75MHz时钟速率时),能满足一些需要精确频率和相位控制的应用。

AD9834 75MHz DDS

AD9834BRUZ-REEL Analog Devices Inc.

RF2-04A-T-00-50-G

AMS1117-3.3S

KC2016Z75.0000C1JX00

KC2016Z75.0000C1JX00 KC2016Z75.0000C1JX00

原理图和PCB模块介绍

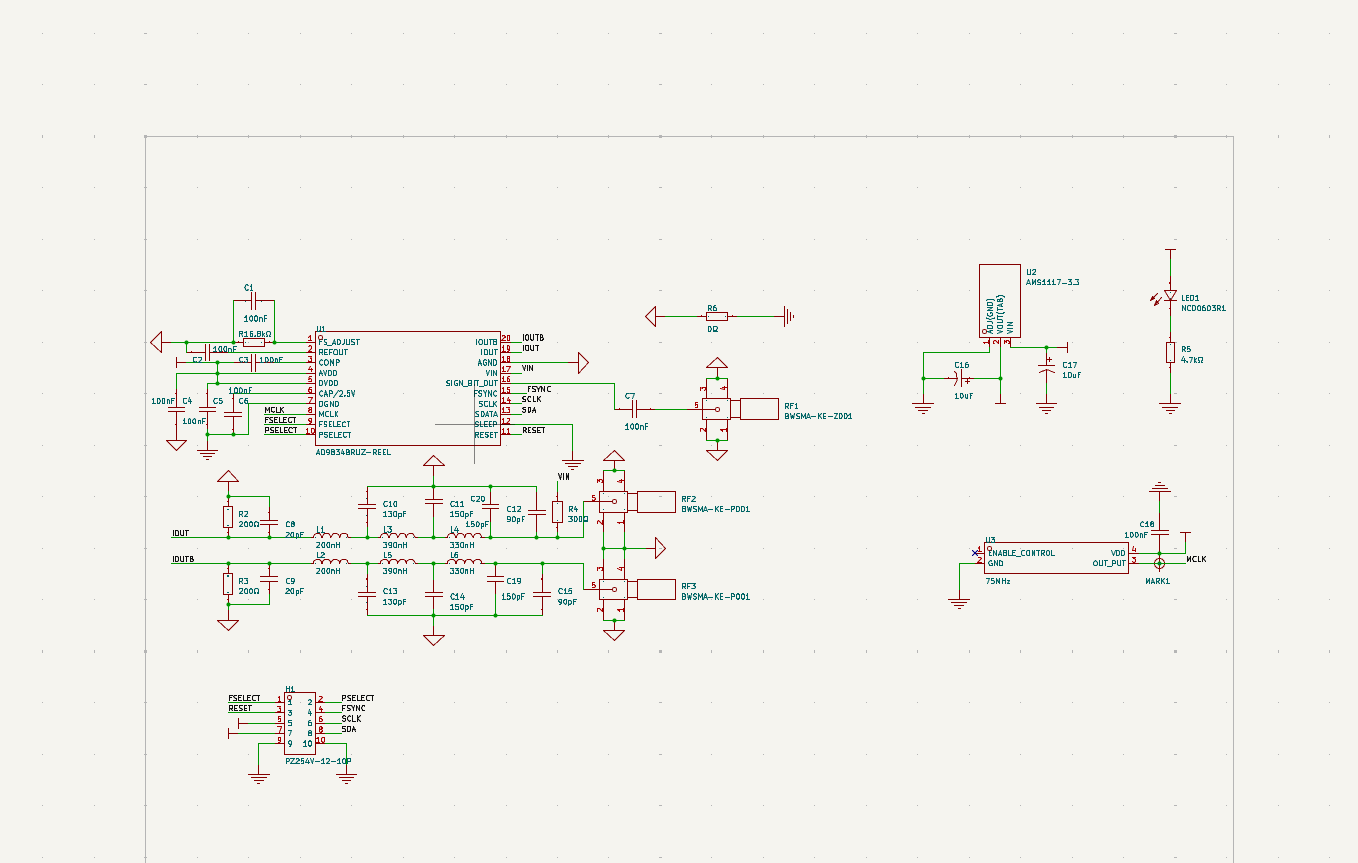

原理图

一、AD9834BRUZ-REEL主要性能指标

1.电源电压:范围为2.3V至5.5V,模拟和数字部分可采用不同电源供电。

2. 功耗:3V供电时功耗为20mW,适合对功耗敏感的应用。

3.输出频率:最高可达37.5MHz。

4. 频率分辨率:频率寄存器为28位,75MHz时钟速率下分辨率为0.28Hz,1MHz时钟速率下分辨率为0.004Hz。

5.波形输出:可产生高性能正弦波和三角波输出,片内集成比较器,支持产生方波用于时钟发生。

6.串行接口:三线式串行接口,最高时钟速率40MHz,与DSP和微控制器标准兼容。

7.温度范围:扩展温度范围为−40°C至+105°C。

8.封装形式:采用20引脚TSSOP封装。

9.窄带SFDR:大于72dB。

二、管脚定义

(一)AD9834BRUZ-REEL 主要管脚定义

1. COMP(3 脚):DAC偏置引脚,用于对DAC偏置电压进行去耦。

2.SIGN BIT OUT(16):逻辑输出。

3.CAP/2.5V(6 脚):数字电路的电源引脚,通常由内部稳压器从VDD产生2.5V电源。若VDD小于或等于2.7V,该引脚应直接连接到VDD。

4. DGND(7 脚):数字地。

5.AGND(18脚):模拟地。

6. SCLK(14脚):串行时钟输入,数据在SCLK的每个下降沿移入芯片。

7.SDATA(13 脚):串行数据输入,16位串行数据字通过此引脚输入。

8.FS ADJUST(1 脚):满量程调整引脚,与AGND之间连接一个电阻RSET,用于决定满量程DAC电流的幅度。

9. REFOUT(2 脚):基准电压输出引脚,提供1.20V内部基准电压源。

10. VIN(17 脚):比较器输入引脚,可利用比较器从正弦DAC输出产生方波。

(二)其他管脚定义

1.AVDD(4脚):模拟部分的正电源,为芯片模拟电路提供工作电压。

2.DVDD(5脚):数字部分的正电源,给芯片数字电路供电,可与AVDD不同。

3. MCLK(8脚):数字时钟输引脚,为芯片内部数字电路提供时钟信号。

4. FSELECT(9脚):频率选择输入引脚,用于选择不同的频率控制模式或频率范围等相关功能。

5.RESET(11脚):高电平有效数字输入引脚,用于将芯片内部寄存器等复位到初始状态。

6.SLEEP(12脚):高电平有效数字输入引脚,用于控制芯片进入休眠模式,以降低功耗。

7.FSYNC(15脚):低电平有效控制输入引脚,用于同步数据传输,告知AD9834控制寄存器的内容将改变。

8.IOUT(19脚):电流输出引脚,DAC转换后的电流信号从该引脚输出。

9.IOUTB(20脚):互补电流输出引脚,与IOUT输出互补的电流信号,可用于差分输出等应用场景。

10.PSELECT(10脚):相位选择输入端,用于控制相位寄存器PHASE0或PHASE1,其状态(0或1)决定选择哪个相位寄存器,该寄存器的值会增加到相位累加器的输出。

三、板上设置及标识

(一)电源设置

采用2.3 V至5.5 V电源供电。模拟和数字部分彼此独 立,可以采用不同的电源供电;例如,AVDD可以是5 V,而DVDD可以是3 V。

(二)寄存器内部设置

通过SPI接口向AD9834的控制寄存器写入控制字。AD9834包含16位控制寄存器,例如要告知控制寄存器内容将改变,需将DB15和DB14置0。通过特定的位设置可选择频率寄存器、相位寄存器等进行操作,其中b15和b16用于地址频率寄存器,b14、b15和b16设置为11时用于地址相位寄存器。

(三)输出设置

1.波形类型:默认正弦波;利用内部比较器可生成方波;通过特定寄存器设置可输出三角波。

2. 输出频率:根据系统时钟MCLK,按公式计算频率字,经SPI写入频率寄存器。

3.输出相位:通过PSELECT引脚或控制位选择相位寄存器(PHASE0/1),写入相位值。

4.其他:初始化时可置位RESET避免杂散输出;通过FS ADJUST引脚接电阻RSET调整DAC满量程电流。

(四)标识说明

1.型号核心部分“AD9834”:代表该器件的基础型号,明确其为低功耗直接数字合成(DDS)芯片。

2.“BRUZ”:是型号后缀,用于区分具体规格,其中“B”可能与工作温度范围(−40°C至+105°C)相关,“R”表示封装类型为TSSOP,“U”可能涉及特定工艺或版本,“Z”通常表示无铅环保封装。

3. “-REEL”:表明该器件的供货形式为卷带包装,适用于自动化贴片生产,方便批量焊接组装。

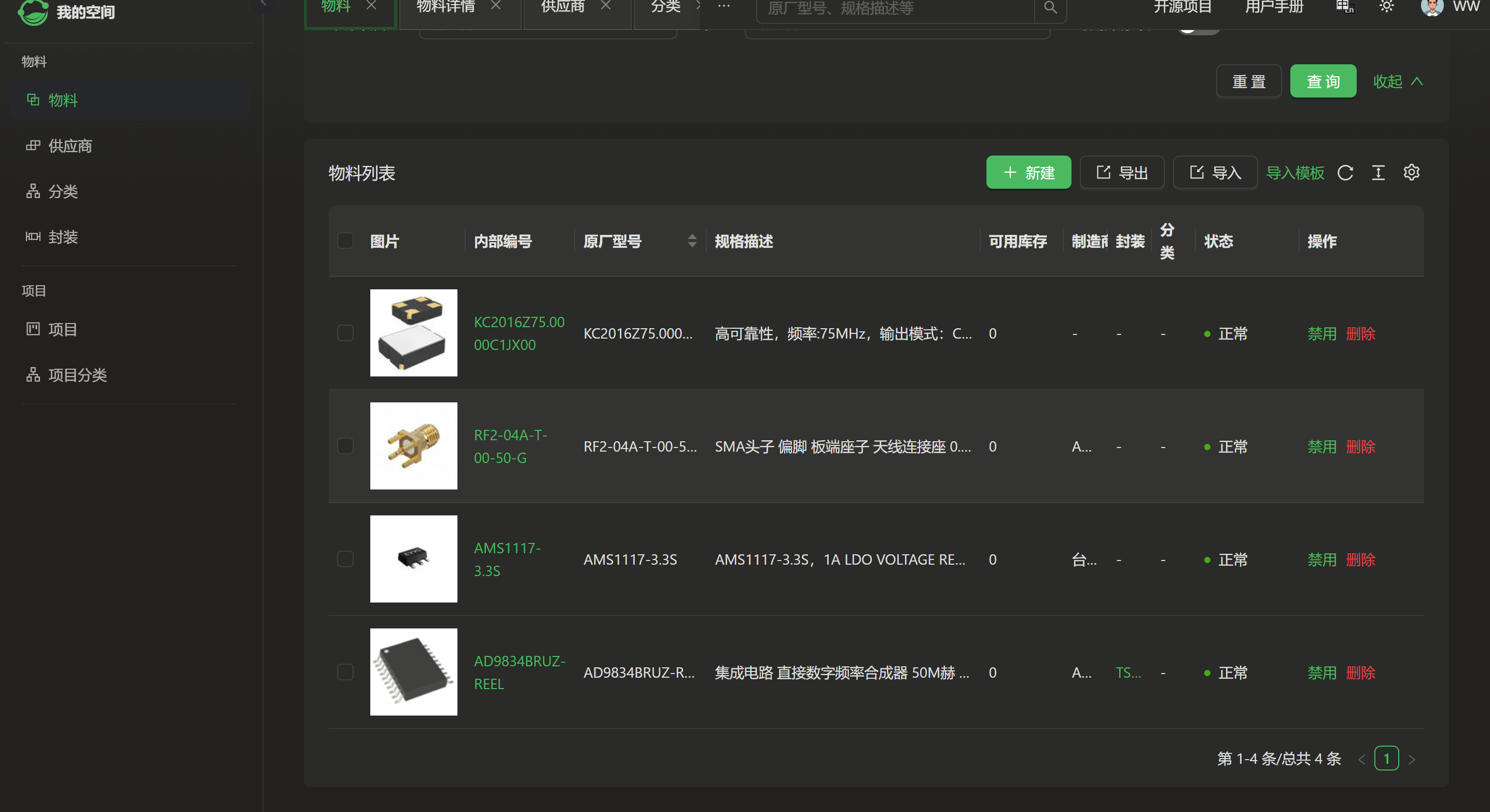

eZ-PLM上新建物料和项目的截图

物料截图

项目详情图

心得体会

用AD9834BRUZ-REEL设计函数发生器时,使我深刻体会到“细节决定成败”,尤其在硬件实现层面,这些经验将是我以后宝贵的财富。首先电源滤波与信号隔离是基础。AD9834的模拟部分AVDD和数字部分DVDD需分开供电,且电源入口处要加滤波电容比如100nF陶瓷电容就近接地,否则数字电路的开关噪声会串入模拟输出,导致波形失真。高频时钟线用75MHz系统时钟更要远离模拟信号线,必要时用地线隔离,避免电磁干扰影响输出纯度。然后布线的信号完整性会直接影响性能。AD9834的串行接口SCLK、SDATA、FSYNC虽速率不算极致,但高频下若布线过长或阻抗不匹配,容易出现信号反射,导致控制指令传输错误,如频率控制字写错,输出频率跑偏。时钟线尤其要短且直,最好走在接地平面上,减少辐射干扰。再者,电磁兼容性EMC需提前规划。布局时要区分数字区微控制器、接口电路和模拟区,AD9834、输出缓冲电路,地平面尽量完整,避免分割不当导致地电位差,曾试过因模拟地和数字地没处理好,三角波输出出现杂散毛刺,后来通过单点接地才解决。另外,前期参数匹配与后期调试便利性同样重要。在最后我深刻意识到管脚功能复用需反复核对手册。AD9834的部分引脚如比较器输入/输出有多重功能,如果不熟悉芯片手册上的引脚功能将比较器输出脚当作普通IO,会导致矩形波无法输出。调试时遇到过类似问题,翻遍手册才发现是管脚配置冲突,这也让我更明白:硬件设计不是简单的“接线”,而是从参数选型、布局布线到功能验证的全流程细节把控,每一步都不能马虎,在以后的实际应用中,要多练多看多学精炼自己的技术,在多种需求和环境条件下能轻松应对,争取对模块进行最优的合理选择及调整,以发挥其最佳结果。

团队:个人

工具:KIcad