FPGA在2019年全国大学生电子设计竞赛中的应用要点

收藏

分享

脑图

FPGA在2019年全国大学生电子设计竞赛中的应用要点

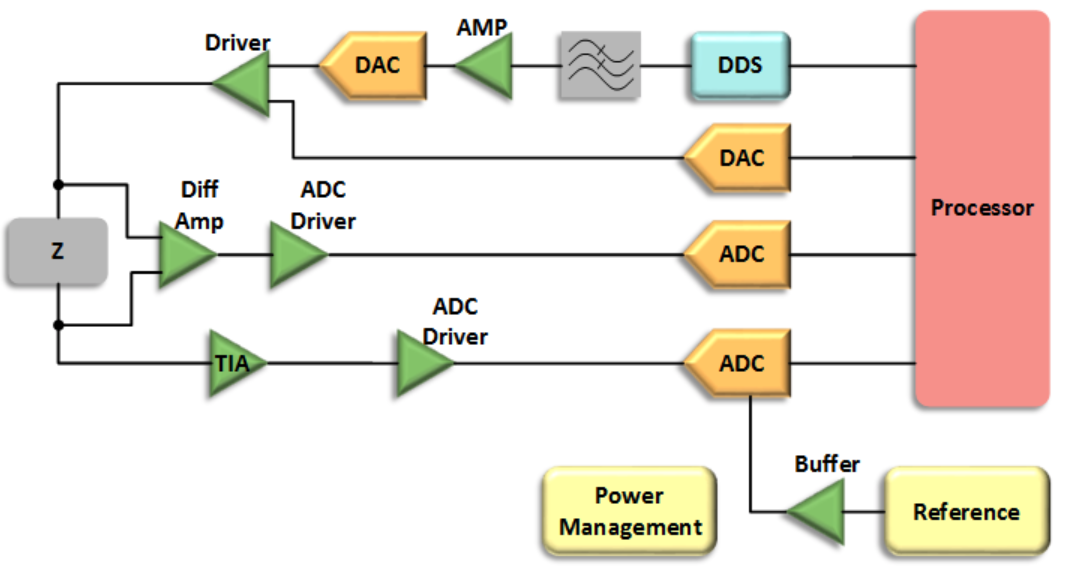

C题:线路负载及故障检测装置

参考方案框图 - 来自ADI的器件AD5933

自行搭建:FPGA + DAC + ADC + 运算放大器

FPGA的功能

+12bits 1Mbps DAC构成DDS系统,生成需要的信号

+ 12 bits 1Mbps ADC进行数据采集

进行离散傅立叶变换,将采集到的信号分解为实部和虚部

数字滤波 - 去除干扰信号

显示参数信息、状态报警

根据状态自动调整参数

FPGA参考资源

D题:简易电路特性测试仪

参考资料

FPGA参考设计

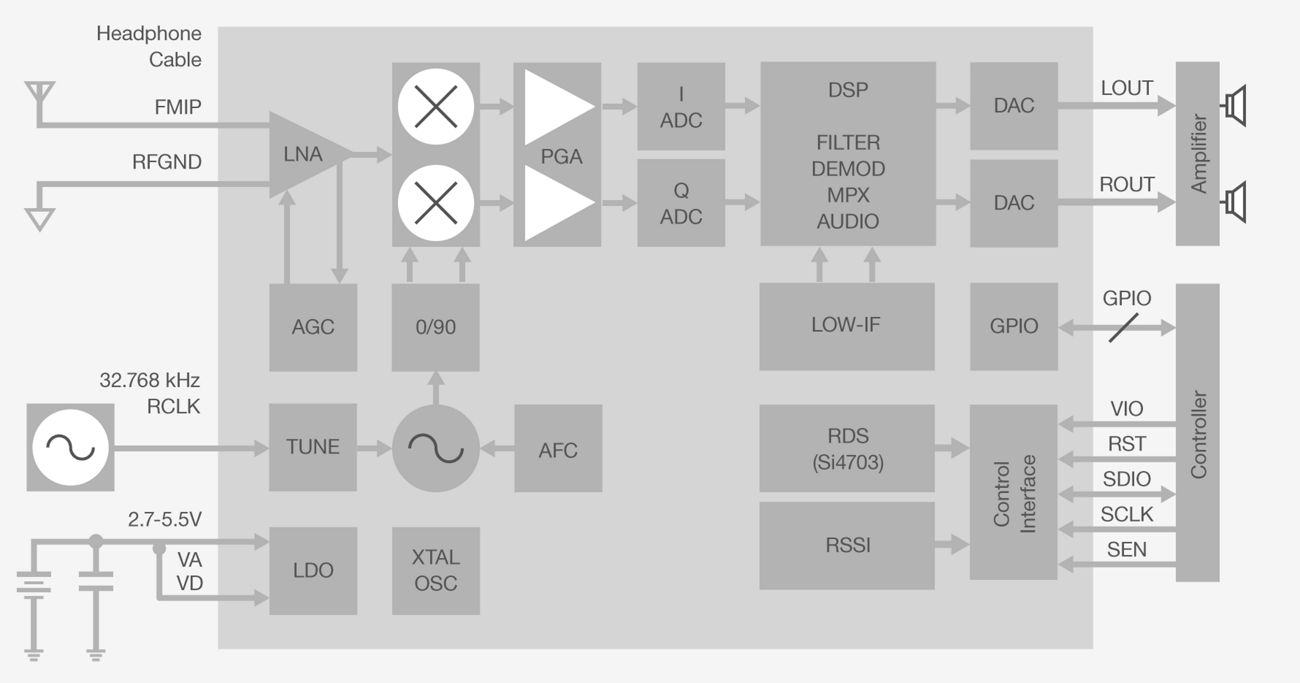

E题:基于互联网的信号传输系统

设计分析

考察点2 - 输出端和输入端的时钟同步,因此ADC和DAC采样时钟的选择是个挑战

考察点1:网络延时的自动测量与补偿,IEEE802.1AS有方案用于Layer 2以太网

输出端(C端):FPGA + 高速DAC + 低通滤波器 + 宽带放大器 + 带以太网口的嵌入式系统

FPGA用于将收到的IP数据包进行解包并以固定的速率送给高速DAC

DAC可选ADI、TI、美信的器件, 40Msps以上/10bits的比较合适

DAC输出端需要加低通滤波器,截止频率可以选在2MHz

低通滤波器之后需要加一个放大器,以驱动输出50欧的负载

整个模拟链路需要用MultiSim或其它仿真软件进行仿真以确定模拟链路各器件的值

输入端(A/B端):双路高速ADC + FPGA + 带以太网接口的嵌入式系统

ADC的采样率15Msps ~50Msps就可以

ADC的分辨率8位~10位即可

需要对输入信号做衰减 - 从5Vpp衰减到适合ADC采样的电压范围

如果采用10bit ADC,可以不接模拟开关,如果你用的ADC只有8位,建议在衰减后加一个模拟开关进行切换

在ADC之前最好加一个低阶的低通滤波器,截止频率可以选在2MHz以上,用于抗混叠

FPGA将10Msps/10bit的数字信号进行IP数据包的封装,送给以太网发送芯片

FPGA设计资源参考

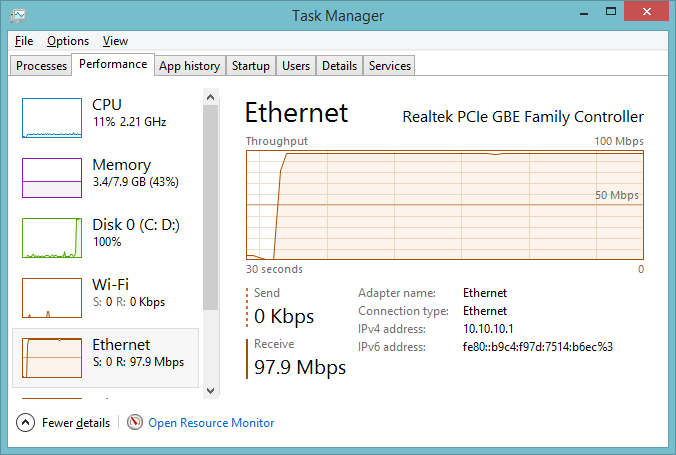

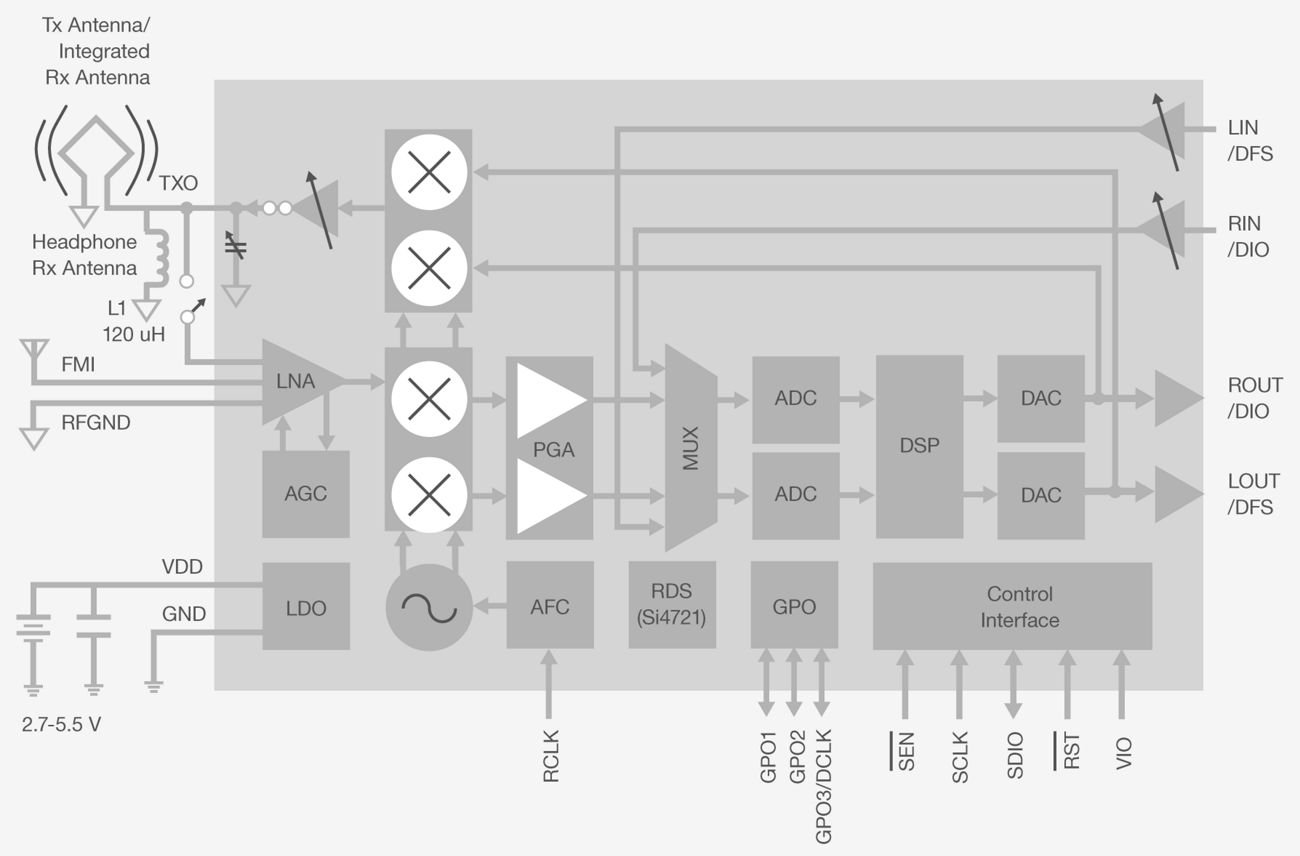

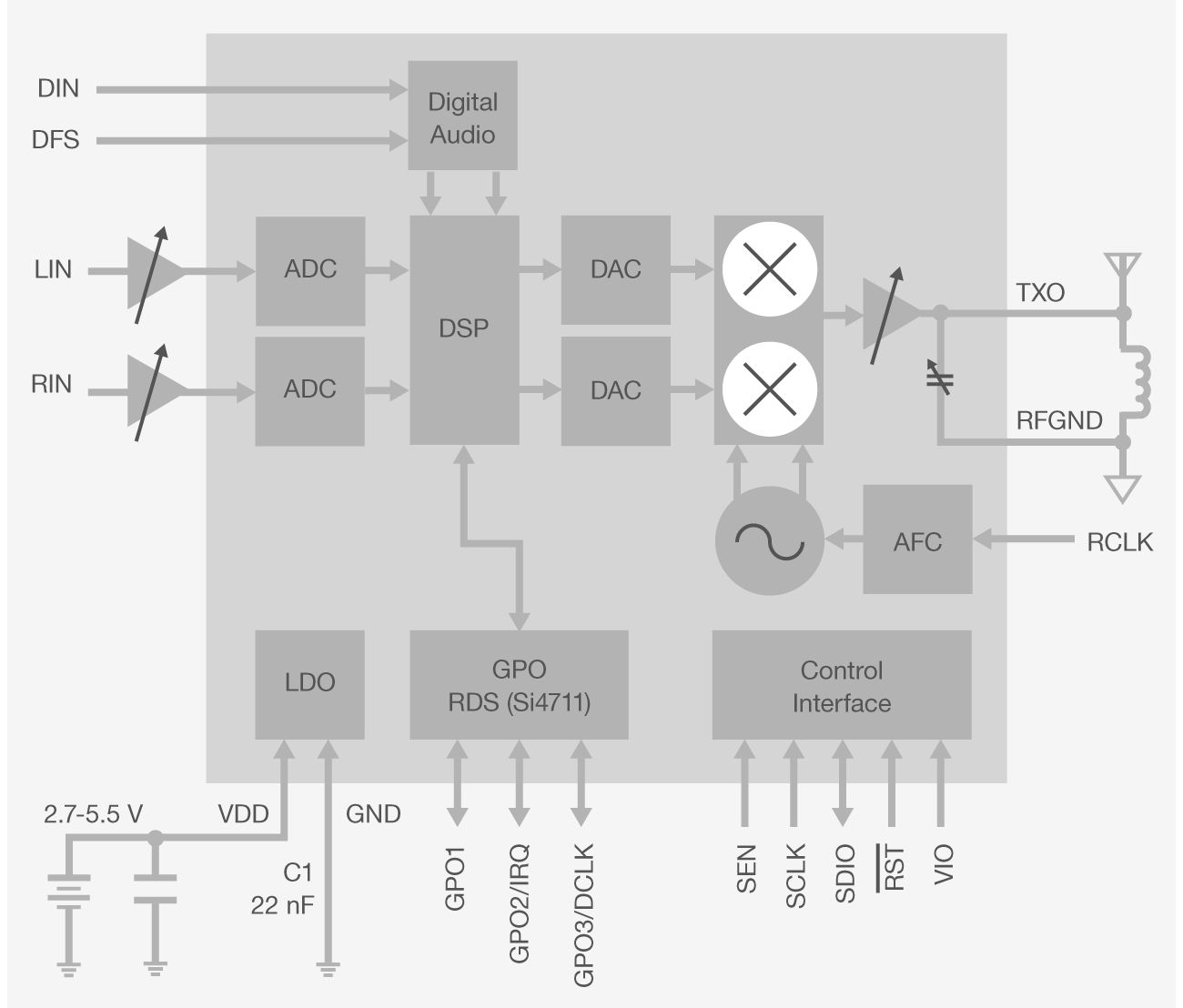

G题:双路语音同传的无线收发系统

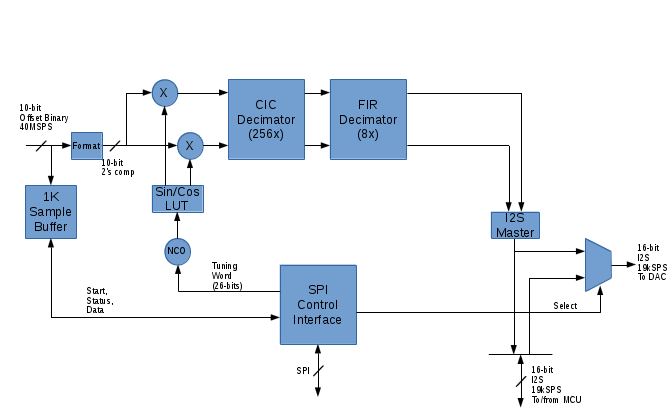

用数字的方式SDR来进行调制解调

评论

0 / 100

查看更多

2019-08-09

5743

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号