# FPGA APPLICATION ACCELERATOR & DEVELOPMENT BOARD

User's Manual and Release Notes

February 8, 2017

Copyright 2017 Alorium Technology

Downloaded from Arrow.com.

| Version | DATE          | AUTHOR    | CHANGES                                    |

|---------|---------------|-----------|--------------------------------------------|

| 1.0     | April 3, 2016 | mwebber   | Initial Version                            |

| 1.1     | Dec 14, 2016  | jpeterson | Added Best Practices section for SPI       |

| 1.2     | Feb 1, 2017   | hjuedes   | Updated 3.3 Reconfigurability Instructions |

| 1.3     | Feb 8, 2017   | Hjuedes   | Updated Register Summary description       |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

|         |               |           |                                            |

# **Table of Contents**

| 1 | Ove   | rview                                                  | 4  |

|---|-------|--------------------------------------------------------|----|

| 2 | Usag  | ge                                                     | 4  |

| 3 | Diff  | erences between XLR8 and Arduino Uno/Sparkfun RedBoard | 4  |

| - | 3.1   | USB                                                    |    |

|   | 3.2   | Xcelerator Blocks (XBs)                                | 4  |

|   | 3.3   | Reconfigurability                                      | 5  |

|   | 3.3.1 | Connecting to Ground                                   | 5  |

|   |       | I/0                                                    |    |

|   | 3.5   | ADC                                                    |    |

|   | 3.6   | Bootloader and ICSP header                             |    |

|   |       | I2C / Two Wire Interface (TWI)                         |    |

|   | 3.8   | UART                                                   |    |

|   | 3.9   | SPI                                                    |    |

|   | 3.9.1 |                                                        |    |

|   | 3.10  | Analog Compare                                         |    |

|   | 3.11  | EEPROM                                                 |    |

|   | 3.12  | Power<br>Pin13 LED                                     |    |

|   | 3.13  |                                                        |    |

| 4 | ATn   | 1ega328p features not implemented                      | 9  |

|   |       | Fuses                                                  |    |

|   | 4.2   | Power Reduction                                        |    |

| 5 | Xcel  | erator Blocks (XBs)                                    |    |

|   |       | Floating Point                                         |    |

|   | 5.2   | Servo Control                                          |    |

|   | 5.3   | NeoPixel Control                                       |    |

| 6 | Dog   | ister Summary                                          | 12 |

| U | 6.1   | XLR8 and XB Register Descriptions                      |    |

|   | 6.1.1 | <b>o i</b>                                             |    |

|   | 6.1.2 | · · · · · · · · · · · · · · · · · · ·                  |    |

|   | 6.1.3 | 1 0                                                    |    |

|   | 6.1.4 | 1 0                                                    |    |

|   | 6.1.5 | · · · · · · · · · · · · · · · · · · ·                  |    |

|   | 6.1.6 | <b>6</b>                                               |    |

|   | 6.1.7 |                                                        |    |

|   | 6.1.8 |                                                        |    |

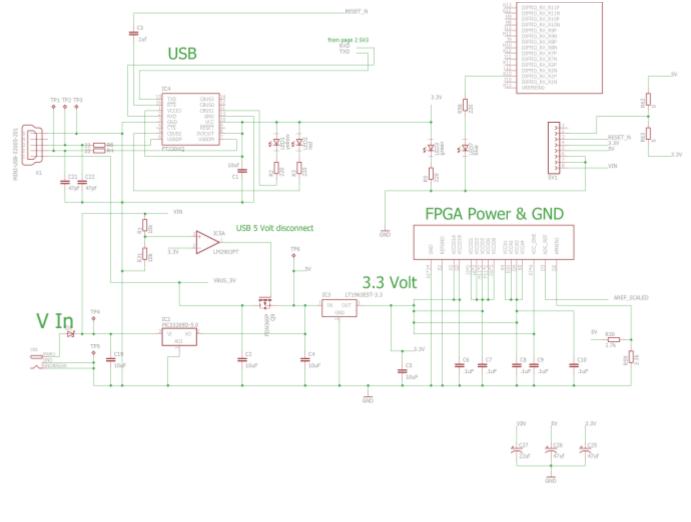

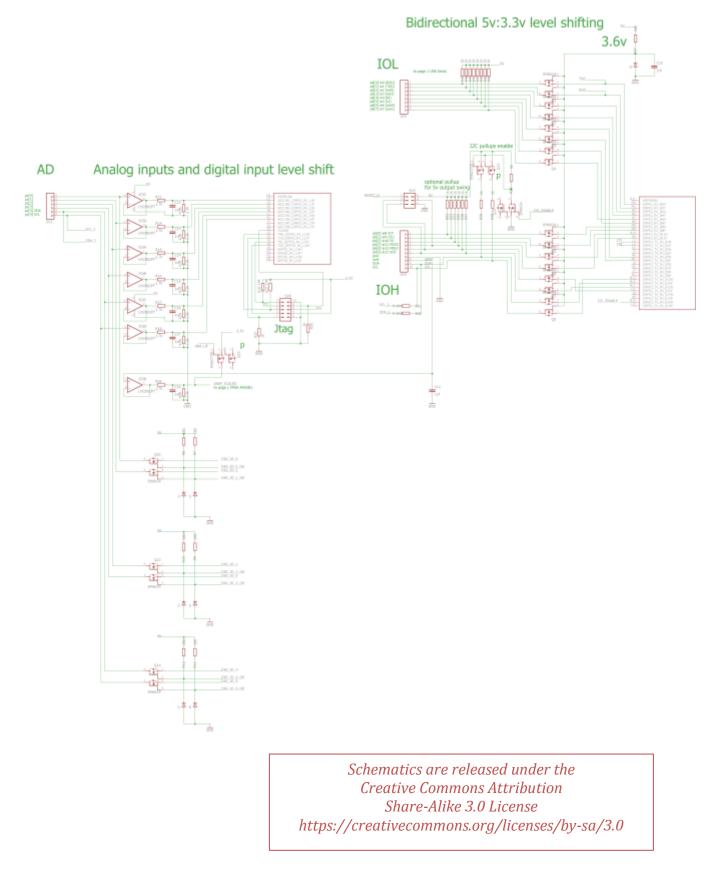

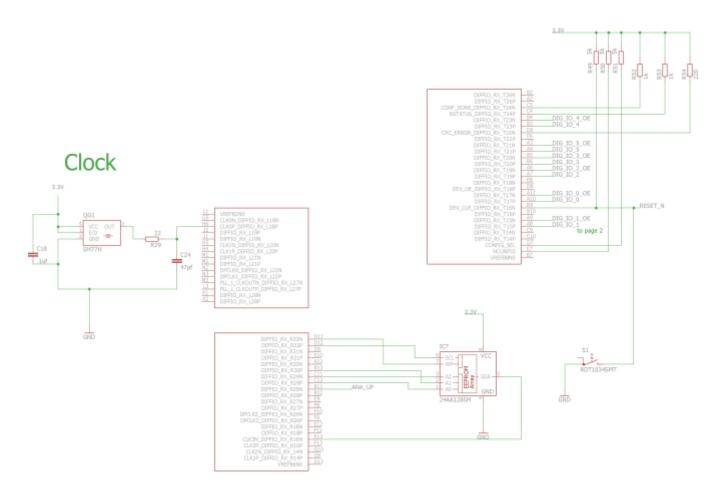

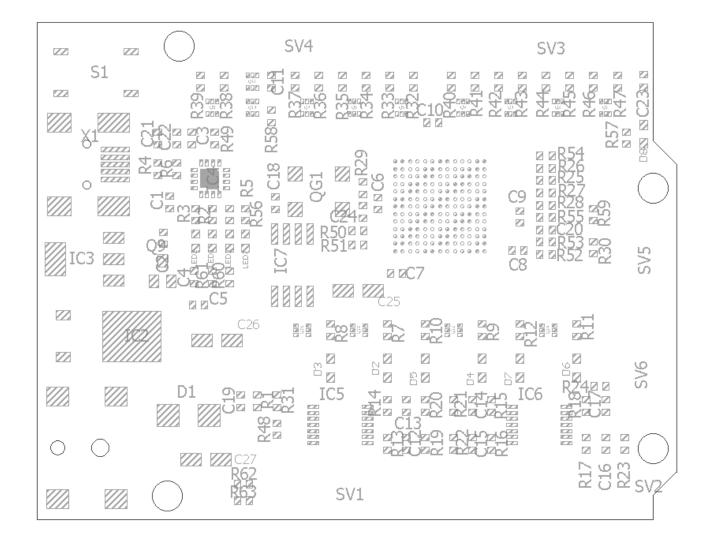

| 7 | Sche  | ematics and Layout                                     | 21 |

| 8 | Crea  | lits                                                   |    |

|   |       |                                                        |    |

# **1** Overview

XLR8 is an FPGA-based application accelerator and development board that has been specifically designed to look, feel, and act like a standard Arduino. It is programmed with the popular and easy to use Arduino IDE. The heart of XLR8 is an FPGA chip that is configured with an ATMega328 microcontroller clone as well as additional accelerator functions.

XLR8 provides an option for Arduino developers to achieve significantly improved performance in the same physical footprint and using the same tool chain as standard Arduino Uno and other similar Arduino compatible boards, even when incorporating custom hardware functions via accelerator blocks.

# 2 Usage

XLR8 can be programmed with Arduino sketches from the Arduino IDE by selecting "Arduino Uno" as the target board, in the same way as the Uno. The pin headers are compliant with the Arduino Uno R3 layout. It has the same analog pins, the same digital pins, and the same pins with PWM functionality as the Uno. So, using it as a clone of the Uno is a simple as using an Uno. The real fun starts after installing our Arduino Board package as described in the instructions at <a href="https://github.com/AloriumTechnology/Arduino Boards">https://github.com/AloriumTechnology/Arduino Boards</a>, enabling advanced features such as doubling the microcontroller's clock speed or utilizing Xcelerator Blocks (XBs). But you don't need to do that until you are ready.

# **3** Differences between XLR8 and Arduino Uno/Sparkfun RedBoard

### 3.1 USB

Similar to the Sparkfun RedBoard, XLR8 uses a USB mini-B connector and an FTDI chip to do the USB-to-Serial conversion, which is slightly different than the Uno. If you haven't already, you'll likely need to install FTDI drivers. Note that this is not needed and should not be done if you are using Mac OS El Capitan or later. The OS will have the correct drivers.

## Sparkfun has a great tutorial showing just how to do that

<u>https://learn.sparkfun.com/tutorials/how-to-install-ftdi-drivers</u>). We have noticed for the Mac that Sparkfun's tutorial doesn't mention restarting your computer after installing the driver, but we've generally needed to do that and everything has worked great afterwards. We have also noticed that the FTDI driver in older Linux kernels (specifically, version 2.6 or older) does not appear to support the newer FTDI chips that are used on XLR8, Sparkfun's RedBoard, and many other products. This can be fixed by upgrading your Linux kernel to version 3.10 or newer.

## 3.2 Xcelerator Blocks (XBs)

Xcelerator Blocks give XLR8 a performance advantage through a combination of custom hardware in the FPGA fabric along with a software library that is able to communicate with that hardware and make it easy for users to take advantage of the performance. The software libraries are available on our github site (<u>https://github.com/AloriumTechnology</u>), but it is

easy to install them without even going to github. In the Arduino IDE, go to the menu **Sketch -> Include Library -> Manage Libraries**, which will open the Library Manager in a new window. Enter **XLR8** in the search bar and you will find the entries for the various XLR8 libraries available. Click on the desired library and an **Install** button will appear for it.

### 3.3 Reconfigurability

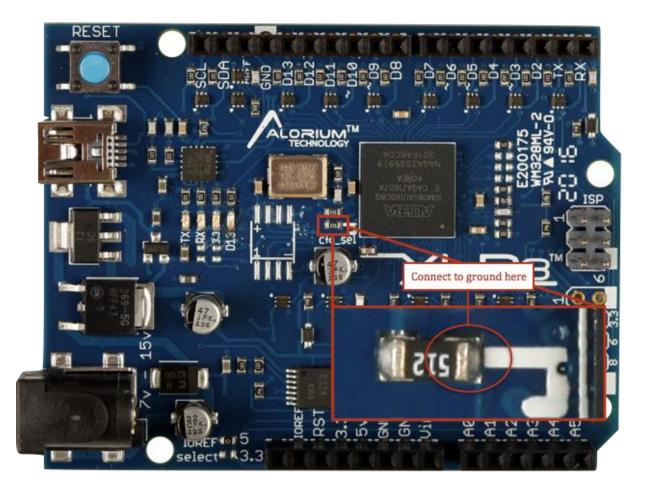

One of the most awesome things about XLR8 is its re-configurability. XLR8 is able to hold two different FPGA images. Image 1 can be reconfigured from the Arduino IDE to take advantage of increased functionality as new XBs are introduced. The reconfiguration files are obtained by installing our Arduino Board package as described in the instructions at <a href="https://github.com/AloriumTechnology/Arduino Boards">https://github.com/AloriumTechnology/Arduino Boards</a>. Image 0 is never changed and is typically unused unless the primary image 1 becomes corrupted. If necessary, a "factory reset" of XLR8 can be performed by grounding the FPGA side of R51 (cfg\_sel) while applying power to the board. It only takes a momentary grounding to cause this to happen. The factory image is then loaded. However, any attempt to run a sketch or reset after loading the factory image will lead to the bad image being reloaded. The user will immediately want to reburn a knowngood image into image 1 before attempting anything further.

#### 3.3.1 Connecting to Ground

## 3.4 I/O

The FPGA at the heart of XLR8 is a 3.3v device. However, unlike other 3.3v boards, we've made a concerted effort to make XLR8 as compatible as possible with the 5v Arduino Uno. We've done this by adding level shifting and protection circuitry to the I/O so that existing shields can be used without fear of damaging the board. The digital I/O's (RX, TX, and D2-D13) can both drive and receive 5V signals providing great compatibility with all shields. The analog I/O's (A0-A5) can tolerate both analog and digital inputs up to 5.0V, and as digital outputs can drive up to 3.3V and that should work fine for the majority of shields and other circuits. XLR8 provides 5.0V on the IOREF pin for newer shields that use that feature.

While ATmega328p inputs can enable or disable the internal weak pullup resistors, in XLR8, the pullups differ by pin as follows:

- RX, TX, D2-D13: Strong pullups on XLR8 board (1K ohms) are always enabled. The initial value of the PINB and PIND registers is therefore 0x3F and 0xFF respectively.

- A0-A5: No pullups

- SDA, SCL: Strong pullups on XLR8 board (1K ohms) are included. When using Arduino libraries, Wire.begin() enables the pullups for the I2C case (assuming the PUD bit of the MCUCR (0x35) register is not set) without any additional work required from the user. If desired, disabling the pullups in Arduino is as simple as doing both digitalWrite(SDA, LOW); and digitalWrite(SCL, LOW);. Outside of the Arduino environment the pullups are enabled when PUD is low, TWEN is high, and both PORTC4 and PORTC5 are high.

### 3.5 ADC

The ADC used in XLR8 is higher performing in both speed and resolution than the ADC found in the ATMega328p. By default, doing an analogRead will give the same speed and 10 bit resolution as an Arduino Uno. By using the XLR8ADC library (<u>https://github.com/AloriumTechnology/XLR8ADC</u>) you can get 12 bit resolution. Further enhancements will be available in the future.

One ADC difference between XLR8 and Arduino Uno/Sparkfun RedBoard occurs when running from USB power. The USB may supply a voltage that is somewhat lower than 5V and because the Uno and RedBoard use this for the default analog reference it results in higher ADC readings compared both to what would be expected and to what is measured when powered from the barrel connector. The XLR8 board does not suffer from this issue; it will give the same ADC reading whether powered from the barrel or from USB. Some shields, however, can be deceiving. If an analog voltage that the shield is creating drops along with the 5V USB power, it will appear on the Uno/Redboard that the ADC readings stay somewhat constant while on XLR8 the ADC readings will be reduced. If it is desired to have XLR8 vary the reference voltage with the USB power similar to an Uno/Redboard, this can be accomplished quite easily by wiring from the 5V header pin to the AREF header pin and using Arduino's analogReference (EXTERNAL);.

While the ATMega328p is able to switch its ADC reference voltage between internal 5V, internal 1.1V, and external references, XLR8 uses circuitry on the board to make this selection. From the user's point of view, there shouldn't be a noticeable difference. To ensure that XLR8 can tolerate ADC inputs up to 5V, the analog inputs run through an opamp and voltage divider circuit before entering the FPGA. Again, from the user's point of view, there shouldn't be a noticeable.

While the ADC channel selection is the same for measuring the primary six analog inputs (ADMUX=0000 through 0101), there are differences in the other channels. Channel 6 (ADMUX=0110) reads from the voltage divider created by R30 and R59, and should be around the max ADC value (1023 when in 10 bit mode) if the 5V supply is at or above 5.0V, but may be slightly less if the 5V supply is lower. Channel 7, and the temperature sensor are not implemented (ADMUX=0111 and 1000). Using the ADC to read the bandgap (ADMUX=1110) does not actually do a measurement but returns a calculated value equivalent to 1.1/Aref. Using the ADC to read ground (ADMUX=1111) does not actually do a measurement and instead returns a fixed value of 0.

## 3.6 Bootloader and ICSP header

XLR8 uses the Optiboot bootloader that is used by the Arduino Uno, with a slight modification that allows it to run correctly at different CPU speeds. As an extra indication of XLR8's current CPU speed, you may notice when running at 32MHz that the beginning of an upload sequence blinks the pin 13 LED three times rather quickly just like an Arduino Uno, while at 16MHz you get two slightly slower blinks. This bootloader is hardcoded into the design and cannot be changed by the user. If you have a need for something different in the bootloader, we'd be interested to hear about it. Consistent with using Optiboot, the BOOTRST "fuse" is hardcoded to zero (programmed) and the IVSEL and IVCE bits of the MCUCR (0x35) register are hardcoded to zero.

XLR8 is programmed only via the USB-UART path. While the XLR8 board includes the ICSP header it is useful only as a convenient connector for the SPI interface; it can't be used to load programs/sketches into the design.

## 3.7 I2C / Two Wire Interface (TWI)

Although the Arduino Uno's Rev3 layout has separate SDA and SCL pins for I2C/TWI, they are still connected on the Uno board to the original A4/A5 pins. This means that when using the I2C interface, two of your analog inputs are no longer available. On XLR8, I2C/TWI is by default only available on the SDA/SCL pins and the A4/A5 pins can still be used as analog or digital inputs (but not outputs). If you have existing projects that need to use A4/A5 as the I2C pins, you can reconnect them to SDA/SCL by populating 00hm resistors at R60 and R61. Another difference between the I2C/TWI on XLR8 and Arduino that you will likely never notice is related to the TWBR register. While Arduino allows running with non-standard SCL clock frequencies, XLR8 is optimized for 100KHz and 400KHz operation and setting TWBR and the prescaler bits of TWSR for other speeds will not be operational.

### 3.8 UART

XLR8 has a Universal Asynchronous serial Receiver and Transmitter (UART) block similar to the ATmega328p USART. However, XLR8's UART does not implement the Synchronous UART

(USART) in SPI Modes that are available on the ATmega328p. Therefore, the UMSEL01, UMSEL00, and UCPOL0 bits of the UCSR0C (0x) register, while implemented, have no effect and the UART block always runs in "Asynchronous UART" mode. We have not yet seen a case where anything else is needed in an Arduino environment; if you have one, please let us know.

### 3.9 SPI

The SPI interface on XLR8 should operate the same as the SPI interface on an Uno or Redboard. The only item to note is that we've seen some SPI examples where the XLR8/Uno/Redboard is the SPI slave and instead of being driven from the SPI master, the SS pin is left floating. Although a sloppy design practice, an Uno or Redboard will often still work in this arrangement. Our XLR8 board, due to its I/O pullups, needs to have SS driven and not floating.

#### 3.9.1 SPI Best Practices

In rare cases, we have observed an issue with the SPI clock being properly sampled by a shield. We suggest adding a 100-200 ohm pulldown resistor to the SPI clock pin D13 for more robust operation.

#### 3.10 Analog Compare

XLR8 does not have the Analog Compare function that is found in the ATmega328p. The ACME bit and analog compare triggering (ADTS=001) of the ADCSRB (0x7B) register, the ACSR (0x30) register, and the DIDR1 (0x7F) register are not implemented. If an analog compare function is desired, pins 6 and 7 on the (unpopulated) JTAG connector are wired to MAX10 pins DIFFIO\_TX\_RX\_B1P/N which is a differential I/O. Using the OpenXLR8 platform, a user could implement an analog compare function that is very similar to the ATMega328's, although the pin voltage would need to be limited to 3.3V.

#### 3.11 EEPROM

XLR8 does not have the EEPROM memory that is found in the ATmega328p. However, there is an SOIC-8 location that could be populated with an EEPROM and using the OpenXLR8 platform, a user could implement an EEPROM function that is very similar to the one found in the ATMega328. The SOIC-8 pinout is:

| FPGA pin | Typical | SOIC-8 |     | SOIC-8 | Typical | FPGA pin |

|----------|---------|--------|-----|--------|---------|----------|

|          | Use     | pin    |     | pin    | Use     |          |

| C12      | Addr0   | 1      | 1 + | 8      | Vcc     | 3.3V     |

| B13      | Addr1   | 2      |     | 7      | WP      | D11      |

| C11      | Addr2   | 3      |     | 6      | SCL     | D12      |

| Gnd      | Vss     | 4      | -   | 5      | SDA     | E13      |

#### **3.12 Power**

The Arduino Uno and the Sparkfun RedBoard are only able to supply 50mA from the 3.3V pin header. XLR8 has a 1.5A regulator creating its 3.3V power (an LT1963EST-3.3) and the Max10 FPGA is estimated to draw less than 100mA, leaving a significant amount of 3.3V power available to the user for shields or other circuits. (Keep in mind that USB power is limited to about 500mA.)

### 3.13 Pin13 LED

Digital pin 13 is used for both the on-board LED as well as the SPI clock, SCK. While the Arduino Uno R3 adds circuitry to prevent the LED and its pulldown resistor from affecting SCK, the Sparkfun Redboard does not take those precautions. On XLR8 we've decided to follow Arduino's lead and keep SCK separated from the LED.

# 4 ATmega328p features not implemented

The ATmega328p microcontroller includes several features that are seldom or never used in an Arduino environment. In XLR8, these features are hard coded to match the Arduino usage. Therefore, when comparing to the ATmega328p specification the following differences may be noted, however they do not impact functionality in an Arduino environment. One exception is that Arduino Uno allows programming via the SPI interface while, as mentioned in section 3.6, XLR8 has not implemented this feature (SPIEN fuse).

#### 4.1 Fuses

The Arduino Uno runs with the following fuse settings.

- Low Fuse 0xFF (all unprogrammed)

- CKDIV8: Default to clock division factor of 1.

- CKOUT: Don't output system clock on port B pin 0

- SUT1/0: Start up time

- CKSEL3/2/1/0

- Always use external clock (supplied by 16MHz) crystal.

- XLR8 does not have the internal 128kHz RC Oscillator or the Calibrated Internal RC Oscillator that exists in ATmega328p. The OSCCAL (0x66) register is not implemented.

- Because ATmega328 shares the TOSC1/2 pins with the XTAL1/2 pins, and XTAL1/2 are used to bring in the external 16MHz clock, the asynchronous mode of timer/counter 2 is not available and the ASSR register (0xB6) is not implemented.

- High Fuse 0xDE in Arduino (SPIEN and BOOTRST programmed), 0xFE in XLR8 (BOOTRST programmed)

- RSTDISBL: External reset is always enabled. This is how the microcontroller returns to the bootloader to upload a new sketch from the Arduino IDE to program memory

- DWEN: The debug wire feature is not enabled in Arduino and is not implemented in XLR8.

- SPIEN: While Arduino programs this bit, XLR8 instead functions as if it were not programmed (see section 3.6)

- WDTON: Watchdog always on not enabled

- EESAVE: EEPROM not preserved through chip erase. Not applicable on XLR8.

- BOOTSZ1/0: Bootloader is 256 words starting at 0x3F00

- BOOTRST: Reset starts at the bootloader address

- Extended Fuse 0x05 in Arduino (BODLEVEL1 programmed), 0x07 in XLR8 (all unprogrammed)

- BODLEVEL2/1/0: In XLR8 the brown out detection circuitry is disabled and not implemented. The BODS and BOSE bits of the MCUCR (0x35) register are not implemented, as well as the BORF bit of the MCUSR (0x34) register.

## 4.2 **Power Reduction**

Because we don't see it being used very often (or at all) in Arduino projects, XLR8 has not implemented the ATmega328p's Power Reduction Register PRR (0x64), Sleep Mode Control Register SMCR (0x33), or Clock Prescale Register CLKPR (0x61). They could be added if customer feedback indicates that would be a good thing to do.

# **5** Xcelerator Blocks (XBs)

Xcelerator Blocks are custom hardware blocks implemented within the XLR8 FPGA chip and are tightly integrated with the ATmega328 clone that is also implemented inside the FPGA chip. These custom hardware blocks can implement almost any functionality you can dream up, and can then be loaded into the XLR8 as with the Arduino toolset. Since an FPGA can be reprogrammed many times, a single XLR8 can be reconfigured to incorporate different XB depending on the project requirements.

XLR8 ships with three sample XBs: Floating Point, NeoPixel, and Servo Control. As mentioned in section 3.2, the software libraries are delivered as .zip files from our github site (<u>https://github.com/AloriumTechnology</u>). They are installed like other Arduino .zip libraries as described here (<u>https://www.arduino.cc/en/Guide/Libraries - toc4</u>).

Note: There is one thing to be aware of with all Arduino libraries. If you download an updated version and simply rename the directory of the old version (perhaps you think you might want to go back to it or maybe you are just feeling nostalgic), Arduino very likely will still end up using the old version as it simply looks for the first place it can find the #include header file name, regardless of what directory it is in. If you want to save an old version of a library, move it to someplace outside of your Arduino/libraries folder.

### 5.1 Floating Point

As an 8 bit microcontroller, the ATmega328p struggles with floating point math. The Floating Point XB provides functions that will give you floating point results in about ¼ the time that it takes software floating point to get the same answer. Available functions include add, subtract, multiply, and divide.

### 5.2 Servo Control

It is common for the standard Servo.h library to cause jitter in the servo control due to timing uncertainties caused by interrupt processing. The Servo Control XB completely eliminates this jitter by putting a dedicated hardware timer behind all 20 digital and analog pins. The XLR8Servo.h library is a drop-in replacement for the standard Servo.h library, so taking advantage of this XB is as simple as changing one line in your sketch from #include <Servo.h>

```

#include <XLR8Servo.h>

```

### 5.3 NeoPixel Control

The standard Arduino struggles to meet the timing requirements of NeoPixels. With the XLR8 NeoPixel hardware and library, interrupts remain enabled, data memory is saved, and pixel color information does not need to be rewritten when brightness is lowered and then brought back up. The XLR8NeoPixel library can be a drop-in replacement for the standard Adafruit\_NeoPixel library. It is common for other libraries, such as Adafruit\_NeoMatrix, to build on the Adafruit\_NeoPixel library and with just three lines added to the top of your sketch, it is possible to get the XLR8 advantages used by those libraries as well. For example,

```

// 3 new lines added

#include <XLR8NeoPixel.h>

#define Adafruit_NeoPixel XLR8NeoPixel

#define ADAFRUIT_NEOPIXEL_H

// Existing lines kept

#include <Adafruit_GFX.h>

#include <Adafruit_NeoMatrix.h>

#include <Adafruit_NeoPixel.h>

```

As explanation, working from the bottom up:

- Including Adafruit\_NeoPixel.h remains because other library files that we are using but are not modifying (Adafruit\_NeoMatrix.h in this case) have #include

<Adafruit\_NeoPixel.h>. The way Arduino handles compiling and linking generally requires that lower level #includes also be included in the sketch.

- Including Adafruit\_NeoMatrix remains because that is the library that this particular sketch is using

- Including Adafruit\_GFX remains for the same reason that it was there initially. It is included by Adafruit\_NeoMatrix, and the way Arduino handles compiling and linking generally requires that lower level #includes also be included in the sketch.

- Even though we are still including the Adafruit\_NeoPixel.h, adding #define ADAFRUIT\_NEOPIXEL\_H causes that header file to appear empty instead of having the actual Adafruit library code.

- By adding #define Adafruit\_NeoPixel XLR8NeoPixel, any place in your sketch, or in the libraries that your sketch is using, where an Adafruit\_NeoPixel string is instantiated, it will instantiate an XLR8NeoPixel string instead.

- And of course, the XLR8NeoPixel library is included.

Easy. Powerful. Fun.

And designed to become even more powerful in the future. Watch for updates.

# 6 Register Summary

The registers used in XLR8 are listed below. Those with a grey background have identical function to the equivalent ATmega328p register. Those with just a touch of grey are reserved in both XLR8 and ATmega328p but are noted because they are used in the ATmega328pb. Those with green background function like the equivalent ATmega328p register, but with some differences as noted. Those with blue background are new registers added for XLR8 functions. Those with white background are ATmega328p registers that do not exist in XLR8.

| Address | Name     | Bit 7                                                                                        | Bit 6         | Bit 5          | Bit 4           | Bit 3        | Bit 2        | Bit 1         | Bit O      | Notes |

|---------|----------|----------------------------------------------------------------------------------------------|---------------|----------------|-----------------|--------------|--------------|---------------|------------|-------|

| (0xFF)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (OxFE)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xFD)  | SVPWH    | -                                                                                            | -             | -              | -               | Ser          | vo Pulse Wid | th High Regi  | ster       | 6.1.5 |

| (0xFC)  | SVPWL    |                                                                                              |               | Ser            | vo Pulse Wid    | Ith Low Regi | ster         |               |            | 6.1.5 |

| (OxFB)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xFA)  | SVCR     | SVEN                                                                                         | SVDIS         | SVUP           |                 |              | SVCHAN       |               |            | 6.1.5 |

| (0xF9)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xF8)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xF7)  | NEOD2    |                                                                                              | Ne            | oPixel Data 2  | 2 register, fui | nction deper | nds on NEOC  | MD            |            | 6.1.6 |

| (0xF6)  | NEOD1    | NeoPixel D                                                                                   | ata 1 registe | er, function d | lepends on N    | IEOCMD, oft  | en high half | of pixel addr | ess/length | 6.1.6 |

| (0xF5)  | NEOD0    | NeoPixel Data 0 register, function depends on NEOCMD, often low half of pixel address/length |               |                |                 |              |              |               |            |       |

| (0xF4)  | NEOCR    |                                                                                              | NEC           | DPIN           |                 |              | NEO          | CMD           |            | 6.1.6 |

| (0xF3)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xF2)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xF1)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xF0)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (OxEF)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (OxEE)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xED)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xEC)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (OxEB)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xEA)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xE9)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xE8)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| (0xE7)  | Reserved | -                                                                                            | -             | -              | -               | -            | -            | -             | -          |       |

| Address          | Name                 | Bit 7      | Bit 6                                  | Bit 5    | Bit 4          | Bit 3            | Bit 2       | Bit 1         | Bit 0  | Notes          |

|------------------|----------------------|------------|----------------------------------------|----------|----------------|------------------|-------------|---------------|--------|----------------|

| (0xE6)           | Reserved             | -          | _                                      | _        | _              | _                | _           | -             | _      |                |

| (0xE5)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0xE4)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0xE3)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0xE2)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0xE1)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0xE0)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      |                |

| (0x20)<br>(0xDF) | Reserved             | _          | _                                      | _        | _              | _                | _           | _             |        |                |

| (0xDF)           | Reserved             |            | _                                      | _        | _              | _                | _           |               |        |                |

| (0xDD)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             | _      | TWAMR1         |

| (0xDC)           | Reserved             |            | _                                      |          |                |                  | _           |               |        | TWCR1          |

| (0xDB)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             |        | TWDR1          |

| (0xDB)<br>(0xDA) | Reserved             |            | _                                      |          |                |                  |             |               |        | TWDR1          |

| (0xDA)<br>(0xD9) | Reserved             | _          | _                                      |          |                |                  |             |               |        | TWARI<br>TWSR! |

| (0xD3)<br>(0xD8) | Reserved             |            | _                                      | _        | _              |                  | _           |               |        | TWBR1          |

|                  |                      | _          | _                                      | _        | -              | -                | _           | _             | _      | IVVDKT         |

| (0xD7)           | Reserved<br>XLR8VERT | _          | _                                      |          |                | -<br>Number Elec |             | -             | _      | 6.1.1          |

| (0xD6)           |                      |            |                                        |          |                | Number Flag      |             |               |        | 6.1.1          |

| (0xD5)           | XLR8VERH             |            | XLR8 Version Number Register High Byte |          |                |                  |             |               |        |                |

| (0xD4)           | XLR8VERL             |            | XLR8 Version Number Register Low Byte  |          |                |                  |             |               |        |                |

| (0xD3)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      |                |

| (0xD2)           | FCFGDAT              |            | -                                      |          | -              | tion Data Re     | gister      |               |        | 6.1.4          |

| (0xD1)           | FCFGSTS              | FCFGDN     | 0                                      | FCFGFM   | FCFGRDY        | -                | -           | -             | -      | 6.1.4          |

| (0xD0)           | FCFGCTL              | -          |                                        | FCFGSEC  |                | -                | FCFG        | CMD           | FCFGEN | 6.1.4          |

| (0xCF)           | FCFGCID              |            | 1                                      |          | Chip ID        | register         | 1           |               |        | 6.1.2          |

| (0xCE)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UDR1           |

| (0xCD)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UBBR1H         |

| (0xCC)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UBBR1L         |

| (0xCB)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UCSR1D         |

| (0xCA)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UCSR1C         |

| (0xC9)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UCSR1B         |

| (0xC8)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UCSR1A         |

| (0xC7)           | Reserved             | -          | _                                      | -        | -              | -                | _           | -             | _      |                |

| (0xC6)           | UDRO                 |            |                                        |          | USART I/O D    | ata Register     |             |               |        |                |

| (0xC5)           | UBRROH               | -          | -                                      | -        | -              | US               | ART Baud Ra | te Register H | ligh   |                |

| (0xC4)           | UBRROL               |            |                                        | US       | ART Baud Ra    | te Register L    | .ow         |               |        |                |

| (0xC3)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      | UCSROD         |

| (0               | LICEBOC              |            |                                        |          |                |                  | UCSZ01/     | UCSZ00/       |        | 3.8            |

| (0xC2)           | UCSROC               |            | UMSEL00                                |          | UPM00          | USBSO            | UDORD0      | UCPHA0        | UCPOL0 | 0.0            |

| (0xC1)           | UCSROB               | RXCIEO     | TXCIEO                                 | UDRIEO   | RXENO          | TXEN0            | UCSZ02      | RXB80         | TXB80  |                |

| (0xC0)           | UCSROA               | RXCO       | TXC0                                   | UDREO    | FEO            | DOR0             | UPE0        | U2X0          | MPCM0  |                |

| (0xBF)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      |                |

| (OxBE)           | Reserved             | -          | -                                      | -        | -              | -                |             | -             | -      |                |

| (0xBD)           | TWAMR                | TWAM6      | TWAM5                                  | TWAM4    | TWAM3          | TWAM2            | TWAM1       | TWAM0         | -      |                |

| (0xBC)           | TWCR                 | TWINT      | TWEA                                   | TWSTA    | TWSTO          | TWWC             | TWEN        | -             | TWIE   |                |

| (OxBB)           | TWDR                 |            | I                                      |          |                | face Data Re     | 1           |               |        |                |

| (0xBA)           | TWAR                 | TWA6       | TWA5                                   | TWA4     | TWA3           | TWA2             | TWA1        | TWA0          | TWGCE  |                |

| (0xB9)           | TWSR                 | TWS7       | TWS6                                   | TWS5     | TWS4           | TWS3             | -           | TWPS1         | TWPS0  |                |

| (0xB8)           | TWBR                 |            |                                        | 2-wire   | Serial Interfa | ice Bit Rate F   | Register    |               |        |                |

| (0xB7)           | Reserved             | -          | -                                      | _        | _              | _                | -           | -             |        |                |

| (0xB6)           | Reserved             | _          | _                                      | _        | _              | _                | _           | _             |        | ASSR 4.1       |

| (0xB5)           | Reserved             | -          | -                                      | -        | -              | -                | -           | -             | -      |                |

| (0xB4)           | OCR2B                |            |                                        |          | •              | ut Compare       |             |               |        |                |

| (0xB3)           | OCR2A                |            |                                        | Timer/Co | unter2 Outp    | ut Compare       | Register A  |               |        |                |

| (0xB2)           | TCNT2                |            |                                        |          | Timer/Cour     | nter2 (8-bit)    |             |               |        |                |

| (0xB1)           | TCCR2B               | FOC2A      | FOC2B                                  | -        | -              | WGM22            | CS22        | CS21          | CS20   |                |

| Convright 2      | 017 Alorium          | Technology |                                        |          |                |                  |             |               |        | Page 13        |

| Address          | Name             | Bit 7       | Bit 6                                                                                     | Bit 5                                 | Bit 4            | Bit 3 | Bit 2    | Bit 1    | Bit O    | Notes     |  |

|------------------|------------------|-------------|-------------------------------------------------------------------------------------------|---------------------------------------|------------------|-------|----------|----------|----------|-----------|--|

| (0xB0)           | TCCR2A           | COM2A1      | COM2A0                                                                                    | COM2B1                                | COM2B0           | -     | _        | WGM21    | WGM20    |           |  |

| (0xAF)           | Reserved         | _           | _                                                                                         | -                                     | _                | _     | _        | _        | _        |           |  |

| (0xAE)           | Reserved         | _           | _                                                                                         | -                                     | _                | -     | _        | _        | -        | SPDR1     |  |

| (0xAD)           | Reserved         | _           | _                                                                                         | -                                     | _                | -     | _        | _        | -        | SPSR1     |  |

| (0xAC)           | Reserved         | _           | _                                                                                         | -                                     | -                | _     | _        | _        | _        | SPCR1     |  |

| (0xAB)           | Reserved         | _           | -                                                                                         | -                                     | -                | _     | _        | -        | -        | OCR4BH    |  |

| (0xAA)           | Reserved         | _           | -                                                                                         | -                                     | -                | _     | _        | -        | -        | OCR4BL    |  |

| (0xA9)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR4AH    |  |

| (0xA8)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR4AL    |  |

| (0xA7)           | Reserved         | _           | _                                                                                         | _                                     | -                | _     | _        | -        | _        | ICR4H     |  |

| (0xA6)           | Reserved         | _           | _                                                                                         | -                                     | _                | -     | _        | _        | -        | ICR4L     |  |

| (0xA5)           | Reserved         | _           | _                                                                                         | _                                     | -                | _     | _        | -        | _        | TCNT4H    |  |

| (0xA4)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCNT4L    |  |

| (0xA3)           | Reserved         | -           | -                                                                                         | -                                     | -                | _     | -        | -        | -        |           |  |

| (0xA2)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR4C    |  |

| (0xA1)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR4B    |  |

| (0xA0)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR4A    |  |

| (0x9F)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x9E)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x9D)           | Reserved         | _           | _                                                                                         | _                                     | _                | -     | _        | -        | _        |           |  |

| (0x9C)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x9B)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR3BH    |  |

| (0x9A)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR3BL    |  |

| (0x99)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR3AH    |  |

| (0x98)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | OCR3AL    |  |

| (0x97)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | ICR3H     |  |

| (0x96)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | ICR3L     |  |

| (0x95)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCNT3H    |  |

| (0x94)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCNT3L    |  |

| (0x93)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TOTTOL    |  |

| (0x92)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR3C    |  |

| (0x91)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR3B    |  |

| (0x90)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | TCCR3A    |  |

| (0x8F)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        | 1001071   |  |

| (0x8F)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        |          | _        |           |  |

| (0x8D)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x8C)           | Reserved         | _           | _                                                                                         | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x8B)           | OCR1BH           |             |                                                                                           |                                       | 1<br>– Output Co |       |          |          | l        |           |  |

| (0x8A)           | OCR1BL           |             |                                                                                           |                                       | 1 – Output C     |       | -        |          |          |           |  |

| (0x8A)           | OCR1AH           |             |                                                                                           | · · · · · · · · · · · · · · · · · · · | L – Output Co    | · · · |          | ·        |          |           |  |

| (0x88)           | OCR1AI           |             |                                                                                           |                                       | 1 – Output Co    |       | U        |          |          |           |  |

| (0x88)<br>(0x87) | ICR1H            |             |                                                                                           |                                       | er1 – Input C    |       |          |          |          |           |  |

| (0x86)           | ICR1L            |             |                                                                                           |                                       | er1 – Input C    |       |          |          |          |           |  |

| (0x85)           | TCNT1H           |             |                                                                                           |                                       |                  |       |          | <b>.</b> |          |           |  |

| (0x85)<br>(0x84) | TCNT1H<br>TCNT1L |             | Timer/Counter1 – Counter Register High Byte<br>Timer/Counter1 – Counter Register Low Byte |                                       |                  |       |          |          |          |           |  |

| (0x84)<br>(0x83) | Reserved         |             |                                                                                           |                                       |                  |       |          |          |          |           |  |

| (0x83)<br>(0x82) | TCCR1C           | FOC1A       | FOC1B                                                                                     | _                                     | _                | _     | _        | _        | _        |           |  |

| (0x82)<br>(0x81) | TCCR1C<br>TCCR1B | ICNC1       | ICES1                                                                                     | _                                     | WGM13            | WGM12 | <br>CS12 | <br>CS11 | <br>CS10 |           |  |

| (0x81)<br>(0x80) | TCCR1B<br>TCCR1A | COM1A1      | COM1A0                                                                                    |                                       | 1                |       | C312     |          | WGM10    |           |  |

| . ,              | Reserved         | CONTAT      | CONTAU                                                                                    | COM1B1                                | COM1B0           |       | _        | WGM11    | VVGIVI10 | DIDR1 3.9 |  |

| (0x7F)           |                  |             |                                                                                           |                                       |                  |       |          |          |          | 2.5 1701  |  |

| (0x7E)           |                  | -<br>AD12EN | -                                                                                         | ADC5D                                 | ADC4D            | ADC3D | ADC2D    | ADC1D    | ADCOD    | 619       |  |

| (0x7D)           | XLR8ADCR         | AD12EN      |                                                                                           |                                       |                  |       |          |          |          | 6.1.8     |  |

| (0x7C)           |                  | REFS1       | REFSO                                                                                     | ADLAR                                 | -                | MUX3  | MUX2     | MUX1     | MUX0     | 3.5       |  |

| (0x7B)           | ADCSRB           | -           | -                                                                                         | -                                     | -                | -     | ADTS2    | ADTS1    | ADTS0    | ACME 3.9  |  |

| Address    | Name     | Bit 7   | Bit 6   | Bit 5        | Bit 4          | Bit 3          | Bit 2        | Bit 1   | Bit O   | Notes       |

|------------|----------|---------|---------|--------------|----------------|----------------|--------------|---------|---------|-------------|

| (0x7A)     | ADCSRA   | ADEN    | ADSC    | ADATE        | ADIF           | ADIE           | ADPS2        | ADPS1   | ADPS0   |             |

| (0x79)     | ADCH     |         |         | A            | DC Data Regi   | ister High by  | te           |         |         |             |

| (0x78)     | ADCL     |         |         | A            | DC Data Reg    | ister Low by   | te           |         |         |             |

| (0x77)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x76)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x75)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x74)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x73)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       | PCMSK3      |

| (0x72)     | Reserved | -       |         |              |                |                |              |         |         |             |

| (0x71)     | Reserved | _       | -       | -            | -              | _              | -            | -       | -       | TIMSK3      |

| (0x70)     | TIMSK2   | -       | -       | -            | -              | -              | OCIE2B       | OCIE2A  | TOIE2   |             |

| (0x6F)     | TIMSK1   | -       | -       | ICIE1        | -              | -              | OCIE1B       | OCIE1A  | TOIE1   |             |

| (0x6E)     | TIMSK0   | -       | -       | -            | -              | -              | OCIEOB       | OCIE0A  | TOIE0   |             |

| (0x6D)     | PCMSK2   | PCINT23 | PCINT22 | PCINT21      | PCINT20        | PCINT19        | PCINT18      | PCINT17 | PCINT16 |             |

| (0x6C)     | PCMSK1   | -       | PCINT14 | PCINT13      | PCINT12        | PCINT11        | PCINT10      | PCINT9  | PCINT8  |             |

| (0x6B)     | PCMSK0   | PCINT7  | PCINT6  | PCINT5       | PCINT4         | PCINT3         | PCINT2       | PCINT1  | PCINT0  |             |

| (0x6A)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x69)     | EICRA    | -       | -       | -            | -              | ISC11          | ISC10        | ISC01   | ISC00   |             |

| (0x68)     | PCICR    | -       | -       | -            | -              | -              | PCIE2        | PCIE1   | PCIE0   |             |

| (0x67)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| (0x66)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       | OSCCAL 4.1  |

| (0x65)     | Reserved | -       | -       | -            | -              | -              | _            | -       | -       |             |

| (0x64)     | PRR      | -       | -       | -            | PRINTOSC       | -              | -            | -       | -       | 4.2, 6.1.3  |

| (0x63)     | Reserved | -       | -       | -            | -              | -              | _            | -       | -       |             |

| (0x62)     | Reserved | -       | -       | -            | -              | -              | -            | -       | -       | XFDCSR      |

| (0x61)     | Reserved | I       | -       | -            | -              | I              | -            | -       | -       | CLKPR 4.2   |

| (0x60)     | WDTCSR   | WDIF    | WDIE    | WDP3         | WDCE           | WDE            | WDP2         | WDP1    | WDP0    |             |

| 0x3F(0x5F) | SREG     |         | Т       | Н            | S              | V              | N            | Z       | С       |             |

| 0x3E(0x5E) | SPH      | -       | -       | -            | -              | SP11           | SP10         | SP9     | SP8     |             |

| 0x3D(0x5D) | SPL      | SP7     | SP6     | SP5          | SP4            | SP3            | SP2          | SP1     | SP0     |             |

| 0x3C(0x5C) | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| 0x3B(0x5B) | XFR3     |         | X       |              | ı (floating po |                |              | te      |         | 6.1.7       |

| 0x3A(0x5A) | XFR2     |         |         |              | ion (floating  |                |              |         |         | 6.1.7       |

| 0x39(0x59) | XFR1     |         |         | XLR8 Funct   | ion (floating  | point) 32 bit  | Result Byte  |         |         | 6.1.7       |

| 0x38(0x58) | XFRO     |         | Х       | LR8 Functior | n (floating po | int) 32 bit Re | esult Low By | te      |         | 6.1.7       |

| 0x37(0x57) | SPMCSR   | SPMIE   | RWWSB   | SIGRD        | RWWSRE         | BLBSET         | PGWRT        | PGERS   | SPMEN   |             |

| 0x36(0x56) | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

|            |          |         |         |              |                |                |              |         |         | MCUCR       |

| 0x35(0x55) | Reserved | _       | -       | -            | -              | _              | -            | -       | -       | 4.1,3.4,3.6 |

| 0x34(0x54) | MCUSR    | -       | -       | -            | -              | WDRF           | -            | EXTRF   | PORF    | BORF 4.1    |

| 0x33(0x53) | Reserved | _       | -       | -            | -              | _              | -            | _       | -       | SMCR 4.2    |

| 0x32(0x52) | Reserved | -       | -       | -            | -              | -              | -            | -       | -       |             |

| 0x31(0x51) | Reserved | -       | -       | -            | -              | -              | -            | -       | -       | DWDR        |

| 0x30(0x50) | Reserved | _       | -       | -            | -              | _              | -            | _       | -       | ACSR 3.9    |

| 0x2F(0x4F) | Reserved | -       | -       | -            | -              | -              | -            | -       | -       | ACSRB       |

| 0x2E(0x4E) | SPDR     |         |         |              | SPI Data       | Register       |              |         |         |             |

| 0x2D(0x4D) | SPSR     | SPIF    | WCOL    | -            | -              | _              | -            | -       | SPI2X   |             |

| 0x2C(0x4C) | SPCR     | SPIE    | SPE     | DORD         | MSTR           | CPOL           | СРНА         | SPR1    | SPRO    |             |

| 0x2B(0x4B) | GPIOR2   |         |         |              | neral Purpos   |                |              |         |         |             |

| 0x2A(0x4A) | GPIOR1   |         |         |              | neral Purpos   |                |              |         |         |             |

| 0x29(0x49) | CLKSPD   |         | C       |              | programming    |                |              | r       |         | 6.1.3       |

| 0x28(0x48) | OCR0B    |         |         |              | unter0 Outp    |                | -            |         |         |             |

| 0x27(0x47) | OCR0A    |         |         | Timer/Co     | unter0 Outp    |                | Register A   |         |         |             |

| 0x26(0x46) | TCNT0    |         |         |              | Timer/Cour     | nter0 (8-bit)  |              |         |         |             |

| Address    | Name     | Bit 7                  | Bit 6       | Bit 5                     | Bit 4        | Bit 3         | Bit 2  | Bit 1  | Bit O   | Notes        |

|------------|----------|------------------------|-------------|---------------------------|--------------|---------------|--------|--------|---------|--------------|

| 0x25(0x45) | TCCR0B   | FOC0A                  | FOCOB       | -                         | -            | WGM02         | CS02   | CS01   | CS00    |              |

| 0x24(0x44) | TCCR0A   | COM0A1                 | COM0A0      | COM0B1                    | COM0B0       | _             | _      | WGM01  | WGM00   |              |

| 0x23(0x43) | GTCCR    | TSM                    | -           | -                         | -            | -             | -      | PSRASY | PSRSYNC |              |

| 0x22(0x42) | EEARH    |                        |             | EEPRO                     | OM Address   | Register Hig  | h Byte |        |         | EEPROM       |

| 0x21(0x41) | EEARL    |                        |             | EEPR                      | OM Address   | Register Lov  | v Byte |        |         | function     |

| 0x20(0x40) | EEDR     |                        |             |                           | EEPROM Da    | ata Register  |        |        |         | could be     |

| 0x1F(0x3F) | EECR     | -                      | -           | EEPM1                     | EEPM0        | EERIE         | EEMPE  | EEPE   | EERE    | added - 3.11 |

| Ox1E(Ox3E) | GPIOR0   |                        |             | Ge                        | neral Purpos | e I/O Registe | er O   |        |         |              |

| 0x1D(0x3D) | EIMSK    | -                      | -           | -                         | -            | -             | -      | INT1   | INT0    |              |

| 0x1C(0x3C) | EIFR     | -                      | -           | -                         | -            | -             | -      | INTF1  | INTF0   |              |

| Ox1B(Ox3B) | PCIFR    | -                      | -           | -                         | -            | -             | PCIF2  | PCIF1  | PCIF0   |              |

| 0x1A(0x3A) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x19(0x39) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       | TIFR4        |

| 0x18(0x38) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       | TIFR3        |

| 0x17(0x37) | TIFR2    | -                      | -           | -                         | -            | -             | OCF2B  | OCF2A  | TOV2    |              |

| 0x16(0x36) | TIFR1    | -                      | -           | ICF1                      | -            | -             | OCF1B  | OCF1A  | TOV1    |              |

| 0x15(0x35) | TIFRO    | -                      | -           | -                         | -            | -             | OCF0B  | OCF0A  | TOV0    |              |

| 0x14(0x34) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x13(0x33) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x12(0x32) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x11(0x31) | XFSTAT   | XFDONE                 | XFERR       | -                         | -            | -             | -      | -      | -       | 6.1.7        |

| 0x10(0x30) | XFCTRL   | -                      | XFSTART     | -                         | -            | -             |        | XFCMD  |         | 6.1.7        |

| 0x0F(0x2F) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x0E(0x2E) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       | 328PB PORTE  |

| 0x0D(0x2D) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       | 328PB DDRE   |

| 0x0C(0x2C) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       | 328PB PINE   |

| 0x0B(0x2B) | PORTD    | PORTD7                 | PORTD6      | PORTD5                    | PORTD4       | PORTD3        | PORTD2 | PORTD1 | PORTD0  | pullup 3.4   |

| 0x0A(0x2A) | DDRD     | DDD7                   | DDD6        | DDD5                      | DDD4         | DDD3          | DDD2   | DDD1   | DDD0    |              |

| 0x09(0x29) | PIND     | PIND7                  | PIND6       | PIND5                     | PIND4        | PIND3         | PIND2  | PIND1  | PINDO   | reset 3.4    |

| 0x08(0x28) | PORTC    | -                      | PORTC6      | PORTC5                    | PORTC4       | PORTC3        | PORTC2 | PORTC1 | PORTCO  | pullup 3.4   |

| 0x07(0x27) | DDRC     | -                      | DDC6        | DDC5                      | DDC4         | DDC3          | DDC2   | DDC1   | DDC0    |              |

| 0x06(0x26) | PINC     | -                      | PINC6       | PINC5                     | PINC4        | PINC3         | PINC2  | PINC1  | PINCO   |              |

| 0x05(0x25) | PORTB    | PORTB7                 | PORTB6      | PORTB5                    | PORTB4       | PORTB3        | PORTB2 | PORTB1 | PORTBO  | pullup 3.4   |

| 0x04(0x24) | DDRB     | DDB7                   | DDB6        | DDB5                      | DDB4         | DDB3          | DDB2   | DDB1   | DDB0    |              |

| 0x03(0x23) | PINB     | PINB7                  | PINB6       | PINB5                     | PINB4        | PINB3         | PINB2  | PINB1  | PINBO   | reset 3.4    |

| 0x02(0x22) | Reserved | -                      | -           | -                         | -            | _             | -      | -      | -       |              |

| 0x01(0x21) | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

| 0x0(0x20)  | Reserved | -                      | -           | -                         | -            | -             | -      | -      | -       |              |

|            |          |                        |             |                           |              |               |        |        |         |              |

|            |          |                        |             |                           |              |               |        |        |         |              |

|            |          |                        | od from AT  | mega328p                  |              |               |        | •      |         |              |

| 1 1        |          | i = unchang            | eu nom Ai   | IIICgaJZOD                |              |               |        |        |         |              |

|            |          |                        |             |                           | lemented i   | n XLR8        |        |        |         |              |

|            |          | = ATmega               | 328p regist | ers not imp               | lemented i   |               |        |        |         |              |

|            |          | = ATmega<br>= Some dit | 328p regist | ers not imp<br>1 XLR8 com |              |               |        |        |         |              |

## 6.1 XLR8 and XB Register Descriptions

### 6.1.1 XLR8VERL, XLR8VERH, XLR8VERT – Version Number Registers

| Address | Name     | Bit 7 | Bit 6                     | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O | Notes |  |

|---------|----------|-------|---------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| (0xD6)  | XLR8VERT |       | XLR8 Version Number Flags |       |       |       |       |       |       |       |  |

| Address       | Name     | Bit 7 | Bit 6                                  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O | Notes |  |

|---------------|----------|-------|----------------------------------------|-------|-------|-------|-------|-------|-------|-------|--|

| (0xD5)        | XLR8VERH |       | XLR8 Version Number Register High Byte |       |       |       |       |       |       |       |  |

| (0xD4)        | XLR8VERL |       | XLR8 Version Number Register Low Byte  |       |       |       |       |       |       |       |  |

| Read/Write    |          | R     | R                                      | R     | R     | R     | R     | R     | R     |       |  |

| Initial Value |          | N/A   | N/A                                    | N/A   | N/A   | N/A   | N/A   | N/A   | N/A   |       |  |

The version number register provides the FPGA design revision, while the version flags register indicates if the build had a mixed or modified version. The registers have a constant value for a particular design, but the value changes for each version. The easiest way to use these registers is with the XLR8Info library (https://github.com/AloriumTechnology/XLR8Info).

#### 6.1.2 FCFGCID – Chip ID Register

| Address    | Name    | Bit 7 | Bit 6            | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit O | Notes       |

|------------|---------|-------|------------------|-------|-------|-------|-------|-------|-------|-------------|