# AnalogDialogue

# Volume 52, Number 4, 2018

Your Engineering Resource for Innovative Design

- 5 Use of Integrated Passives in Micromodule SIPs

- 8 A Large Current Source with High Accuracy and Fast Settling

- 12 Modeling and Control for Current-Mode Buck Converter with a Secondary LC Filter

- 22 Over-the-Air (OTA) Updates in Embedded Microcontroller Applications: Design Trade-Offs and Lessons Learned

- 29 Functional Safety in a Data Acquisition System

- 48 Programmable Gain Instrumentation Amplifier: Finding One that Works for You

- 54 Remote Sensing Using a High Precision Instrumentation Amplifier

- 57 Overcoming Constraints: Design a Precision Bipolar Power Supply on a Simple Buck Controller

# **33** Care and Feeding of FPGA Power Supplies: A How and Why Guide to Success

# In This Issue

| <br>     | -    |

|----------|------|

| PASSIVES | • #• |

When standalone discrete passives, or even integrated passive networks, are included as part of a chipset, routing parasitics, device compatibility, and board assembly considerations still require careful design management. While integrated passives continue to have a strong play in the industry, their most significant value begins to be realized only when they are included in system in package (SIP) type applications, and there are many advantages to doing so.

# A Large Current Source with High Accuracy and Fast Settling

Voltage controlled current sources (VCCSs) are widely used in many areas. The dc precision, ac performance, and drive capability of the VCCS are very important in these applications. This article analyzes the enhanced Howland current source (EHCS) circuit's limitation and improves it with composite amplifier topology to implement a  $\pm$ 500 mA current source with high precision and fast settling.

# 12 Modeling and Control for Current-Mode Buck Converter with a Secondary LC Filter

Modern signal processing system design utilizing ADCs, PLLs, and RF transceivers demands lower power consumption and higher system performance. Selecting proper power supplies for those noise-sensitive devices is a common pain point for system designers. Traditionally, LDO regulators are often used to power those noise-sensitive devices. Switching regulators are more efficient than LDO regulators, but they are too noisy to directly power ADCs or PLLs.

# 20 Rarely Asked Questions—Issue 158: Driving a Unipolar Gate Driver in a Bipolar Way

The majority of today's available isolated gate drivers only accept a single supply on the output side. An increasing number of power devices need a negative gate drive voltage at the gate for better performance. This RAQ article details some elegant methods on how to operate a single supply gate driver in a bipolar method.

# 22 Over-the-Air (OTA) Updates in Embedded Microcontroller Applications: Design Trade-Offs and Lessons Learned

While many people are aware of over-the-air updates on their mobile devices, they may not be as familiar with the design and implementation of an OTA update for an embedded system. In this article, several different software designs for OTA updates and the trade-offs that come with various design decisions are discussed.

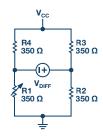

R4

350

VOIFF

# Analog Dialogue Volume 52 Number 4

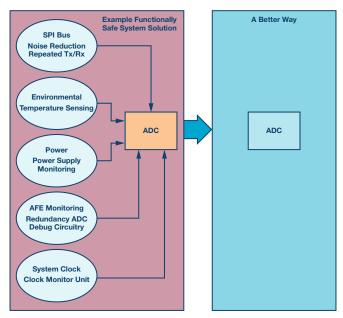

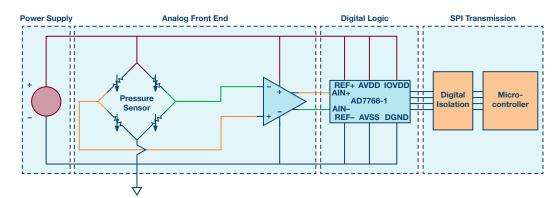

#### 29 Functional Safety in a Data Acquisition System

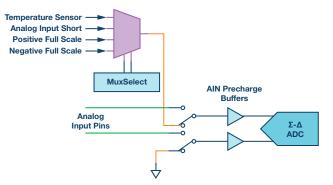

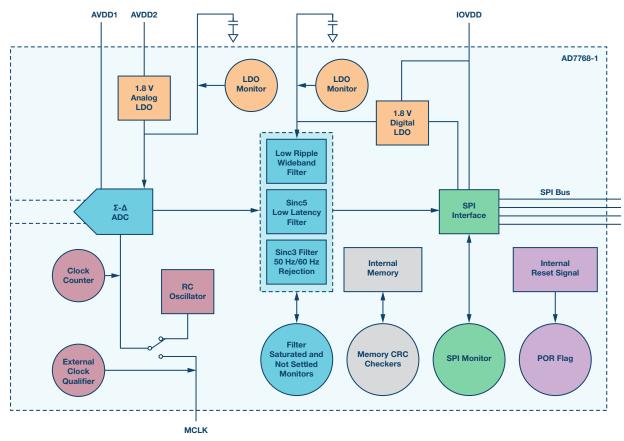

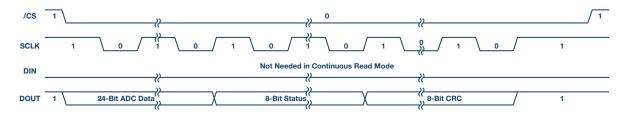

The requirements for systems to be functionally safe have grown significantly in recent years. From nuclear power plants to medical devices, an errorless system has become an ideal for some and a necessity for others. ADI sought to solve this issue for our customers by designing in security at the IC level with the AD7768.

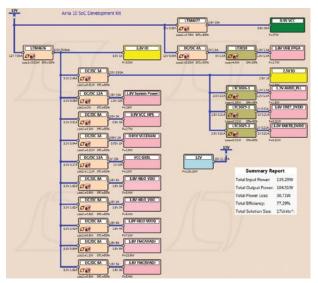

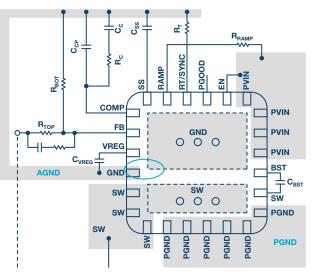

#### Care and Feeding of FPGA Power Supplies: A How and Why 33 **Guide to Success**

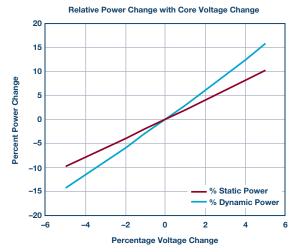

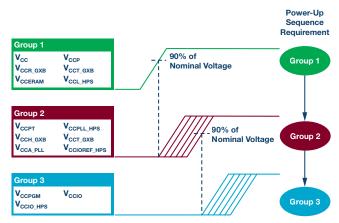

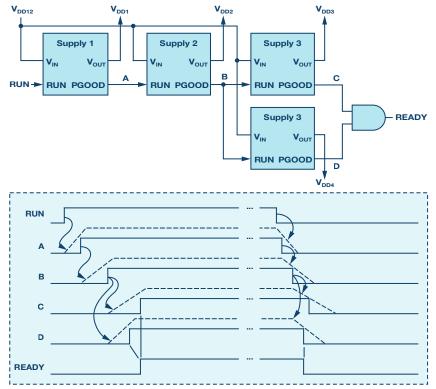

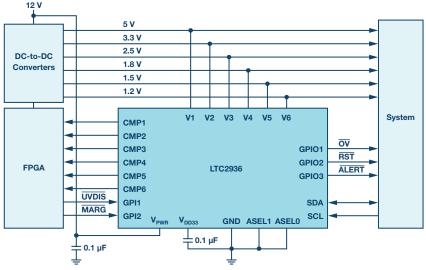

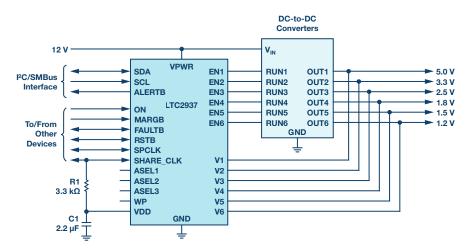

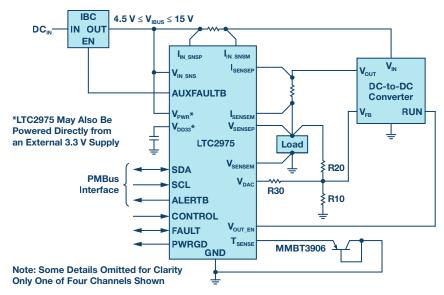

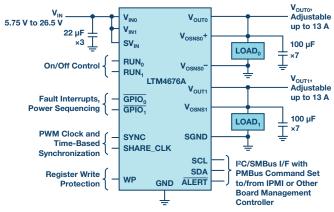

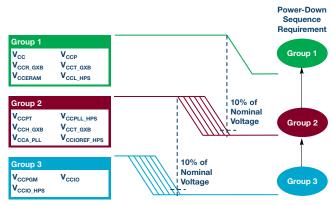

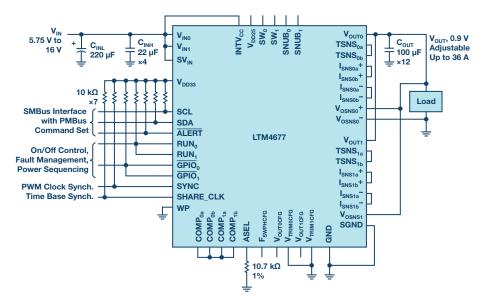

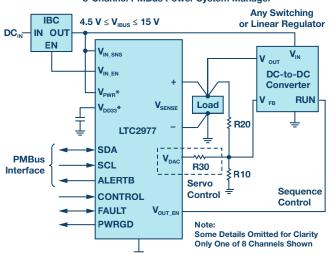

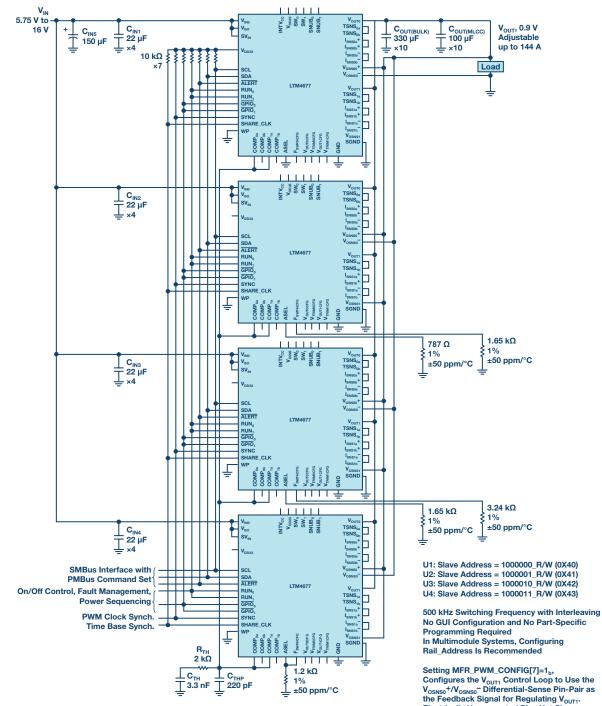

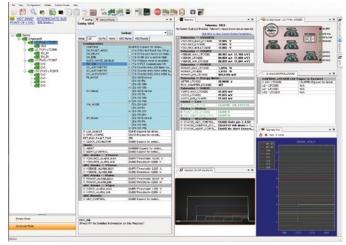

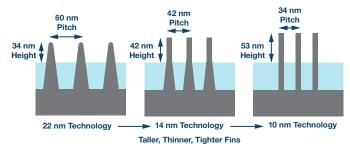

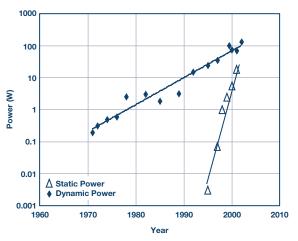

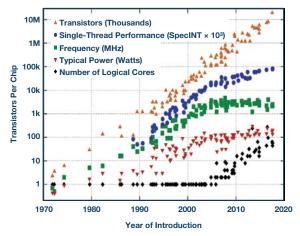

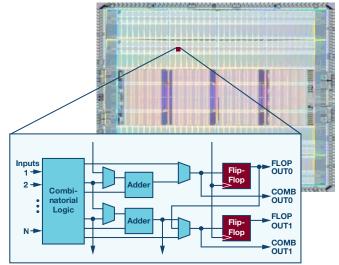

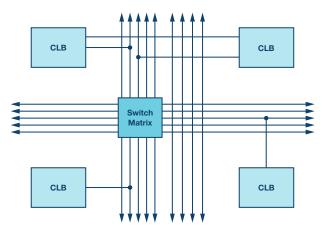

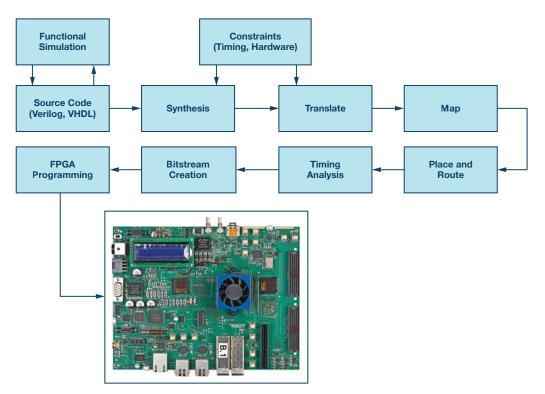

Modern FPGAs are among the most complex integrated circuits ever created. This also means the power supply for an FPGA must be more accurate, more agile, more controllable, smaller, more efficient, and more fault aware with each new FPGA generation. This article looks specifically at some of the constraining specifications for the Altera Arria 10 FPGA and what they mean for a power supply design challenge.

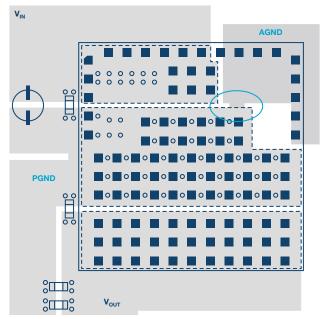

#### Rarely Asked Questions—Issue 159: When Grounds Are Separated 46

How should you proceed with a switching regulator with an analog ground (AGND) and a power ground (PGND)? Some developers are accustomed to dealing with a digital GND and an analog GND; however, their experience frequently fails them when it comes to the power GND. Designers then often copy the board layout for a selected switching regulator and stop thinking about the problem.

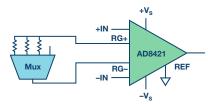

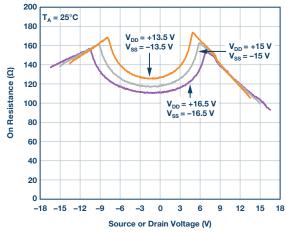

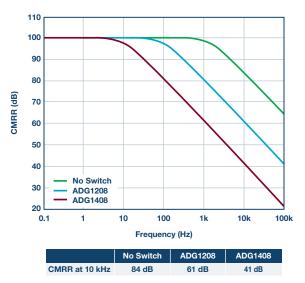

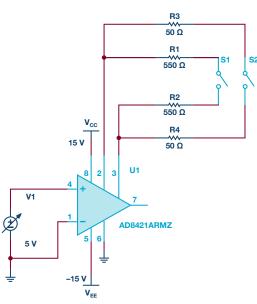

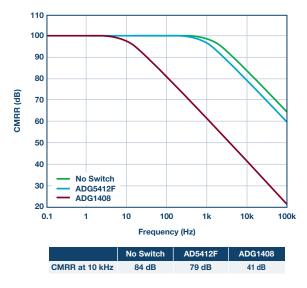

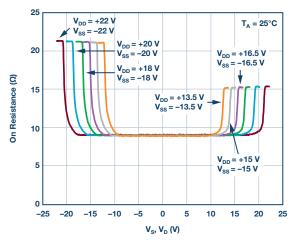

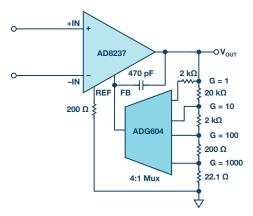

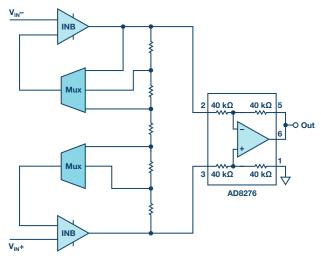

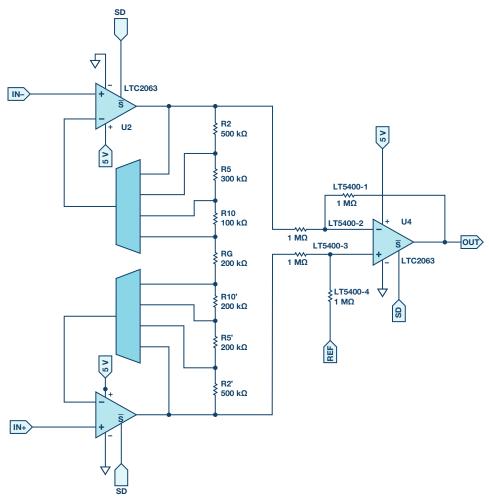

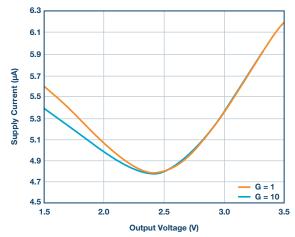

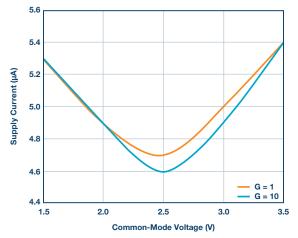

#### Programmable Gain Instrumentation Amplifier: Finding One that 48 Works for You

Data acquisition systems are used in many industries for a wide range of applications, such as research, analysis, design verification, manufacturing, and test. By nature, these systems interface with various sensors, which poses a challenge to the front end. We will discuss various integrated PGIAs and the advantages of using them-such as for best CMRR, low offsets, and exceptional gain and drift performance.

#### **Remote Sensing Using a High Precision Instrumentation Amplifier** 54

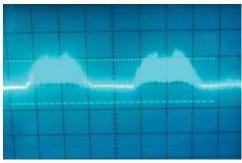

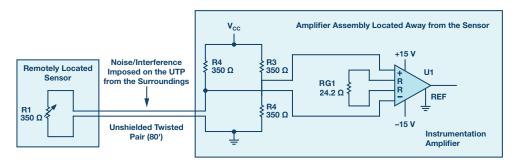

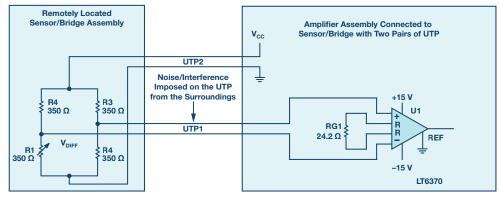

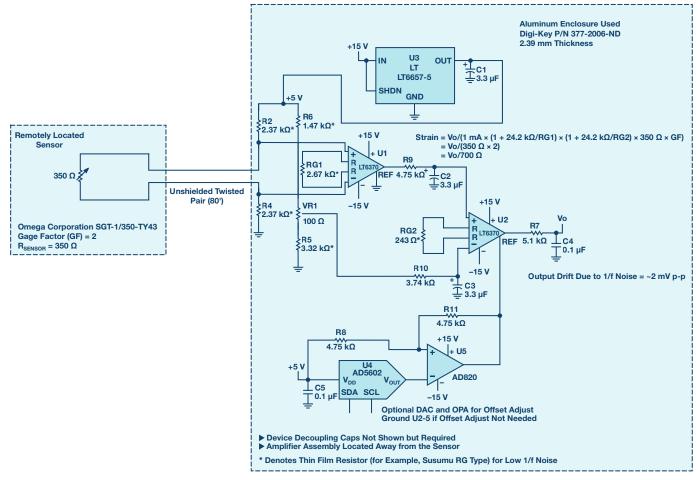

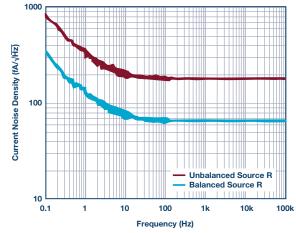

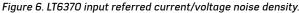

Instrumentation amplifiers are the workhorses of sensing applications. The article explores some ways to take advantage of the amplifiers' balance and excellent dc/low frequency common-mode rejection (CMR). These amplifiers can be used with resistive transducers (for example, strain gage) when the sensor is physically separated from the amplifier.

-16.5 V

# **57** Overcoming Constraints: Design a Precision Bipolar Power Supply on a Simple Buck Controller

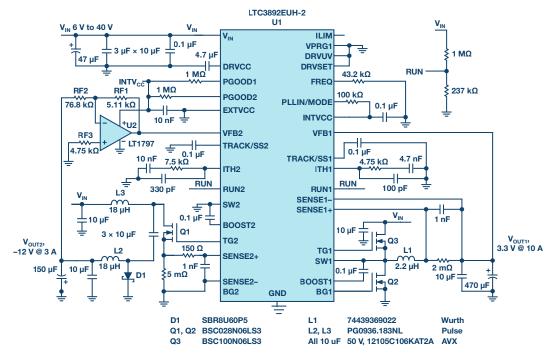

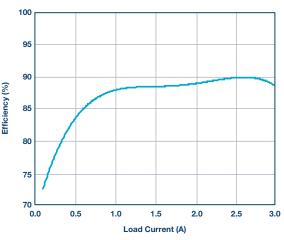

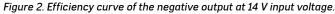

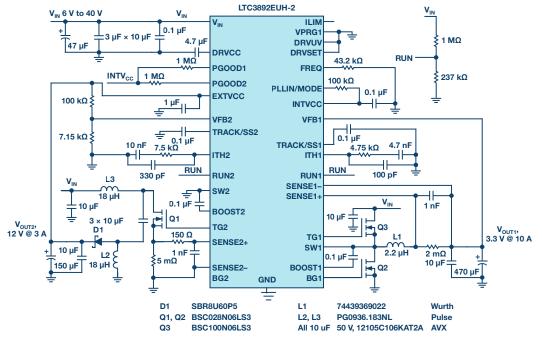

Industrial, automotive, and networking companies use the full array of the available topologies of the dc-to-dc converters, employing buck, boost, and SEPIC in different variations. The obvious solution to reducing development cost is employing already approved and verified controllers for multiple topologies. This article explains how to use this buck controller to generate negative voltages and positive outputs immune to input voltage drops and spikes.

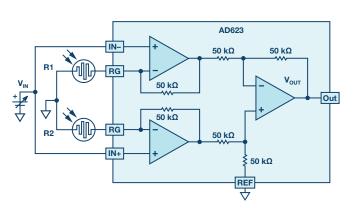

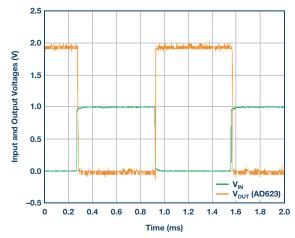

# 60 Rarely Asked Questions—Issue 160: Simple Circuit Measures Relative Intensity of Two Light Sources

Can you measure a difference signal with an instrumentation amplifier? That's the question for our monthly RAQ. In many lighting applications, measuring the relative intensity of two light sources is more important than measuring the intensity of either of them.

# Bernhard Siegel, Editor

Bernhard became editor of Analog Dialogue in March 2017. He has been with Analog Devices for over 25 years, starting at the ADI Munich office in Germany. In his current role as the chief technical

editor, he is responsible for the worldwide technical article program within Analog Devices.

Bernhard has worked in various engineering roles including sales, field applications, and product engineering, as well as in technical support and marketing roles.

Residing near Munich, Germany, Bernhard enjoys spending time with his family and playing trombone and euphonium in both a brass band and a symphony orchestra.

You can reach him at *bernhard.siegel@analog.com*.

*Analog Dialogue* is a technical magazine created and published by Analog Devices. It provides in-depth design related information on products, applications, technology, software, and system solutions for analog, digital, and mixed-signal processing. Published continuously for over 50 years—starting in 1967—it is produced as a monthly online edition and as a printable quarterly journal featuring article collections. For history buffs, the *Analog Dialogue* archive includes all issues, starting with Volume 1, Number 1, and four special anniversary editions. To access articles, the archive, the journal, design resources, and to subscribe, visit the *Analog Dialogue* homepage, *analogdialogue.com*.

# Use of Integrated Passives in Micromodule SIPs

By Mark Murphy and Pat McGuinness

# Share on 🕥 🚹 in

# Introduction

Integrated passives are nothing new in our business—they're long established and well understood. In fact, ADI produced such components for the market in the past. When standalone discrete passives or even integrated passive networks are included as part of a chipset, then routing parasitics, device compatibility, and board assembly considerations will require careful design management. While integrated passives continue to have a strong presence in the industry, their most significant value begins to be realized only when they are included in system in package applications.

A new integrated passives technology initiative (*i*Passives<sup>™</sup>) began at ADI several years ago. The aim of this initiative was to deliver passive components, diodes, resistors, inductors, and capacitors that could enable ADI to encompass more of the signal chain while overcoming the past limitations and complexities of the existing approaches of adopting passive components. The demand from ADI's customer base for more complete solutions in spatially efficient footprints also drove these developments. From the designer's perspective, *i*Passives can be viewed as a flexible design tool that enables the design of system solutions with best-in-class performance and robustness in exceptionally short development cycle times. ADI has many signal conditioning ICs whose superior performance is enabled by the unique silicon fabrication processes that we have at our disposal. Without the complexity of having to develop highly complex integrated processes, ADI can leverage the diversity of its existing offering to produce plug and play systems that have exceptional performance characteristics. The integrated passives technology is being used to tie this all together in highly customizable networks and packaged up via system in package technology to create µModule® devices that are fully qualified, tested, and characterized. Systems that were previously board-level solutions can now be reduced to what appears as a single device. From our customer perspective, they now get complete solutions with excellent out of the box performance, short development cycles, and cost savingsall in very compact packages.

# **Passives Technology**

So, let's go back briefly to the basics and remind ourselves of what a passive component is. Passive components are unpowered devices that give a relatively simple relationship between current and voltage. These components are resistors, capacitors, inductors, transformers (which are effectively coupled inductors), and diodes. Sometimes the current-voltage relationship is very simple, like in a resistor where the current is linearly dependent on voltage. For a diode there is a direct relationship between current and voltage, but the relationship is exponential. In inductors and capacitors, the relationship has a current and voltage transient dependency. Tables 1 shows the formulae that define these relationships for four of the basic passive components:

# Table 1. Basic Formulae for Primary Passive Components

| Discrete Element | Equation                                              | Symbol |                                                                    |

|------------------|-------------------------------------------------------|--------|--------------------------------------------------------------------|

| Resistor         | $V = I \times R$                                      |        | V = Voltage<br>I = Current                                         |

| Capacitor        | $I = C \frac{dV}{dt}$                                 | ⊣⊢     | t = Time<br>R = Resistance in ohms<br>C = Capacitance in farads    |

| Inductor         | $V = L \frac{dI}{dt}$                                 |        | $L = Coil inductance in henrys$ $I_{s} = Diode saturation current$ |

| Diode            | $I = I_s \left( e^{\frac{V}{\eta^{V_T}}} - 1 \right)$ |        | $V_{T}$ = Thermal voltage<br>h = Diode ideality factor             |

Passive devices can be used individually, can be connected in series or parallel, and are essential components in analog signal processing (RLC for amplification, attenuation, coupling, tuning, and filtering), in digital signal processing (pull-up, pull-down, and impedance matching resistors), in EMI suppression (LC noise suppression), and in power management (R for current sensing and limiting, LC for energy accumulation).

# Limitations of Discrete Components

Historically, passive components have been discrete, meaning they are manufactured separately and connected in a circuit using conductive wires or tracks on a printed circuit board (PCB). Over time they have evolved along three paths: smaller size, lower cost, and higher performance. The evolution is now mature and optimized, but the size of the footprint and profile means that discrete passive components are always limiting the effort to reduce overall solution area and volume. Passives generally constitute over 80% of the bill of materials in an application, occupy about 60% of the area, and make up about 20% of the overall component spend. These factors compound to produce very complex inventory control and storage challenges.

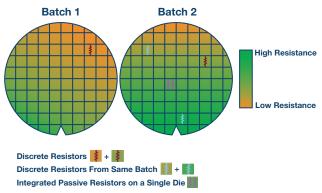

By their very nature, discrete devices are individually processed components. While there may be ways of ensuring that components can be selected from certain process batches, there is still a high degree of uniqueness to every single component. This, however, is a significant disadvantage when it comes to needing very well matched components. For devices that are meant to match, uniqueness and differences between components contribute to errors that degrade time zero circuit performance. Additionally, this performance degradation invariably gets worse across the operating temperature and lifetime of the circuit.

Another drawback to discrete passive devices is that assembly and wiring of individual components takes time, and simply occupies a large space. The elements are connected using a soldering process, generally throughhole or surface-mount technology (SMT) assembly. Through-hole is the older assembly technology where leaded parts are inserted into holes on a PCB, any excess in lead length is clinched and cut back, and a molten wave of solder connects the leads of the devices to the PCB interconnect tracks. Surface-mount assembly has enabled the development of smaller passive components; in this case, a landing pattern is etched on a PCB, solder paste is used to cover the patterns, and then SMT components are positioned using a pick and place machine. The PCB is then run through a soldering reflow process, where the solder liquefies and establishes electrical connections, and, when cooled, the solder solidifies and mechanically affixes the SMT components to the PCB. The primary problem with both assembly technologies is that the soldering processes can be very unreliable and, in an industry where defect targets are in parts per million, this is becoming more and more of a concern. Several factors are important in ensuring solder reliability: the actual composition of the solder (which is generally lead free now and thus less reliable), mechanical stability during the solder reflow process (mechanical vibrations can render a dry solder joint), purity of the solder (any contaminants adversely affect solder reliability), and the time and temperature in the solder reflow process. How quickly solder is heated, what the actual temperature and uniformity of temperature is, and for how long the solder is heated are critical. Any variation here can lead to damage to landing pads or through-holes, or it can induce mechanical stress on components that will lead to failure over time.

Another limitation in employing passive components on PCBs due to them being spread apart is that trace lengths need to be long. This can introduce unaccounted for parasitic elements that can limit performance and the repeatability of results. Typically, PCB traces have in the order of 1 nH/mm length and capacitance that depends on the width of trace and proximity to its neighbors. PCB trace tolerances contribute to variability in parasitics, so not only are the parasitics disruptive, but they are also unpredictable. Tighter tolerances on PCB boards cost more.

Passive devices also present a lot of potential contact points to the outside world, points where ESD events can occur, via manual or machine handling. Again, this has consequences and risks in overall reliability and robustness.

# Advantages of Integrated Passives

Before delving into the advantages integrated passives have over their discrete passive counterparts, let us first outline the origins of integrated passives. Integrated circuits now contain many transistors (millions in fact) wired together with very well defined metal interconnections. Special processes have been developed for analog type applications like DACs and ADCs that contain portfolios of passive components such as resistors and capacitors in addition to the transistors. To achieve the performances required in these precision analog applications, very high quality passive components have been developed. It is these high quality passive components that are used to build integrated passives can contain many high quality passive components packed into a very small area. Like integrated circuits, integrated passives are fabricated on large area substrates (wafers) where multiple passive networks are produced at the same time.

One of the most compelling advantages integrated passives have to offer over discrete passives is the precise matching that can be achieved with them. When integrated passive networks are fabricated, all components within a network are manufactured at the same time, under the same conditions, with the same material set and, because of network compactness, essentially in the same place. Passive components manufactured in this way have a much better chance of being very well matched than discrete passive alternatives. To illustrate this let's say we have an application that requires two matched resistors. These resistors are fabricated on circular substrates such as silicon wafers, as illustrated in Figure 1. Due to slight process variations like resistive film thickness, chemical properties of the film, contact resistance, etc., there will be some level of resistance variation within a batch and even more variation across multiple batches. In the example in Figure 1, dark green indicates the resistance is on the high side of the tolerance range and yellow indicates the resistance is on the low side of the tolerance range. For standard discrete devices, there is the possibility that each of the two resistors may come from different fabrication batches as indicated by the two separate resistors drawn in red. The full tolerance range of the process may be observable between the two discrete resistors and hence the matching will not be very good. With special ordering restrictions it may be possible to have the two discrete resistors chosen from the same batch as indicated by the two separate resistors drawn in blue. The tolerance range within just one batch may be observable between the two resistors. While the matching between these resistors will be better than the random discrete case, there is still scope for some level of mismatch. Finally, with integrated passives, the two resistors come from the same die, as indicated by the resistors drawn in black in Figure 1. The tolerance range within one die is the only range that will be observable between the two resistors. Hence, matching between the two resistors will be excellent. Additional techniques of using cross quad layouts and other means can be employed to tighten the spread between the two resistors even further, which culminates in extremely well matched components. Matching between integrated passive components is not only much better than discrete passives at time zero, but will also track better across temperature, mechanical stress, and lifetime due to their manufacture having been so well coupled.

The individual components within integrated passives are placed closely together (within microns in fact) and, because of this, the interconnect parasitics such as trace resistance and inductance can be kept to an absolute minimum. On PCBs, interconnect parasitics can be variable due to trace tolerances and component placement tolerances. With integrated passives, interconnect tolerances and component placement tolerances are extremely tight due to the photolithographic processes employed in their manufacture. On integrated passives, not only are the parasitics very small, but the few that are there are very predictable and, hence, can be reliably accounted for.

The miniaturization of passive networks through integrated passives has the very straightforward benefit of making circuit boards smaller. This leads directly to reducing circuit board costs and to allowing more and more functionality and performance to be packed into a smaller footprint. Building systems with high channel counts becomes much more practical when using integrated passives.

Another significant advantage of integrated passives is the robustness of the complete wiring network around them. Rather than needing lots of soldered connections, integrated passives are essentially forged together in one complete unit, sealed up with glass, and then further protected with a robust plastic encapsulant. Within integrated passive networks, issues with dry solder joints, corrosion, or misplaced components are not present. An additional benefit of integrated passive networks being so well sealed up is that the number of exposed nodes in a system is much reduced. Hence, the possibility of systems being damaged by accidental shorting or electrostatic discharge (ESD) events are significantly diminished.

Maintaining and controlling the stock of components for any circuit board assembly is quite a complex task. Integrated passives having multiple passive components within one device greatly unburdens the customers' bill of materials, which results in the cost of ownership going down. Customers receive integrated passive networks fully tested and proven good. This means that the final board build yields are improved and this not only enables further cost savings but also enhances supply chain predictability.

# Use of Integrated Passives by ADI (*i*Passives)

As alluded to earlier, high quality passive devices have been core to the circuit performances achieved by many of ADI's products over many years. During that time, the range and quality of the passive devices has grown and the integrated passives portfolio now contains a significant number of components. The integrated passives process is modular, which means that the processing steps needed to produce a certain type of passive device need only be performed if that particular component is needed. An *i*Passives network can essentially be built up with just the processing complexity required—no more and no less. As illustrated in Figure 2, there are a number of passives network can be as simple as piecing together the required components.

Figure 2. Building blocks for iPassives.

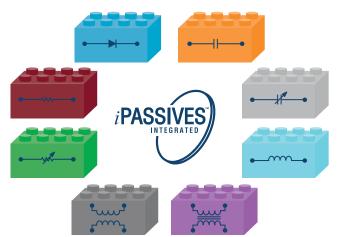

As outlined earlier in this article, integrated passives hold many advantages over discrete passives. ADI has brought these advantages a step further by employing their use in  $\mu$ Module devices. These modules leverage off the capabilities of a diverse range of integrated circuits. These circuits are manufactured through tailored processes that provide enhanced performance and that are not achievable from any one single process. ADI is using *i*Passives to tie these integrated circuits together and in doing so are building complete precision signal chains within a single device. The two  $\mu$ Module device examples in Figure 3 contain data converters, amplifiers, and other components, and bringing them together are passive gain and filtering networks that are built with integrated passives.

Figure 3. µModule product examples using iPassives.

ADI produces precision signal conditioning systems that are highly customizable. By adopting a reusability approach from a huge portfolio of field proven ICs and combining this approach with the versatility of *i*Passives, both the development cycle times and costs are dropping significantly. This decision offers immense benefits to customers who themselves can get to market faster and more efficiently with state-of-the-art performance.

# Conclusion

At first glance, the use of integrated passives may appear only incrementally more advantageous over more established approaches. The advantages, however, turn out to be significant and *i*Passives as employed by ADI are redefining not just what can be done, but also what speeds, costs, and sizes are beneficial to customers.

Mark Murphy [mark.murphy@analog.com] is a product marketing engineer with the Precision Converter Group in Limerick Ireland. He holds a B.S.E.E. from Merrimack College and an M.B.A. from the University of Limerick.

Pat McGuinness

Mark Murphy

Pat McGuinness [pat.mcguinness@analog.com] is a product engineer at Analog Devices with responsibility for the use of integrated passive components in system in package applications. Since joining ADI in 1994, Pat has worked on product yield improvement activities, circuit design, device modeling, and new process development. Throughout his time at ADI he has designed precision converters, switches, sensors, and passive networks. Pat received his bachelor's degree in electrical and microelectronic engineering from University College Cork.

# A Large Current Source with High Accuracy and Fast Settling

By Nick Jiang

# Share on 💙 🚹 💼

Voltage controlled current sources (VCCSs) are widely used in many areas, like medical machine and industrial automation. The dc precision, ac performance, and drive capability of a VCCS are highly important in these applications. This article analyzes the enhanced Howland current source (EHCS) circuit's limitations and shows how to improve it with a composite amplifier topology to implement a  $\pm$ 500 mA current source with high precision and fast settling.

# **Enhanced Howland Current Source**

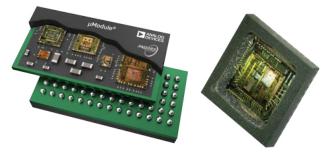

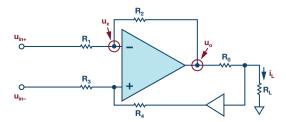

Figure 1. Howland current source circuit.

Figure 1 shows the traditional Howland current source (HCS) circuit, while Equation 1 shows how the output current can be calculated. The output current will be constant if R2 is large enough.

$$i_{L}R_{0}\left[1+\frac{R_{1}}{R_{2}}+R_{L}\left(\frac{1}{R_{2}}+\frac{1-\frac{R_{1}}{R_{2}}\times\frac{R_{4}}{R_{3}}}{R_{0}}\right)\right]=$$

$$u_{in+}\left(\frac{R_{0}}{R_{2}}+\frac{R_{4}}{R_{3}}+1\right)-u_{in-}\left(\frac{R_{4}}{R_{3}}+\frac{R_{1}}{R_{2}}\times\frac{R_{4}}{R_{3}}\right)$$

(1)

Figure 2. Enhanced Howland current source circuit.

While a large R2 will reduce the speed and precision of the circuit, inserting a buffer into the feedback route to form an enhanced Howland current source will eliminate this, as shown in Figure 2. All the current flows through  $R_0$  is through into  $R_1$ . The output current is calculated with Equation 2.

$$i_{L}R_{0}\left[1+\frac{R_{1}}{R_{2}}+R_{L}\left(1-\frac{R_{1}}{R_{2}}\times\frac{R_{4}}{R_{3}}\right)\right] = u_{in+}\left(\frac{R_{4}}{R_{3}}+1\right)-u_{in-}\left(\frac{R_{4}}{R_{3}}+\frac{R_{1}}{R_{2}}\times\frac{R_{4}}{R_{3}}\right)$$

(2)

If R1/R2 = R3/R4 = k, the equation is changed to Equation 3. The output current is independent of the load and only controlled by the input voltage. It's an ideal VCCS.

$$i_L = \frac{u_{in+} - u_{in-}}{kR_0}$$

(3)

# **Performance Analysis**

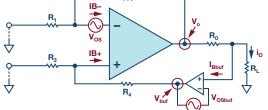

Equation 3 is based on the ideal system. Figure 3 shows the dc error analysis model of the EHCS.  $V_{\rm OS}$  and IB+/IB– are the input offset voltage and bias current of the main amplifier.  $V_{\rm OSbuf}$  and  $I_{\rm Bbuf}$  are the input offset voltage and bias current of the buffer. The total output error can be calculated by Equation 4.

$$I_{O}\left[R_{0}+R_{L}\left(1-\frac{R_{1}+R_{2}}{R_{1}}\times\frac{R_{3}}{R_{3}+R_{4}}\right)\right]=\left(\frac{R_{2}}{R_{1}}+1\right)\times V_{os}+\left(\frac{R_{2}}{R_{1}}+1\right)\times \frac{R_{3}R_{4}}{R_{3}+R_{4}}\times I_{B+}-\left(\frac{R_{2}}{R_{1}}+1\right)\times \frac{R_{1}R_{2}}{R_{1}+R_{2}}\times I_{B-}+\left(\frac{R_{2}}{R_{1}}+1\right)\times \frac{R_{3}}{R_{3}+R_{4}}\times V_{OSbuf}-I_{Bbuf}R_{0}$$

$$(4)$$

Figure 3. Offset voltage calculation.

Ignore the mismatch from the gain resistors, and consider  $R_1/R_2 = R_3/R_4$ = k,  $R_1//R_2 = R_3//R_4$ . The output offset current depends on the amplifiers' offset and bias current, as shown in Equation 5.

$$I_{O} = \left(\frac{1}{k} + 1\right) \times \frac{1}{R_{0}} \times V_{os} + \left(\frac{1}{k} + 1\right) \times \frac{1}{R_{0}} \times \frac{R_{1}R_{2}}{R_{1} + R_{2}} \times I_{os} + \frac{1}{R_{0}} \times \frac{V_{OSbuf} - I_{Bbuf}}{V_{OSbuf} - I_{Bbuf}}$$

(5)

Taking the mismatch of  $R_1/R_2$  and  $R_3/R_4$  into consideration,  $R_L$  will influence the output offset current. The worst relative error is shown in Equation 6. The error depends on  $R_L/R_0$  and k. A smaller load resistor and higher k will decrease the offset error.

Max Relative Error of

$$I_O = \frac{R_L}{R_0} \times \frac{2\Delta_k}{k(k+1)}$$

(6)

We can also calculate the temperature drift of the circuit, which comes from amplifiers and resistors. Amplifiers' offset voltage and bias current change with the work temperature. For most CMOS input amplifiers, the bias current doubles for every increase of 10°C. The drift of resistors changes a lot with different types. For example, carbon composition units' TC is approximately 1500 ppm/°C, while metal film and bulk metal resistors' TC can be 1 ppm/°C.

#### **Table 1. Precision Amplifiers Parameters**

| Devices   | V <sub>os</sub> Max<br>(µV) | IB Max (pA) | GPB (MHz) | Slew Rate<br>(V/µs) | lsc (mA) |

|-----------|-----------------------------|-------------|-----------|---------------------|----------|

| ADA4522   | 5                           | 150         | 3         | 1.3                 | 22       |

| ADA4077   | 25                          | 1500        | 4         | 1                   | 22       |

| LTC2057HV | 4                           | 120         | 2         | 1.2                 | 26       |

| LT1012    | 25                          | 100         | 1         | 0.2                 | 13       |

Choosing a precision amplifier is good for the dc accuracy of the output current. However, there are many limitations in the precision amplifier selection. The drive capability and ac performance are not good enough. Table 1 lists some common precision amplifiers. We want to build a  $\pm 500$  mA current source with 1 µs settling time. For a current source we would need high drive capability. For a current source with additional high settling time we need good ac performance. In general, precision amplifiers do not provide that specification combination as the slew rate and bandwidth are not good enough. This requires choosing from a few other amplifiers.

# **EHCS** Implementation

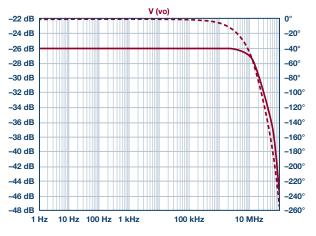

ADA4870 is a high speed, high voltage, and high drive capacity amplifier. It can supply 10 V to 40 V with 1.2 A output current limitation. Its bandwidth is over 52 MHz for a large signal and the slew rate is up to 2500 V/ $\mu$ s. All these specifications make it the right fit for fast settling and a large current source. Figure 4 shows an EHCS circuit based on the ADA4870 that generates a  $\pm$ 500 mA output current source by 10 V input.

Figure 4. EHCS circuit based on ADA4870.

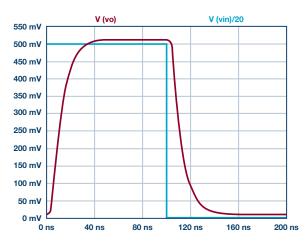

In ac specifications, we are more care about settling time, slew rate, bandwidth, and noise. The settling time is about 60 ns and bandwidth is about 18 MHz as shown in Figure 5. The output current slew rate can be calculated by measuring the slope of the rising and falling stage. The positive and negative slew rate are +25 A/µs and -25 A/µs. The noise performance is shown in the output noise density curve. It's about 24 nV/ $\sqrt{\text{Hz}}$  at 1 kHz.

Figure 5. Settling time and frequency response of an EHCS based on ADA4870

Figure 6. Output noise density curve of EHCS based on ADA4870.

Due to large input offset voltage and bias current, the dc precision is not good in this circuit. Table 2 shows different dc error sources and contribution. The main dc error comes from the  $V_{os}$  and  $I_B$  of ADA4870. The typical output current offset is about 11.06 mA, which is about 2.21% range error referring to 500 mA full range.

# Table 2. The DC Error of EHCS Based on ADA4870

| Error Source       | Parameters (Typ) | Error Output (mA) | Percentage |

|--------------------|------------------|-------------------|------------|

| IB                 | –12 µA           | 6.00              | 54.2%      |

| IB+                | +9 µA            | 4.50              | 40.7%      |

| V <sub>os</sub>    | 1 mV             | 0.55              | 5.0%       |

| I <sub>Bbuf</sub>  | –0.1 μA          | 0.00              | 0.0%       |

| V <sub>OSbuf</sub> | 0.02 mV          | 0.01              | 0.1%       |

| Total              |                  | 11.06             | 100%       |

# **Composite Amplifier Technology**

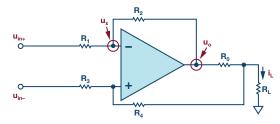

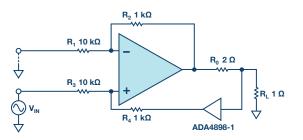

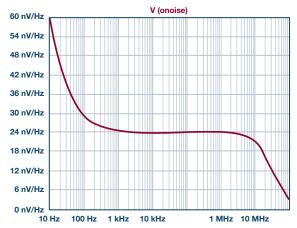

High drive amplifiers like ADA4870's dc parameters limit output current accuracy, and high precision amplifiers don't have enough speed. Here we can combine all these qualities into one circuit with composite amplifier technology. Figure 7 shows the composite amplifier enhanced Howland current source (CAEHCS) that is formed by ADA4870 and ADA4898-2.

Figure 7. EHCS circuit with composite amplifier.

ADA4898-2 is chosen to form the composite amplifier for its excellent ac and dc performance. Its –3 dB bandwidth is 63 MHz. The settling time to 0.1% with a 5 V output step is 90 ns and the slew rate is up to 55 V/µs. It has ultralow noise, too. The voltage noise density is 0.9 nV/ $\sqrt{Hz}$  and current noise density is 2.4 pA/ $\sqrt{Hz}$ . As for dc specifications, it performs well, too. The typical input offset voltage is 20 µV with 1 µV/°C temperature drift. The bias current is 0.1 µA. Table 3 shows the dc error of the CAEHCS. The output current offset is decreased to 0.121 mA, which means the range error is lower than 0.03%.

## Table 3. The DC Error of CAEHCS Based on ADA4898

| Error Source       | Parameters (Typ) | Error Output (mA) | Percentage |

|--------------------|------------------|-------------------|------------|

| IB-                | –0.1 μA          | 0.050             | 41.3%      |

| IB+                | +0.1 μA          | 0.0050            | 41.3%      |

| V <sub>os</sub>    | 20 mV            | 0.011             | 9.1%       |

| I <sub>Bbuf</sub>  | –0.1 μA          | 0.000             | 0.1%       |

| V <sub>OSbuf</sub> | 20 µV            | 0.01              | 8.2%       |

| Total              |                  | 0.121             | 100%       |

The ac performance of the CAEHCS is shown in Table 4. The settling time and bandwidth are lower than EHCS due to the loop delay of the composite amplifier. CAEHCS output noise is much lower than EHCS output noise due to low current noise of ADA4898-2. As specified in the data sheet, the ADA4870's invert input current noise density is 47 pA/ $\sqrt{\text{Hz}}$ . With several k $\Omega$  resistors, it will generate much higher noise than the voltage noise (2.1 nV/ $\sqrt{\text{Hz}}$ ). While the input current noise density of the CAEHCS is 2.4 pA/ $\sqrt{\text{Hz}}$ . It will generate much lower output noise.

## Table 4. The AC Specification of the CAEHCS

| Parameter                                              | CAEHCS | EHCS |

|--------------------------------------------------------|--------|------|

| Settling time (ns)                                     | 200    | 60   |

| Slew rate (A/µs)                                       | 7.7    | 25   |

| Bandwidth (MHz)                                        | 6      | 18   |

| Output Noise Density<br>at 1 kHz (nV/ <del>√Hz</del> ) | 4      | 24   |

Above all, CAEHCS has greatly improved the dc accuracy of the VCCS with comparable drive capacity and ac performance. Besides, there are many selections of the composite amplifiers for different requirements. Table 5 shows the performance of different amplifiers in the CAEHCS circuit. LT6275 is the best in ac performance. Its settling time can be within 100 ns, and the slew rate is up to 15 A/µs. Zero-drift amplifiers like ADA4522-2 are suitable for high precision applications that have about 0.002 mA output current offset error.

## Table 5. Selection of Main Amplifier in CAEHCS

| Main Amplifier | EHCS      | CAEHCS    |

|----------------|-----------|-----------|

| ADA4898        | Good      | Good      |

| LT6275         | Good      | Excellent |

| ADA4522        | Excellent | Not good  |

# **Test Results**

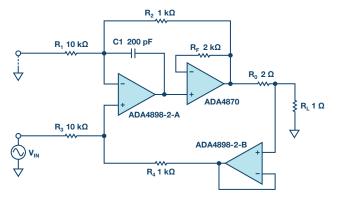

The performance of the EHCS and CATHCS based on ADA4898 are shown in Table 6 and Figure 8.

# Table 6. Comparison of EHCS vs. CAEHCS

| Main Amplifier |                               | EHCS | CAEHCS |

|----------------|-------------------------------|------|--------|

| DC Parameters  | Output current<br>offset (mA) | 10.9 | 0.2    |

| AC Parameters  | Settling time (ns)            | 100  | 100    |

|                | Slew rate (A/µs)              | 22.2 | 12.6   |

|                | Bandwidth (MHz)               | 18   | 8      |

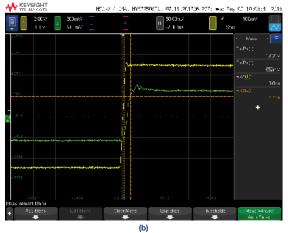

Figure 8. The settling time of the ADA4898-2 (CH1-Input, CH2-Output).

The CAEHCS circuit has much better dc specifications than an EHCS circuit. Its output current offset is 0.2 mA, while the EHCS circuit's output current offset is 10.9 mA. The CAEHCS circuit has good ac specifications, too. The settling time both are about 100 ns. The bandwidth of the EHCS circuit is 18 MHz, and the CAEHCS circuit is 8 MHz.

The performance of the CAEHCS based on the ADA4522-2 and LT6275 is shown in Table 7. The output offset error of ADA4522-2 version is lower to 0.04 mA. The settling time of LT6275 version is about 60 ns and the output current slew rate is up to  $16.6 \text{ A/}\mu\text{s}$ , which is shown in Figure 9.

# Table 7. Test Results of the Different Main Amplifier in CAEHCS

| Main Amplifier | los (mA) | Settling time<br>(ns) | Slew Rate<br>(A/µs) | Bandwidth<br>(MHz) |

|----------------|----------|-----------------------|---------------------|--------------------|

| ADA4898        | 0.2      | 100                   | 12.6                | 10                 |

| LT6275         | 0.8      | 60                    | 16.6                | 11                 |

| ADA4522        | 0.04     | 1000                  | 0.4                 | 1.2                |

Figure 9. The settling time of the LT6275 (CH1-Input, CH2-Output).

# **Thermal Consideration**

The output current of the VCCS can be several hundred milliamperes. The whole power dissipation can be several watts. If output efficiency is bad, the temperature of the part will rise rapidly. The thermal resistance ( $\theta_{JR}$ ) of ADA4870 without a head sink can be 15.95°C/W. The temperature rising can be calculated by using Equation 7.

$$\Gamma_{\rm rise} = \theta_{\rm JA} \times P \tag{7}$$

The value of  $R_{0}$  will influence the power dissipation of ADA4870. Table 8 shows the temperature rise with different  $R_{0}$  selected at a  $\pm 20$  V supply. The temperature rising will decrease greatly when larger  $R_{0}$  is used. Therefore, larger  $R_{0}$  is recommended to decrease the temperature rise.

# Table 8. ADA4870's Power Dissipation and Temperature Rise vs. RO (Io = 500 mA)

| RL/Ω | Power Dissipation (W) |                     | Temperature Rise (°C) |                     |

|------|-----------------------|---------------------|-----------------------|---------------------|

|      | $R_0 = 2 \Omega$      | $R_0 = 10 \ \Omega$ | $R_0 = 2 \Omega$      | $R_0 = 10 \ \Omega$ |

| 1    | 6.92                  | 4.92                | 110.4                 | 78.5                |

| 5    | 5.92                  | 3.92                | 94.5                  | 62.6                |

| 10   | 4.67                  | 2.67                | 74.6                  | 42.7                |

# Conclusion

The CAEHCS circuit that combines a high drive amplifier and a high precision amplifier can provide excellent ac and dc performance with large output capacity in VCCS applications. ADA4870 combined with ADA4898, LT6275, and ADA4522 are recommended for use in this circuit.

Nick Jiang is a product applications engineer in the Analog Devices Linear and Precision Technology Group, and he is based in Beijing. He graduated from Xi'an Jiaotong University, with a bachelor's and master's degree in electrical engineering.

Nick Jiang

# Modeling and Control for a Current-Mode Buck Converter with a Secondary LC Filter

By Ricky Yang

# Share on 💙 🚹 💼

# Introduction

Modern signal processing system design utilizing ADCs, PLLs, and RF transceivers demands lower power consumption and higher system performance. Selecting proper power supplies for those noise sensitive devices is always the pain point for system designers. There is always a trade-off between high efficiency and high performance.

Traditionally, LDO regulators are often used to power those noise sensitive devices. LDO regulators reject the low frequency noise that often presents in system power supplies and they provide clean power to ADCs, PLLs, or RF transceivers. But LDO regulators usually have low efficiency, especially in systems where LDO regulators must regulate down from a power rail several volts above their output voltage. In this kind of situation, LDO regulators typically offer 30% to 50% efficiency, while using switching regulators can reach 90% or even higher efficiency.

Switching regulators are more efficient than LDO regulators, but they are too noisy to directly power ADCs or PLLs without significant performance degradation. One of the noise sources of switching regulators is the output ripple, which can appear as distinct tones or spurs in ADCs output spectrum. To avoid degrading the signal-to-noise ratio (SNR) and spurious-free dynamic range (SFDR), minimizing the output ripple and output noise of switching regulators can be very important.

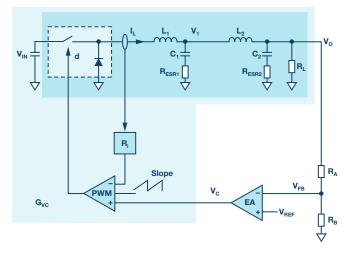

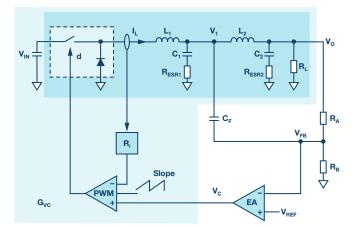

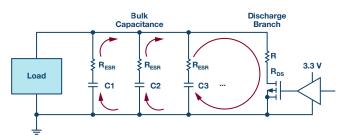

In order to maintain high efficiency and high system performance at the same time, it is often desirable to add a secondary LC filter ( $L_2$  and  $C_2$ ) to the output of switching regulator to reduce the ripple and noise, as Figure 1 shows. However, the two-stage LC output filter has associated disadvantages, too. The power stage transfer function is ideally modeled as a fourth-order system that can easily be unstable. If the sample data effect of a current loop<sup>1</sup> is also taken into consideration, the complete control-to-output transfer function is shown to be fifth order. An alternate solution is to sense the output voltage from the primary LC filter ( $L_1$  and  $C_1$ ) point to stabilize the system. However, applying this approach results in poor output voltage regulation due to the large voltage drops on the secondary LC filter when the load current is heavy, which is not acceptable in some applications.

In this article, a new hybrid feedback method is proposed to provide adequate stability margin and maintain the output accuracy over all the load condition in the application where switching regulators with secondary LC filters are used to provide high efficiency, high performance power supplies to ADCs, PLLs, or RF transceivers. There has been some published research work on the dc-to-dc converter with a secondary LC output filter.<sup>2-5</sup> Specifically, the articles "Control Loop Design for Two-Stage DC-to-DC Converters with Low Voltage/High Current Output" and "Comparative Evaluation of Multiloop Control Schemes for a High Bandwidth AC Power Source with a Two-Stage LC Output Filter" discuss the modeling and control of a two-stage voltage-mode converter, which can't be directly applied to a current-mode converter. A current-mode converter with a secondary LC filter has been analyzed and modeled in "Secondary LC Filter Analysis and Design Techniques for Current-Mode-Controlled Converters" and "Three-Loop Control for Multimodule Converter Systems." However, both articles have an assumption that the secondary inductor has a much smaller inductance value than the primary inductor, which is not always eligible in real applications.

Figure 1. Circuit diagram of a current-mode buck converter with a secondary LC filter.

The outline of this article is as follows:

The small signal modeling of a buck converter with a secondary LC filter is analyzed. A new fifth-order control-to-output transfer function is presented, which is very accurate regardless of the peripheral inductor and capacitor parameters.

A new hybrid feedback method is proposed to provide adequate stability margins while maintaining good dc accuracy of the output voltage. The limitation of the feedback parameters has been analyzed for the first time, which can provide basic criteria for practical design.

Based on the power stage small signal model and new hybrid feedback method, the compensation network is designed. The stability of the closed-loop transfer function is evaluated using a Nyquist plot.

A simple design example is presented based on the power management product ADP5014. With the secondary LC filter, the output noise of ADP5014 in a high frequency range is even better than an LDO regulator.

Appendix I and Appendix II present necessary small signal transfer function for power stage and feedback network respectively.

# Small Signal Modeling of Power Stage

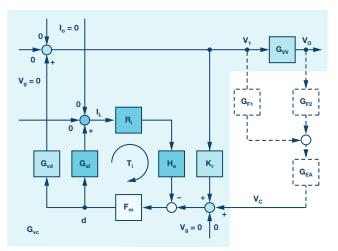

Figure 2 shows the small signal block diagram for Figure 1. The control loop is composed by inner current loop and outer voltage loop. The sample data coefficient  $H_e(s)$  in the current loop refers to the model proposed by Raymond B. Ridley in "A New, Continuous-Time Model for Current-Mode Control." Note that in the simplified small signal block diagram in Figure 2, the input voltage disturbance and load current disturbance are assumed to be zero since transfer functions related with input voltage and load current will not be discussed in this article.

Figure 2. A small signal block diagram of a current-mode buck converter with a secondary LC filter.

## **Buck Converter Example**

The new small signal model is demonstrated with a current-mode buck converter with the following parameters:

- $\triangleright$  V<sub>g</sub> = 5 V

- ▶ V<sub>0</sub> = 2 V

- ► L<sub>1</sub> = 0.8 µH

- ▶ L<sub>2</sub> = 0.22 µH

- ► C<sub>1</sub> = 47 µF

- ► C<sub>2</sub> = 3× 47 µF

- $R_{ESR1} = 2 m\Omega$

- $R_{ESR2} = 2 m\Omega$

- R<sub>L</sub> = 1 Ω

- R<sub>i</sub> = 0.1 Ω

- T<sub>s</sub> = 0.833 µs

## **Current-Loop Gain**

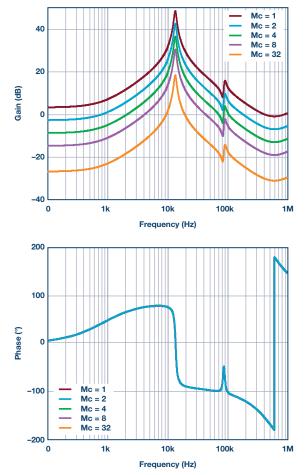

The first transfer function of interest is the current-loop gain measured at the output of the duty-cycle modulator. The resulting current loop transfer function (see Equation 16 in Appendix I) exhibits a fourth-order system with two pairs of complex conjugate poles, which results in two system resonances ( $\omega_1$  and  $\omega_2$ ). Both of these two resonance frequency are determined by L<sub>1</sub>, L<sub>2</sub>, C<sub>1</sub>, and C<sub>2</sub>. A domain zero is contributed by load resistor R<sub>L</sub>, C<sub>1</sub>, and C<sub>2</sub>. Dne pair of complex conjugate zeros ( $\omega_3$ ) is determined by L<sub>2</sub>, C<sub>1</sub>, and C<sub>2</sub>. Besides, the sample data coefficient  $H_e(s)$  in the current loop will introduce a complex pair of right half plane (RHP) zeros at half of the switching frequency.

Compared with the conventional current-mode buck converter without the secondary LC filter, the new current-loop gain has one more pair of complex conjugate poles and one more pair of complex conjugate zeros, which locate very close to each other.

Figure 3. Buck converter current-loop gain.

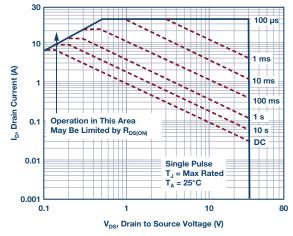

Figure 3 shows a plot of the current-loop gain with different values of external ramp. For the case without external slope compensation ( $M_c = 1$ ), it can be seen that there is very little phase margin in the current loop, which may lead to subharmonic oscillation. With added external slope compensation, the shape of the gain and phase curves do not change, but the amplitude of the gain will decrease and phase margin will increase.

#### Control-to-Output Gain

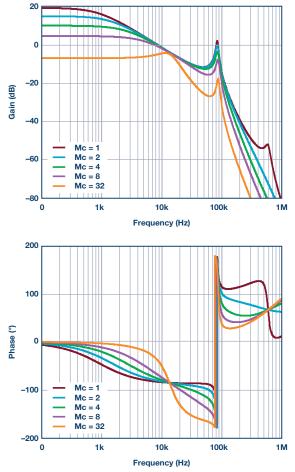

A new control-to-output transfer function is created when the current loop is closed. The resulting control-to-output transfer function (see Equation 19 in Appendix I) exhibits a fifth-order system with one domain pole ( $\omega_p$ ) and two pairs of complex conjugate poles ( $\omega_1$  and  $\omega_p$ ). The domain pole is mainly determined by load resistor R<sub>L</sub>, C<sub>1</sub>, and C<sub>2</sub>. The lower frequency pair of conjugate poles is determined by L<sub>2</sub>, C<sub>1</sub>, and C<sub>2</sub>, while the higher frequency pair of conjugate poles locates at half of the switching frequency. Additionally, two zeros are contributed by the *ESR* of C<sub>1</sub> and *ESR* of C<sub>2</sub>, respectively.

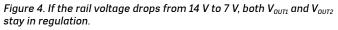

Figure 4 shows a plot of the control-to-output loop gain with different values of external ramp. Compared with the conventional current-mode buck converter, there is one more pair complex conjugate poles ( $\omega$ ) in the control-to-output gain of current-mode buck converter with a secondary LC filter. The additional resonant poles will give up to 180° additional phase delay. The phase margin drops dramatically, and it can make the system unstable even with Type III compensation. Besides, Figure 4 clearly shows the transition from current-mode to voltage-mode control as the slope compensation is increased.

Figure 4. Control-to-output transfer function for a buck converter

# The Hybrid Feedback Method

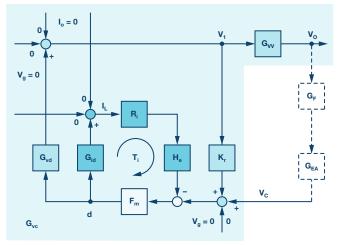

This article presents a new hybrid feedback structure, as Figure 5(a) shows. The idea of hybrid feedback is to stabilize the control loop by using an additional capacitor feedback from the primary LC filter. The

outer voltage feedback from the output through resistor divider is defined as the remote voltage feedback and the inner voltage feedback though capacitor  $C_F$  will be referred to as the local voltage feedback hereafter. The remote feedback and local feedback carry different information on the frequency domain. Specifically, the remote feedback senses the low frequency signal to provide good dc regulation of the output, while the local feedback senses the high frequency signal to provide good ac stability for the system. Figure 5(b) shows the simplified small signal block diagram for Figure 5(a).

Figure 5. A current-mode buck converter with a proposed hybrid feedback method, showing (a) a circuit diagram and (b) a small signal model.

#### The Feedback Network Transfer Function

The resulting equivalent transfer function (see Equation 31 and Equation 32 in Appendix II) of a hybrid feedback structure differs significantly from the transfer function of conventional resistor divider feedback. The new hybrid feedback transfer function has more zeros than poles, and the additional zeros will lead to 180° phase ahead at the resonant frequency determined by  $L_2$  and  $C_2$ . Therefore, with the hybrid feedback method, the additional phase delay in control-to-output transfer function will be compensated for by the additional zeros in the feedback transfer function, which will facilitate the compensation design based on the complete control-to-feedback transfer function.

#### The Limitation of Feedback Parameters

Apart from those parameters in the power stage, there are two more parameters in the feedback transfer function. Parameter  $\beta$  (see Equation 30 in Appendix II) is the output voltage magnification ratio, which is already well-known. However, the parameter  $\alpha$  is a brand new concept.

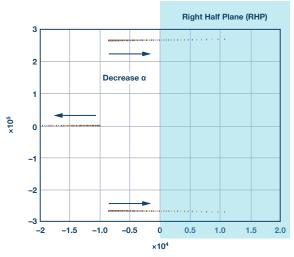

The feedback parameter  $\alpha$  (see Equation 29 in Appendix II) can be adjusted to understand the behavior of the feedback transfer function. Figure 6 exhibits the change trend of the zeros in the feedback transfer when  $\alpha$  is decreased. It clearly shows that one pair of conjugate zeros will be pushed from left half plane (LHP) to right half plane (RHP) with decreased  $\alpha$ .

Figure 6. Effect of feedback parameter  $\alpha$  on the zeros of the feedback network.

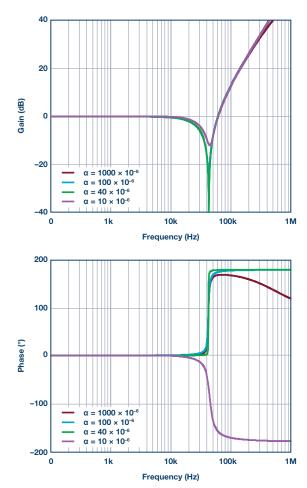

Figure 7 is a plot of the feedback transfer function with a different  $\alpha$ . It shows that when  $\alpha$  is decreased to  $10^{-6}$  (for example:  $R_A$  = 10k,  $C_F$  = 1 nF), the transfer function of the feedback network will exhibit 180° phase delay, which means the complex zeros have become RHP zeros. The feedback transfer function has been simplified to a new form (see Equation 33 in Appendix II). To keep the zeros in the LHP, the parameter  $\alpha$  should always meet the following condition:

$$\alpha > \frac{L_2 \times C_2}{\frac{L_2}{R_L} + R_{ESR2} \times C_2}$$

(Formula 1)

Formula 1 gives a minimum limitation basis for feedback parameter  $\alpha$ . As long as the condition is satisfied, the control system will be easily stable. However, since  $R_A$  and  $C_F$  will work as an RC filter of output voltage change during a load transient, the load transient performance will be degraded with a very big  $\alpha$ . So  $\alpha$  should not be too large. In practical design, the parameter  $\alpha$  is recommended to be 20% to ~30% bigger than the minimum limitation value.

Figure 7. The transfer function of a proposed hybrid feedback network with a different parameter  $\alpha$ .

# Loop Compensation Design

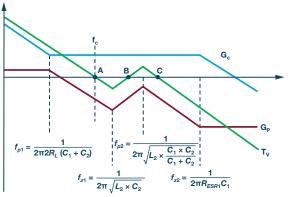

#### Design the compensation

The control-to-feedback transfer function GP(s) can be derived by the product of the control-to-output transfer function  $G_{vc}(s)$  and the feedback transfer function  $G_{FB}(s)$ . The compensation transfer function  $G_{C}(s)$  is designed to have one zero and one pole. The asymptotic Bode plots of the control-to-feedback and compensation transfer function, as well as closed-loop transfer function  $T_v(s)$ , are shown in Figure 8. The following procedures show how to design the compensation transfer function.

Determine the cross frequency ( $f_c$ ). Since the bandwidth is limit by  $f_{z1}$ , choosing an  $f_c$  smaller than  $f_{z1}$  is recommended.

Calculate the gain of  $G_P(s)$  at fc, then the middle frequency band gain of  $G_C(s)$ should be the opposite number of  $G_P(s)$ .

Place the compensation zero at the domain pole  $(f_{n1})$  of the power stage.

Place the compensation pole at the zero  $(f_{\rm z2})$  caused by the ESR of output capacitor  $C_{\rm 1}.$

Figure 8. A loop gain design based on a proposed control-to-output and hybrid feedback transfer function.

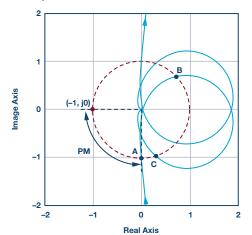

#### Using a Nyquist Plot to Analyze Stability

According to Figure 8, the closed-loop transfer function  $T_v(s)$  has crossed 0 dB three times. The Nyquist plot is used to analyze the stability of closed-loop transfer function, as Figure 9 shows. Since the plot is far away from

(-1, j0), the closed loop is stable and has adequate phase margin. Note that the points A, B, and C in the Nyquist plot correspond to the points A, B, and C in the Bode plot.

Figure 9. Nyquist plot of the closed-loop transfer function.

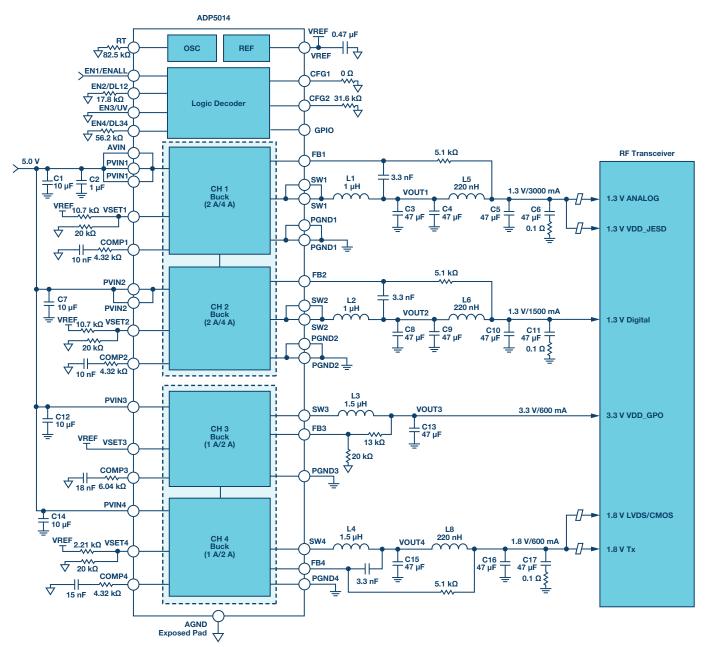

Figure 10. RF transceiver powered up by ADP5014 with a secondary LC filter.

# **Design Example**

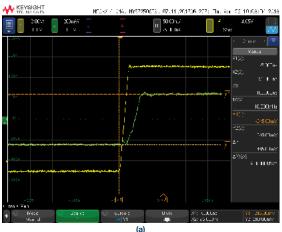

The ADP5014 optimizes many analog blocks to achieve lower output noise at a low frequency range. The unit-gain voltage reference structure also makes its output noise independent from the output voltage setting when  $V_{\text{OUT}}$  setting is less than the  $V_{\text{REF}}$  voltage. A secondary LC filter is added to attenuate the output noise at a high frequency range, especially for fundamental switching ripple and its harmonic. Figure 10 shows the design details.

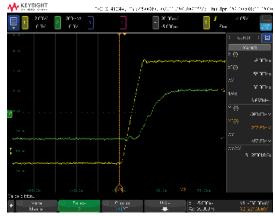

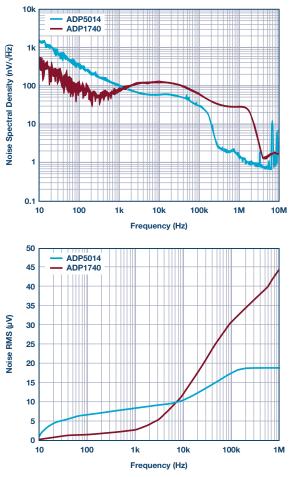

Figure 11 shows the ADP5014 noise spectral density measurement from a 10 Hz to 10 MHz frequency range and integrated rms noise from a 10 Hz to 1 MHz frequency range, compared to the ADP1740s as another traditional, 2 A, low noise LDO regulator. The output noise of ADP5014 in the high frequency range is even better than ADP1740's.

Figure 11. A comparison of output noise performance between ADP5014 and ADP1740 showing (a) noise spectral density and (b) integrated rms noise.

# Conclusion

This article presents a general analysis framework for modeling and control for a current-mode buck converter with a secondary-stage LC output filter. The accurate control-to-output transfer function is discussed. A new hybrid feedback structure is proposed and the feedback parameter limitation is deduced.

The design example shows that a switching regulator with secondary LC filter and hybrid feedback method can provide a clean, stable power supply that is competitive with, or even better than, an LDO regulator.

Modeling and control in this article concentrates on a current-mode buck converter, but the methods described here can be applied to voltage-mode buck converters as well.

# Appendix 1

The power stage transfer functions in Figure 2 are as follows.

$$G_{id} = \frac{i_L}{d} = \frac{V_g}{R_L} \times \frac{\left[1 + R_L \times (C_1 + C_2) \times S\right] \times \left(1 + \frac{S}{Q_3 \times \omega_3} + \frac{S^2}{\omega_3^2}\right)}{\left(1 + \frac{S}{Q_1 \times \omega_1} + \frac{S^2}{\omega_1^2}\right) \times \left(1 + \frac{S}{Q_2 \times \omega_2} + \frac{S^2}{\omega_2^2}\right)}$$

(1)

$$G_{vd} = \frac{v_1}{d} = V_g \times (1 + R_{ESR1} \times C_1 \times S) \times \left(1 + \frac{S}{Q_4 \times \omega_4} + \frac{S^2}{\omega_4^2}\right) \times \left(1 + \frac{S}{Q_1 \times \omega_1} + \frac{S^2}{\omega_1^2}\right) \times \left(1 + \frac{S}{Q_2 \times \omega_2} + \frac{S^2}{\omega_2^2}\right)$$

(2)

$$G_{\nu\nu} = \frac{\nu_o}{\nu_1} = \frac{1 + R_{ESR2} \times C_2 \times S}{1 + \frac{S}{Q_4 \times \omega_4} + \frac{S^2}{\omega_4^2}}$$

(3)

where:

$$\omega_1 = \frac{1}{\sqrt{L_1 \times (C_1 + C_2) + L_2 \times C_2}}$$

(4)

$$Q_1 = \frac{1}{\omega_1 \times \left(\frac{L_1}{R_L} + \frac{L_2}{R_L} + R_{ESR1} \times C_1 + R_{ESR2} \times C_2\right)}$$

(5)

$$\omega_2 = \frac{1}{\sqrt{\frac{L_1 \times L_2 \times C_1 \times C_2}{L_1 \times (C_1 + C_2) + L_2 \times C_2}}}$$

(6)

$$Q_{2} = \frac{1}{\left(L_{1} + L_{2}\right) \times C_{1} \times C_{2} \times R_{ESR1} + \frac{L_{1} \times L_{2} \times C_{1}}{R_{L}} + L_{1} \times C_{1} \times C_{2} \times R_{ESR2}}\right)}$$

(7)

$$\omega_{3} = \frac{1}{\sqrt{L_{2} \times \frac{C_{1} \times C_{2}}{C_{1} + C_{2}}}}$$

(8)

$$Q_{3} = \frac{1}{\frac{L_{2} \times C_{1} + R_{ESR1} \times R_{L} \times C_{1} \times C_{1}}{\omega_{3} \times \frac{C_{2} + R_{ESR2} \times R_{L} \times C_{1} \times C_{2}}{R_{L} \times (C_{1} + C_{2})}}}$$

(9)

$$\omega_4 = \frac{1}{\sqrt{L_2 \times C_2}} \tag{10}$$

$$Q_4 = \frac{1}{\omega_4 \times \left(\frac{L_2}{R_L} + R_{ESR2} \times C_2\right)}$$

where:  $L_1$  is the primary inductance.

$C_1$  is the primary capacitance.

$R_{\mbox{\scriptsize ESR1}}$  is the equivalent series resistance of the primary capacitor.

$L_2$  is the secondary inductance.

$C_2$  is the secondary capacitance.

$R_{\mbox{\tiny ESR2}}$  is the equivalent series resistance of the secondary capacitor.  $R_{\mbox{\tiny L}}$  is the load resistance.

The gain blocks in the current loop are as follows.

$$F_m = \frac{1}{m_c \times S_n \times T_s} \tag{12}$$

$$H_e = 1 - \frac{T_s}{2} \times S + \frac{S}{\omega_h^2} \tag{13}$$

where:

$$m_c = 1 + \frac{S_e}{S_n} \tag{14}$$

$$\omega_h = \frac{\pi}{T_s} \tag{15}$$

where: R<sub>i</sub> is the equivalent current sense resistance

$S_{\scriptscriptstyle e}$  is the sawtooth ramp of slope compensation

$S_{\mbox{\tiny n}}$  is on-time slope of the current sense waveform

$\rm T_{\rm s}$  is the switching period

The current-loop gain is

$$T_{i}(S) = F_{m} \times R_{i} \times G_{id} \times H_{e} = \frac{L_{1}}{R_{L} \times D' \times m_{c} \times T_{s}} \times \frac{[1 + R_{L} \times (C_{1} + C_{2}) \times S] \times \left(1 + \frac{S}{Q_{3} \times \omega_{3}} + \frac{S^{2}}{\omega_{3}^{2}}\right)}{\left(1 + \frac{S}{Q_{1} \times \omega_{1}} + \frac{S^{2}}{\omega_{1}^{2}}\right) \times \left(1 + \frac{S}{Q_{2} \times \omega_{2}} + \frac{S^{2}}{\omega_{2}^{2}}\right)} \times H_{e}}$$

(16)

where:

$$D' = 1 - D \tag{17}$$

where:

D is the duty cycle

According to Figure 2, the gain block  $k_r$  is given by

$$k_r = \frac{R_i \times T_s}{2 \times L_1} \tag{18}$$

The control-to-output transfer function is

$$G_{vc} = \frac{v_o}{v_c} = \frac{R_L}{R_i} \times \frac{1}{1 + \frac{R_L \times T_s}{L_1} \times (mc \times D' - 0.5)} \times F_l(s) \times F_h(s)$$

(19)

where:

(11)

$$F_{l}(s) = \frac{(1 + R_{ESR1} \times C_{1} \times S) \times (1 + R_{ESR2} \times C_{2} \times S)}{\left(1 + \frac{S}{\omega_{p}}\right) \times \left(1 + \frac{S}{Q_{1} \times \omega_{1}} + \frac{S^{2}}{\omega_{1}^{2}}\right)}$$

(20)

$$F_h(s) = \frac{1}{1 + \frac{S}{Q_h \times \omega_h} + \frac{S^2}{\omega_h^2}}$$

(21)

$$\omega_p = \frac{1 + \frac{R_L \times T_S}{L_1} \times (mc \times D' - 0.5)}{R_L \times (C_1 + C_2)}$$

(22)

$$\omega_1 = \frac{1}{\sqrt{L_2 \times \frac{C_1 \times C_2}{C_1 + C_2}}}$$

(23)

$$Q_{1} = \frac{1}{\omega_{1} \times \frac{L_{2} \times C_{1} + (R_{ESR1} + R_{ESR2}) \times R_{L} \times C_{1} \times C_{2}}{R_{L} \times (C_{1} + C_{2})}}$$

(24)

$$Q_h = \frac{1}{\pi \times [m_c \times (1 - D) - 0.5]}$$

(25)

# Appendix II

In Figure 5, the local feedback and remote feedback transfer function are

$$G_{F1} = \frac{R_A \times C_F \times S}{1 + \frac{R_A}{R_B} + R_A \times C_F \times S}$$

(26)

$$G_{F2} = \frac{1}{1 + \frac{R_A}{R_B} + R_A \times C_F \times S}$$

(27)

According to Equation 1 through Equation 27, the control-to-feedback transfer function is given by

$$G_P = \frac{v_{FB}}{v_C} = 1 + (\alpha + R_{ESR2} \times C_2) \times S + \alpha \times \frac{L_2}{R_L} + R_{ESR2} \times C_2 \times S^2 + \alpha \times L_2 \times C_2 \times S^3}{(\beta + \alpha \times S) \times (1 + R_{ESR2} \times C_2 \times S)} \times G_{VC}$$

(28)

where:

$$\alpha = R_A \times C_F \tag{29}$$

$$\beta = 1 + \frac{R_A}{R_B} \tag{30}$$

where:  $R_{\!\scriptscriptstyle A}$  is the top resistor of feedback resistor divider

R<sub>B</sub> is the bottom resistor of feedback resistor divider

C<sub>F</sub> is the local feedback capacitor

The equivalent feedback network transfer function is

$$G_{FB} = \frac{v_{FB}}{v_o} = 1 + (\alpha + R_{ESR2} \times C_2) \times S + \alpha \times \left(\frac{L_2}{R_L} + R_{ESR2} \times C_2\right) \times$$

$$\frac{S^2 + \alpha \times L_2 \times C_2 \times S^3}{(\beta + \alpha \times S) \times (1 + R_{ESR2} \times C_2 \times S)}$$

(31)

The approximate feedback transfer function is

$$G_{FB\_appr} = \frac{1 + \alpha \times S}{(\beta + \alpha \times S) \times (1 + R_{ESR2} \times C_2 \times S)} \times \Delta$$

where:

$$\Delta = 1 + \left(\frac{L_2}{R_L} + R_{ESR2} \times C - \frac{L_2 \times C_2}{\alpha}\right)$$

$$\times S + L_2 \times C_2 \times S^2$$

(33)

In typical low noise applications, the unit-gain voltage reference structure is usually applied, so parameter  $\beta$  will be equal to 1. Then the feedback transfer function is

$$G_{FB} = \frac{\Delta}{1 + R_{ESR2} \times C_2 \times S} \tag{34}$$

# References

<sup>1</sup>Raymond B. Ridley. "A New, Continuous-Time Model for Current-Mode Control." *IEEE Transactions on Power Electronics*, Vol. 6, No. 2, 1991.

<sup>2</sup>Julie Yixuan Zhu and Brad Lehman. "Control Loop Design for Two-Stage DC-to-DC Converters with Low Voltage/High Current Output." *IEEE Transactions on Power Electronics*, Vol 20, No. 1, 2005.

<sup>3</sup>Patricio Cortes, David O. Boillat, Hans Ertl, and Johann W. Kolar. "Comparative Evaluation of Multiloop Control Schemes for a High Bandwidth AC Power Source with a Two-Stage LC Output Filter." International Conference on Renewable Energy Research and Applications, IEEE, 2013.

<sup>4</sup>Raymond B. Ridley. "Secondary LC Filter Analysis and Design Techniques for Current-Mode-Controlled Converters." *IEEE Transactions on Power Electronics*, Vol. 3, No. 4, 1988.

(32) <sup>5</sup>Byungcho Choi, Bo H. Ch, Fred C. Lee, and Raymond B. Ridley. "Three-Loop Control for Multimodule Converter Systems." *Power Electronics IEEE Transactions on Power Electronics*, Vol. 8, No. 4, 1993.

Ricky Yang [ricky.yang@analog.com] joined Analog Devices in April 2008 and works as an applications engineer for the Power Management Group based in Shanghai, China. He graduated from Shanghai Jiaotong University with a bachelor's degree in information and controlling engineering and a master's degree in power electronics. He has 10 years of experience in application work for various switching regulators and related system design.

# Rarely Asked Questions—Issue 158 Driving a Unipolar Gate Driver in a Bipolar Way

# By Ryan Schnell

# Share on 💟 🚹 in

# Question:

Do you need a specialized gate driver to deliver positive and negative voltages?

## Answer:

No, you can adapt a unipolar gate driver to drive in a bipolar manner.

If a positive and negative gate drive is required for a particular power device, circuit designers don't need to search for a special gate driver that handles bipolar operation specifically. Use this simple trick to make a unipolar gate driver deliver bipolar voltages!

When driving medium to high powered MOSFETs and IGBTs, there is a risk of a Miller effect induced turn-on when a high rate of change of voltage is seen across the power device. Current is injected onto the gate of a power device through the gate-to-drain or gate-to-collector capacitance. If the current injection is large enough to bring the gate voltage above the device threshold voltage, parasitic turn-on can be observed resulting in lower efficiency or even device failure.

The Miller effect can be mitigated through use of a very low impedance path from the power device gate to the source or drain, or by driving the gate to a negative voltage with respect to the source or drain. The goal of the Miller effect turn-on mitigation techniques is to keep the gate voltage below a desired threshold when a current spike through the Miller capacitance occurs.

Certain power device types even require a negative voltage to be fully off, necessitating some kind of negative voltage drive coming from the gate driver. Device manufacturers that recommend negative gate drive voltage include standard silicon MOSFETs, IGBTs, SiC, and GaN devices.

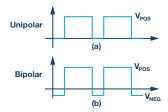

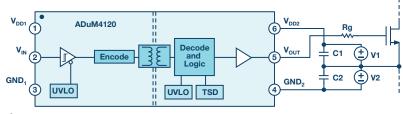

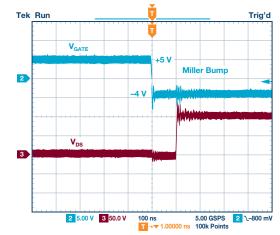

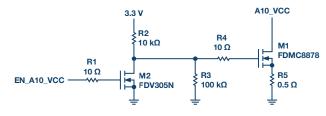

There is a wide selection of isolated gate drivers that operate on a unipolar power supply on the secondary side (the side driving the power device), but much fewer gate driver devices that allow for explicit bipolar voltage drives. One method to overcome this lack of negative gate drive devices is to offset the gate driver from the power device, thereby creating a negative gate drive relative to the source or drain of the power device, while the gate driver IC still only sees a unipolar supply. Unipolar and bipolar gate drive waveform examples are shown in Figure 1.

Figure 1.(a) Unipolar and (b) bipolar gate drive waveforms.

A schematic with ideal voltage sources pictured is shown in Figure 2. In this example, the driver IC is powered by a voltage equal to the sum of V<sub>1</sub> and V<sub>2</sub>, while the gate of the MOSFET is driven to a +V<sub>1</sub> in the ON state and a -V<sub>2</sub> in the OFF state, relative to the MOSFET source node. Note that in this example, both voltage sources are decoupled with individual capacitors. The effective decoupling seen by the gate driver IC is the series combination of the capacitors, which is less than the value of each individual capacitor. Additional decoupling can be added between V<sub>DD</sub> and GND if desired, but it is important to keep C<sub>1</sub> and C<sub>2</sub> as the capacitors provide low impedance paths for the gate current during turn-on and turn-off separately.

Isolated gate driver ICs often come with an undervoltage lockout (UVLO) to prevent a power device from being driven weakly if the gate driver is being driven with too low of a gate voltage. When driving a unipolar gate driver as shown in Figure 2, care must be taken with the expected operation of the UVLO as the UVLO is usually referenced to the ground of the gate driver. Consider a case where  $V_1 = 15$  V,  $V_2 = 9$  V, and the gate driver UVLO is around 11 V, which is common for IGBT operation. If  $V_1$  were to drop more than 4 V, the UVLO would not trigger, but the IGBT would be driven under 11 V during the ON time, thereby underdriving the IGBT.

Creating two separate voltage sources for this purpose can be accomplished by using two isolated power supplies, but cost is often a concern for this approach. If a flyback topology is used, multiple winding taps could be used to obtain multiple voltages relatively easily.

There are isolated voltage source modules that can provide isolated power, and some manufacturers are selecting voltages conducive to power device voltages. One example is RECOM, with devices such as the IGBT targeted product line that produces an isolated +15 V and -9 V rail.

Figure 2. Example bipolar supply setup.

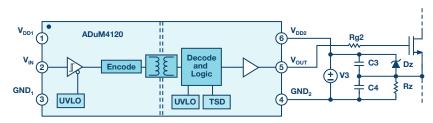

Figure 3. Zener diode example.

For such a large voltage swing, the gate driver must be able to withstand a larger range than the range at which other devices were targeted. Two gate drivers that work well with these voltages are ADI's ADuM4135 and ADuM4136 IGBT gate drivers with *i*Coupler<sup>®</sup> technology, which have a recommended voltage range that allows up to 30 V. Both provide a dedicated ground pin on the output side, allowing the driver UVLO to be referenced against the positive supply rail. The ADuM4135 also includes an integrated Miller Clamp, which can further help suppress the Miller induced turn-on gate voltage bump.

A simple method for creating a bipolar supply from a single voltage source is to create a second voltage source using a biased Zener diode. Although gate drivers provide high currents during the turn-on and turn-off of a power device, the average current actually needed from the power supply is relatively low—often in the tens of mA range for most applications.

The Zener diode can be placed to either regulate the positive or the negative voltage, and can be selected based on which rail needs higher accuracy. The example shown in Figure 3 is setup to regulate the positive voltage more than the negative voltage. One reason to regulate the positive voltage could be if the gate being driven has a tight tolerance on the gate voltage requirements, such as in the case of some GaN devices. Regulating the positive supply also has the added benefit of allowing the UVLO of the gate driver to act as expected, since any fluctuation in V<sub>3</sub> will be attenuated by the Zener diode until V<sub>3</sub> is too low to support the Zener voltage.

Using the Zener diode method to create two supplies out of a single supply also has the benefit of layout savings. Not only does a Zener diode and a resistor effectively replace an entire isolated voltage source, but by using a unipolar isolated gate driver, a six pin device can be used, such as ADI's ADuM4120 with *i*Coupler technology—saving even more space around the gate driver IC along the isolated creepage area.

Ryan Schnell [ryan.schnell@analog.com] is an applications engineer at Analog Devices. His responsibilities include isolated gate drivers that use *i*Coupler technology to achieve isolation, as well as various power management products. He holds a B.S. and an M.S in electrical engineering, and a Ph.D. in power electronics from the University of Colorado.

A reference example of the Zener diode bipolar setup was created using ADI's ADuM4121 and GaN Systems' GS66508T to create a half bridge. The example was designed to have a +5 V and -4 V drive referenced to the device source. The example could easily be adapted to have +6 V and -3 V drive by using a different Zener diode, and the same 9 V isolated power supply. A large deadtime is used to separate the Miller bump from other turn-off transients visually, but in practice the ADuM4121 allows for much shorter deadtimes in the tens of ns range, which is an important metric for high efficiency GaN designs.

Figure 4. ADuM4121 and GS66508T experimental results.

Creating a negative gate volt drive that can mitigate Miller effect parasitic turn-on does not have to be complicated. Many existing gate drivers that are unipolar in operation can be operated to easily drive a gate negative with minimal external circuitry. There are some implications to consider, such as the effective UVLO voltage, but the benefit of such operation is great.

## **Ryan Schnell**

# Over-the-Air (OTA) Updates in Embedded Microcontroller Applications: Design Trade-Offs and Lessons Learned

By Benjamin Bucklin Brown

# Share on 🕥 🚹 in

# Abstract

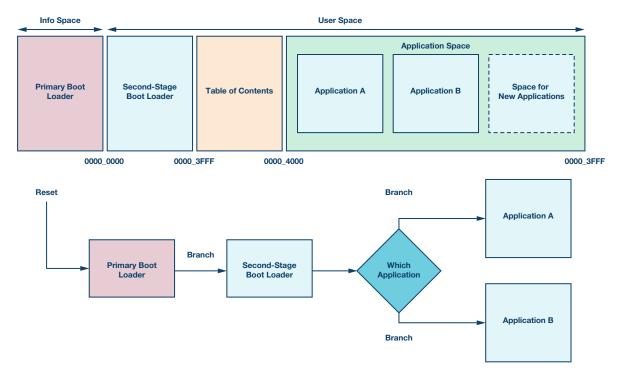

Many embedded systems are deployed in places that are difficult or impractical for a human operator to access. This is especially true for Internet of Things (IoT) applications, which are typically deployed in larger quantities and with limited battery life. Some examples would be embedded systems that monitor the health of a person or a machine. These challenges, coupled with the rapid software lifecycle, cause many systems to require support for over-the-air (OTA) updates. An OTA update replaces the software on the microcontroller or microprocessor of the embedded system with new software. While many people are very familiar with OTA updates on their mobile devices, the design and implementation on a resource constrained system leads to many different challenges. In this article, we will describe several different software designs for OTA updates and discuss their trade-offs. We will see how hardware features of two ultra low power microcontrollers can be leveraged in OTA update software.

# **Building Blocks**

#### **Server and Client**

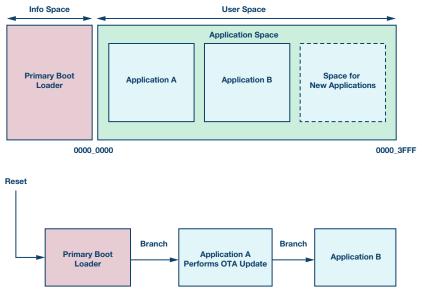

An OTA update replaces the current software on a device with new software, with the new software being downloaded wirelessly. In an embedded system, the device that runs this software is typically a microcontroller. A microcontroller is a small computing device with limited memory, speed, and power consumption. A microcontroller typically contains a microprocessor (core) as well as digital hardware blocks for specific operations (peripherals). Ultra low power microcontrollers that typically consume 30 µA/MHz to 40 µA/MHz in active mode are ideal for this type of application. Using specific hardware peripherals on these microcontrollers and placing them into low power modes is an important part of the OTA update software design. An example of an embedded system that might require OTA updates is shown in Figure 1. Here we see a microcontroller connected with a radio and sensor, which may be used in an IoT application that gathers data about the environment using the sensor and reports it periodically using the radio. This portion of the system is referred to as the edge node or client and is the target of the OTA update. The other portion of the system is referred to as the cloud or server and is the provider of the new software. The server and client communicate over a wireless connection using transceivers (radios).

Figure 1. Server/client architecture in an example embedded system.

# What Makes a Software Application?

Much of the OTA update process is the act of transferring the new software from the server to the client. The software is transferred as a sequence of bytes, after it has been converted into a binary format from the source format. The conversion process compiles the source code files (for example, c, cpp), links them together into an executable file (for example, exe, elf), and then the executable is converted into a portable binary file format (for example, *bin, hex*). At a high level, these file formats contain a sequence of bytes that belong at a specific address of memory in the microcontroller. Typically, we conceptualize the information being sent over a wireless link as data, such as a command to change the system's state or sensor data collected by the system. In the case of the OTA update, the data is the new software in binary format. In many cases, the binary file will be too large to send in a single transfer from the server to the client, meaning that the binary file will need to be placed into separate packets, in a process called packetizing. To visualize this process better, Figure 2 demonstrates how different versions of the software will produce different binary files, and thus different packets to be sent during the OTA update. In this simple example, each packet contains 8 bytes of data, with the first 4 bytes representing the address in the client's memory to store the next 4 bytes.

## **Major Challenges**

Based on this high level description of the OTA update process, three major challenges arise that the OTA update solution must address. The first challenge relates to memory. The software solution must organize the new software application into volatile or nonvolatile memory of the client device so that it can be executed when the update process completes. The solution must ensure that a previous version of the software is kept as a fallback application in case the new software has problems. Also, we must retain the state of the client device between resets and power cycles, such as the version of the software we are currently running, and where

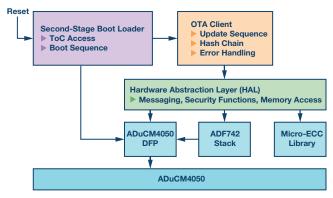

Figure 2. Binary conversion and packetization process of a software application.