# AnalogDialogue

# Volume 51, Number 2, 2017

(in)

#### Your Engineering Resource for Innovative Design

Visit analogdialogue.com

# In This Issue

# **3** Ray Stata Remembers

Some thoughts and insights from the man who cofounded the company and started *Analog Dialogue* on its five-decade run.

## 4 Flexible ECG Front-End IC Serves Ultralow Power IoT Edge Node Signal Processing Designs

This article breaks down the architecture of ADI's AD8233 ECG front-end IC and demonstrates how its unique mix of flexible analog signal processing capability, active low power (50  $\mu$ A), tiny 2 mm  $\times$  1.7 mm WLCSP package, shutdown pin, and more render the IC suitable for edge node applications in IoT, WSN, or any other low power design where battery life is a critical design requirement.

8 Analyzing and Solving Fixed Frequency Spur Issues in High Precision ADC Signal Chains

When designing precision signal chains, it can be hard to achieve a clear noise floor without spurs. Spurs can be introduced by components or they can be the result of external interference. This article will introduce approaches for determining the root causes of spur issues in high resolution, precision ADC applications and present solutions to solve them.

# **13** Presto! Multiply Your ADC's Virtual Channel Count with DDC Magic

I bought a dual-channel ADC and configured the digital downconverters. Now I am being told I have four converters! Is there a 2-for-1 data converter sale I wasn't aware of?

**14** Highlights from Five Decades of Innovation

We look back over the past 50 years at some of the key developments in the industry and some of our favorite articles.

**21** Precision SPI Switch Configuration Increases Channel Density

This article concentrates on reducing PCB space by using SPI controlled switches in test instrumentation applications.

This article focuses on the description of 1/f noise and how 1/f noise could get reduced in precision measurement applications.

# 28 Sometimes, a Signal Needs to Ride the Rails

I'm designing a signal conditioning block for a precision sensor analog front end. Should I use an op amp with rail-to-rail input?

# **Ray Stata Remembers**

We are proud to celebrate the 50<sup>th</sup> anniversary of *Analog Dialogue* with the first edition published in 1967—just two years after the company was founded. *Analog Dialogue*, now the longest published corporate technical journal, has survived budget cuts and shifting priorities over many decades, because it is highly valued by our customers. In the past three months alone, nearly 240,000 *Analog Dialogue* site visitors have clicked to download the journal and its articles 90,000 times.

# Written by Engineers for Engineers

Our customers are engineers. From the earliest days, our customers wanted more than innovative products, they wanted detailed technical information about how the products were designed, about the limitations of their performance, and about how to apply them. That was and continues to be the purpose of *Analog Dialogue*.

Analog Devices' business strategy was to continuously push the state of the art in product performance and capability. Customers looked to us to keep them informed about what was possible, not only through *Analog Dialogue*, but also through comprehensive data sheets, application notes, and tutorial handbooks. Consistently publishing high quality technical material takes a lot of hard work, resources, and discipline, but we do it because our technical community understands that this is an important part of the job and customers value this contribution as much as they value innovative products.

# Responding, Adapting, and Growing for Five Decades

Few companies survive—let alone thrive—for 50 years, because they fail to sense and respond to change in the environment. Analog Devices reinvented itself three times over its 50-year history, as it shifted from module to IC technology; from low volume industrial and military markets to high volume communication and consumer markets; and from components to system-level ICs. The company continually expanded its product base from operational amplifiers to converters, RF, DSP, sensors, and power management to offer more complete solutions for both analog and digital signal processing products and systems.

The tagline and content of *Analog Dialogue* tracked the evolution of the company. The tagline for the premiere edition in 1967 read "A Journal for the Exchange of Operational Amplifier Technology," to reflect the initial focus on op amps.

But in 1969, the tagline was changed to "A Journal for the Exchange of Analog Circuit Technology," as the company diversified into converter products and other analog function circuits.

In 1971, *Analog Dialogue* was now "A Forum for the Exchange of Circuit Technology: Analog and Digital, Monolithic, and Discrete." ADI had entered the IC business and developed mixed analog and digital process technology for monolithic IC converters.

In 1979, the tagline was updated to "A Forum for the Exchange of Circuits and Systems for Measurement and Control," as for a brief time ADI experimented with more complete computerized systems for measurement and control.

Ray Stata poses with an early edition of Analog Dialogue magazine.

In 1984, *Analog Dialogue* was described as "A Forum for the Exchange of Circuits, Systems, and Software for Real-World Signal Processing." The company had entered the DSP market, which broadened its vision to include both analog and digital signal processing and evolution toward more complete solutions, including software and algorithms.

Most recently, in 2016, the journal underwent a major redesign to reflect ADI's new Ahead of What's Possible brand and mission, and to become "Your Engineering Resource for Innovative Design." The way in which we support and collaborate with customers today involves consideration of not just hardware and signal processing capabilities, but also in how we combine these with deep domain expertise to deliver platforms, systems, and services. The new tagline recognizes *Analog Dialogue* as a tool for customers in their pursuit of innovation on many levels.

There are many factors that account for Analog Devices' long lived success, but no doubt our dedication to high quality technical communications as exemplified by *Analog Dialogue* has contributed much to our leadership, especially in the world of "analog devices." As our products grow ever more complex and specialized in their application, we continue to be committed to making your job easier through our technical publications such as *Analog Dialogue*.

Kay Stata

## **Our First Editor**

Ray Stata is Analog Devices Chairman of the Board. He cofounded the company in 1965. Shortly after starting the company, Ray established *Analog Dialogue* in 1967. Created as a resource for engineers, *Analog Dialogue* has provided product information, reflections on industry trends, and insights into both analog and digital circuit design. As *Analog Dialogue's* first editor, Ray set the vision and direction for the publication that continue to guide it more than half a century later.

# Flexible ECG Front-End IC Serves Ultralow Power IoT Edge Node Signal Processing Designs

By David Plourde

# Share on 💟 🚹 in

As system designers search for power efficient, signal conditioning components, they may find that there are very few ICs available under 100  $\mu$ A supply current and even fewer that include a small package variant. With battery life and board space becoming critical specifications for the growing number of wireless sensor networks (WSNs), the lack of available options can be frustrating. In a search for a low power edge node IoT component, an analog front-end IC such as a heart rate monitor for wearable products may not even show up, or it may be quickly dismissed as too application specific. However, at 50  $\mu$ A supply current and a tiny 2 mm  $\times$  1.7 mm WLCSP package, an ADI ECG front-end IC deserves a closer look. When designers dig deeper, they'll find that its flexible architecture is basically an instrumentation amplifier (IA) and a handful of op amps that can be configured to make some useful ultralow power signal processing circuits for more than just healthcare or fitness applications.

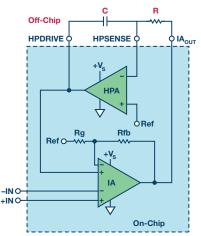

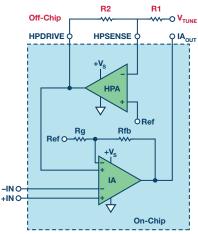

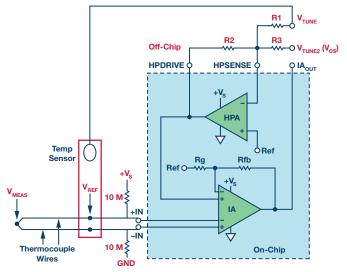

A simplified, single-lead electrocardiogram (ECG) front end is shown in Figure 1. It consists of an indirect current mode IA with a standalone transfer function of

$$IA_{OUT} = \left(1 + \frac{Rfb}{Rg}\right)(V_{IN}) + Ref$$

In the case of this front end, giving a fixed gain of 100. The reference of the IA is driven by the high-pass amplifier (HPA), which is configured as an integrator in feedback with its input tied to  $IA_{OUT}$  and crossover frequency set by an external capacitor and resistor. The HPA will force HPDRIVE to whatever voltage is needed to keep HPSENSE and therefore  $IA_{OUT}$  at the ref voltage. This circuit creates a first-order high-pass filter with cutoff frequency:

$$fc = \frac{100}{2\pi RC}$$

For diagnostic quality ECG, the cutoff frequency is typically set to 0.05 Hz, while 7 Hz may be suitable for fitness applications detecting heart rate only. The high-pass filter function solves the issue of rejecting the large dc half-cell potential (due to electrode/skin contact) and low frequency baseline wander associated with ECG measurements, while amplifying the higher frequency ECG signal (1 mV to 2 mV). The architecture enables a large gain since the rejection of the dc half-cell potential (up to 300 mV) occurs at the input of the IA. An added benefit is the rejection of the IA's offset and offset drift. Monitoring HPDRIVE with respect to ref will show an inverted version of the input offset being autocorrected.

Figure 1. Simplified single-lead ECG front end.

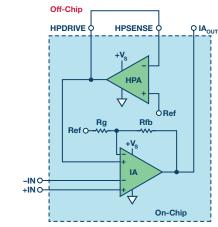

While the design originally targeted ECG applications, any application that requires amplification of small, low frequency signals could benefit from its low power and small size—an electromagnetic water flow sensor, for example. If dc measurements are required, then a simple modification to the circuit is all that is needed. Figure 2 shows a dc-coupled IA with a fixed gain of 100. This is done by removing the R and C from Figure 1 and shorting HPSENSE to HPDRIVE, making the HPA a unity-gain buffer. This will still force the IA reference to the reference voltage. In this case, IA offset voltages should be considered.

Figure 2. DC-coupled IA with fixed gain of 100.

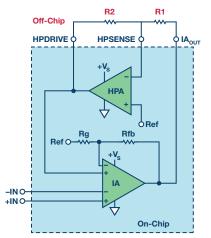

If a gain of 100 is too high or the bandwidth of 1 kHz is too low, the circuit could be modified, as shown in Figure 3. The HPA is now configured as an inverting amplifier with a gain of -R2/R1 and input fed back from  $IA_{out}$ . The new transfer function can be simplified as follows:

$$IA_{OUT} = \frac{V_{IN}}{\left(\frac{1}{100} + \frac{R2}{R1}\right)} + Ref$$

By configuring the HPA as an attenuator (R2 < R1), gains of less than 100 can be achieved. Due to the 300 mV differential input limit and stability of the circuit, it is not recommended to go below a gain of 10. Table 1 shows some gain configurations to consider.

# Table 1. DC-Coupled IA with Different Gain and Bandwidth Configurations

| R2    | R1   | Gain | Bandwidth |

|-------|------|------|-----------|

| Short | Open | 100  | 1.2 kHz   |

| 10 kΩ | 1 MΩ | 50   | 2.4 kHz   |

| 40 kΩ | 1 MΩ | 20   | 6.5 kHz   |

| 90 kΩ | 1 MΩ | 10   | 15.2 kHz  |

Figure 3. DC-coupled IA with adjustable gain and bandwidth.

If dc precision remains important, then leaving the IA in a gain of 100 and modifying the circuit per Figure 4 provides a means of compensating offsets of the IA and any attached sensors. The adjusted transfer function is shown below:

$$IA_{OUT} = 100 \left( V_{IN} - \left( \frac{R2}{R1} \right) V_{TUNE} \right) + Ref$$

$V_{\text{TUNE}}$  is the source voltage used to correct for offset voltages and could be provided by a filtered PWM signal from a microcontroller or driven directly from a low power DAC. The HPA remains configured as an inverting amplifier with gain of -R2/R1 and can be used to further adjust the range and resolution of the offset correction. Breaking down  $V_{\text{IN}}$  to components and plugging into above equation gives target transfer function:

$$V_{IN} = V_{SIGNAL} + V_{OS}$$

$$V_{OS} = \left(\frac{R2}{R1}\right) V_{TUNE}$$

$$IA_{OUT} = (100) V_{SIGNAL} + Ref$$

The total offset can be compensated by attaching a sensor without V<sub>SIGNAL</sub> applied. Just measure IA<sub>OUT</sub> with respect to reference and adjust (R2/R1) V<sub>TUNE</sub> until the voltage is close enough to zero.

Figure 4. DC-coupled IA with offset compensation.

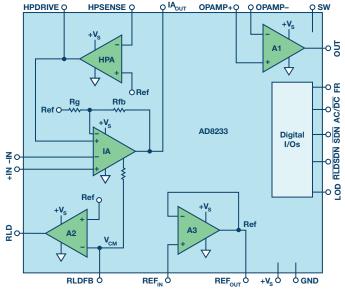

Before utilizing the above mentioned circuit configurations for low power IoT designs, the rest of the AD8233 ECG front-end solution should be understood. The circuit is detailed in Figure 5. The first op amp, A1, is fully uncommitted and typically used for additional gain and/or filtering after the IA stage. It could be similarly advantageous for other sensor applications. Amplifier A2 is typically used as the right leg drive in ECG solutions. A buffered version of the IA's input common mode appears at the inverting input of A2 where:

$$V_{CM} \sim \frac{+IN + -IN}{2}$$

The amplifier would normally be configured as an integrator with a capacitor placed between RLDFB and RLD, while RLD drives a third electrode, improving the overall system common-mode rejection ratio (CMRR). Unless a useful circuit can be built from this amplifier, it is better to power down the amplifier by tying RLDSDN digital input to ground, and leaving the RLD and RLDFB pins floating.

Figure 5. Complete ECG and low power signal conditioning front end.

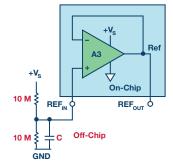

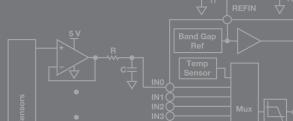

The third op amp, A3, is an integrated reference buffer that drives the reference voltage both on-chip and off-chip at REF<sub>out</sub>. Usually, REF<sub>IN</sub> is set to +Vs/2, where the single-supply +Vs can range from 1.7 V to 3.5 V. An easy low power solution is to tie two 10 MΩ resistors as a voltage divider from +Vs to GND, as shown in Figure 6. A capacitor is added between REFIN and GND to help with any noise pickup. Alternatively, REF<sub>IN</sub> could be driven from an ADC reference or used to level shift the IA output.

3 V

Figure 6. Low power reference.

The digital input FR enables the fast restore function, which is beneficial when using the ac-coupled circuit in Figure 1. It will take some time to charge the external capacitor during startup or in the event of a dc step at the input. When this happens, the IA will rail until the integrator has settled. The automatic fast restore detects this event and switches a smaller resistor in parallel with the external resistor for a fixed amount of time, greatly speeding up the settling time. The SW pin is used to quickly settle a second external high-pass filter if needed.

The AC/DC digital input determines the method for lead off detection used in ECG applications, but could also be utilized as a wire break detection for other sensors at the input. If configured correctly, the digital output LOD would indicate when one of the IA inputs becomes disconnected from the sensor.

In addition to its small size and low active power dissipation, the AD8233 incorporates a shutdown (SDN) pin that drops the total supply current to less than 1  $\mu$ A. This is convenient when taking infrequent sensor measurements, which greatly increases overall battery life. The wire break detection will remain functional even in shutdown mode.

Figure 7. Low power pressure sensor circuit.

Now that the complete AD8233 chip is better understood, let's take a look a couple of different sensor application ideas. Table 2 provides a getting started guide for building non-ECG circuits.

#### Table 2. AD8233 Starting Guide for Non-ECG Applications

| Pins                                                       | Action                                               |

|------------------------------------------------------------|------------------------------------------------------|

| $+V_{s}$ to GND                                            | Battery or regulated voltage (1.7 V to 3.5 V)        |

| REF <sub>ℕ</sub>                                           | Set to $+V_s/2$ —Figure 6                            |

| +IN, -IN                                                   | Connect sensor (nominal $V_{cm} = +V_S/2$ )          |

| ${\rm HPSENSE,  HPDRIVE,  IA_{\rm out}}$                   | Reference figures 1 to 4                             |

| RLD, RLDFB, SW, LOD                                        | Float                                                |

| FR, AC/ $\overline{\text{DC}}$ , $\overline{\text{RLSDN}}$ | Tie to GND                                           |

| SDN                                                        | Tie to +Vs (active), tie to GND (shutdown)           |

| OPAMP+, OPAMP-, OUT                                        | Flexible use (additional gain/filtering after IA)    |

| REF <sub>OUT</sub>                                         | External reference for A1 and ADC or microcontroller |

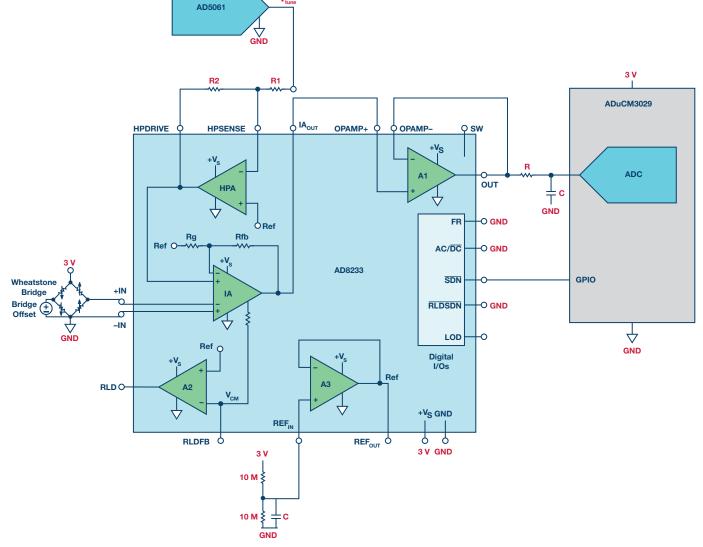

## IoT Edge Node Applications for the AD8233

A great example of where the fixed gain of 100 and offset correction in Figure 4 could be suitable is a pressure sensor application based on a Wheatstone bridge. The bridge naturally sets the input common mode to +Vs/2. Depending on measurement range and current required, the bridge could be driven by  $\text{REF}_{\text{out}}$  or the uncommitted op amp, such that the bridge supply current is disabled in shutdown. Figure 7 shows an example circuit. The AD5601 DAC is a good choice for correcting the bridge and IA offset, due to its low power (60  $\mu$ A at 3 V), shutdown pin, and small SC70 package. The op amp (A1) is left as a placeholder buffer with option to set additional gain or filtering of noise and 60 Hz. The output amplifier drives an on-board ADC of the ultralow power ARM® Cortex®-M3 (ADuCM3029) that also comes in a space saving WLCSP package. A GPIO from the ADuCM3029 can control the shutdown pin of the AD8233.

Another application that could take advantage of the circuit in Figure 4, is making a temperature measurement with a thermocouple. A K-type thermocouple is fairly linear over a wide temperature range with a Seebeck coefficient of about 41  $\mu$ V/°C at room temperature (25°C). Assuming the reference or cold junction was compensated for, the output of the IA would be a gained up version of the measurement junction ~4.1 mV/°C (for more accurate results, use a NIST lookup table). The output of a thermocouple is the difference between the measurement junction and the reference junction, so an equivalent reference junction drift must be added to cancel it.

To start the process, determine the expected reference junction temperature range by using the NIST table to determine the expected drift. For example:

0°C to 50°C:

$$\frac{2.023 \text{ mV} - 0 \text{ mV}}{50^{\circ}\text{C}} = 40.46 \ \mu\text{V}/^{\circ}\text{C}$$

25°C to 100°C:  $\frac{4.096 \text{ mV} - 1 \text{ mV}}{75^{\circ}\text{C}} = 41.28 \ \mu\text{V}/^{\circ}\text{C}$

By placing an accurate temperature sensor at the reference junction, the results can be fed back into  $V_{\text{TUNE}}$  and adjusted by -R2/R1 to get the correct drift. Note that the drift of temperature sensor should be negative or the IA

inputs swapped in order to get a positive drift at the IA output. To separate offset and drift correction, the circuit could be split into a summing node where the offset is fixed at  $V_{TUNE2}$  via -R2/R3. See the updated transfer function:

$$IA_{OUT} = 100 \left( V_{IN} - \left(\frac{R2}{R1}\right) V_{TUNE} - \left(\frac{R2}{R3}\right) V_{TUNE2} \right) + Ref$$

$$V_{IN} = V_{MEAS_{TC}} - V_{REF_{TC}} + V_{OS_{IA}}$$

The modified circuit is shown in Figure 8. Note that the input common mode is set to +V<sub>s</sub>/2 by 10 M $\Omega$  pull-up on +IN and 10 M $\Omega$  pull-down on -IN. This configuration would enable use of lead off detection of the AD8233 by pulling +IN to +Vs in the event of a wire break. This could be monitored at the LOD pin. The AD8233 also has an integrated RFI filter to assist with any high frequency pickup from the thermocouple. Placing additional resistance in series with the inputs can reduce the cutoff frequency.

Figure 8. Thermocouple circuit with reference junction compensation and wire break detection.

## Conclusion

Breaking down the AD8233 proved it to be more than an ECG front end. Its unique mix of active low power (50  $\mu$ A), tiny 2 mm  $\times$  1.7 mm WLCSP package, shutdown pin, and flexible architecture enables smaller, lighter designs with extended battery life. So the next time you are searching for components for your IoT, WSN, or any other low power design acronym, take a look at the AD8233 and see what circuits you can come up with. Your battery's life may depend on it.

## References

Castro, Gustavo and Scott Hunt. "How to Stay Out of Deep Water when Designing with Bridge Sensors." *Analog Dialogue*, Volume 48, 2014.

Duff, Matthew and Joseph Towey. "Two Ways to Measure Temperature Using Thermocouples Feature Simplicity, Accuracy, and Flexibility." *Analog Dialogue*, Volume 44, 2010.

ITS-90 Table for Type K Thermocouple.

David Plourde

# Analyzing and Solving Fixed Frequency Spur Issues in High Precision ADC Signal Chains

By Steven Xie

# Introduction

Current high resolution SAR ADCs and  $\Sigma$ - $\Delta$  ADCs provide high resolution and low noise, but system designers can have difficulty achieving the rated data sheet SNR performance. It can be even harder to achieve the optimum SFDR—that is, a clear noise floor without spurs in their system signal chain. Spurs can be introduced by improper circuitry surrounding the ADC or can be the result of external interference that occurs in a harsh operating environment.

This article will introduce approaches for determining the root causes of spur issues in high resolution, precision ADC applications and present solutions to solve them. These techniques and methods will help improve end-system EMC capability and reliability.

This article will cover five different application cases of specific design solutions for reducing spurs:

- Spur issues caused by dc-to-dc power supply radiation from the controller board.

- Spur issues caused by ac-to-dc adaptor noise through the external reference.

- Spur issues caused by analog input cable.

- > Spur issues caused by interference coupled on the analog input cable.

- Spur issues caused by room lighting.

#### Spurs and SFDR

As is known, spurious-free dynamic range (SFDR) represents the smallest power signal that can be distinguished from a large interfering signal. For current high resolution, precision ADCs, the SFDR is typically dominated by the dynamic range between a fundamental frequency and the second or third harmonic of the fundamental frequency of interest. However, there are spurs that can occur and limit the performance due to other aspects of the system.

The spurs can be categorized as input frequency dependent spurs and fixed frequency spurs. The input frequency dependent spurs are related to harmonic or nonlinearity performance. This article will focus on the fixed frequency spurs that are caused by power supplies, external references, digital interfacing, external interference, and more. Based on the application, these types of spurs can either be reduced or avoided entirely to help achieve maximum signal chain performance.

# Spur Issues Caused by On-Board DC-to-DC Power Supply Noise

Typically, LDOs are the suggested solution for generating low noise power supply rails for precision ADCs in precision measurement systems because of the dc-to-dc switching regulator's higher ripple noise. The fixed frequency or pulse-width modulated switching regulators provide switching ripple that is usually at a fixed frequency ranging from tens of kHz to a couple of MHz. The noise at the fixed frequency can feed into the ADC conversion codes via the ADC's PSRR mechanism. Some designers may use dc-to-dc switching regulators for precision ADC applications due to limited budget or board space. They have to limit the ripple noise or use ADCs with high PSRR to make sure that the ripple noise is below the ADC noise floor in order to achieve signal chain performance. Otherwise, there could be spurs at the switching frequency in the ADC's output spectrum, which may degrade signal chain dynamic range.

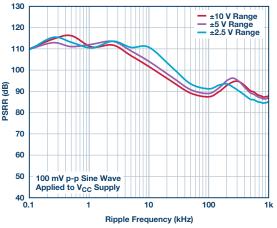

The AD7616 is a 16-bit DAS that supports dual-simultaneous sampling of 16 channels for power line monitoring. It has a very high PSRR and will do a good job of rejecting/attenuating the switching ripple. For example, a dc-to-dc switching power supply with 100 mV p-p ripple noise at 100 kHz is used for AD7616, a V<sub>cc</sub> 5 V with ±10 V input range.

The digital code noise caused by the ripple noise is:

$$\frac{100 \text{ mV } p-p}{10^{\frac{88 \text{ dB}}{20}}} = 3.98 \text{ } \mu\text{V} \text{ } or \text{ } 0.013 \text{ LSB}$$

This level of ripple showing up in the ADC output is extremely low for a 16-bit converter. High PSRR performance in ADCs makes it possible to use switching regulators in precision measurement systems.

Figure 1. AD7616 PSRR vs. ripple frequency.

# Spur Issues Caused by DC-to-DC Power Supply Radiation

Using a high PSRR ADC does not ensure that switching regulators will not cause problems in precision measurement systems. The ripple noise from switching regulators could feed into the ADC's digital codes through other ways.

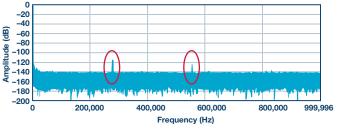

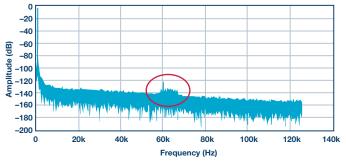

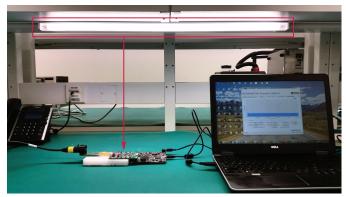

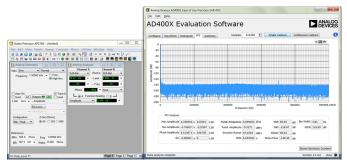

The AD4003 is a low noise, low power, high speed 18-bit, 2 MSPS precision successive approximation register (SAR) ADC. During EVAL-AD4003FMCZ evaluation board ac performance testing, a spur at a level of about -115 dBFS was found at around 277.5 kHz; the spur and its second harmonic appeared as shown in Figure 2.

Figure 2. Spur issue as seen on an EVAL-AD4003FMCZ eval board.

First, it was confirmed that the AD4003 power supplies were not causing the spurs.

Then, tests were performed to determine if the spurs were coming from the analog input.

- The spurs decreased when the differential analog input conditioning circuitry was removed.

- The spurs decreased when a narrow bandwidth RC filter (such as 1 kΩ, 10 nF) was inserted at the front end of AD4003 buffer amplifier, ADA4807-1.

These results show that the noise causing the spurs may pass through the conditioning circuitry and into the AD4003's analog inputs. Next, the sensor output was disconnected and the conditioning circuitry removed, leaving only the  $V_{\text{REP}}/2$  CM voltage input at the noninverting input of the ADA4807-1. However, the spurs remained and at a similar level.

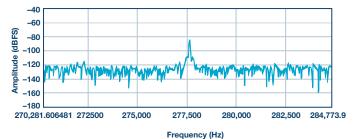

It was then suspected that the interference source was located around the EVAL-AD4003FMCZ signal chain. To prove this, a copper foil shield was placed at various locations on the EVAL-AD4003FMCZ board and the controller SDP-H1 board. It was determined that when the copper foil shield was placed over the dc-to-dc power supplies on the SDP-H1 board, as shown in Figure 3, the spurs would disappear. The spur frequency of 277.5 kHz matches the programmed switching frequency of the ADP2323 regulator. Figure 4 shows the 3.3 V VADJ\_FMC switching frequency power as captured by the EVAL-AD7616SDZ GUI FFT.

Figure 3. VADJ\_FMC inductor L5 covered by copper foil shield.

Figure 4. VADJ\_FMC 3.3 V switching ripple captured by EVAL-AD7616SDZ GUI FFT.

The conclusion was reached that the dc-to-dc switching frequency interference was being emitted by the 8.2  $\mu$ H inductor, L5. The interference was being injected into the signal chain at the input of buffer amplifier ADA4807-1, where it then went into the AD4003 ADC's analog input.

Possible solutions to this spur issue caused by dc-to-dc power converter are:

- Use a low-pass filter at the front end of the AD4003 ADC to attenuate the coupled dc-to-dc switching frequency interference to a level that meets the design target (that is, spur buried in noise floor) if the application bandwidth allows it.

- Use the new SDP-H1 board (BOM Rev 1.4), which uses a shielded inductor for L5. The radiated interference power is reduced, so the spurs captured in AD4003 ADC's spectrum are much lower.

- The VADJ\_FMC voltage level can be programmed by the EEPROM on the EVAL-AD4003FMCZ board. It was found that using a lower voltage level, such as 2.5 V for VADJ\_FMC, caused the spurs to disappear also.

## Spur Issues Caused by AC-to-DC Adaptor Noise Coupling Through the External Reference

ADCs quantize an analog signal into a digital code as referred to the ADC's dc reference voltage level. Therefore, the noise on the dc reference input will directly feed into the ADC's output digital codes.

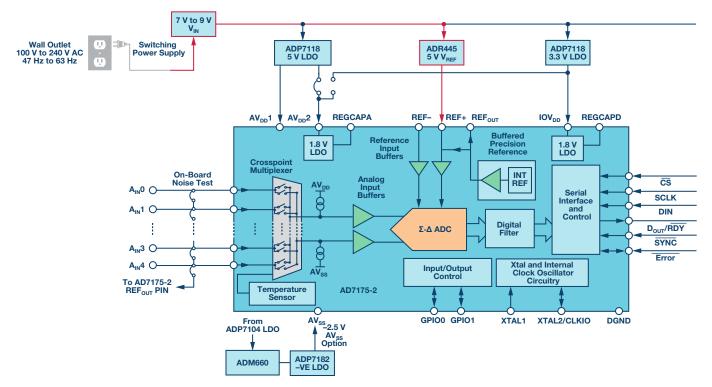

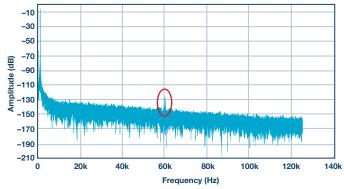

The AD7175-2 is a low noise, fast settling, multiplexed, 2-/4-channel (fully/pseudo differential)  $\Sigma$ - $\Delta$  ADC for low bandwidth inputs. During the EVAL-AD7175SDZ evaluation board's signal chain test, a cluster of spurs around 60 kHz was captured, as shown in Figure 5.

Figure 5. Spur issue as seen on EVAL-AD7175-2SDZ eval board.

Figure 6. Spur issue seen on EVAL-AD7175-2SDZ eval board.

The AD7175-2 ADC's power supplies and analog conditioning circuitries were evaluated and found to be good. However, as shown in Figure 6, the AD7175-2's 5 V reference input is generated by the ADR445 reference that is supplied by a 9 V dc from an ac-to-dc adaptor that is external to the evaluation board. Next, a bench 9 V dc power module was substituted for the adaptor. As a result, the cluster of spurs disappeared, leaving only a narrow spur at 60 kHz.

Figure 7. The cluster of spurs removed on EVAL-AD7175-2SDZ eval board.

The 9 V output ac-to-dc adaptor was tested with the EVAL-AD7616SDZ GUI FFT while supplying the EVAL-AD7175-2SDZ board with 320 mA of current output. The switching frequency power at the ADR445 reference's power pin is about -70 dBFS with an AD7616  $\pm$ 10 V input range, which means 6.325 mV p-p or -64 dBFS at an AD7175-2  $\pm$ 5 V input range.

Figure 8. 3.3 V VADJ\_FMC switching ripple captured by EVAL-AD7616SDZ GUI FFT.

$$20 \text{ V} \times 10^{\frac{-70 \text{ dB}}{20}} = 6.325 \text{ mV p-p}$$

$$20 \times \log \left(\frac{6.325 \text{ mV p-p}}{10 \text{ V}}\right) = -64 \text{ dBFS}$$

This power switching ripple noise feeds into the AD7175-2 ADC and shows up in the digital codes with some attenuation as stated below:

- ▶ The ADR445 reference's data sheet specifies a PSRR of 49 dB at 60 kHz.

- The ADR445 reference's output impedance is about 4.2 Ω at 60 kHz. It combines with the 4.8 µF reservoir caps, giving a further 18 dB of attention.

- Additionally, the AD7175-2 ADC's digital filter sinc5 + sinc1 adds about -3 dB of attenuation at 60 kHz, when ODR is 256 kSPS.

This calculated -134 dBFS level is very close to the level of the captured -130 dBFS cluster of spurs (not including the highest narrow spur) shown in Figure 5. This verifies that the cluster of spurs is caused by the ac-to-dc adaptor's switching ripple feeding through the external reference ADR445. The remaining narrow spur will be resolved in the subsequent section.

$$-64 \text{ dBFS} - 49 \text{ dB} - 18 \text{ dB} - 3 \text{ dB} = -134 \text{ dBFS}$$

# Spur Issues Caused by Interference Injected into the Signal Chain

In the hardware system, there is generally a long signal chain from the input sensor to the input of the precision converters. This signal chain includes connecting cables, connectors, routing wires, scaling and conditioning circuitries, ADC drivers, and more. There is a high potential for external interference to inject into the analog input signal chain and cause ADC spurs.

# Spur Issues Caused By Power Cable Interference into the Signal Chain

During the investigation of the remaining narrow spur on the EVAL-AD7175-2SDZ evaluation board's spectral output, it was noticed that there was a digital oscilloscope operating on the test bench. As shown in Figure 9, the scope's 220 V ac power supply cable (the black one) was overlapping the EVAL-AD7175-2SDZ EVB's analog input cable (the gray one). When the oscilloscope was turned off or its power cable was physically moved away from the analog input cable, the narrow spur at 60 kHz disappeared, as shown in Figure 10.

In the system cabinet, care should be taken in routing the cables from the sensor to the DAQ board. It is a good practice to keep the low level sensitive analog signals separated from the high current power lines.

Figure 9. Spur caused by oscilloscope power supply cable.

Figure 10. All spurs removed on EVAL-AD7175-2SDZ eval board.

#### Spur Issues Caused by Lamp Radiation

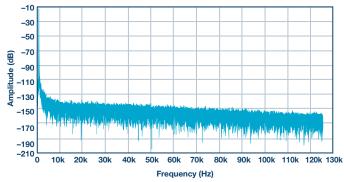

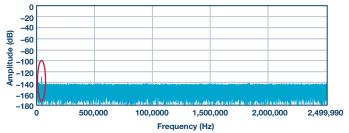

A spur appeared on the FFT spectrum while testing the EVAL-AD7960FMCZ evaluation board. As shown in Figure 11, the spur level was about -130 dB at 40 kHz.

The 40 kHz seemed to be unrelated to any of the signal frequencies that appear on the EVAL-AD7960FMCZ board and its controller board, SDP-H1. The next approach to finding the source of the spur was to clear the test bench in case there was something generating external interference. When the fluorescent light on the bench rack was turned off, the spur disappeared. Furthermore, it was found that as the EVAL-AD7960FMCZ board was put closer to the light, the 40 kHz spur would get higher. An additional RC filter (such as 1 k $\Omega$ , 10 nF) was placed at the front of the buffer amplifier ADA4899-1 and the spur decreased about 10 dB. That meant that the fluorescent light was radiating disturbance into the signal chain path at the front of the noninverting input of the buffer amplifier.

For systems that operate in a lighted environment, installing a shielding case over the front-end circuitry can help protect it from radiating interference and optimize signal chain performance.

Figure 12. Fluorescent lighting in proximity to the EVAL-AD7960FMCZ board.

## Spur Issues Caused by a Long Analog Input Cable

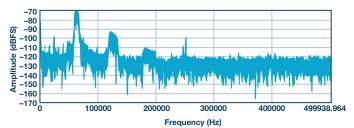

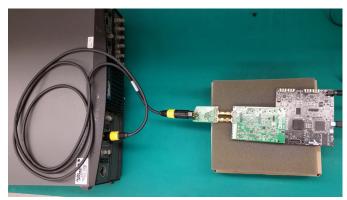

During the evaluation of the EVAL-AD4003FMCZ board, an AP SY2712 signal generator was used to drive a low noise and low THD sine wave to the analog inputs through an XLR microphone cable (about 2 meters long). In this setup, a spur was apparent at a level of about -125 dB at 700 kHz, as shown in Figure 13.

In the investigation of the spur, three ways to solve it were found:

- Bypass the two meter long XLR microphone cable and short the AP balanced output XLR male connector to the interposer XLR female connector.

- Set the signal source SY2712's output impedance from Z-Out = 40  $\Omega$  to Z-Out = 600  $\Omega$ .

- ► The spur becomes smaller when a narrow bandwidth RC filter (such as 1 k $\Omega$ , 10 nF) is inserted in the signal chain at the front end of the AD4003's buffer amplifier, the ADA4807-1.

Finally, the conclusion was reached that the mismatch in the signal source's output impedance, and the long XLR cable, caused the high frequency spur at 700 kHz.

Figure 13. Spur on EVAL-AD4003FMCZ eval board caused by XLR cable.

Figure 14. AP driving the EVAL-AD4003FMCZ board through a long XLR cable.

Steven Xie [steven.xie@analog.com] has worked as a product applications engineer with the China Design Center in ADI Beijing since March 2011. He provides technical support for SAR ADC products across China. Prior to that, he worked as a hardware designer in wireless communication base stations for four years. In 2007, Steven graduated from Beihang University with a master's degree in communications and information systems.

## Steven Xie

Also by this Author:

Practical Filter Design Challenges and Considerations for Precision ADCs

Volume 50, Number 2

#### Conclusion

This article discusses approaches for determining the root causes of spur issues in high resolution, precision ADC circuits, in system applications. It introduces specific design solutions to eliminate or reduce spurs in five different application cases. The article also discusses spur calculation methods to help estimate the spur power level as a design target for specific applications.

#### References

AD4003 Evaluation Kits. Analog Devices, Inc.

AD7175-2 Evaluation Kits. Analog Devices, Inc.

Beavers, Ian. "Understanding Spurious-Free Dynamic Range in Wideband GSPS ADCs." Analog Devices, Inc., 2014.

Walsh, Alan. "Powering a Precision SAR ADC Using a High Efficiency, Ultralow Power Switcher in Power Sensitive Applications." Analog Devices, Inc., 2016.

# Acknowledgements

Many thanks to ADI applications engineers Alan Walsh, Maithil Pachchigar, Nandin Xu, and Jeson Zhu, for their advice and support in the bench testing efforts required for this article.

# Rarely Asked Questions—140 Presto! Multiply Your ADC's Virtual Channel Count with DDC Magic

By Umesh Jayamohan

# Share on 💙 🚹 in

#### Question:

I bought a dual-channel ADC and configured the digital downconverters. Now I am being told I have four converters! Is there a 2-for-1 data converter sale I wasn't aware of?

#### Answer:

Ever since the advent of the very first monolithic, silicon-based analog-todigital converters (ADCs), the ADC has been keeping pace with the rapid advancements in silicon processing technology. Over the years, the silicon processing technology has advanced enough that it is now possible to economically design ADCs with a lot more powerful digital processing. Earlier generation ADC designs used very little digital circuitry outside of error correction and digital drivers. The new family of GSPS (gigasample per second) converters (also known as RF sampling ADCs) are enabled using sophisticated 65 nm CMOS technology and can pack a lot more digital processing power to enhance the ADC's performance.

With high sample rates (in the GSPS realm) also come a huge payload of data (bits per second). Take the AD9680, which is a dual 14-bit, 1.25 GSPS/1 GSPS/820 MSPS/500 MSPS, JESD204B analog-to-digital converter as an example. At the maximum sample rate of 1.25 GSPS, the ADC streams

14 bits  $\times$  2 converter channels  $\times$  1.25 Gbps = 35 Gbps

This amount of data will require an enormous number of LVDS routing lanes to extract the digital data. In order to facilitate the implementation of

(continued on Page 20)

this large throughput, the JESD204B standard was adopted. The JESD204B is a high speed, data transmission protocol that employs 8b/10b encoding and scrambling among other features aimed at providing adequate signal integrity. With the JESD204B standard, the total throughput now becomes

16 bits × 2 converter channels ×

$$\left(\frac{10}{8}\right)$$

× 1.25 Gbps = 50 Gbps

Using the JESD204B standard, the data throughput can be split across four high speed serial lanes at 12.5 Gpbs on each lane. Compare this to an LVDS interface where, at a line rate cap of about 1 Gbps/lane, the chip would need more than 28 pairs!

A quick inspection of the AD9680 data sheet reveals that there is quite the alphabet soup as far as setting up the link goes. Whereas earlier generation LVDS ADCs were easier to implement, the newer generation JESD204B ADCs are a bit more complicated. They become even more complicated when you take into account the internal digital downconverter (DDC) setups. However, the ADC setup is primarily determined by three letters in that alphabet soup:

- L = number of lanes per JESD204B link

- M = number of converters per JESD204B link

- F = number of octets per frame of data in the JESD204B link

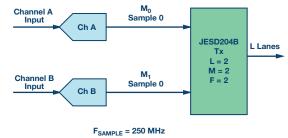

Take for example the AD9250, which is a dual 14-bit, 250 MSPS JESD204B analog-to-digital converter. Figure 1 shows the block diagram representation of the AD9250 in its default setup.

Figure 1. Setting up the AD9250.

In this setup the JESD204B link (JESD204B transmitter) is pretty straightforward, as there are no additional digital processing done in the AD9250. To the JESD204B link, Channel A becomes Converter 0 ( $M_0$ ), whereas Channel B becomes Converter 1 ( $M_1$ ), which means the value of M becomes 2. The total line rate for this setup is

# THE BEST OF ANALOG DIALOGUE

To read full articles, go to: analogdialogue.com

# 1967

# User's Guide to Applying and Measuring Operational Amplifier Specifications

September 1967: Vol 1 #3 **Ray Stata**

Ray Stata establishes the standards for operational amplifier specifications and establishes what will become the analog and mixed-signal industry's longest running engineering journal.

<u>Read full article</u>

# 1974 A 10-Bit Monolithic CMOS D/A Converter

March 1974: Vol 8 #1 Jim Cecil and Jerry Whitmore

A look at CMOS (complementary metal-oxide-semiconductor) becoming the leading technology for converters.

# Read full article

Differential Instrumentation Amplifier on a Single Chip Has High Input Impedance, Single-Resistor Gain Adjustment, Adjustable Output Bias, Output-Current Sensing

March 1972: Vol 6 #1 **Heinrich Krabbe**

We took a look at a new kind of amplifier, the AD520. It would set the industry standard for instrumentation amps with breakthrough FET inputs. *<u>Read full article</u>*

Low-Power Digital Signal-Processing ICs—Facilitate Filtering, FFT, Correlation, Averaging, and Much Else; 1983

8 × 8 and 16 × **16 Multipliers** and Multiplier/ Accumulators Dissipate <175 mW

March 1983: Vol 17 #1 John Oxaal

The introduction of DSP block building devices-the birth of the DSPs of today. Read full article

# 1987

2S81 Resolver-to-Computer **Interface Chip Provides** 12-Bit Outputs; Accurate, Simple, Inexpensive, It Operates at Speeds up to 260 rev/sec, Has **Velocity Output**

February 1987: Vol 21 #1 **Richard Parker**

Need to know the position of a rotating shaft? Since 1987, monolithic synchro-to-digital converters have been making that possible.

# Read full article

# Analog Dialogue

1990

**Electronic Adjustment** Made Easy with the TrimDAC<sup>™</sup>-Manipulate Voltages and Gains Digitally, **Replacing Pots.** Serial Drive Keeps **Pin-Count Low. Are Manual Trims Obsolete?**

July 1990: Vol 24 #3 Walter Heinzer and Joe Buxton

The beginning of the end for mechanical potentiometers?

# Read full article

# 1994

Floating-Point DSP Leads in Memory, Interconnectivity, Performance— For Single- and Multiple Processor Applications, SHARC Also Provides Upward Compatibility

July 1994: Vol 28 #3 **Bill Schweber**

Nearly 20 years after *Jaws*, the SHARC<sup>®</sup> (Super Harvard Architecture Computer) 32-bit floating-point DSP creates a sensation in digital signal processing.

Read full article

Single-Chip Direct Digital Synthesis vs. the Analog PLL—Complete-DDS Chips with DAC Have Excellent AC Performance, Low Power and Price, Small Size

July 1996: Vol 30 #3 Jim Surber and Leo McHugh

It's DDS (direct digital synthesis) in a bid to replace RC oscillators.

Read full article

ONFIGURATION

Othello: A New Direct-Conversion Radio Chip Set Eliminates IF Stages

November 1999: Vol 33 **Daniel E. Fague**

A look at the SoftCell™ multicarrier wireless

# 1999

communications transceiver chipset, the Othello<sup>®</sup> direct conversion radio chipset, and the TruPwr<sup>™</sup> RF IC power detector.

# The PDA 2001 Challenge—Met by the AD7873 Resistive-Touch-Screen Controller

August 2001: Vol 35 **Paul Kearney**

An introduction to Analog Devices' touch screen digitizer and the first small steps toward contactless gesture control.

Read full article

# 2006

Wideband A/D Converter Front-End Design Considerations: When to Use a Double Transformer Configuration

# July 2006: Vol 40 #3 **Rob Reeder** and **Ramya Ramachandran**

A pair of *Analog Dialogue* authors looks at the imbalance of a double transformer configuration and how it affects the ADC in high bandwidth applications.

<u>Read full article</u>

#

40 Video Kainer

2006 Digital Isolation Offers Compact, Low-Cost Solutions to Challenging Design Problems

ANALOG

December 2006: Vol 40 #4 **David Krakauer**

Isolation without optocouplers? We take a look at a breakthrough technology from Analog Devices. <u>Read full article</u>

# 2009 Accelerometers— Fantasy and Reality

June 2009: Vol 43 #2 Harvey Weinberg

What can be done with *i*MEMS<sup>®</sup> accelerometers? We look at reality, fantasy, and dream land.

Read full article

# 2013

Successive-Approximation ADCs: Ensuring a Valid First Conversion

December 2013: Vol 47 #4 **Steven Xie**

SAR ADCs with 18-bit resolution and 10 MSPS sample rates—not so long ago, it was pretty impressive. *Read full article*

The 20-Bit DAC Is the Easiest Part of a 1-ppm-Accurate Precision Voltage Source

April 2010: Vol 44 #2 **Maurice Egan**

20 bits, precision up to 1 ppm. Are we pushing precision to its end?

<u>Read full article</u>

2010

# 2014

# ADC Modeling Tools Speed Up Evaluation

November 2014: Vol 48 #4 **Umesh Jayamohan**

Low risk and high reward? There's a new suite of simulation tools for that. *Read full article*

2014 Wearable Electronic Devices Monitor Vital Signs, Activity Level, and More

# December 2014: Vol 48 #4 **Jan-Hein Broeders**

The devices we can't seem to live without are going from mobile to wearable.

# <u>Read full article</u>

# 2015

Four Quick Steps to Production: Using Model-Based Design for Software-Defined Radio (Part 1)

# **Analog Dialogue**

# 2017

# Improving Precision Data Acquisition Signal Chain Density Using SIP Technology

January 2017: Vol 51 #1 **Ryan Curran**

SIP (system in package) is now available for analog parts, and, yes, it provides some great advantages.

# Read full article

# To read full articles, go to: analogdialogue.com

September 2015: Vol 49 #3 Di Pu, Andrei Cozma, and Tom Hill

A look at closing the gap between a concept and working design.

Read full article

$$Line Rate = \frac{M \times N' \times \left(\frac{10}{8}\right) \times F_{OUT}}{L} = \frac{2 \times 16 \times 1.25 \times 250 M}{2} = 5 \text{ Gbps/lane}$$

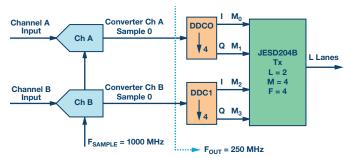

Compare this to the AD9680 sampling at 1 GSPS—but in this case, two digital downconverters are used in a complex (I/Q) setup. Figure 2 shows the AD9680 where the digital downconverters are used to decimate the data sampled at 1 GSPS by four. This results in an output sample rate ( $F_{OUT}$ ) of 250 MSPS.

Figure 2. Setting up the AD9860-1000 with two DDCs set to decimate by 4.

It is clear from Figure 2 that the AD9680 can effectively reduce the sample rate using the internal on-chip digital downconverters. Since each of the DDCs outputs a 16-bit stream, the actual (physical) converter bit streams are now decoupled from the "M" parameter of the JESD204B alphabet soup. Per the standard, M is the number of converters per link.

In the modified scenario, M now becomes a parameter called a virtual converter. Even though the AD9680 physically only has two ADC channels (A and B), with the DDCs in complex output mode enabled, there are now four different (16-bit) data streams to the JESD204B interface. To the JESD204B interface, this looks like there are now four (virtual) converters sending bit streams. Hence, the M = 4 or converter multiplying act. The output line rate in this case becomes

$$Line Rate = \frac{M \times N' \times \left(\frac{10}{8}\right) \times F_{OUT}}{L} = \frac{4 \times 16 \times 1.25 \times 250 M}{2} = 10 \text{ Gbps/lane}$$

The flexibility of the AD9680's JESD204B interface becomes apparent here, as there are now two options available depending on what the line rate acceptability of the receive logic (ASIC or FPGA). Table 1 shows the available options for the JESD204B interface in the AD9680 setup shown in Figure 2.

# Table 1. Configuration Options for the AD9680 ADC's JESD204B Output Interface

| # Virtual Converters M | # Lanes Per<br>Link L | # Octets Per<br>Frame F | Line Rate<br>(Gbps/Lane) |

|------------------------|-----------------------|-------------------------|--------------------------|

| ٨                      | 4                     | 2                       | 5                        |

| 4                      | 2                     | 4                       | 10                       |

For a dual-channel ADC like the AD9680 that has four DDCs, Table 2 shows the virtual converter mapping that is available for various configurations.

## Table 2. Configuration Options for the AD9680 ADC's JESD204B Output Interface

| - Uperaling . |                           | Virtual Converter Mapping |                    |                    |                    |                    |                    |                    |                    |                    |

|---------------|---------------------------|---------------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|

|               | Chip Q<br>Ignore          | 0                         |                    | 2                  | 3                  | 4                  | 5                  | 6                  | 7                  |                    |

| 1 to 2        | Full<br>Bandwidth<br>Mode | Real or<br>Complex        | ADC A<br>Samples   | ADC B<br>Samples   | Unused             | Unused             | Unused             | Unused             | Unused             | Unused             |

| 1             | One DDC<br>Mode           | Real (I Only)             | DDC 0 I<br>Samples | Unused             |

| 2             | One DDC<br>Mode           | Complex (I/Q)             | DDC 0 I<br>Samples | DDC 0 Q<br>Samples | Unused             | Unused             | Unused             | Unused             | Unused             | Unused             |

| 2             | Two DDC<br>Mode           | Real (I Only)             | DDC 0 I<br>Samples | DDC 1 I<br>Samples | Unused             | Unused             | Unused             | Unused             | Unused             | Unused             |

| 4             | Two DDC<br>Mode           | Complex (I/Q)             | DDC 0 I<br>Samples | DDC 0 Q<br>Samples | DDC 1 I<br>Samples | DDC 1 Q<br>Samples | Unused             | Unused             | Unused             | Unused             |

| 4             | Four DDC<br>Mode          | Real (I Only)             | DDC 0 I<br>Samples | DDC 1 I<br>Samples | DDC 2 I<br>Samples | DDC 3 I<br>Samples | Unused             | Unused             | Unused             | Unused             |

| 8             | Four DDC<br>Mode          | Complex (I/Q)             | DDC 0 I<br>Samples | DDC 0 Q<br>Samples | DDC 1 I<br>Samples | DDC 1 Q<br>Samples | DDC 2 I<br>Samples | DDC 2 Q<br>Samples | DDC 3 I<br>Samples | DDC 3 Q<br>Samples |

Umesh Jayamohan [umesh.jayamohan@analog.com] is an applications engineer with Analog Devices in the High Speed Converter Group (Greensboro, NC). He has been a part of Analog Devices since 2010. Umesh received his B.S.E.E. from the University of Kerala, India, in 1998, and his M.S.E.E. from Arizona State University in 2002.

Umesh Jayamohan

Also by this Author: Because Mr. Ohm Said So ... Volume 50, Number 4

# Precision SPI Switch Configuration Increases Channel Density

By Stephen Nugent

# Abstract

When designing a system that requires high channel density such as in test instrumentation, there is typically a necessity to include a large number of switches on the board. When using switches controlled by a parallel interface, a large percentage of board space is taken up by the logic lines necessary to control the switches, as well as the serial-to-parallel converters needed to generate the GPIO control signals. This article discusses the new generation of ADI SPI controlled switches that address this design challenge, their architecture, and the channel density increase they offer vs. parallel controlled switches. ADI's innovative copackaging process enables a new SPI-to-parallel converter die to be combined with existing high performance analog switch die. This allows space saving to be offered without compromise to the precision switch performance.

Maximizing channel count in test equipment is of the utmost importance, as this allows more devices to be tested in parallel, which, in turn, cuts testing time and cost for the end customer. Switches are a key element in allowing channel increases, as they enable the tester to share its resources to support multiple DUTs. But more parallel controlled switches means more control lines, resulting in increased board space consumed. This severely restricts the channel density that can be realized.

Using SPI controlled switches in this situation offers significant benefits in terms of solution size and channel count. The SPI switches can be placed in a daisy-chain formation that massively reduces the number of digital lines needed as compared to a traditional solution.

This article details the problems encountered when trying to maximize channel count, discusses the traditional method used to control a group of switches and the associated drawbacks, presents the solution offered by SPI controlled analog switches, and finally introduces the best-in-class performance, SPI controlled ADI precision switches.

# **Common Issues When Maximizing Channel Count**

When developing a module where the main aim is to maximize channel count, board space becomes a commodity. Switches are key to increasing channel count in a system but as the number of switches increase, board space is reduced not only by the switches themselves, but by the logic lines and associated devices needed to generate these logic lines. Ultimately the channel count that can be realized suffers because of the associated items needed to control the switch itself.

# **Traditional Parallel Switch Solution**

The most common solution to increasing channel density is to use switches that are controlled by parallel logic signals. This requires a large amount of GPIO signals that a standard microcontroller would not be able to supply. A solution to generating the GPIO signals is using serial-to-parallel converters. These devices output parallel signals and are configured by serial protocols such as I<sup>2</sup>C and SPI.

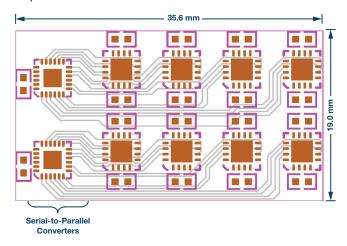

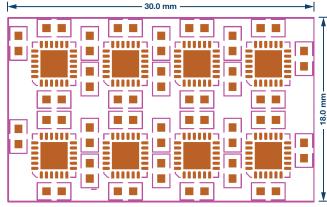

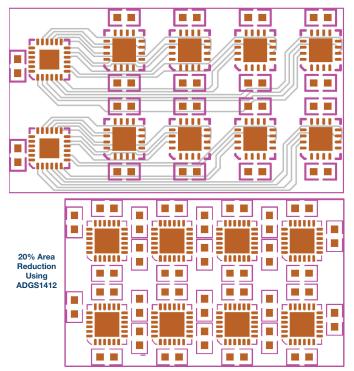

Figure 1 is a layout, showing eight ADG1412 quad, single-pole, singlethrow (SPST) switches in a  $4 \times 8$  cross point configuration on a 6-layer board. The switches are controlled by two serial-to-parallel converters with the serial lines coming from a controller board. Each converter supplies 16 GPIO lines each that are distributed between the eight switches. The layout shows the footprints of the devices, supply decoupling capacitors, and the digital control signals in gray. The size of  $4 \times 8$  matrix solution using the parallel controlled switches is 35.6 mm  $\times$  19 mm, which occupies an area of 676.4 mm.<sup>2</sup>

Figure 1. Parallel controlled switch 4 × 8 matrix layout.

As is evident from Figure 1, a large percentage of the solution area is taken up by the serial-to-parallel converters and the digital control lines, rather than the switches themselves. This inefficient use of board space is not ideal and will vastly reduce the number of switches in the module, which, in turn, has a detrimental effect on the channel count of the system.

# SPI Switch Solution

Figure 2 shows a  $4 \times 8$  cross point configuration with eight quad SPST switches on a 6-layer board. However, this time the switches are SPI controlled ADGS1412 devices. As before, the device footprints, supply decoupling capacitors, and SDO pull-up resistors are shown.

The solution shows the devices configured in a daisy-chain formation. All devices share the same chip select and serial clock digital lines from an SPI interface, while the first device in the chain receives the serial data. This data is then passed through all devices in the chain like a shift register. The size of this example solution is 30 mm  $\times$  18 mm, which is an area of 540 mm.<sup>2</sup>

The use of the SPI interface in a daisy-chain format vastly reduces the board space occupied by the serial-to-parallel converter and the digital lines. So much so that an overall board area reduction of 20% is realized with the same switch configuration. This enables a large increase in channel density. The system platform is also simplified. When the switch count increases on a board, the space area savings ramps up along with that—leading to >50% space saving on boards containing hundreds of switches.

This demonstrates the ability to fit more switches into a smaller area, which, in turn, would allow for the large channel count on a fixed area board compared to the traditional serial-to-parallel converter solution.

Figure 2. Daisy-chain switch, 4 × 8 matrix layout.

Figure 3. Area comparison of SPI switch and parallel switch solutions.

# **ADI SPI Switch Features**

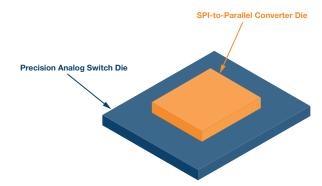

ADI's new SPI switch portfolio can be used to achieve increased channel density, as shown in the previous example. An innovative stacked dualdie solution (Figure 4) enables ADI's current industry-leading precision switches to be configured with an industry standard, SPI mode 0 interface. This means that the space saving can be achieved without having an adverse effect on the performance of the system. The following is a summary of the key functionality of the new ADI SPI switch.

Figure 4. ADI's innovative stacked dual-die solution.

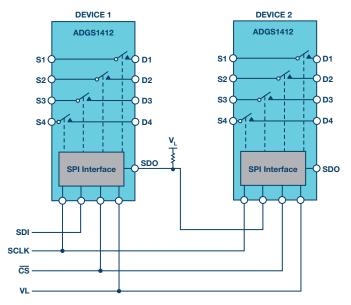

# Daisy-Chain Mode

As outlined before, the ADI SPI switches are able to operate in daisy-chain mode. The connection of ADGS1412 devices in a daisy-chain is illustrated in Figure 5. All devices share  $\overline{CS}$  and SCLK digital lines, whereas the SDO of a device forms a connection to the SDI of the next device. One single 16-bit SPI frame is used to command all the devices in the chain to enter daisy-chain mode. In daisy-chain mode, SDO is an 8-cycle delayed version of SDI, so the desired switch configuration can be passed from one device to the next device in the chain.

Figure 5. Two switches in a daisy-chain configuration.

## **Error Detection Function**

When the device is in address mode or burst mode, protocol and communication errors on the SPI interface are detectable. There are three error detection methods, which are incorrect SCLK count, invalid read and write address, and CRC error detection up to 3 bits. These error detection function ensure a robust digital interface even in the harshest of environments.

# **ADI SPI Switch Family**

The ADGS1412 is the first release in a family of SPI switches that are being developed by Analog Devices. Thanks to the innovative dual-die solution developed by ADI, the ADGS1412, has the same best-in-class, low  $R_{\rm ON}$  performance as the parallel controlled ADG1412 while offering the benefits that a serial interface brings.

The portfolio will be built on ADI's high performance switches, offering SPI controlled versions of the industry-leading switches already available. Table 1 shows the current and planned products in the new ADI SPI switch family. The part number represents which analog switch die is copackaged with the SPI-to-parallel converter with an additional S to show that this is the SPI controlled version. These products will be released throughout 2017.

# Table 1. Planned Device-Optimized Products in the New SDI SPI

| Part Number | Configuration          | Device Optimization                                        |

|-------------|------------------------|------------------------------------------------------------|

| ADGS1412    | $4 \times \text{SPST}$ | $\rm R_{_{ON}}$ optimized                                  |

| ADGS5412    | $4 \times \text{SPST}$ | Low R <sub>on</sub> , latch-up<br>immune                   |

| ADGS1212    | $4 \times \text{SPST}$ | Charge injection and $C_{\mbox{\scriptsize ON}}$ optimized |

| ADGS1612    | $4 \times \text{SPST}$ | $R_{\mbox{\scriptsize on}}$ optimized, medium voltage      |

| ADGS5414    | $8 \times \text{SPST}$ | Low R <sub>on</sub> , latch-up<br>immune                   |

Stephen Nugent [stephen.nugent@analog.com] is an applications engineer in the Linear and Precision Technology Group of Analog Devices. He graduated from Queen's University Belfast in 2014 with a master's degree in electrical and electronic engineering. Stephen joined the Linear and Precision Technology Group in July 2014 supporting the analog switch and multiplexer product portfolio. He also previously worked in the Precision Converter Group within ADI.

## Summary

Using SPI controlled switches in a high channel density application has many advantages over the use of parallel controlled switches. It enables the reduction of board space used per switch, which, in turn, increases the density of switches that can be realized. This is due to the reduction of digital control lines needed and the removal of the devices required to provide these control lines.

Analog Devices has a new innovative precision SPI switch solution that enables the increase of channel density. This is facilitated by the daisychain mode that is available on these devices. The same industry-leading switch performance seen in Analog Devices' current switch offerings is maintained due to the dual-die solution used. The ADGS1412 is the first release in a family of new SPI controlled switches with a complete portfolio coming in 2017 and 2018.

#### Stephen Nugent

# Understanding and Eliminating 1/f Noise

By Robert Kiely

# Share on 💟 🚹 💼

## Introduction

This article explains what 1/f noise is and how to reduce or eliminate it in precision measurement applications. 1/f noise cannot be filtered out and can be a limit to achieving the best performance in precision measurement applications.

## What Is 1/f Noise?

1/f noise is low frequency noise for which the noise power is inversely proportional to the frequency. 1/f noise has been observed not only in electronics but also in music, biology, and even economics.<sup>1</sup> The sources of 1/f noise are still widely debated and much research is still being done in this area.<sup>2</sup>

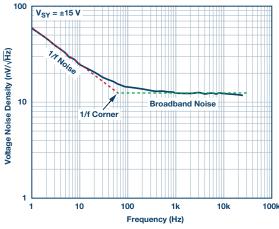

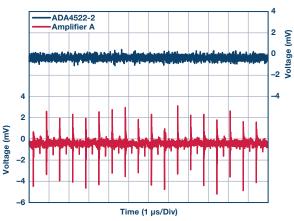

Looking at the voltage noise spectral density of the ADA4622-2 op amp shown in Figure 1, we can see that there are two distinct regions visible in the graph. On the left of Figure 1 we can see the 1/f noise region and on the right of Figure 1 we can see the broadband noise region. The crossover point between the 1/f noise and the broadband noise is called the 1/f corner.

Figure 1. ADA4622-2 voltage noise spectral density.

#### How Do We Measure and Specify 1/f Noise?

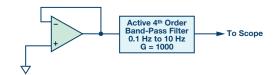

After comparing the noise density graphs of a number of op amps, it becomes apparent that the 1/f corner can vary for each product. To easily compare components, we need to use the same bandwidth when measuring the noise of each component. For low frequency voltage noise, the standard specification is 0.1 Hz to 10 Hz peak-to-peak noise. For op amps, the 0.1 Hz to 10 Hz noise can be measured using the circuit shown in Figure 2.

Figure 2. Low frequency noise measurement.

The op amp is put in a unity-gain feedback configuration with the noninverting input grounded. The op amp is powered from a split supply to allow for the input and the output to be at the ground.

The active filter block limits the bandwidth of the noise that is measured while simultaneously providing a gain of 1000 to the noise from the op amp. This ensures that the noise from the device under test is the dominant source of noise. The offset of the op amp is not important, as the input to the filter is ac-coupled.

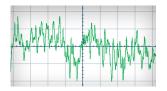

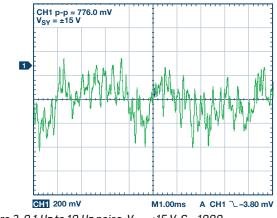

The output of the filter is connected to an oscilloscope and the peak-topeak voltage is measured for 10 seconds to ensure we capture the full 0.1 Hz to 10 Hz bandwidth (1/10 seconds = 0.1 Hz). The results shown on the scope are then divided by the gain of 1000 to calculate the 0.1 Hz to 10 Hz noise. Figure 3 shows the 0.1 Hz to 10 Hz noise for the ADA4622-2. The ADA4622-2 has a very low, 0.1 Hz to 10 Hz noise of just 0.75  $\mu$ V p-p typical.

Figure 3. 0.1 Hz to 10 Hz noise,  $V_{sy} = \pm 15 V$ , G = 1000.

# What Impact Does 1/f Noise Have in My Circuit?

The total noise in a system is the combined 1/f noise and broadband noise from each component in the system. Passive components have 1/f noise and current noise also has a 1/f noise component. However, for low resistances the 1/f noise and current noise are usually too small to be considered. This article will focus on voltage noise only.

To calculate the total system noise we calculate the 1/f noise and the broadband noise, and then combine them. If we use the 0.1 Hz to 10 Hz noise specification to calculate the 1/f noise, then we are assuming that the 1/f corner is below 10 Hz. If the 1/f corner is above 10 Hz, then we can estimate the 1/f noise using the following formula<sup>3</sup>:

$$\frac{1}{f} Noise_{rms} = en_{IHz} \left( \sqrt{\ln\left(\frac{f_h}{f_l}\right)} \right)$$

where:

$e_{n1Hz}$  is the noise density at 1 Hz,

f<sub>h</sub> is the 1/f noise corner frequency,

f<sub>1</sub> is 1/aperture time.

For example, if we want to estimate the 1/f noise for the ADA4622-2, then  $f_{\rm h}$  is about 60 Hz. We set  $f_{\rm l}$  to be equal to 1/aperture time. Aperture time is the total measurement time. If we set the aperture time or measurement time to be 10 seconds, then  $f_{\rm l}$  is 0.1 Hz. The noise density at 1 Hz,  $e_{n1Hz}$ , is approximately 55 nV/Hz. This gives us a result of 139 nV<sub>rms</sub> between 0.1 Hz and 60 Hz. To convert this to peak-to-peak we should multiply by 6.6, which will give us approximately 0.92  $\mu$ V p-p.<sup>4</sup> This is about 23% higher than the 0.1 Hz to 10 Hz specification.

The broadband noise can be calculated using the following formula:

$$Noise_{rms} = e_n \left( \sqrt{NEBW} \right)$$

where:

$e_n$  is the noise density at 1 kHz,

NEBW is the noise equivalent bandwidth.

The noise equivalent bandwidth takes into account the additional noise beyond the filter cutoff frequency due to the gradual roll-off of the filter. The noise equivalent bandwidth is dependent on the number of poles in the filter and the filter type. For a simple one pole, low-pass Butterworth filter, the NEBW is  $1.57 \times \text{filter cutoff}$ .

The wideband rms noise for the ADA4622-2 is just 12 nv $\sqrt{\text{Hz}}$  at 1 kHz. Using a simple RC filter on the output with a cutoff frequency of 1 kHz, the wideband rms noise is approximately 475.5 nV<sub>rms</sub> and can be calculated as follows:

WB Noise<sub>rms</sub> = 12 nV (

$$\sqrt{1 \text{ kHz} \times 1.57}$$

)

Note that a simple low-pass RC filter has the same transfer function as a single-pole, low-pass Butterworth filter.

To get the total noise we must add the 1/f noise and the broadband noise together. To do this we can use the root sum square method as the noise sources are uncorrelated.

$$Total Noise_{rms} = \sqrt{\left(\frac{1}{f}Noise_{rms}\right)^2 + \left(WB Noise_{rms}\right)^2}$$

Using this equation we can calculate the ADA4622-2 total rms noise with a simple 1 kHz, low-pass RC filter on the output to be 495.4 nV<sub>rms</sub>. This is just over 4% higher noise than the broadband noise alone. It's clear from this example that 1/f noise affects systems that measure from dc up to very low bandwidth only. Once you go beyond the 1/f corner by about a decade or more, the contribution of the 1/f noise to the total noise becomes almost too small to worry about.

Since noise adds together as a root sum square, we can decide to ignore the smaller noise source if it is below about  $^{1/_{5}\text{th}}$  of the larger noise source, since below a ratio of  $^{1/_{5}\text{th}}$  the noise contribution is about a 1% increase in the total noise.<sup>5</sup>

#### How Do We Remove or Mitigate 1/f Noise?

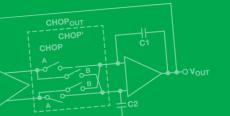

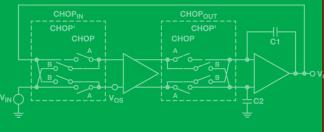

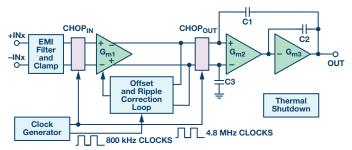

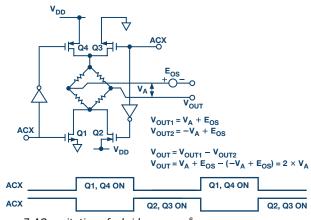

Chopper stabilization, or chopping, is a technique to reduce amplifier offset voltage. However, since 1/f noise is near dc low frequency noise, it is also effectively reduced by this technique. Chopper stabilization works by alternating or chopping the input signals at the input stage and then chopping the signals again at the output stage. This is the equivalent to modulation using a square wave.

Figure 4. ADA4522 architecture block diagram.

Referring to the ADA4522 architecture block diagram shown in Figure 4, the input signal is modulated to the chopping frequency at the CHOP<sub>IN</sub> stage. At the CHOP<sub>OUT</sub> stage, the input signal is synchronously demodulated back to its original frequency and simultaneously the offset and 1/f noise of the amplifier input stage are modulated to the chopping frequency. In addition to reducing the initial offset voltage, the change in offset vs. common-mode voltage is reduced, which results in very good dc linearity and a high common-mode rejection ratio (CMRR). Chopping also reduces the offset voltage drift vs. temperature. For this reason, amplifiers that use chopping are often referred to as zero-drift amplifiers. One key thing to note is that zero-drift amplifiers only remove the 1/f noise of the amplifier. Any 1/f noise from other sources, such as the sensor, will pass through unaffected.

The trade-off for using chopping is that it introduces switching artifacts into the output and increases the input bias current. Glitches and ripple are visible on the output of the amplifier when viewed on an oscilloscope and noise spikes are visible in the noise spectral density when viewed using a spectrum analyzer. The newest zero-drift amplifiers from Analog Devices—such as the ADA4522 55 V zero-drift amplifier family—use a patented offset and ripple correction loop circuit to minimize switching artifacts.<sup>6</sup>

Figure 5. Output voltage noise in the time domain.<sup>6</sup>

Chopping can also be applied to instrumentation amplifiers and ADCs. Products such as the AD8237 true rail-to-rail, zero-drift instrumentation amplifier, the new AD7124-4 low noise and low power, 24-bit  $\Sigma$ - $\Delta$  ADC, and the recently released AD7177-2 ultralow noise, 32-bit  $\Sigma$ - $\Delta$  ADC, use chopping to eliminate 1/f noise and minimize drift vs. temperature.

One disadvantage to using square wave modulation is that square waves contain many harmonics. Noise at each harmonic will be demodulated back to dc. If sine wave modulation is used instead, then this approach is much less susceptible to noise and can recover very small signals in the presence of large noise or interference. This is the approach used by lock-in amplifiers.<sup>7</sup>

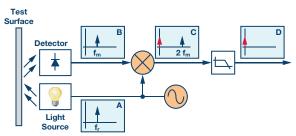

Figure 6. Measuring surface contamination with a lock-in amplifier.<sup>7</sup>

In the example shown in Figure 6, the sensor output is modulated by using a sine wave to control a light source. A photodetector circuit is used to detect the signal. Once the signal passes through the signal conditioning stage it can be demodulated. The same sine wave is used to modulate and demodulate the signal. The demodulation returns the sensor output to dc, but also shifts the 1/f noise of the signal conditioning stage to the modulation frequency. The demodulation can be done in either the analog or digital domain after ADC conversion. A very narrow low-pass filter—for example, 0.01 Hz—is used to reject the noise above dc and we are left with only the original sensor output with extremely low noise. This relies on the sensor output being at exactly dc, so the precision and fidelity of the sine wave is important. This approach eliminates the 1/f noise of the sensor.

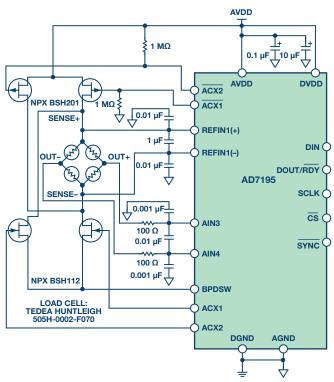

If a sensor requires an excitation signal, then it is possible to eliminate the 1/f noise from the sensor using ac excitation. AC excitation works by alternating the sensor excitation source to produce a square wave output from the sensor and then subtracting the output from each phase of the excitation. This approach not only allows us to eliminate the 1/f noise of the sensor, but also eliminates offset drift in the sensor and eliminates unwanted parasitic thermocouple effects.<sup>8</sup>

Figure 7. AC excitation of a bridge sensor.<sup>8</sup>

AC excitation can be done using discrete switches and controlling them with a microcontroller. The AD7195 low noise, low drift, 24-bit  $\Sigma$ - $\Delta$  ADC with internal PGA included drivers to implement ac excitation of the sensor. The ADC manages the ac excitation transparently by synchronizing the sensor excitation with the ADC conversions, making ac excitation easier to use.

Figure 8.CN-0155—Precision weigh scale design using a 24-bit  $\Sigma$ -  $\Delta$  ADC with internal PGA and ac excitation.

## Implementation

When using zero-drift amplifiers and zero-drift ADCs, it is very important to be aware of the chopping frequency of each component and the potential for intermodulation distortion (IMD) to occur. When two signals are combined, the resulting waveform will contain the original two signals, as well as the sum and difference of these two signals. For example, if we consider a simple circuit using the ADA4522-2 zero-drift amplifier and the AD7177-2  $\Sigma$ - $\Delta$  ADC, the chopping frequencies of each part will mix and create sum and difference signals. The ADA4522-2 has a switching frequency of 800 kHz, while the AD7177-2 has a switching frequency of 250 kHz. The mixing of these two switching frequencies will cause additional switching artifacts at 550 kHz and 1050 kHz. In this case, the AD7177-2 maximum corner frequency of the digital filter, 2.6 kHz, is much lower than the lowest artifact and will remove all of these IMD artifacts. However, if two identical zero-drift amplifiers are used in series, the IMD created will be the difference in the internal clock frequency of the parts. This difference could be small, and therefore, the IMD would appear at much closer to dc and be more likely to fall inside the bandwidth of interest.

In any case it is important to consider IMD when designing a system that uses zero-drift or chopped parts. It should be noted that most zero-drift amplifiers have much lower switching frequencies than the ADA4522-2. In fact, the high switching frequency is a key benefit to using the ADA4522 family when designing precision signal chains.

# Conclusion

1/f noise can limit performance in any precision dc signal chain. However, it can be removed by using techniques such as chopping and ac excitation. There are some trade-offs to using these techniques, but modern amplifiers and  $\Sigma$ - $\Delta$  converters have addressed these issues, making zero-drift products easier to use across a broader range of end applications.

## References

- <sup>1.</sup> W. H. Press. "Flicker Noises in Astronomy and Elsewhere." *Comments in Astrophysics*, 1978.

- <sup>2</sup> F.N. Hooge. "1/f Noise Sources." *IEEE Transactions on Electron Devices* Vol. 41, 11., 1994.

- <sup>3</sup> MT-048. "Op Amp Noise Relationships: 1/f Noise, RMS Noise and Equivalent Noise Bandwidth." Analog Devices, Inc., 2009.

- <sup>4.</sup> Walt Jung. *Op Amp Applications Handbook*. Newnes, 2005.

- <sup>5.</sup> MT-047. "Op Amp Noise." Analog Devices, Inc., 2009.

- <sup>6.</sup> Kusuda Wong. "Zero-Drift Amplifiers: Now Easy to Use in High Precision Circuits." *Analog Dialogue* Vol. 49, 2015.

- <sup>7.</sup> Luis Orozco. "Synchronous Detectors Facilitate Precision Low-Level Measurements." *Analog Dialogue* Vol. 48, 2014.

- <sup>8.</sup> Albert O'Grady. "Transducer/Sensor Excitation and Measurement Techniques." *Analog Dialogue* Vol. 34, 2000.

## **Acknowledgements**

The author would like to thank Scott Hunt and Gustavo Castro for their previous work on sources of noise in amplifiers.

Robert Kiely [robert.kiely@analog.com] is a senior applications engineer in the Linear and Precision Technology Group in San Jose, CA. He joined Analog Devices in 2010. Rob's focus is in precision signal chains and products including  $\Sigma$ - $\Delta$  ADCs, precision amplifiers, and voltage references. Rob received his B.S.E.E. and M.E. in VLSI systems from the University of Limerick, Ireland.

# Rarely Asked Questions—Issue 141 Sometimes, a Signal Needs to Ride the Rails

By Daniel Burton

# Share on 💟 🚹 🗓

## Question:

I'm designing a signal conditioning block for a precision sensor analog front end. Should I use an op amp with rail-to-rail input?

#### Answer:

Possibly—it depends on if the output signal from the sensor forces the op amp to a voltage near the supply rails. For example, if we were to monitor a load current of 0 mA to 500 mA through a precision 10  $\Omega$  shunt resistor, the maximum output would be 5 V. If the amplifier supply voltage was 5 V, you would need to choose an amplifier with a rail-to-rail input voltage range.

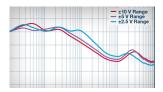

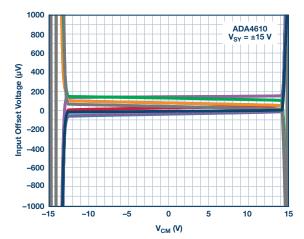

The classic input stage of many op amps is a transistor differential pair. In order for the op amp to amplify the common-mode voltage ( $V_{CM}$ ) signal at the input, it must have sufficient voltage headroom between the  $V_{CM}$  and the supply voltages. If  $V_{CM}$  gets close enough to either supply rail so that the input pair runs out of headroom, the input offset voltage, as well as other key parameters, will be degraded, resulting in a loss of accuracy, as seen in Figure 1. It is these headroom requirements that define the op amp's specified input voltage range (IVR). Some of the industry's highest precision amplifiers, like the ADA4610, have this classic input structure. As long as the input voltage stays away from the rails, it has excellent precision.

Figure 1. ADA4610 Typical input offset voltage vs. common-mode voltage.