# Analog Dialogue

# 本期介绍

- 2 编者寄语,新产品简介

- 3 在光电流应用中补偿电流反馈放大器

- 7 在多通道应用中使用放大器禁用功能代替多路复用器

- 9 多路复用三线式RTD数据采集系统的误差最小化

- 11 系统演示平台简化从评估到原型制作的过渡

- 13 缩短积分时间可以提高航位推算导航系统的精度

- 15 如何设计并调试锁相环(PLL)电路

www.analog.com/zh/analogdialogue

### 本期介绍

### 在光电流应用中补偿电流反馈放大器

电流反馈放大器(CFA)一般不用作跨阻放大器(TIA),因为它们具有相对较高的反相输入电流和电流噪声。然而,CFA易于使用,并且在要求高增益、低功耗、低噪声、宽带宽和高压摆率的应用中,其性能超过电压反馈放大器。本文讨论如何正确补偿CFA。(第3页)

### 在多通道应用中使用放大器禁用功能代替多路复用器

多路复用器将来自多路输入的其中一路信号路由至公共输出。很多应用会在信号进入多路复用器之前,使用放大器对其进行调理。这种情况下,带禁用功能的放大器可用来选择通道,因此无需使用多路复用器,同时还能降低成本、减少PCB面积与失真。本文描述了使用带有禁用功能的运算放大器选择通道时面临的挑战。(第7页)

### 多路复用三线式RTD数据采集系统的误差最小化

在可编程逻辑控制器或分布式控制系统中,一个数据采集模块可用来监控大量远程电阻式温度检测器(RTD)的温度。当每个RTD都有自己的激励电路和ADC时,可实现最佳精度,但模块体积庞大、成本高昂且功耗巨大。多路复用模块具有体积较小、成本和功耗较低的特性。(第9页)

### 系统演示平台简化从评估到原型制作的过渡

为了简化新设计的元器件选择,ADI提供评估板和应用软件,但节省时间和提升成功率的最好方法是在搭建电路板前准备好代码和接口。系统演示平台设计允许进行这类原型制作,为开启系统开发过程提供前所未有的便捷性。(第11页)

### 缩短积分时间可以提高航位推算导航系统的精度

汽车航位推算导航系统采用陀螺仪来推算车辆的瞬时航向。此信息结合行驶距离信息,即使在卫星信号受阻的情况下,导航系统也能确定车辆的正确位置。如果卫星信号长时间丢失,那么累积角度误差将变得非常大。本文提出一种简单的方法来最大程度地解决此问题。(第13页)

### 如何设计并调试锁相环(PLL)电路

设计并调试锁相环(PLL)电路可能会很复杂,除非工程师深入了解 PLL理论以及逻辑开发过程。若在设计阶段谨慎仔细,便可避免很 多问题。本文介绍PLL设计的简易方法,并提供有效、符合逻辑的 方法调试PLL问题。(第15页)

Scott Wayne [scott.wayne@analog.com]

### 产品目录: 第47卷, 第3期

所有ADI产品数据手册都可在www.analog.com/zh网站查到,只需在搜索框中输入产品型号即可。

### 7月

| . 74                                        |                    |

|---------------------------------------------|--------------------|

| ±0.5 g/±1 g/±2 g/±4 g三轴MEMS数字 <b>加速度计</b> . | ADXL313            |

| 集成四个降压调节器、一个LDO的5通道PMU                      | ADP5050/ADP5052    |

| 13 GHz小数N分频频率 <b>合成器</b>                    | ADF4159            |

| 8月                                          |                    |

| Σ-Δ型4通道 <b>ADC</b>                          | ADAU1978           |

| 高稳定性隔离误差 <b>放大器</b>                         | ADuM4190           |

| 1100 MHz可编程滤波器的可变增益 <b>放大器</b>              | ADRF6518           |

| USB兼容型线性LiFePO4电池 <b>充电器</b>                | ADP5063            |

| RF强化型超低噪声模拟MEMS麦克风                          | ADMP510            |

| Blackfin®双核嵌入式 <b>处理器</b>                   | ADSP-BF60x         |

| 200 mA超低噪声线性 <b>调节器</b>                     | ADM7160            |

| 9月                                          |                    |

| ±200 g三轴低功耗MEMS数字 <b>加速度计</b>               | ADXL375            |

| 5 MSPS 16位逐次逼近型 <b>ADC</b>                  | AD7961             |

| 5 MSPS 18位逐次逼近型 <b>ADC</b>                  | AD7960             |

| RRIO低功耗CMOS运算 <b>放大器</b>                    | ADA4666-2          |

| RRIO精密CMOS运算 <b>放大器</b>                     | ADA4661-2          |

| 低功耗高温运算放大器                                  | AD8634             |

| 6.5 Mbps至11.3 Gbps <b>时钟和数据恢复</b>           | ADN2915            |

| PMBus隔离式电源数字 <b>控制器</b>                     | ADP1051            |

| 30 MHz至6 GHz RF/IF <b>增益模块</b>              | ADL5610/ADL5611    |

| ARM7TDMI 12位I/O精密模拟 <b>微控制器</b>             | ADuC7023           |

| 小容差超低噪声MEMS数字 <b>麦克风</b>                    | ADMP522            |

| 宽动态范围MEMS数字 <b>麦克风</b>                      | ADMP621            |

| 集成VCO、PLL、DGA的700 MHz至2700 MHz              |                    |

| Rx混频器                                       | ADRF6620           |

| 微功耗高温2.5 V基准电压源                             | ADR225             |

| 集成软启动的低噪声、500 mA、20 V LDO调节器                | ADP7105            |

| 集成RF收发器的数字MEMS振动传感器Al                       | DIS16000/ADIS16229 |

| 3 A/5 V逻辑控制型高端或低端负载 <b>开关</b>               | ADP1196            |

|                                             |                    |

-Analog Dialogue

模拟对话杂志(www.analog.com/zh/analogdialogue)是ADI公司于1967年创办的技术杂志,至今已经连续出版47年,主要讨论有关模拟信号、数字信号和混合信号处理产品、应用、技术和技巧。模拟对话杂志目前提供两种版本。 在线版每月发行一期;印刷版每年发行四期。作为对在线版中技术文章的定期回顾和汇集。在线版的内容包括:技术文章;近期应用笔记、新产品简介、在线研讨会、已发表文章等及时信息;以及"集锦"栏目,其中包括从ADI网站(www.analog.com/zh)获得重要相关信息的通用链接网址。感兴趣的读者也可以至Analog Dialogue档案库www.analog.com/library/analogdialogue/china/archives.html查阅自1967年第1卷第1期创刊至今的每期存档,包括三期纪念特刊。如需订阅,请访问www.analog.com/library/analogDialogue/china/subscribe.html。欢迎提出您的宝贵意见:Facebook; www.facebook.com/analogdialogue; 模拟对话博客: analogdiablog.blogspot.com,电子邮件: dialogue.editor@analog.com、编辑Scott Wayne, [scott.wayne@analog.com]。

# 在光电流应用中补偿电流反馈 放大器

作者: Jonathan Pearson

### 简介

电流反馈放大器(CFA)历来都不是跨阻放大器(TIA)的首选,因为它们具有较高的反相输入电流和反相输入电流噪声,可能比同等级电压反馈放大器(VFA)至少高出一个数量级。另外,许多系统设计师对CFA并不熟悉,因为不大愿意使用它们。然而,事实上,CFA使用起来非常简单,而且在要求高增益、低功耗、低噪声、宽带宽和高压摆率的应用中,其性能可能超过VFA。其主要优势之一是,一个理想 CFA的环路增益独立于其闭环增益,为此,CFA可以实现出色的谐波失真和带宽性能,而不受其闭环增益的影响。

因超低的输入偏置电流和输入电流噪声,FET输入运算放大器往往是TIA应用的首选,尤其是将低输出电流器件(如光电元件)用作输入电流源的应用。尽管FET输入放大器在诸多此类应用中技高一筹,但其速度却可能无法满足需要更快性能的系统要求。因此,在可以耐受较大噪声、速度更快的系统中,越来越多地将CFA用作TIA。

本文旨在探讨光电二极管或其他光-电流传感器的寄生电容对用作 TIA的CFA的影响,以及如何针对这种电容对放大器进行补偿。同 时简要介绍CFA运行模式,并说明CFA和VFA分析法之间的相似之 处。本文不使用VFA电路"噪声增益"或者CFA电路"反馈阻抗" 分析法。相反,采用基于环路增益的经典反馈理论,以避免在电 流和电压域之间来回转换时遇到的困难(环路增益始终是一个无维 度的量),而且该理论还可产生直观、易用的波特图。

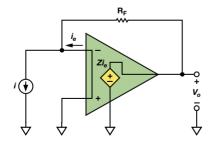

### 电流反馈放大器的基本知识

理想的CFA的输入阻抗为零——其输入端跨接完全短路——因为负 反馈信号为电流。相对地,理想的VFA的输入阻抗则是无穷大,因 为其反馈信号为电压。CFA检测在其输入端中流过的误差电流,并 形成等于Z与输入电流之积的输出电压,其中,Z表示跨阻增益。须 正确定义误差电流的方向,以产生负反馈。与VFA中的A相似,在 理想CFA中,Z接近无穷大。图1所示基本原理展示了如何将理想的 CFA配置成TIA,以便将来自理想电流源的电流转换为输出电压。

图1. 用作TIA的理想CFA

该TIA的闭环增益可以表示为

$$\frac{v_o}{i} = R_F \left[ \frac{1}{1 + \frac{R_F}{Z}} \right]$$

等式1表示,Z接近无穷大,TIA增益则接近其理想值 $R_F$ 。随着Z接近无穷大,误差电流 $i_c$ 接近零,所有输入电流均流过 $R_F$ 。在等式1中,环路增益表示为 Z

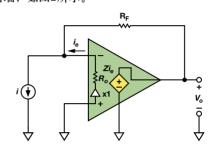

不幸的是,理想的CFA是不存在的,因此,实用器件一般都退而求其次:在其输入端跨接一个单位增益缓冲器。电流镜将误差电流反射至一个高阻抗节点,在此,误差电流被转换成电压,缓冲后馈入输出端,如图2所示。

图2. 用作TIA的实用CFA(带单位增益缓冲器)

只要 $R_o = 0$ ,则闭环增益与等式1中的闭环增益相同。当 $R_o > 0$ 时,闭环增益变成

$$\frac{v_o}{i} = R_F \left[ \frac{1}{1 + \frac{R_F + R_O}{Z}} \right] \tag{2}$$

且环路增益为  $\frac{Z}{R_F + R_O}$  。

### 使用实用元件设计TIA

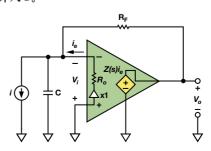

光电二极管和其他光电器件表现出一种与器件面积成比例的寄生分流电容。当Ro = 0时,该电容完全自举,因而不会影响闭环响应。在实际CFA中,Ro > 0,并且寄生电容会影响响应,结果可能导致电路不稳定。另外,就像VFA中的开环增益A一样,在实际CFA中,Z的幅度在低频下较大,随着频率的增加而滚降,而随着频率的增加,相移表现出更大迟滞。对于一阶,Z(s)的特性可以描述为单个主极点,其中,s=p直流跨阻为Zo,如等式3所示。Z(s)中的高频极点稍后再作讨论。

$$Z(s) = \frac{Z_O}{1 - \frac{s}{n}} \tag{3}$$

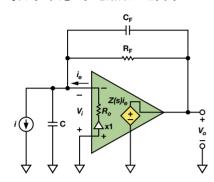

图3中的电路包含寄生电容C和跨阻Z(s)。请注意, CFA的反相输入电容可以并入C。

图3. 基于实用型CFA的TIA(含寄生电容)

通过在反相输入端执行KCL,可求得等式4。

$$\frac{v_o + i_e R_o}{R_E} = -i_e - i_e R_o C s + i \tag{4}$$

误差电流,ie,为

$$i_e = \frac{v_o}{Z(s)} \tag{5}$$

结合等式4和等式5,可以得到如下结果,即图3所示电路的闭环TIA增益:

$$\frac{v_o}{i} = R_F \left| \frac{1}{1 + \frac{R_F R_o C \left(s + \frac{1}{\left(R_F || R_o\right)C}\right)}{Z(s)}} \right|$$

(6)

等式6中的环路增益非常明显,可通过以下等式求得

Loop Gain =

$$\frac{Z(s)}{R_F R_o C \left( s + \frac{1}{(R_F || R_o)C} \right)} = \left[ \frac{Z_o}{1 - \frac{s}{p}} \right] \left[ \frac{1}{R_F R_o C \left( s + \frac{1}{(R_F || R_o)C} \right)} \right]$$

(7)

环路增益含有两个极点,一个低频极点(s=p)以及一个高频极点(s=-p)以及一个高频极点 $(s=-\frac{1}{(R_F||R_o)C})$ 。当 $R_o$ <<  $R_F$ 时, $R_F$ 和 $R_o$ 的并联结果可

以通过R。近似求出。如果在高频极点发生的频率下,环路增益的幅度大于0 dB,则这两个极点会带来稳定性问题。当R。和C较小时,寄生极点发生的频率高于交越频率,放大器稳定。但在多数TIA电路中,情况并非如此,因此,我们必须找到一种办法,对反相输入寄生电容进行补偿。

### 添加一个反馈电容(题外话)

带有单极点传递函数(如等式3所示)的CFA在任何反馈电阻值下都表现稳定,因为其反馈环路周围的迟滞相移被限制为 $-90^{\circ}$ 。但实际CFA的次要极点在高频下会带来较大的相移迟滞,因此,为了确保稳定性,实际会对 $R_F$ 的最小值做出限制( $45^{\circ}$ 一般是可接受的最小相位裕量)。此后,Z(s)将包含一个高频极点( $s=p_H$ )和一个主极点(s=p)。

为了确保反馈阻抗不变成零,通常建议在任何CFA电路中都不应使用反馈电容。然而,事情并非如此简单,因为在幅度变化以外,反馈电容还会导致相移。本节将考察将一个反馈电容添加至基于CFA的TIA时产生的结果,暂且忽略寄生输入电容。在图2所示电路中,在反馈电阻 $R_F$ 上跨接一个反馈电容 $C_F$ ,结果形成一个极点,并在环路增益中产生一个零。 $Z_F$ 定义为 $R_F$ 和 $C_F$ 的并联结果:

$$Z_F = \frac{1}{C_F \left( s + \frac{1}{R_F C_F} \right)} \tag{8}$$

如果以ZF取代等式2中的RF,则闭环增益可表示为等式9。

$$\frac{v_o}{i} = \left[ \frac{1}{C_F \left( s + \frac{1}{R_F C_F} \right)} \right] \frac{1}{1 + \frac{R_o \left( s + \frac{1}{(R_O \parallel R_F) C_F} \right)}{Z(s) \left( s + \frac{1}{R_F C_F} \right)}}$$

(9)

此时, 环路增益为

Loop Gain =

$$\frac{Z(s)\left(s + \frac{1}{R_F C_F}\right)}{R_O\left(s + \frac{1}{(R_O \parallel R_F)C_F}\right)} = \left(\frac{Z_O}{R_O}\right) \frac{\left(s + \frac{1}{R_F C_F}\right)}{\left(1 - \frac{s}{p}\right)\left(1 - \frac{s}{p_H}\right)\left(s + \frac{1}{(R_O \parallel R_F)C_F}\right)}$$

(10)

环路增益有一个来自Z(s)的主极点(s=p)和一个高频极点 $(s=p_H)$ 。另外,受增加的反馈电容的影响,在  $s=-\frac{1}{\left(R_O \parallel R_E\right)C_E}$

时形成一个极点,在

$$s = -\frac{1}{R_F C_F}$$

时产生一个零。

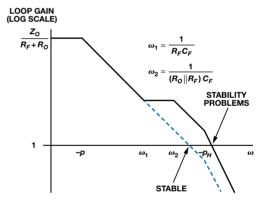

在波特图中, $C_F$ 导致的零产生时的频率低于 $C_F$ 导致的极点,因为零频率表达式的分母中含有 $R_F$ ,而极点频率表达式的分母中则含有 $(R_o||R_F)$ 。一种基于CFA的可能TIA(含 $C_F$ (等式10))的波特图如图4所示。

图4. 基于CFA的TIA(含反馈)的波特图

随着频率的增加,零会导致幅度不断提高,相移不断加大,从稳定性角度来看,在某些情况下,这可能是一件好事。但在图4所示系统中,零出现在环路增益跨过0 dB之处,而  $p_H$ 下的极点则在跨交越点—40 dB/十倍频程时导致幅度渐近线下降。蓝色虚线表示不含 $C_F$ 的环路增益,采用的是等式2以及双极点版本的Z(s)(见等式11)。

Loop Gain without

$$C_F = \frac{Z_O}{R_F + R_O} \left( \frac{1}{\left(1 - \frac{S}{p}\right) \left(1 - \frac{S}{p_H}\right)} \right)$$

(11)

图4表明,当无 $C_F$ 时,放大器表现稳定,但在添加 $C_F$ 之后,则会产生稳定性问题。图4中的坐标图并不完全排除反馈电容的使用,因为该特定Z(s)并不代表所有CFA,而且未使用实际电阻和电容值,尽管如此,图中确实表明,高频极点会限制可以安全应用的反

馈电容。图4同时表明,可以向一个带单极点传递函数的假想CFA安全添加任意量的反馈电容,而添加反馈电容会增加其闭环带宽。

### 使用CF导致的零抵销寄生电容导致的极点

以上简要介绍了向CFA添加 $C_F$ 产生的影响,从中可以看出,可以安全使用 $C_F$ 来补偿输入电流源的寄生分流电容。

图3所示电路的闭环增益表示为等式6。为了厘清添加反馈电容对该电路的影响,可用 $Z_F$ 取代等式6中的 $R_F$ ,与推导等式9的方法相似,其中, $Z_F$ 由等式8定义。电路如图5所示。

图5. 基于实用CFA的TIA(用CF补偿寄生电容)

图5所示电路的闭环增益可通过等式12求得

$$\frac{v_o}{i} = \left[ \frac{1}{C_F \left( s + \frac{1}{R_F C_F} \right)} \right] \frac{1}{1 + \frac{R_o \left( C + C_F \right) \left( s + \frac{1}{\left( R_F || R_o \right) \left( C + C_F \right)} \right)}{Z(s) C_F \left( s + \frac{1}{R_F C_F} \right)}$$

(12)

根据该等式,可以算出环路增益为

$$\text{Loop Gain with } C \text{ and } C_F = \frac{Z(s)C_F \left( s + \frac{1}{R_F C_F} \right)}{R_o \left( C + C_F \right) \left( s + \frac{1}{\left( R_F || R_o \right) \left( C + C_F \right)} \right)} =$$

$$\left(\frac{Z_{o}C_{F}}{R_{o}(C+C_{F})}\right) \frac{\left(s+\frac{1}{R_{F}C_{F}}\right)}{\left(1-\frac{s}{p}\right)\left(1-\frac{s}{p_{H}}\right)\left(s+\frac{1}{(R_{F}||R_{o})(C+C_{F})}\right)}$$

(13)

等式13中,因 $C_F$ 导致的零与等式10中的零相同,但 $C_F$ 导致的极点则从

$$s = -\frac{1}{(R_O \parallel R_F)C_F}$$

移到了  $s = -\frac{1}{(R_O \parallel R_F)(C + C_F)}$ .

通过向 $C_F$ 添加C,可以移动极点位置,以匹配零的位置,从而抵销掉输入电流源的寄生电容C导致的极点。在等式13中,将 $C_F$ 和C导致的极点频率设为因 $C_F$ 导致的零频率,则得到等式14:

$$\frac{1}{R_F C_F} = \frac{1}{\left(R_F \parallel R_o\right) \left(C + C_F\right)} \Rightarrow C_F = \left(\frac{R_o}{R_F}\right) C \tag{14}$$

等式14所示为计算 $C_F$ 的值的简单公式,该值可抵销图5所示TIA中的寄生电容C导致的环路增益中的极点。以这种方式将极点零完美

抵销之后,环路增益会回归最初形式,含有主极点和高频极点,如 等式11所示。至此,闭环增益可以表示为等式15。

$$\frac{v_o}{i} = \left[ \frac{1}{C_F \left( s + \frac{1}{R_F C_F} \right)} \right] \left[ \frac{1}{1 + \frac{R_F + R_O}{Z(s)}} \right]$$

(15)

在使用等式14时,遇到的主要困难是确定R。,该值是可变的,而且CFA数据手册中未必提供其额定值。然而,只要环路增益图的斜率在通过0 dB时合理接近-20 dB/十倍频程,则极点-零抵销无需如此精确。等式14表明, $C_F$ 随R。线性递减,因为随着R。接近0,自举发生次数会增加,其中,C完全自举,所需 $C_F$ 等于0。等式14也可表示为一种匹配时间常数形式,如 $R_0C=R_FC_F$ 。等式14的匹配时间常数形式与对VFA进行寄生求和节点电容补偿时获得的结果非常相似: $R_GC_G=R_FC_F$ ,其中 $R_G$ 为VFA增益电阻, $C_G$ 为 $R_G$ 的交越电容,该电容一般为寄生求和节点电容。然而,获得这种优势是需要付出代价的。虽然添加 $C_F$ 可使TIA变稳定,但同时也会在  $S=-\frac{1}{R_0C_B}$ ,时在闭环增益中导致一个极点,

如等式12和等式15所示。等式15所描述的闭环增益可以视为传递 函数相乘的两个级联系统。第一个系统的传递函数为等式15中最 左侧的因子,维度为欧姆。第二个系统的传递函数为等式15中最 右侧的因子,无维度。

第二个系统的响应取决于环路增益,只要环路增益幅度在-20 dB/十倍频程时跨过0 dB,就可以模拟为一个一阶传递函数。基本反馈理论表明,如果达到这一滚降条件,当环路增益幅度>>1时,第二个系统的闭环增益幅度约等于单位增益,当环路增益幅度<<1时,则跟随环路增益幅度。闭环增益中的3-dB点出现在环路增益幅度跨过0 dB时的频率(如果斜率略快于-20 dB/十倍频程,则在接近0-dB交越点之处,闭环响应中会出现一些峰化)。因此,在一个稳定的放大器中,第二个系统可以近似模拟为一个一阶、低通滤波器,其单位增益处于通带中,且截止频率等于环路增益幅度跨过0 dB时的频率。第一个系统的传递函数为反馈因子的倒数,其响应为简单的一阶、低通响应,直流值为RF,转折频率为

$$\frac{1}{2\pi R_F C_F}$$

凭直觉可以看出, $C_F$ 导致的额外极点是意义的,因为输出电压是流过反馈阻抗的电流形成的,而反馈阻抗随频率增加而下降。当  $C_F$ 的电抗等于 $R_F$ 的值时,会形成极点。在使用反馈电容补偿、基于VFA的TIA中会发生相同的情况。不过可以略微扩大闭环带宽,其方法是从根据等式14计算的值开始,小心地减小 $C_F$ ,移出极点频率,并缩减相位裕量,但这只能尝试着做。

### 仿真数据

为了测试该结果,我们针对CFA提出了一种简单的仿真模型,其中, $Z_o=1$  M $\Omega$ ,  $p=-2\pi$  (100 kHz),  $p_H=-2\pi$  (200 MHz),  $R_o=50$   $\Omega$ , 且 $R_F=500$   $\Omega$ 。环路增益的幅度则可通过以这些值代入等式11中的幅度计算得到。

|Loop Gain without

$$C_F$$

| =  $\frac{10^6}{500 + 50} \left( \frac{1}{\sqrt{1 + \left(\frac{f}{100 \text{ kHz}}\right)^2} \sqrt{1 + \left(\frac{f}{200 \text{ MHz}}\right)^2}} \right)$  (16)

结果约等于1, 其中 f = 145 MHz。

### 145 MHz时的环路增益相移为

$$\angle$$

Loop Gain without  $C_F = -\tan^{-1} \left( \frac{145 \text{ MHz}}{100 \text{ kHz}} \right) - \tan^{-1} \left( \frac{145 \text{ MHz}}{200 \text{ MHz}} \right) \approx -126^{\circ}, (17)$

结果得到大约54°的相位裕量,对于无寄生电容的基本CFA来说,这是一个不错的起点。

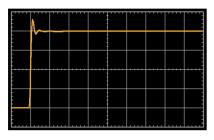

图6所示为该模型的响应仿真情况,其中,电流阶跃输入上升时间 为1-ns。

图6. 基本TIA的阶跃响应(无寄生电容)(20 ns/div)。

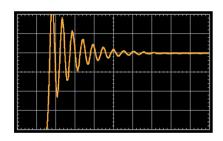

响应非常干净,响铃振荡已减至最小——为54°相位裕量条件下的 应有水平。对于同一放大器,当在反相输入端和接地之间添加一个50 pF的寄生电容时,其阶跃响应如图7所示。

图7. 阶跃响应(反相输入端与接地之间存在50 pF的电容) (20 ns/div)。

图7中的纵坐标与图6相同,只是轨迹下移了一个刻度,以适应响铃振荡。显然存在过多响铃振荡,这种放大器明显有相位裕量问题。放大器可以通过添加一个反馈电容(其值通过等式14决定)来实现稳定化,经计算,该电容为5 pF。图8 所示为添加5-pF反馈电容后的结果。

图8. 阶跃响应(以5 pF反馈电容实现极点/零抵销)(20 ns/div)。

显然,闭环增益中的极点会对频带形成限制。原始放大器的环路增益0-dB交越确定为145 MHz,相当于一阶系统中约1.1的时间常数,RFCF时间常数为2.5 ns(注意,0-dB交越时,环路增益幅度滚降速率略快于-20 dB/十倍频程,因为相位裕量少于90°,但一阶闭环模型是一种比较精确的近似模型)。使用由两个级联系统构成的上述模型,级联系统的合并时间常数可以估算为两个时间常数的方和根(输入电流源10%至90%的上升时间为1 ns,相当于次纳秒级的有效时间常数,可忽略不计),即2.7 ns左右,似乎与图7所示响应相符合。

将C<sub>F</sub>降为3 pF可以略微减少相位裕量,加大闭环极点频率,由此提升速度,如图9所示。

图9. 阶跃响应(带3-pF反馈电容)(20 ns/div)。

显然,要获得最佳的C<sub>F</sub>的值,需要进行一些实验。诸如负载电容、 电路板布局、R<sub>o</sub>变化等因素在挑选C<sub>F</sub>时也是需要考虑的。

### 结论

随着将CFA用作TIA的做法日渐盛行,有必要了解如何对CFA反相输入端的传感器电容进行补偿,有必要了解补偿机制的工作原理。本文基于经典反馈技术,提出了一种简便办法,即将一个反馈电容与反馈电阻并联起来,对反相输入电容进行补偿。反馈电容会在闭环响应中导致一个无用极点,但可以基于计算所得值对电容的值进行调整,以减少极点对频带的限制作用。

### 参考文献

Gray, Paul R., and Robert G. Meyer. *Analysis and Design of Analog Integrated Circuits*. John Wiley & Sons, Inc., 1977.

Lundberg, Kent. "Feedback Control Systems." M.I.T. Course Notes.

Roberge, James K. Operational Amplifier: Theory and Practice. John Wiley & Sons, 1975.

### 作者简介

Jonathan Pearson [jonathan.pearson@analog.com] 从2002年8月开始,一直是高速放大器部门的一位高级应用工程师。加盟ADI之前,他在电信行业从事模拟电路和系统设计工作。他持有美国东北大学电机工程学士学位,以及WPI电机工程学硕士学

位,独立/与他人合作注册专利4项。除了与家人共度美好时光以外,他还喜欢弹各种吉它,录制音乐,收集真空管吉它放大器和古董收音机。

# 在多通道应用中使用放大器 禁用功能代替多路复用器

作者: Charly El-Khoury

多路复用器(MUX)可将信号从多个输入的其中之一路由至公共输出,允许共享某个器件或资源——如混合信号应用中的ADC或视频应用中的显示屏——而非为每个输入指定专用器件。很多应用会在信号进入多路复用器之前,使用放大器对其进行调理。这种情况下,带禁用功能的放大器可用来选择通道,因此无需使用多路复用器,同时还能降低成本、减少PCB面积与失真。本文介绍使用具有禁用功能的运算放大器进行通道选择时遇到的挑战,并提供采用ADI高速放大器产品组合的示例。

首先,必须比较*禁用*功能与关断功能。放大器禁用时,功耗下降,输出进入高阻态,允许将多个输出连在一起。该功能与关断不同,其目的仅在于节省功耗。

使用运算放大器选择通道时,还需要考虑放大器输入之间允许的最大电压。该信息通常可在数据手册的"绝对最大额定值"部分找到,如图1所示。如果该放大器的输入之间具有背靠背二极管,则差分输入电压将限制为——甚至放大器禁用时也是如此——0.7V、1.2V或更高,具体取决于串联背靠背二极管的数目。

### ABSOLUTE MAXIMUM RATINGS1

| INDOOLE IL MEMINICITI IUTIN (GO              |            |

|----------------------------------------------|------------|

| Supply Voltage                               | 12.6 V     |

| Internal Power Dissipation <sup>2</sup>      |            |

| PDIP Package (N)                             | 1.3 W      |

| SOIC Package (R)                             | 0.9 W      |

| Input Voltage (Common Mode)                  | $ \pm v_S$ |

| Differential Input Voltage                   | ±3.4 V     |

| Output Short Circuit Duration                |            |

| Observe Power Derating O                     | Curves     |

| Storage Temperature Range N, R65°C to +      | 125°C      |

| Operating Temperature Range (A Grade)40°C to | +85°C      |

| Lead Temperature Range (Soldering 10 sec)    | 300°C      |

|                                              |            |

### 图1. AD8041绝对最大额定值

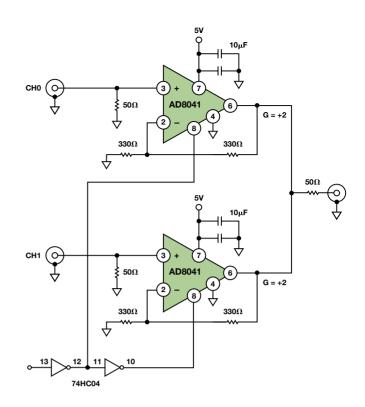

某些放大器(如AD8041)在输入之间没有背靠背二极管,因此可处理高达±3.4 V的差分输入电压。禁用时,放大器输出处于高阻态。两个放大器的增益配置为2,可相连并选择两通道之一,同时采用5 V单电源工作,如图2所示。

图2. 使用两个AD8041运算放大器构建的2:1多路复用器

但是,这并非对所有集成禁用引脚的放大器有效。为了演示该特性,表1显示集成禁用功能的某些高速放大器,以及差分输入电压额定值、带宽和最小增益要求。

表1. 集成禁用功能的高速放大器

| 器件号码      | 放大器数 | 帯宽<br>(MHz) | 差分输入电压(V) | 最小稳定<br>增益 |

|-----------|------|-------------|-----------|------------|

| AD8021    | 单    | 490         | ±0.8      | 1          |

| AD8027    | 单    | 190         | ±1.8      | 1          |

| AD8029    | 单    | 125         | ±1.8      | 1          |

| AD8041    | 单    | 160         | ±3.4      | 1          |

| AD8063    | 单    | 320         | ±6        | 1          |

| AD8099    | 单    | 440         | ±1.8      | 2          |

| ADA4853-1 | 单    | 100         | ±5        | 1          |

| ADA4895-1 | 单    | 236         | ±0.7      | 10         |

| ADA4897-1 | 单    | 230         | ±0.7      | 1          |

| ADA4899-1 | 单    | 535         | ±1.2      | 1          |

| AD8028    | 双    | 190         | ±1.8      | 1          |

| ADA4853-2 | 双    | 100         | ±5        | 1          |

| ADA4895-2 | 双    | 236         | ±0.7      | 10         |

| ADA4897-2 | 双    | 230         | ±0.7      | 1          |

| AD813     | 三    | 125         | ±6        | 1          |

| AD8013    | 三    | 230         | ±6        | 1          |

| AD8023    | 三    | 460         | ±3        | 1          |

| ADA4853-3 | 三    | 100         | ±5        | 1          |

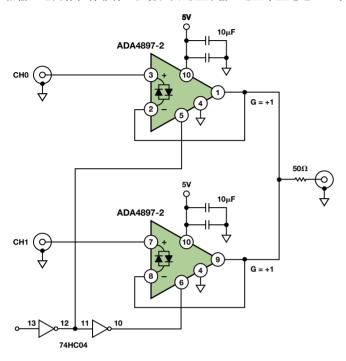

例如,针对信号调理和通道选择,使用集成独立禁用引脚的双通道低功耗运算放大器ADA4897-2,无需多路复用器。图3显示两个单位增益缓冲器配置为2:1通道选择器的简单原理图。本文将分析三种情况:1)两个输入源CH0和CH1具有2.5 V直流电平和0.5 Vp-p交流信号;2)相同信号,但两个输入源之间具有1 V直流失调3)相同直流电平,1 Vp-p交流信号。由于每个放大器的反相和同相输入之间存在背靠背二极管,因此差分输入电压不应超过0.7 V。

图3. 使用双通道ADA4897-2构成2:1多路复用器

使能放大器时,反馈功能迫使反相和同相输入相等,但禁用放大器后,反馈环路开路,输入发生漂移。如果两个输入之间存在背靠背二极管,则输入漂移的程度也会受到限制。对于ADA4897-2而言,输入漂移程度不能超过二极管压降(0.7 V),否则背靠背二极管就会开启。为了帮助演示这一点,图4显示该电路的简化原理图,图中禁用了一个放大器。

8

图4. 图3禁用一个放大器的简化原理图

回到我们所说的三种情况。如果CH0和CH1上的直流电平相等,则二极管正向偏置之前,两个输入源之间允许存在的最大差分交流信号为0.7~V。在第一种情况中,电路能正常工作,因为最大差分信号仅0.5~V p-p。在第二种情况中,两个输入源的直流失调电平大于0.7~V,因此电路不工作。在第三种情况中,当两个输入源之间具有 $180^\circ$ 相位差时,最大差分信号可达1~V p-p。这将导致背

靠背二极管正向偏置,因此电路在这种情况下也无法工作。针对后两种情况,使用AD8041或其他差分输入电压足够大的放大器(表1中的器件)将是更好的选择。

如果出于成本或性能考虑而必须使用带有背靠背二极管的放大器,并且如果无法添加额外的多路复用器,则可将放大器增益设为1以上,或者使用单位增益配置的反馈电阻,这样可以使问题不那么严重。第二种情况只有在使用电压反馈放大器时才会有问题,因为这种情况下不应使用单位增益反馈电阻。如需处理峰值问题,则可以使用一个电容与反馈电阻并联连接,降低峰值电平,最小化反馈电阻效应。

图5所示为图2的简化原理图,但使用ADA4897-2代替AD8041。放大器的增益配置为2。

图5. 图2的简化原理图,使用ADA4897-2

在该电路中,反馈电阻限制流过背靠背二极管的电流。这样可以使二极管不会完全正向偏置,对电路形成负载。假设CH0和CH1具有1 V p-p,则电阻两端的最大差分信号(假定二极管压降为0.7 V) 就是1.5 V - 0.7 V = 0.8 V,相当于0.8 V/330 Ω = 2.4 mA电流。相比负载电流,该最差情况下的电流足够低,因此放大器应当能提供该电流,同时驱动电路的其余部分。如有必要,可以增加反馈电阻值,以便降低电流。采用2作为增益值而非使用单位增益(如假定该配置下的电压反馈放大器稳定,则可以使用单位增益反馈电阻)将允许交流输入电压倍增。使用反馈和增益电阻时,在反相输入端增加直流偏置可以消除CH0和CH1之间的失调直流电压电平。在高精度应用中,使用非背靠背二极管的放大器可能效果更佳,因为二极管会使信号失真,哪怕它们并未完全导通。

总之,只要所有输入背靠背二极管保持非饱和状态,就可以将带禁用功能的放大器用作通道选择器。单位增益配置相比更高的增益会有更多限制,该配置下增益和反馈电阻可用于限制流过背靠背二极管的电流,消除直流偏置。若需要单位增益,可在反馈环路中使用电阻,前提是该配置下的放大器稳定。最后,请记住,背靠背二极管会产生失真,因此对于高精度应用而言,使用无背靠背二极管的放大器可能是更好的选择。

### 作者简介

Charly El-Khoury [charly.el-khoury@analog.com] 是高速放大器部门的应用工程师。他于2006年毕业于伍斯特理工学院(WPI),获得电气与计算机工程(ECE)硕士学位,之后加入ADI公司。

# 多路复用三线式RTD数据采 集系统的误差最小化

作者: Henry He

电阻温度检测器(RTD)可在很多工业应用中监控温度。在一个分布式控制系统(DCS)或可编程逻辑控制器(PLC)中,一个数据采集模块可用来监控很多安装在远处的RTD温度。在高性能应用中,若每个RTD都自带激励电路和ADC,则具有最佳的精度,但数据采集模块将会体积庞大、成本高昂,且功耗高。多路复用模块具有体积较小、成本和功耗较低的特性,但可能会损失一定精度性能。本文讨论如何最小化多路复用系统误差。

### 电路结构

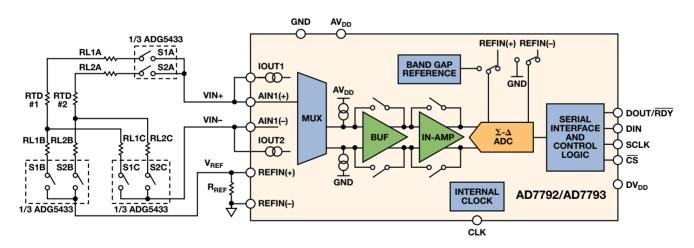

提供双线式、三线式和四线式RTD配置,其中,双线式配置的器件成本最低,四线式器件精度最佳。三线式RTD通常用于工业应用中,可采用两个相同的电流源激励,以消除引脚电阻。与精密参考电阻一同使用时,电流源误差不影响测量精度。高性能ADC(如AD7792和AD7793)集成激励电流源,适合高精度RTD测量。

图1显示片内电流源激励两个三线式RTD。RTD通道可由多路复用器选择,如ADG5433高压、防闩锁、三路SPDT开关。

一次只能测量一个RTD。S1A、S1B和S1C闭合测量RTD #1,S2A、S2B和S3B闭合测量RTD #2。单个ADG5433可切换两个三线式RTD,可增加额外的多路复用器处理两个以上的传感器。 $RL_{XX}$ 表示RTD和测量系统之间由于导线过长引入的电阻以及开关的导通电阻。

### 计算RTD电阻

由于S1A、S1B和S1C闭环测量RTD #1, RTD电阻可计算如下:

Define

$$\Delta V_{IN} = V_{IN+} - V_{IN-}$$

Assume  $I_{OUTI} = I_{OUT2} = I_{OUT}$  and  $RL_{IA} = RL_{IB} = RL_{IC}$

$$I_{OUTI} + I_{OUT2} \text{ flows through } R_{REF}, \text{ so } I_{OUTI} = \frac{V_{REF}}{2R_{REF}}$$

$$RTD = \Delta V_{IN} / I_{OUT} = \frac{\Delta V_{IN} \times 2R_{REF}}{V_{REF}}$$

因此,测量值仅取决于 $R_{REF}$ 的数值(和精度)。但请记住,我们假定  $I_{OUT1} = I_{OUT2}$ ,并且 $RL_{1A} = RL_{1B} = RL_{1C}$ 。事实上,这些电流和电阻失配是测量误差的主要来源。

### 电流源和线路电阻失配的影响

下一步,假定两个电流源失配,比如 $I_{OUT2} = (1 + x) I_{OUT1}$ 。现在,考虑下列情况:

$$RTD = \frac{\Delta V_{IN}}{V_{REF}} (2 + x) R_{REF} + (1 + x) RL_{IC} - RL_{IA}$$

图1. 两个三线式RTD多路复用至一个AD7792/AD7793 ADC

请注意,失配会导致失调误差以及增益误差。失调误差与两个引脚电阻之间的失配有关,而增益误差与两个电流源之间的失配有关。如果不考虑这些失配情况,则根据ADC的数据读数计算的RTD电阻值将是不准确的。

以200  $\Omega$  RTD为例,表1显示不考虑失配时,得到的数值,其中, $R_{\rm REF}$  = 1000  $\Omega$ , $I_{\rm OUT1}$  = 1 mA, $I_{\rm OUT2}$  >  $I_{\rm OUT1}$ (以百分比显示), $RL_{\rm IA}$  = 10  $\Omega$ , $RL_{\rm IC}$  >  $RL_{\rm IA}$ (以电阻值显示)。

表1. 不考虑失配时的RTD测量值

| $RL_{1C} - RL_{1A}$ $(I_{OUT2} - I_{OUT1})/I_{OUT1}$ | 0.01 Ω | 0.1 Ω  | 1 Ω    |

|------------------------------------------------------|--------|--------|--------|

| 0.1%                                                 | 199.88 | 199.79 | 198.89 |

| 0.5%                                                 | 199.44 | 199.35 | 198.45 |

| 1.0%                                                 | 198.90 | 198.81 | 197.90 |

### 最小化误差

数据显示很小的失配就会严重影响精度,因此应当使用匹配良好 的电流源和开关,以便改进性能。

传递函数是线性的,因此可轻松校准电流源和电阻失配导致的初始 误差。然而,失配随温度的变化而改变,这使得补偿变得很不容易。 因此,选用的器件应随温度的变化而具有低漂移特性。

若 $I_{OUT1}$  ≠  $I_{OUT2}$ , 且电流源如图所示连接:

$$\Delta V_{INI} = I_{OUTI} (RL_{IA} + RTD) - I_{OUT2} \times RL_{IC}$$

假定我们交换 $I_{\text{OUT}1}$ 和 $I_{\text{OUT}2}$ ,使 $I_{\text{OUT}1}$ 连接 $V_{\text{IN-}}$ 和 $I_{\text{OUT}2}$ ,并连接 $V_{\text{IN+}}$ :

$$\Delta V_{IN2} = I_{OUT2} (RL_{1A} + RTD) - I_{OUT1} \times RL_{1C}$$

现在,如果我们对转换结果求和,并且电流源以初始方向连接,同时第二次转换时交换电流源,则可得:

$$\begin{split} \Delta V_{INI} + \Delta V_{IN2} &= (I_{OUTI} + I_{OUT2}) \times (RTD + RL_{IA} - RL_{IC}) = \\ &\frac{V_{REF}}{R_{RFF}} \left(RTD + RL_{IA} - RL_{IC}\right) \end{split}$$

Consequently,

$$RTD = \frac{\Delta V_{INI} + \Delta V_{IN2}}{V_{REF}} \times R_{REF} + RL_{IC} - RL_{IA}$$

请注意,测量值现已独立于电流源失配。唯一的缺点是速度的损失,因为每次RTD计算都需经过两次转换。

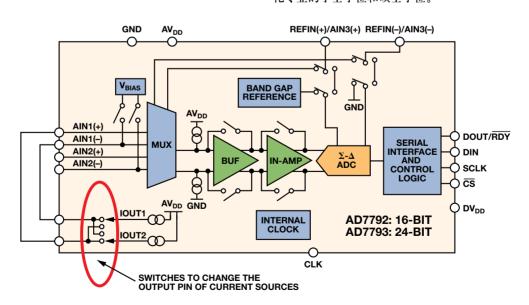

AD7792和AD7793针对该应用设计。如图2所示,通过写入I/O寄存器,集成开关可简化电流源到输出引脚的交换。

### 结论

在AD7792/AD7793器件内交换激励电流源可改善多路复用RTD 测量电路的精度。计算显示了电流源和线路电阻之间失配问题的 重要性。

### 参考文献

Kester, Walt, James Bryant, and Walt Jung. "Temperature Sensors." Sensor Signal Conditioning, Section 7. Analog Devices, Inc., 1999.

### 作者简介

Henry He [henry.he@analog.com] 于2012年加入ADI公司,担任中国北京现场应用工程师一职。加入ADI之前,Henry曾经作为硬件工程师服务于GE Energy和SUPCON公司。他拥有浙江大学工业自动化专业的学士学位和硕士学位。

图2. AD7792/AD7793功能框图

# 系统演示平台简化从评估到 原型制作的过渡

作者: Rosemary Ryan

### 简介

ADI公司面向设计工程师提供评估板和应用软件,简化新设计的元器件选型过程。完成初始评估后,设计的某些方面通常需要进一步研究。元器件如何连接系统的FPGA、微控制器或数字信号处理器(DSP)? 完成系统设计前是否可对接口和应用代码进行验证? 还没收到印刷电路板的时候能否先进行HDL编码? 节省时间并增加成功可能性的最佳方法是在搭建电路板之前先准备好代码和接口。虽然ADI的系统演示平台(SDP)主要是一款评估工具,但它同时设计为允许进行这类原型制作,为开启系统开发过程提供前所未有的便捷性。

### 系统演示平台

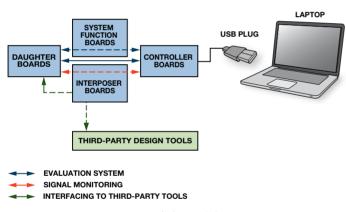

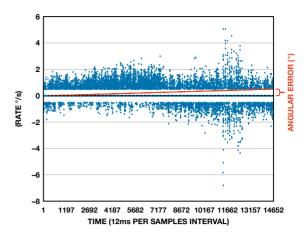

图1中低成本、可重复使用的SDP评估平台在设计时充分考虑到了 功能的多样性。该平台由*控制板、转接板和子评估板*组成,可快 速、方便地实现评估到原型制作的过渡。

图1. 系统演示平台概述

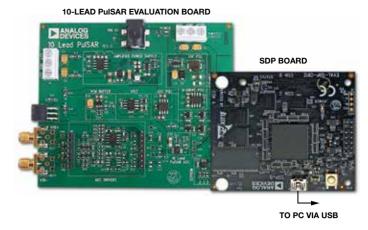

该双板评估系统包括一块控制器板,可配合多块子板重复使用。控制器板通过USB 2.0接口连接个人计算机(PC),利用标准120引脚连接器为子板提供一系列常用的通信接口。同一个120引脚连接器兼容超过180款电路板,用于产品评估以及参考电路评估;该连接器还可连接待评估元器件的输入和输出信号。全系列产品评估板可用于ADC、DAC、DDS、RF PLL和MEMS麦克风等产品的评估。参考电路评估板可用于所有采用了ADI元器件的应用,包括汽车电子、医疗保健、过程控制和工业自动化。图2显示SDP-B控制板连接至PulSAR® ADC评估板。如需所提供评估板的完整列表,请访问www.analog.com/sdp。

图2. 使用SDP-B和PulSAR ADC评估板的评估硬件设置

该平台还集成了一系列转接板,允许宽范围子板直接连接第三方评估工具,如Xilinx® FPGA评估板或BeMicro软件开发套件(SDK)。这些转接板将ADI评估板上的元器件输入和输出连接至Xilinx或Altera® FPGA,是利用ADI评估板和第三方工具进行快速、方便原型制作的关键。

### 120引脚连接器

120引脚控制器采用与ADI公司DSP EZ-KIT Lite®相同、明确定义的标准引脚排列。连接器包括SPI、I<sup>2</sup>C、SPORT、GPIO、定时器和并行接口,以及电源和接地引脚。连接器支持3.3 V逻辑电平。

### 转接板

转接板通过标准120引脚连接器连接子板。然后它们将信号从120引脚连接器路由至第二个连接器,允许用户将子板连接至自行选择的FPGA评估板。转接板不包含任何额外的逻辑或信号调理,仅仅将信号从SDP连接器路由至第二个连接器——例如VITA57标准FMC连接器。提供三种转接板,包括SDP-I-FMC转接板、BeMicroSDK/SDP转接板和SDP分线板。

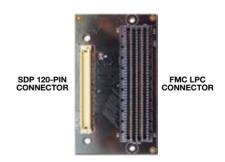

### SDP-I-FMC转接板

如图3所示,SDP-I-FMC转接板可将任意SDP兼容型评估板连接至支持3.3-V I/O的Xilinx FPGA评估板。它集成标准120引脚连接器和低引脚数(LPC) FMC连接器,属于业界标准VITA 57规范的一部分,规定I/O到FPGA的连接性能。子板上的120引脚连接器连接SDP-I-FMC转接板上的120引脚插座。随后,SDP-I-FMC转接板上的FMC连接器连接Xilinx评估板上的FMC连接器。

图3. SDP-I-FMC转接板

Kintex KC705是Xilinx评估板的一个示例,集成3.3 V I/O和FMC 连接器。因此,它可以通过SDP-I-FMC连接ADI评估板,如图4所示。ADI Wiki知识库提供大量SDP兼容型评估板的示例代码,允许用户尽早开始FPGA的开发。欲获得有关SDP-I-FMC的更多信息,包括原理图和订购信息,请访问www.analog.com/sdpFMC。该板零售价为49美元/片。

图4. SDP-I-FMC转接板连接 子板与Kintex KC705评估板。

### BeMicro SDK/SDP转接板

BeMicro SDK/SDP转接板(如图5所示)允许用户将子板与BeMicro SDK评估板上的BeMicro SDK/SDP转接板提供标准120引脚连接器,可连接ADI评估板,同时,BeMicro边缘连接器插座与BeMicro SDK相连。来自SDP连接器的信号路由至边缘连接器插座。BeMicro SDK/SDP转接板可前往www.arrownac.com购买,价格为50美元/片(部件名称:ADI转接板)。如需获得原理图及其他信息,请访问:www.analog.com/bemicroSDP。

SDP 120-PIN CONNECTOR 图5. BeMicro SDK/SDP转接板

### **BeMicro SDK**

BeMicro SDK是基于Altera Cyclone IV的硬件评估平台,可使用 NIOS II处理器创建、编译、运行和调试嵌入式软件。该产品由 Arrow与Altera公司合作开发,提供小型、低成本、易于使用的 FPGA评估和开发平台。大量SDP兼容型评估板的BeMicro SDK示例项目可通过下列网址访问:wiki.analog.com/resources/alliances/altera。一个良好的开端——许多可供使用的元器件接口示例——可以减少FPGA系统开发时间。

图6. BeMicro SDK/SDP转接板连接子板与BeMicro SDK

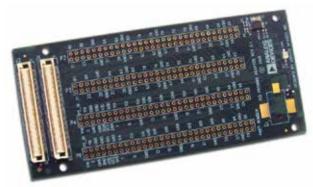

### SDP分线板

SDP分线板有4个120引脚连接器。J1和P1用于SDP和SDP兼容型评估板,J2和P2用于ADSP-BF60x EZ-KIT。该板主要用于信号监控。每个探测点都代表连接器上的一个引脚,允许示波器监控该引脚上的活动。没有专用的转接板硬件时,该板还可作为原型制作的有效工具。

图7. SDP分线板

该板提供4排通孔探测点,如图8所示。这些探测点可方便地连接 DSP或微控制器评估板。来自J1和J2的信号路由至SDP分线板底 部的P1和P2。

图8. SDP分线板顶视图

(接第14页)

# 缩短积分时间可以提高航位 推算导航系统的精度

作者: Ben Wang

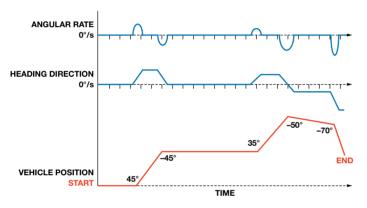

汽车航位推算(DR)导航系统采用一个陀螺仪(gyro)来推算车辆的即时航向。借助该信息再加上行驶的距离,导航系统可以正确确定车辆的位置,即使卫星信号因拥挤的城区环境或隧道而受阻时亦是如此。在DR导航中使用陀螺仪的一个重大挑战是,卫星信号可能会丢失较长时间,结果使累积角度误差过大而无法精确定位车辆。本文为这个问题提出了一种简单的解决办法。

### DR导航的工作原理

图1所示为DR导航的基本工作原理。一个陀螺仪测量车辆的旋转速率,单位为度/秒。代表车辆即时航向的角度通过计算旋转速率的时间积分而求得。结合航向和行驶距离,可以确定车辆的位置,如图中的红线所示。

图1. DR导航的工作原理。

使用数字陀螺仪时,积分速率可以表示为速率样本和与采样间隔 之积:

$$angle = \sum_{i=1}^{n} r_i \times \tau$$

其中, $r_i$ 为陀螺仪检测到的速率,n为样本数, $\tau$ 为采样间隔。随时间累积的角度误差可以表示为:

angular error =

$$\sum_{i=1}^{n} e_i \times \tau$$

其中, e<sub>i</sub>为各样本的速率误差, n为样本数, 7为采样间隔。

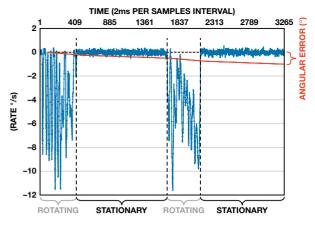

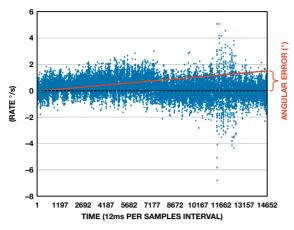

根据该公式,随着所需积分时间变长,累积误差变大,如图2所示。这些速率样本(用带ADXRS810高性能角速率传感器的评估板测得)模拟的是共含有3300个速率样本的DR导航系统。蓝线表示陀螺仪速率样本,红线表示累积角度误差。显然,累积角度误差随时间而变大。

图2. 使用ADXRS810评估板测得的速率。

(注:角度误差未按比例绘制。)

### 用低通滤波器(LPF)缩短积分时间

降低角度误差的传统方法将重点放在减小en上,但当今的数字陀螺仪的速率误差规格已处于非常低的水平。例如,ADXRS810的灵敏度为80 LSB/°/秒,失调为±2°/秒,抗冲击性为0.03°/秒/g,改善空间有限。另外,en的补偿算法非常复杂。与诸如电子稳定控制(ESC)等其他应用相比,DR导航系统中的陀螺仪可以长期运行,例如车辆行驶通过长隧道时GPS信号就不会丢失。在DR导航应用中,较长的运行时间会导致角度误差变大。

如果可以缩短积分时间,则可以显著降低累积角度误差。当陀螺仪不旋转时,速率输出较小,但因陀螺仪噪声的影响,输出不是零。ADXRS810具有超低的陀螺仪噪声和超高的灵敏度,只需设置相应的阈值,即可轻松过滤掉数字域中的噪声。这一过程等效于低通滤波,因为与旋转导致的速率输出相比,陀螺仪速率噪声处于高频区。

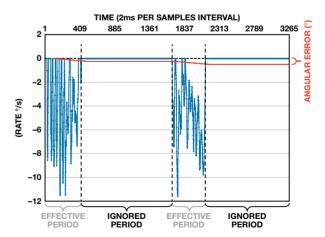

图3所示为图2的LPF版本,其中,小于1%的所有速率样本均归零处理,因此在速率积分时忽略不计。剩下的积分时间,被认为是有效积分时间,只相当于总积分时间的16%左右。如此可以大幅缩短积分时间。结果,累积角度误差也显著降低,如图中的红线所示。

图3. 使用ADXRS810评估板和数字LPF测得的速率。

(注:角度误差未按比例绘制。)

图4. 未经过滤的车载陀螺仪速率样本。

(注:角度误差未按比例绘制。)

在实际应用中,车辆方向盘一般位于零度处。因此,可以通过忽略来减少陀螺仪速率的有效积分时间,如图3所示实验中所做的那样。图4所示为来自真实车载测试的陀螺仪速率样本。在隧道中行驶大约180秒,则需要180秒的速率积分时间。如果不使用LPF过程,则180秒内累积的误差可能高达4°,该值太大,导致无法正确确定车辆在隧道中的位置。采用LPF过程,将阈值设为0.5°/秒,则有效积分时间缩短至84秒,减幅达53%左右。累积误差降至约0.5°,如图5所示。设置LPF阈值时,可以根据具体应用所需要的精度来定。

### 结论

如今的数字陀螺仪具有出色的规格特性,因此,其性能的提升余地有限。在车载DR导航系统以及要求长积分时间的其他应用中,通过设置LPF阈值来缩短积分时间是一种简单但有效的精度提升方法。

图5. 使用LPF后的车载陀螺仪速率样本。

(注:角度误差未按比例绘制。)

ADXRS810高性能、低成本数字陀螺仪采用ADI公司的新型MEMS技术,是车载DR导航应用的上佳选择。该陀螺仪采用超小型封装,具有低失调、低噪声和高速率灵敏度的特点。采用芯片集成温度补偿技术,无需使用外部温度传感器,同时简化了温度补偿算法。其超高的抗冲击和抗振动能力对汽车应用具有十分重要的意义。

### 作者简介

Ben Wang [ben.wang@analog.com], 是ADI公司中国深圳的现场应用工程师(FAE), 毕业于湖南大学。他于2009年6月加入ADI公司, 此前在National Semiconductor工作过六年。

(接第12页)

图9. SDP分线板连接AD7291评估板与Renesas评估板

在图9的示例设置中,SDP分线板的SPI引脚连线至Renesas RL78 评估板。Wiki知识库提供示例代码,用于多个元器件评估板,可通

过下列网站上单个产品页面的链接找到: www.analog.com或ADI Wiki上的微控制器示例部分。

欲获得有关SDP分线板的更多信息,包括原理图和订购信息,请访问:www.analog.com/EI3Breakout。该板零售价为49美元/片。

### 结论

从评估到原型制作的过程中,有很多选择有助于加快设计速度。ADI拥有专用硬件、可自定义硬件以及示例代码,提供一系列解决方案,满足各种需要。我们的系统演示平台正在不断演进中,因此我们鼓励您提供对您的设计过程帮助最大的原型制作硬件和软件反馈信息。

### 作者简介

Rosemary Ryan [rosemary.ryan@analog.com] 是应用技术团队的应用工程师。她2005年毕业于利 默里克大学,获计算机工程工学学士学位,2006年 加入利默里克ADI公司。2010年毕业于沃特福德理 工学院,获电子工程工学硕士学位。目前就职于精 密系统应用团队,负责系统演示平台(SDP)的开发。

# 如何设计并调试锁相环(PLL) 电路

作者: Ray Sun

### 简介

设计并调试锁相环(PLL)电路可能会很复杂,除非工程师深入了解 PLL理论以及逻辑开发过程。本文介绍PLL设计的简易方法,并提 供有效、符合逻辑的方法调试PLL问题。

### 仿真

如果不在特定条件下进行仿真,则估计一个PLL电路的规格将会是十分困难的。因此,进行PLL设计的第一步应当是仿真。我们建议工程师使用ADIsimPLL™软件运行基于系统要求的仿真,包括参考频率、步进频率、相位噪声(抖动)和频率杂散限制。

许多工程师面对如何选择参考频率会感到无所适从,但其实参考频率和输出频率步进之间的关系是很简单的。采用整数N分频PLL,则输出频率步进等于鉴频鉴相器(PFD)输入端的频率,该频率等于参考分频器R分频后的参考频率。采用小数N分频PLL,则输出频率步进等于PFD输入频率除以MOD值,因此,您可以使用较高的参考频率,获得较小的频率步进。决定使用整数N分频或是小数N分频时,可牺牲相位噪声性能换取频率步进,即:较低的PFD频率具有更好的输出频率分辨率,但相位噪声性能下降。

例如,表1显示若要求具有固定频率输出以及极大的频率步进,则应首选整数N分频PLL(如ADF4106),因为它具有更佳的总带内相位噪声。相反,若要求具有较小的频率步进,则应首选小数N分频PLL(如ADF4153),因为它的总噪声性能优于整数N分频PLL。相位噪声是一个基本的PLL规格,但数据手册无法针对所有可能的应用指定性能参数。因此,先仿真,然后进行实际硬件的测试就变得极为关键。

表1. 相位噪声确定PLL的选择

|         | 固定频率应用                                | GSM1800应用                            |

|---------|---------------------------------------|--------------------------------------|

|         | RF = 1.8 GHz,                         | RF = 1.8 GHz,                        |

|         | $f_{\rm osc}$ = 13 MHz,               | $f_{\rm osc} = 13 \text{ MHz},$      |

|         | 固定输出频率                                | $f_{\rm res} = 200 \text{ kHz}$      |

| ADF4106 | $FOM + 10\log f_{pfd} + 20\log N$     | $FOM + 10\log f_{pfd} + 20\log N$    |

| 整数N分频   | $= -223 + 10\log 13 \text{ MHz} +$    | $= -223 + 10\log 200 \text{ kHz}$    |

| PLL     | 20log 138 = -109 dBc/Hz               | $+ 20\log 9000 = -91 \text{ dBc/Hz}$ |

| ADF4153 | $FOM + 10\log f_{\rm pfd} + 20\log N$ | $FOM + 10\log f_{pfd} + 20\log N$    |

| 小数N分频   | = -220 + 10log 13 MHz +               | = -220 + 10log 13 MHz +              |

| PLL     | $20\log 138 = -106 \text{ dBc/Hz}$    | 20log 138 = -106 dBc/Hz              |

| 结果      | 使用整数N分频更佳                             | 使用小数N分频更佳                            |

甚至在真实条件下通过ADIsimPLL仿真PLL电路时,结果也可能是不够的,除非真实参考以及压控振荡器(VCO)的模型文件已包含在内。如果未包含在内,则仿真器将使用理想参考和VCO进行仿真。若要求高仿真精度,则花在编辑VCO和基准电压源库文件上的时间将会是值得的。

PLL使用与放大器类似的负反馈控制系统,因此环路带宽和相位裕量的概念此处依然适用。通常,环路带宽应设为PFD频率的十分之一以下,且相位裕量的安全范围为45°至60°。此外,应当进行针对真实电路板的仿真和原型制作,以便确认电路符合PCB布局对寄生元件、电阻容差和环路滤波器电容的规格要求。

有些情况下,暂时没有合适的电阻和电容值,因此工程师必须确定是否能使用其他值。在ADIsimPLL的"工具"菜单中隐藏了一项小功能,称为"BUILT"。该功能可将电阻和电容值转换为最接近的标准工程值,允许设计人员返回仿真界面,验证相位裕量和环路带宽的新数值。

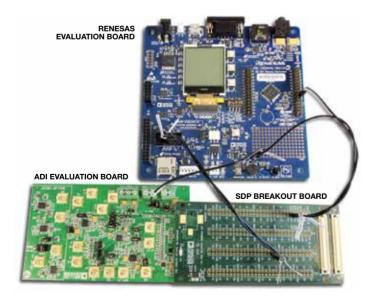

### 寄存器

ADI PLL提供很多用户可配置选项,具有灵活的设计环境,但也会产生如何确定存储在每个寄存器中数值的难题。一种方便的解决方案是使用评估软件设置寄存器值,甚至PCB未连接仿真器时也能这么做。然后,设置文件可保存为.stp文件,或下载至评估板中。图1显示ADIsimPLL仿真结果,提供诸如VCO内核电流等参数的建议寄存器值。

图1. ADIsimPLL仿真软件提供寄存器设置的建议值

### 原理图和PCB布局

设计完整PLL电路时,需牢记几点。首先,重要的是匹配PLL的参考输入端口阻抗,将反射降至最低。另外,保持电容与输入端口并 联组合值尽量小,因为它会降低输入信号的压摆率,增加PLL环路 噪声。更多详细信息请参考PLL数据手册上的输入要求。

其次,将模拟电源与数字电源相分离,最大程度减少它们之间的干扰。VCO电源特别敏感,因此此处的杂散和噪声可轻易耦合至PLL输出。更多注意事项以及详细信息,请参考利用低噪声LDO调节器为小数N分频压控振荡器(VCO)供源,以降低相位噪声(CN-0147)。

再则,用于组成环路滤波器的电阻和电容应当放置在尽可能离 PLL芯片近的地方,并使用仿真文件中的建议值。若您在改变环 路滤波器元器件值之后发现难以锁定信号,请尝试使用最初用于 评估板的数值。

对于PCB布局而言,其主要原则是将输入与输出分离,确保数字电路不会干扰模拟电路。例如,若SPI总线太过靠近参考输入或VCO输出,则访问PLL寄存器时,VCO输出会在PLL输出端产生杂散现象。

从热设计角度来看,可在PLL芯片底下放置一个导热接地焊盘,确保热量流经焊盘,到达PCB和散热片。在极端环境下使用时,设计人员应计算PLL芯片和PCB的所有热参数。

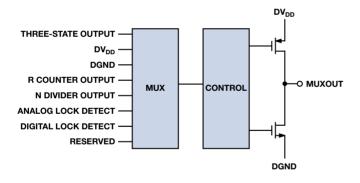

### 有效利用MUX0UT

在调试阶段开始时,若PLL不锁定,则很难确定应当从何处开始。第一步,可以使用MUXOUT查看是否所有内部功能单元都正常工作,如图2所示。例如,MUXOUT能显示R计数器输出,指示参考输入信号良好,且寄存器内容成功写入。MUXOUT还能检查检测器的锁定状态,以及反馈环路中的N分频输出。通过这种方法,设计人员可确定每个分频器、增益或频率值是否正确。这是调试PLL的基本过程。

图2. MUXOUT引脚辅助PLL进行调试

### 时域分析

调试PLL时,使用时域分析,演示写入串行外设接口(SPI)总线上的寄存器数据是正确的。虽然读写操作需要的时间比较长,但请确保SPI时序符合规格,且不同线路之间的串扰减小到最低程度。

应当参考PLL数据手册中的时序图,以便确定数据建立时间、时钟速度、脉冲宽度和其他规格。确保留有足够的裕量,以便在所有条件下都满足时序要求。使用示波器检查时域内的时钟和数据边沿位

于正确位置。若时钟和数据线路太过接近,则串扰会使时钟能量通过PCB布线耦合至数据线路。这种耦合会导致数据线路在时钟的上升沿产生毛刺。因此,读写寄存器时需检查这两条线路,尤其当寄存器出现错误时。确保线路电压满足表2的规格。

表2. 逻辑输入

|                                         | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------------------------------|-----|-----|-----|----|

| 输入高电压, V <sub>INH</sub>                 | 1.5 |     |     | V  |

| 输入低电压, V <sub>INL</sub>                 |     |     | 0.6 | V  |

| 输入电流,I <sub>INH</sub> /I <sub>INL</sub> |     |     | ±1  | μA |

| 输入电容,C <sub>IN</sub>                    |     | 3.0 |     | pF |

### 频谱分析

频域中的问题更常见、更复杂。如果使用频谱分析仪,则应当首 先检查PLL输出是否锁定;如果波形具有稳定的频率峰值则表示 锁定。如果未锁定,则应当遵循前文所述的步骤。

如果PLL已锁定,则收窄频谱分析仪带宽,以便确定相位噪声是否位于可接受范围内,并将测试结果与仿真结果对照确认。测量某些带宽条件下的相位噪声,如1 kHz、10 kHz和1 MHz。

若结果与预期不符,则应首先回顾环路滤波器设计,检查PCB板上 元器件的真实值。然后,检查参考输入的相位噪声是否与仿真结果 一致。PLL仿真相位噪声应与真实值接近,除非外部条件有所不同, 或向寄存器写入了错误值。

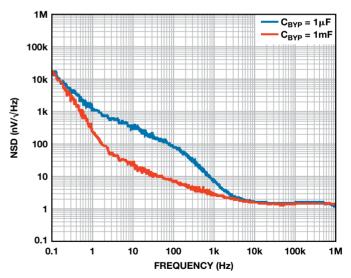

电源噪声不可忽略,哪怕使用了低噪声LDO;因为DC-DC转换器和LDO都可能成为噪声源。LDO数据手册显示的噪声频谱密度通常会影响噪声敏感型器件,比如PLL(见图3)。为PLL选择低噪声电源,特别是需要为VCO的内核电流提供电源。

图3. LDO噪声频谱密度

通常PLL的输出端会有四种类型的杂散: PFD或参考杂散、小数杂散、整数边界杂散以及外部来源杂散,如电源。所有PLL都至少有一种类型的杂散,虽然永远无法消除这些杂散,但某些情况下,在不同类型的杂散或频率之间进行取舍,可以改进整体性能。

若要避免参考杂散,请检查参考信号的上升沿。边沿过快或边沿幅度过大都会对频域造成严重的谐波现象。另外,仔细检查PCB布局,避免输入和输出之间产生串扰。

如需最大程度地减少小数杂散,可增加扰动,迫使小数杂散进入本 底噪声中,但这样做会略为增加本底噪声。

整数边界杂散不常见,且仅当输出频率过于接近参考频率的整数倍时才会发生,此时环路滤波器无法将其滤除。解决该问题的简便方法是重新调节参考频率方案。例如,若边界杂散发生在1100 MHz处,且输出为1100.1 MHz,参考输入为20 MHz,则使用100 kHz环路滤波器将参考频率改为30 MHz即可消除该杂散。

### 结论

调试PLL要求对PLL具有深入的理解,并且如果在设计阶段格外仔细,就能避免很多问题。若问题发生在调试阶段,请遵循本文所述之建议,对问题逐一进行分析并逐步解决问题。更多信息,请参考网站上的丰富信息资源: www.analog.com/pll。

### 参考文献

Curtin, Mike, and Paul O' Brien. "Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 1." *Analog Dialogue*, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O' Brien. "Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 2." *Analog Dialogue*, Volume 33, Number 1, 1999.

Curtin, Mike, and Paul O' Brien, "Phase-Locked Loops for High-Frequency Receivers and Transmitters—Part 3." *Analog Dialogue*, Volume 33, Number 1, 1999.

CN0147 Circuit Note. Powering a Fractional-N Voltage Controlled Oscillator (VCO) with Low Noise LDO Regulators for Reduced Phase Noise.

Fox, Adrian. "PLL Synthesizers (Ask the Applications Engineer—30)." *Analog Dialogue*, Volume 36, Number 3, 2002.

MT-086 Tutorial. Fundamentals of Phase-Locked Loops (PLLs).

### 作者简介

Ray Sun [ray.sun@analog.com] 2002年毕业于武汉技术大学并获得工程学士学位,于2009年加入ADI公司,并于2010年获得华中科技大学MBA学位。Ray目前担任中国武汉的现场应用工程师,为中国中部地区的客户提供支持。业余时间,Ray是

一名驯狗师、一名动物爱好者,以及武汉演讲会的创始人之一。

# 欢迎来到ADI在线购买中心

ADI官方网站已经开放中国大陆、中国香港及台湾地区在线购买服 务. 无论您是购买少量产品的工程师, 还是需要订购大批产品以满 足生产需求的采购人员,都可以利用ADI公司在线购买系统,实现 从设计到生产过程的各种产品订单管理。

- ✓ 原厂产品型号齐全

- ✓ 提供 配套评估板及开发套件 购买

- 部分产品 一片起订,报价依量而定,无最低金额要求

- ✓ 全球实时供货 快速送达, 您的电子邮件将会收到订单状态更新

输入产品型号或关键字 进入产品页面, 获取价格和供货信息

添加至购物车

✔ 完成结算

## ADI在线购买常见问题解答

- ▶ 如何查询产品价格及库存?

- 物流及订单进度跟踪

- ▶ 关于ADI官网的产品价格

- 运费、税费、支付及发票问题

- 请使用信用卡订购 (VISA, MasterCard, AMEX)

- 取消订单及退换货事官

更多帮助内容, 请在购买前详细阅读 >>

### 客户支持

- 申请myAnalog账户

- ▶ 查询订单状态

### 亚洲技术支持中心 4006-100-006

模拟与其他线性产品 china.support@analog.com

嵌入式处理与DSP产品 processor.china@analog.com 免费样片申请 www.analog.com/zh/sample ADI在线技术论坛 ezchina.analog.com

网址 www.analog.com/zh/CIC

点击在线提交客户服务表单

# 只要你开口没什么大不了 ADI官方中文技术论坛正式上线 发现精彩就在今天

- ✔ 全新的技术论坛

- ✔ 崭新的交流平台

- ✓ 高效的疑问解答

- ✓ 丰富的技术资料

- ✓ 专业的专家团队

ezchina.analog.com

# ADI参考设计精选

ADI高性能的硬件平台配合完整软件解决方案,最切合您的设计及应用需求。

由经验丰富的工程师组成的专家队伍更将协助您进行设计和研发。

- √ 完整用户手册

- √ 软件安装文件

- ✓ MCU固件文件

- ✓ 硬件原理图及PCB Layout

设计资源一应俱全, ADI免费提供下载。

www.analog.com/zh/RD

# Analog Devices, Inc. Worldwide Headquarters

One Technology Way P.O. Box 9106, Norwood, MA 02062-9106 U.S.A.

亚太区总部 上海市浦东新区张江高科技园区 祖冲之路 2290 号展想广场 5 楼 邮编: 201203 电话:(86 21) 2320 8000

传真: (86 21) 2320 8222

### 深圳分公司

深圳市福田中心区 益田路与福华三路交汇处 深圳国际商会中心 4205-4210 室 邮编: 518048

电话: (86 755) 8202 3200 传真: (86 755) 8202 3222

北京分公司 北京市海淀区 上地东路 5-2号 京蒙高科大厦5层

邮编: 100085 电话:(86 10) 5987 1000 传真: (86 10) 6298 3574

### 武汉分公司

湖北省武汉市东湖高新区 珞瑜路 889 号光谷国际广场 写字楼 B 座 2403-2405 室 邮编: 430073

电话: (86 27) 8715 9968 传真: (86 27) 8715 9931

**亚洲技术支持中心** 免费热线电话: 4006 100 006

电子邮箱: china.support@analog.com 技术专栏: www.analog.com/zh/CIC

样品申请: www.analog.com/zh/sample

在线购买:

www.analog.com/zh/BOL 在线技术论坛: ezchina.analog.com