# Analog Dialogue

A forum for the exchange of circuits, systems, and software for real-world signal processing

Volume 39, Number 3, 2005

#### In This Issue

| ditors' Notes                                                                                                          | . 2 |

|------------------------------------------------------------------------------------------------------------------------|-----|

| Practical Guide to High-Speed Printed-Circuit-Board Layout                                                             | . 3 |

| uthors and Product Introductions                                                                                       | . 9 |

| Oth Anniversary Timeline                                                                                               | 10  |

| Virect Digital Synthesis (DDS) Controls Waveforms in Test, Measurement, and Communications                             | 12  |

| ncoder's Spare Channel Embeds Whole-House Stereo Audio in Satellite<br>Set-Top-Box Designs Stably and Cost-Effectively | 16  |

www.analog.com/analogdialogue

#### **Editors' Notes**

#### 40TH ANNIVERSARY

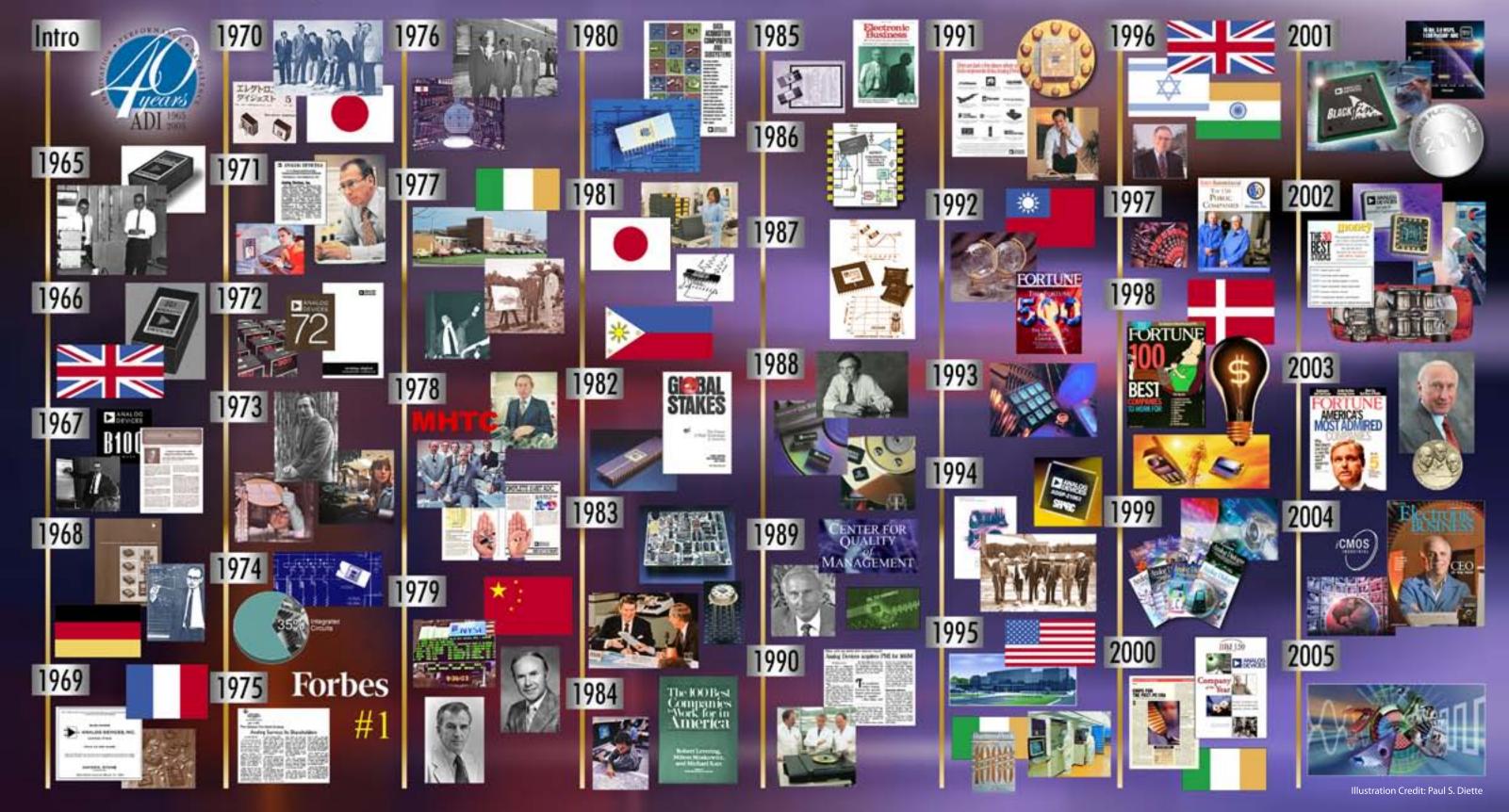

We're still celebrating the 40<sup>th</sup> anniversary of Analog Devices, Inc. Such events create a temptation to wax historical, and this is no exception. If you're interested in the high points of our history, the spread on pages 10-11 depicts the contents page of a timeline accessible on the Web (www.analog.com/timeline); in it you can click on any year to access a brief audiovisual clip reviewing that year's major corporate events.

As part of the celebration, we've devoted this year's four print issues to articles with principal technological focus on (1) digital, (2) conversion, (3) analog, and (4) sensors. This issue is devoted to articles discussing aspects of *analog* technology. As you will see, even digital phenomena are analog at the hardware level.

#### **RFI AGAIN-GONE!**

On multiple occasions, we've referred to—or had our attention called to—the dc offset problems caused by common-mode RF interference with low-frequency measurements, particularly as manifested by rectification in the input stages of instrumentation amplifiers.<sup>1,2,3</sup>

Our purpose for bringing this subject up again is to mention the availability, since July 2005, of a digitally programmable instrumentation amplifier that contains an intrinsic solution to the problem. The AD8556,<sup>4</sup> designed for automotive and industrial applications, features internal electromagnetic-interference (EMI) filtering; in addition, it has a very wide temperature range, low-offset voltage and drift, and open- and shorted-wire protection. It can provide a complete signal processing path from a bridge sensor to an A/D converter. Typical applications are with pressure sensors in anti-lock brake systems (ABS), occupant detection systems, fuel level sensors, transmission controls, and precision strain or pressure gauges.

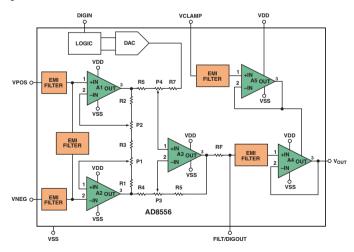

The figure below shows where the on-chip EMI filters are applied to protect the device's inputs: at the main differential inputs, at the *clamp* input, and at the input of the output amplifier. In brief, the problem that they solve is to filter out high frequencies before they reach the amplifier input junctions and create dc offsets through partial rectification.<sup>5</sup>

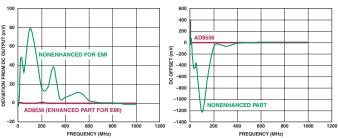

The effectiveness of this filtering scheme can be seen in the figures at the top of next column, comparing responses of the AD8556 and the AD8555, a similar device—but without internal EMI protection. The graph at left compares their dc responses to 200-mV common-mode high-frequency signals that drive both differential inputs (G = 70 mV/mV). The one at right measures dc output responses to 200-mV p-p of high-frequency sine waves driving VPOS, with VNEG grounded.

More about the AD8556: specified with  $10-\mu V$  max offset voltage, 65-nV/°C max offset drift, and 112-dB typical commonmode rejection, it features digitally programmable gain (from 70 mV/mV to 1280 mV/mV) and output-offset voltage, open- and short-circuited-wire fault detection, low-pass filtering, EMI filtering, and output voltage clamping. Output offset voltage can be adjusted with 0.39% resolution. Gain and offset can be temporarily programmed by the user and evaluated in-circuit, then permanently programmed by blowing polysilicon fuse links. The AD8556 operates on a single 2.7-V to 5.5-V supply and consumes 2 mA. Specified from  $-40^{\circ}$ C to  $+140^{\circ}$ C, it is available in 8-lead SOIC and 16-lead, 3-mm  $\times$  3-mm LFCSP packages.

Dan Sheingold [dan.sheingold@analog.com]

http://www.analog.com/library/analogdialogue/Anniversary/14.html Ask The Applications Engineer, Analog Devices

- http://www.analog.com/library/analogdialogue/Anniversary/contents.html

- <sup>2</sup> "A Reader Notes" http://www.analog.com/library/analogdialogue/Anniversary/ Reader\_Notes.html

- <sup>3</sup> H.R. Gelbach, "A Reader Notes: High-Frequency-Caused Errors in Millivolt Measurement Systems," *Analog Dialogue* 37-3, 2003, pp. 2, 14. http://www.analog.com/library/analogdialogue/archives/issues/vol37n3.pdf

<sup>5</sup> W. Jung, ed., "Op Amp Applications Handbook", Elsevier-Newnes, 2005, pp. 719-726. Similar material can be found online in the Analog Devices seminar version, http://www.analog.com/library/analogdialogue/archives/ 39-05/Web\_Ch7\_final\_J.pdf, pp. 7.122-7.129.

#### THE ANALOG WORLD

In mixed-signal systems, an analog-to-digital converter (ADC) translates real-world analog signals into the digital domain so that further signal processing can be implemented by the DSP or embedded processor. A digital-toanalog converter (DAC) then translates the digital signals back into the analog domain. At the start of the chain, and at the end of the day, the signals that we transmit, measure, and control are analog: audio, video,

temperature, pressure, voltage, and current, for instance.

Some amount of analog signal conditioning is always required before the ADC and after the DAC. Even functions that may at first appear to be digital are often analog at their very heart. Take phased-lock loops (PLLs), for example. These include phase detectors, filters, and oscillators—all analog functions. Direct digital synthesis (DDS) devices, on the other hand, are mostly digital, but they provide output signals whose properties are measured using analog quantities such as phase, frequency, and amplitude.

When designing analog circuitry—especially where high speed, high resolution, or low noise is required—a good printed-circuit board layout becomes increasingly important. Careful attention to voltage levels and signal flow can minimize the need for an expensive, time-consuming redesign, and can maintain optimum performance throughout the signal path.

With all this in mind, we invite you to read the "analog" installment of *Analog Dialogue*'s tribute to ADI's 40<sup>th</sup> anniversary. Here you will learn about adding stereo audio to a low-cost satellite set-top box; using DDS to generate waveforms for test, measurement, and communications; and avoiding the layout pitfalls inherent in high-speed amplifier designs. Enjoy!

*Scott Wayne* [scott.wayne@analog.com]

<sup>&</sup>lt;sup>1</sup> "Ask The Applications Engineer—14"

<sup>&</sup>lt;sup>4</sup> http://www.analog.com, Search <AD8556>

### A Practical Guide to High-Speed Printed-Circuit-Board Layout

#### By John Ardizzoni [john.ardizzoni@analog.com]

Despite its critical nature in high-speed circuitry, printed-circuitboard (PCB) layout is often one of the last steps in the design process. There are many aspects to high-speed PCB layout; volumes have been written on the subject. This article addresses high-speed layout from a practical perspective. A major aim is to help sensitize newcomers to the many and various considerations they need to address when designing board layouts for high-speed circuitry. But it is also intended as a refresher to benefit those who have been away from board layout for a while. Not every topic can be covered in detail in the space available here, but we address key areas that can have the greatest payoff in improving circuit performance, reducing design time, and minimizing timeconsuming revisions.

Although the focus is on circuits involving high-speed op amps, the topics and techniques discussed here are generally applicable to layout of most other high-speed analog circuits. When op amps operate at high RF frequencies, circuit performance is heavily dependent on the board layout. A high-performance circuit design that looks good "on paper" can render mediocre performance when hampered by a careless or sloppy layout. Thinking ahead and paying attention to salient details throughout the layout process will help ensure that the circuit performs as expected.

#### **The Schematic**

Although there is no guarantee, a good layout starts with a good schematic. Be thoughtful and generous when drawing a schematic, and think about signal flow through the circuit. A schematic that has a natural and steady flow from left to right will tend to have a good flow on the board as well. Put as much useful information on the schematic as possible. The designers, technicians, and engineers who will work on this job will be most appreciative, including us; at times we are asked by customers to help with a circuit because the designer is no longer there.

What kind of information belongs on a schematic besides the usual reference designators, power dissipations, and tolerances? Here are a few suggestions that can turn an ordinary schematic into a *superschematic!* Add waveforms, mechanical information about the housing or enclosure, trace lengths, keep-out areas; designate which components need to be on top of the board; include tuning information, component value ranges, thermal information, controlled impedance lines, notes, brief circuit operating descriptions ... (and the list goes on).

#### **Trust No One**

If you're not doing your own layout, be sure to set aside ample time to go through the design with the layout person. An ounce of prevention at this point is worth more than a pound of cure! Don't expect the layout person to be able to read your mind. Your inputs and guidance are most critical at the beginning of the layout process. The more information you can provide, and the more involved you are throughout the layout process, the better the board will turn out. Give the designer interim completion points—at which you want to be notified of the layout progress for a quick review. This "loop closure" prevents a layout from going too far astray and will minimize reworking the board layout.

Your instructions for the designer should include: a brief description of the circuit's functions; a sketch of the board that shows the input and output locations; the board *stack up* (i.e., how thick the board will be, how many layers, details of signal layers and planes—power,

ground, analog, digital, and RF); which signals need to be on each layer; where the critical components need to be located; the exact location of bypassing components; which traces are critical; which lines need to be controlled-impedance lines; which lines need to have matched lengths; component sizes; which traces need to kept away from (or near) each other; which *circuits* need to be kept away from (or near) each other; which *components* need to be close to (or away from) each other; which *components* go on the top and the bottom of the board. You'll never get a complaint for giving someone too much information—too *little*, yes; too much, no.

A learning experience: About 10 years ago I designed a multilayer surface-mounted board—with components on both sides of the board. The board was screwed into a gold-plated aluminum housing with many screws (because of a stringent vibration spec). Bias feedthrough pins poked up through the board. The pins were wire-bonded to the PCB. It was a complicated assembly. Some of the components on the board were to be *SAT* (set at test). But I hadn't specified where these components should be. Can you guess where some of them were placed? Right! On the bottom of the board. The production engineers and technicians were not very happy when they had to tear the assembly apart, set the values, and then reassemble everything. I didn't make that mistake again.

#### Location, Location, Location

As in real estate, location is everything. Where a circuit is placed on a board, where the individual circuit components are located, and what other circuits are in the neighborhood are all critical.

Typically, input-, output-, and power locations are defined, but what goes on between them is "up for grabs." This is where paying attention to the layout details will yield significant returns. Start with critical component placement, in terms of both individual circuits and the entire board. Specifying the critical component locations and signal routing paths from the beginning helps ensure that the design will work the way it's intended to. Getting it right the first time lowers cost and stress—and reduces cycle time.

#### **Power-Supply Bypassing**

Bypassing the power supply at the amplifier's supply terminals to minimize noise is a critical aspect of the PCB design process—both for high-speed op amps and any other high-speed circuitry. There are two commonly used configurations for bypassing high-speed op amps.

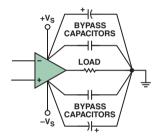

*Rails to ground:* This technique, which works best in most cases, uses multiple parallel capacitors connected from the op amp's power-supply pins directly to ground. Typically, two parallel capacitors are sufficient—but some circuits may benefit from additional capacitors in parallel.

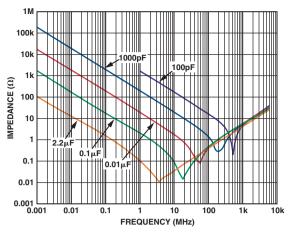

Paralleling different capacitor values helps ensure that the power supply pins see a low ac impedance across a wide band of frequencies. This is especially important at frequencies where the op amp *power-supply rejection* (PSR) is rolling off. The capacitors help compensate for the amplifier's decreasing PSR. Maintaining a low impedance path to ground for many decades of frequency will help ensure that unwanted noise doesn't find its way into the op amp. Figure 1 shows the benefits of multiple parallel capacitors. At lower frequencies the larger capacitors offer a low impedance path to ground. Once those capacitors reach self resonance, the capacitive quality diminishes and the capacitors become inductive. That is why it is important to use multiple capacitors: when one capacitor's frequency response is rolling off, another is becoming significant, thereby maintaining a low ac impedance over many decades of frequency.

Figure 1. Capacitor impedance vs. frequency.

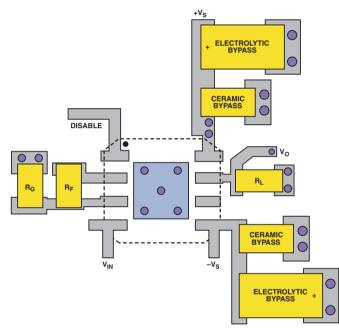

Starting directly at the op amp's power-supply pins; the capacitor with the lowest value and smallest physical size should be placed on the same side of the board as the op amp—and as close to the amplifier as possible. The ground side of the capacitor should be connected into the ground plane with minimal lead- or trace length. This ground connection should be as close as possible to the amplifier's load to minimize disturbances between the rails and ground. Figure 2 illustrates this technique.

Figure 2. Parallel-capacitor rails-to-ground bypassing.

This process should be repeated for the next-higher-value capacitor. A good place to start is with 0.01  $\mu$ F for the smallest value, and a 2.2- $\mu$ F—or larger—electrolytic with low ESR for the next capacitor. The 0.01  $\mu$ F in the 0508 case size offers low series inductance and excellent high-frequency performance.

*Rail to rail:* An alternate configuration uses one or more bypass capacitors tied between the positive- and negative supply rails of the op amp. This method is typically used when it is difficult to get all four capacitors in the circuit. A drawback to this approach is that the capacitor case size can become larger, because the voltage across the capacitor is double that of the single-supply bypassing method. The higher voltage requires a higher breakdown rating, which translates into a larger case size. This option can, however, offer improvements to both PSR and distortion performance.

Since each circuit and layout is different; the configuration, number, and values of the capacitors are determined by the actual circuit requirements.

#### **Parasitics**

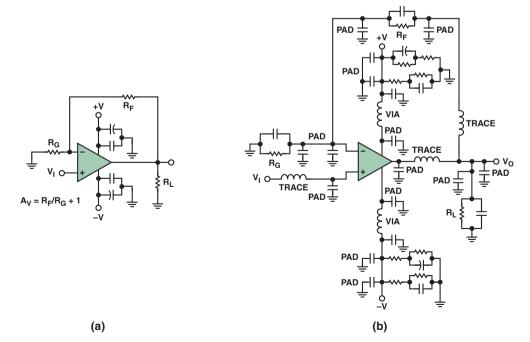

Parasitics are those nasty little gremlins that creep into your PCB (quite literally) and wreak havoc within your circuit. They are the hidden stray capacitors and inductors that infiltrate high-speed circuits. They include inductors formed by package leads and excess trace lengths; pad-to-ground, pad-to-power-plane, and pad-to-trace capacitors; interactions with vias, and many more possibilities. Figure 3(a) is a typical schematic of a noninverting op amp. If parasitic elements were to be taken into account, however, the same circuit would look like Figure 3(b).

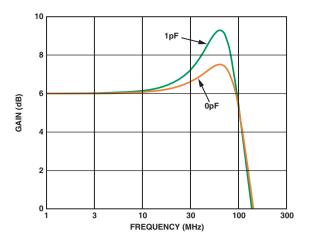

In high-speed circuits, it doesn't take much to influence circuit performance. Sometimes just a few tenths of a picofarad is enough. Case in point: if only 1 pF of additional stray parasitic capacitance is present at the inverting input, it can cause almost 2 dB of peaking in the frequency domain (Figure 4). If enough capacitance is present, it can cause instability and oscillations.

Figure 3. Typical op amp circuit, as designed (a) and with parasitics (b).

Figure 4. Additional peaking caused by parasitic capacitance.

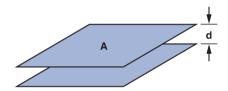

A few basic formulas for calculating the size of those gremlins can come in handy when seeking the sources of the problematic parasitics. Equation 1 is the formula for a parallel-plate capacitor (see Figure 5).

$$C = \frac{kA}{11.3d} \,\mathrm{pF} \tag{1}$$

C is the capacitance, A is the area of the plate in  $\text{cm}^2$ , k is the relative dielectric constant of board material, and d is the distance between the plates in centimeters.

Figure 5. Capacitance between two plates.

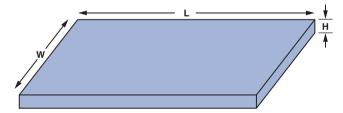

Strip inductance is another parasitic to be considered, resulting from excessive trace length and lack of ground plane. Equation 2 shows the formula for trace inductance. See Figure 6.

Inductance =

$$0.0002L \left[ ln \frac{2L}{(W+H)} + 0.2235 \left( \frac{W+H}{L} \right) + 0.5 \right] \mu H$$

(2)

W is the trace width, L is the trace length, and H is the thickness of the trace. All dimensions are in millimeters.

Figure 6. Inductance of a trace length.

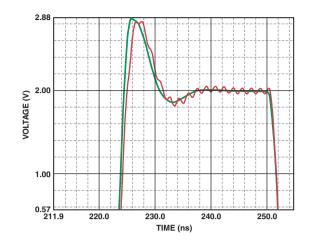

The oscillation in Figure 7 shows the effect of a 2.54-cm trace length at the noninverting input of a high-speed op amp. The equivalent stray inductance is 29 nH (nanohenry), enough to cause a sustained low-level oscillation that persists throughout the period of the transient response. The picture also shows how using a ground plane mitigates the effects of stray inductance.

Figure 7. Pulse response with—and without—ground plane.

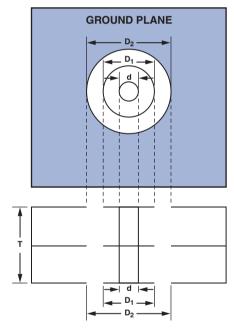

*Vias* are another source of parasitics; they can introduce both inductance and capacitance. Equation 3 is the formula for parasitic inductance (see Figure 8).

$$L = 2T \left[ \ln \frac{4T}{d} + 1 \right] n H$$

(3)

T is the thickness of the board and d is the diameter of the via in centimeters.

Figure 8. Via dimensions.

Equation 4 shows how to calculate the parasitic capacitance of a via (see Figure 8).

$$C = \frac{0.55\varepsilon_r T D_1}{D_2 - D_1} \mathrm{pF} \tag{4}$$

$\varepsilon_r$  is the relative permeability of the board material. *T* is the thickness of the board.  $D_1$  is the diameter of the pad surrounding the via.  $D_2$  is the diameter of the clearance hole in the ground plane. All dimensions are in centimeters. A single via in a 0.157-cm-thick board can add 1.2 nH of inductance and 0.5 pF of capacitance; this is why, when laying out boards, a constant vigil must be kept to minimize the infiltration of parasites!

#### **Ground Plane**

There is much more to discuss than can be covered here, but we'll highlight some of the key features and encourage the reader to pursue the subject in greater detail. A list of references appears at the end of this article.

A ground plane acts as a common reference voltage, provides shielding, enables heat dissipation, and reduces stray inductance (but it also increases parasitic capacitance). While there are many advantages to using a ground plane, care must be taken when implementing it, because there are limitations to what it can and cannot do.

Ideally, one layer of the PCB should be dedicated to serve as the ground plane. Best results will occur when the entire plane is unbroken. Resist the temptation to remove areas of the ground plane for routing other signals on this dedicated layer. The ground plane reduces trace inductance by magnetic-field cancellation between the conductor and the ground plane. When areas of the ground plane are removed, unexpected parasitic inductance can be introduced into the traces above or below the ground plane.

Because ground planes typically have large surface and crosssectional areas, the resistance in the ground plane is kept to a minimum. At low frequencies, current will take the path of least resistance, but at high frequencies current follows the path of least *impedance*.

Nevertheless, there are exceptions, and sometimes less ground plane is better. High-speed *op amps* will perform better if the ground plane is removed from under the input and output pads. The stray capacitance introduced by the ground plane at the input, added to the op amp's input capacitance, lowers the phase margin and can cause instability. As seen in the parasitics discussion, 1 pF of capacitance at an op amp's input can cause significant peaking. Capacitive loading at the output—including strays—creates a pole in the feedback loop. This can reduce phase margin and could cause the circuit to become unstable.

Analog and digital circuitry, including grounds and ground planes, should be kept separate when possible. Fast-rising edges create current spikes flowing in the ground plane. These fast current spikes create noise that can corrupt analog performance. Analog and digital grounds (and supplies) should be tied at one common ground point to minimize circulating digital and analog ground currents and noise.

At high frequencies, a phenomenon called *skin effect* must be considered. Skin effect causes currents to flow in the outer surfaces of a conductor—in effect making the conductor narrower, thus increasing the resistance from its dc value. While skin effect is beyond the scope of this article, a good approximation for the skin depth in copper, in centimeters, is

Skin Depth =

$$\frac{6.61}{\sqrt{f(\text{Hz})}}$$

(5)

Less susceptible plating metals can be helpful in reducing skin effect.

#### Packaging

Op amps are typically offered in a variety of packages. The package chosen can affect an amplifier's high-frequency performance. The main influences are parasitics (mentioned earlier) and *signal routing*. Here we will focus on routing inputs, outputs, and power to the amplifier.

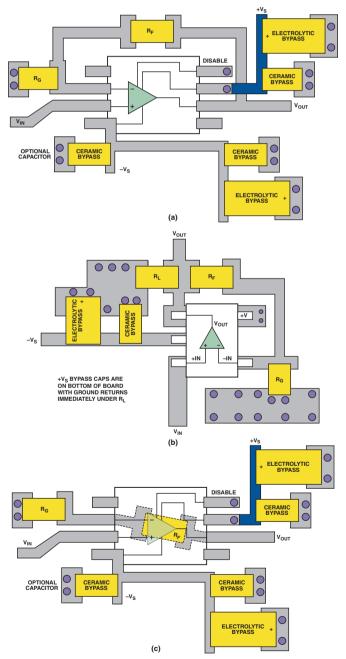

Figure 9 illustrates the layout differences between an op amp in an SOIC package (a) and one in an SOT-23 package (b). Each

package type presents its own set of challenges. Focusing on (a), close examination of the feedback path suggests that there are multiple options for routing the feedback. Keeping trace lengths short is paramount. Parasitic inductance in the feedback can cause ringing and overshoot. In Figures 9(a) and 9(b), the feedback path is routed around the amplifier. Figure 9(c) shows an alternative approach—routing the feedback path under the SOIC package—which minimizes the feedback path length. Each option has subtle differences. The first option can lead to excess trace length, with increased series inductance. The second option uses vias, which can introduce parasitic capacitance and inductance. The influence and implications of these parasitics must be taken into consideration when laying out the board. The SOT-23 layout is almost ideal: minimal feedback trace length and use of vias; the load and bypass capacitors are returned with short paths to the same ground connection; and the positive rail capacitors, not shown in Figure 9(b), are located directly under the negative rail capacitors on the bottom of the board.

Figure 9. Layout differences for an op amp circuit. (a) SOIC package, (b) SOT-23, and (c) SOIC with  $R_F$  underneath board.

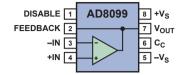

Low-distortion amplifier pinout: A new low-distortion pinout, available in some Analog Devices op amps (the AD8045,<sup>1</sup> for example), helps eliminate both of the previously mentioned problems; and it improves performance in two other important areas as well. The LFCSP's low-distortion pinout, as shown in Figure 10, takes the traditional op amp pinout, rotates it counterclockwise by one pin and adds a second output pin that serves as a dedicated feedback pin.

Figure 10. Op amp with low-distortion pinout.

The low-distortion pinout permits a close connection between the output (the dedicated feedback pin) and the inverting input, as shown in Figure 11. This greatly simplifies and streamlines the layout.

Figure 11. PCB layout for AD8045 low-distortion op amp.

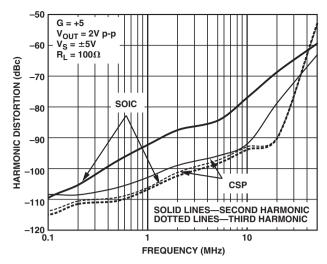

Another benefit is decreased second-harmonic distortion. One cause of second-harmonic distortion in conventional op amp pin configurations is the coupling between the noninverting input and the negative supply pin. The low-distortion pinout for the LFCSP package eliminates this coupling and greatly reduces second-harmonic distortion; in some cases the reduction can be as much as 14 dB. Figure 12 shows the difference in distortion performance between the AD8099<sup>2</sup> SOIC and the LFCSP package.

This package has yet another advantage—in power dissipation. The LFCSP provides an exposed paddle, which lowers the thermal resistance of the package and can improve  $\theta_{JA}$  by approximately 40%. With its lower thermal resistance, the device runs cooler, which translates into higher reliability.

Figure 12. AD8099 distortion comparison—the same op amp in SOIC and LFCSP packages.

At present, three Analog Devices high-speed op amps are available with the new low-distortion pinout: AD8045, AD8099, and AD8000.<sup>3</sup>

#### **Routing and Shielding**

A wide variety of analog and digital signals, with high- and low voltages and currents, ranging from dc to GHz, exists on circuit boards. Keeping signals from interfering with one another can be difficult.

Recalling the advice to "trust no one," it is critical to think ahead and come up with a plan for how the signals will be processed on the board. It is important to note which signals are sensitive and to determine what steps must be taken to maintain their integrity. Ground planes provide a common reference point for electrical signals, and they can also be used for shielding. When signal isolation is required, the first step should be to provide physical distance between the signal traces. Here are some good practices to observe:

- Minimizing long parallel runs and close proximity of signal traces on the same board will reduce inductive coupling.

- Minimizing long traces on adjacent layers will prevent capacitive coupling.

- Signal traces requiring high isolation should be routed on separate layers and—if they cannot be totally distanced—should run orthogonally to one another with ground plane in between. Orthogonal routing will minimize capacitive coupling, and the ground will form an electrical shield. This technique is exploited in the formation of *controlled-impedance* lines.

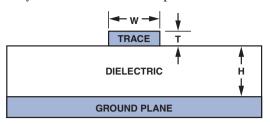

High-frequency (RF) signals are typically run on controlledimpedance lines. That is, the trace maintains a characteristic impedance, such as 50  $\Omega$  (typical in RF applications). Two common types of controlled-impedance lines, *microstrip*<sup>4</sup> and *stripline*<sup>5</sup> can both yield similar results, but with different implementations. A microstrip controlled-impedance line, shown in Figure 13, can be run on either side of a board; it uses the ground plane immediately beneath it as a reference plane.

Figure 13. A microstrip transmission line.

Equation 6 can be used to calculate the characteristic impedance for an FR4 board.

$$Z_{0} = \frac{87}{\sqrt{\varepsilon_{r}} + 1.41} \ln \left[ \frac{5.98H}{(0.8W + T)} \right]$$

(6)

*H* is the distance in from the ground plane to the signal trace, *W* is the trace width, *T* is the trace thickness; all dimensions are in mils (inches  $\times 10^{-3}$ ).  $\varepsilon_r$  is the dielectric constant of the PCB material.

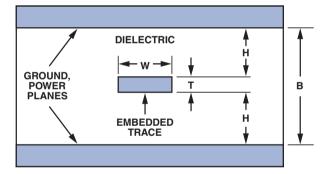

Stripline controlled-impedance lines (see Figure 14) use two layers of ground plane, with signal trace sandwiched between them. This approach uses more traces, requires more board layers, is sensitive to dielectric thickness variations, and costs more—so it is typically used only in demanding applications.

Figure 14. Stripline controlled-impedance line.

The characteristic-impedance design equation for stripline is shown in Equation 7.

$$Z_0(\Omega) = \frac{60}{\sqrt{\varepsilon_r}} \ln \left[ \frac{1.9(B)}{\left( 0.8W + T \right)} \right]$$

(7)

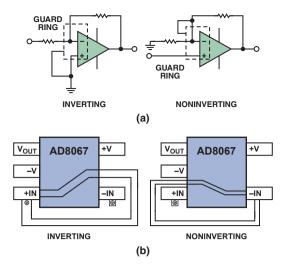

Guard rings, or "guarding," is another common type of shielding used with op amps; it is used to prevent stray currents from entering sensitive nodes. The principle is straightforward—completely surround the sensitive node with a guard conductor that is kept at, or driven to (at low impedance) the same potential as the sensitive node, and thus sinks stray currents away from the sensitive node. Figure 15(a) shows the guard ring schematics for inverting and noninverting op amp configurations. Figure 15(b) shows a typical implementation of both guard rings for a SOT-23-5 package.

Figure 15. Guard rings. (a) Inverting and noninverting operation. (b) SOT-23-5 package.

There are many other options for shielding and routing. The reader is encouraged to review the references below for more information on this and other topics mentioned above.

#### CONCLUSION

Intelligent circuit-board layout is important to successful op amp circuit design, especially for high-speed circuits. A good schematic is the foundation for a good layout; and close coordination between the circuit designer and the layout designer is essential, especially in regard to the location of parts and wiring. Topics to consider include power-supply bypassing, minimizing parasitics, use of ground planes, the effects of op amp packaging, and methods of routing and shielding.

#### FOR FURTHER READING

Ardizzoni, John, "Keep High-Speed Circuit-Board Layout on Track," *EE Times*, May 23, 2005.

Brokaw, Paul, "An IC Amplifier User's Guide to Decoupling, Grounding, and Making Things Go Right for a Change," Analog Devices Application Note AN-202.

Brokaw, Paul and Jeff Barrow, "Grounding for Low- and High-Frequency Circuits," Analog Devices Application Note AN-345.

Buxton, Joe, "Careful Design Tames High-Speed Op Amps," Analog Devices Application Note AN-257.

DiSanto, Greg, "Proper PC-Board Layout Improves Dynamic Range," *EDN*, November 11, 2004.

Grant, Doug and Scott Wurcer, "Avoiding Passive-Component Pitfalls," Analog Devices Application Note AN-348.

Johnson, Howard W. and Martin Graham, *High-Speed Digital Design*, a Handbook of Black Magic, Prentice Hall, 1993.

Jung, Walt, ed., Op Amp Applications Handbook, Elsevier-Newnes, 2005.

#### **REFERENCES-VALID AS OF NOVEMBER 2005**

- <sup>1</sup> ADI website: www.analog.com (Search) AD8045 (Go)

- <sup>2</sup> ADI website: www.analog.com (Search) AD8099 (Go)

- <sup>3</sup> ADI website: www.analog.com (Search) AD8000 (Go)

- <sup>4</sup> http://www.microwaves101.com/encyclopedia/microstrip.cfm

- <sup>5</sup> http://www.microwaves101.com/encyclopedia/stripline.cfm

#### **PRODUCT INTRODUCTIONS: VOLUME 39, NUMBER 3**

Data sheets for all ADI products can be found by entering the model number in the Search Box at www.analog.com

#### July

| Accelerometer, ±2-g, dual-axis, 16-lead LFCSP package ADXL322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amplifier, Digitally Programmable, includes EMI filters AD8556                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Controller, TFT-LCD panels ADD8754                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detector, TruPwr <sup>™</sup> , dual, LF to 2.7 GHz,<br>60-dB dynamic range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Encoder, multichannel television sound (MTS) AD1970                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Level Translator, 8-channel, bidirectional,<br>1.15 V to 5.5 V operation ADG3300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <b>Switches</b> , CMOS SPST, 0.28-Ω, SC70 package,<br>1.65-V to 3.6-V operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Transceiver, FSK/ASK, ISM band                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| August                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Accelerometer, ±1.7-g dual-axis, precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Amplifier, Transimpedance, 4.25-Gbps, 3.3-V operation ADN2882                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Codec, SoundMAX <sup>®</sup> Audio, AC '97 and HD interfaces AD1986A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Converter, Impedance-to-Digital, 12-bit, 250-kSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Laser-Diode Driver, 50-Mbps to 4.25-Gbps, single-loop ADN2871                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Supervisory Watchdog Circuits, low-voltage,<br>4-lead SC70 package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4-lead SC/0 package ADM8010/ADM801/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| September                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ADC, 12-bit, 400-MSPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| ADCs, Successive-Approximation,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12-/10-/8-bit, 3-MSPS AD7276/AD7277/AD7278                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ADC, Successive-Approximation, 14-bit, 500-kSPS AD7946                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Amplifier, Difference, 42-V compatible, 5-V operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Amplifier, Operational, dual, low-noise, precision CMOS AD8656                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Amplifier, Transimpedance, low-noise, 3.2-Gbps,<br>3.3-V operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Codec, SoundMAX Audio, HD Audio 1.0-compliant AD1981HD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Controller, GSM Power Amplifier, 50-dB dynamic range AD8311                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DAC, 14-bit, 32-channel, 50-V-to-200-V output-voltage range AD5535                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Detector, TruPwr, 100-MHz to 6-GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Direct Digital Synthesizer, 4-channel, 10-bit, 500-MSPS AD9959                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Filter, Video, triple, 2-input, with selectable gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| and cutoff frequencies, RGB, HD, SD ADA4411-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Filter, Video, triple, with selectable cutoff frequencies,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Filter, Video, triple, with selectable cutoff frequencies,         RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Filter, Video, triple, with selectable cutoff frequencies,         RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Filter, Video, triple, with selectable cutoff frequencies,         RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature       ADT7466/ADT7476                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADUM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSEET Drivers dual 12-V high-side bootstrap                                                                                                                                                                                                                                                                                                                                                                          |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSEET Drivers dual 12-V high-side bootstrap                                                                                                                                                                                                                                                                                                                                                                          |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disable       ADP3110/ADP3120         Multiplexer, iCMOS <sup>™</sup> , 4:1, low-capacitance,       ADP3110/ADP3120                                                                                                                                                                                                                                   |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disable       ADP3110/ADP3120         Multiplexer, iCMOS <sup>™</sup> , 4:1, low-capacitance,       ADP3110/ADP3120                                                                                                                                                                                                                                   |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADuM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSEET Drivers dual 12-V high-side bootstrap                                                                                                                                                                                                                                                                                                                                                                          |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADUM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disable       ADP3110/ADP3120         Multiplexer, iCMOS <sup>™</sup> , 4:1, low-capacitance,<br>low-charge-injection       ADG1204                                                                                                                                                                                                                   |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADUM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disable       ADP3110/ADP3120         Multiplexer, iCMOS <sup>™</sup> , 4:1, low-capacitance,<br>low-charge-injection       ADG1204         Supervisory Circuit, microprocessor       ADM6384         Switch, CMOS, dual, DPDT, 0.4-Ω       ADG888                                                                                                    |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SD       ADA4412-3         Isolator, Digital, 2-channel       ADUM1210         Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channel       ADT7466/ADT7476         Monitor-Controllers, Temperature<br>and Fan Speed       ADT7473/ADT7475         MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disable       ADP3110/ADP3120         Multiplexer, iCMOS <sup>™</sup> , 4:1, low-capacitance,<br>low-charge-injection       ADG1204         Supervisory Circuit, microprocessor       ADM6384         Switch, CMOS, dual, DPDT, 0.4-Ω       ADG888         Switches, iCMOS, quad SPST, low-capacitance,       ADG888                                  |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SDRGB, HD, SDADA4412-3Isolator, Digital, 2-channelADUM1210Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channelADT7466/ADT7476Monitor-Controllers, Temperature<br>and Fan SpeedADT7473/ADT7475MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADT7473/ADT7475Multiplexer, iCMOS<br>Supervisory Circuit, microprocessorADB3110/ADP3120Switch, CMOS, dual, DPDT, 0.4-ΩADG8888Switches, iCMOS, quad SPST, low-capacitance,<br>low-charge-injectionADG2121/ADG1212/ADG1213Switch/Wultiplexer, CMOSSPDT/211Switch/WultiplexerCMOSSwitch/WultiplexerCMOSSwitch/WultiplexerCMOSSwitch/WultiplexerSpDT/21113-0Switch/Wultiplexer                          |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SDRGB, HD, SDADA4412-3Isolator, Digital, 2-channelADUM1210Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channelADT7466/ADT7476Monitor-Controllers, Temperature<br>and Fan SpeedADT7473/ADT7475MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADT7473/ADT7475Multiplexer, iCMOS<br>Supervisory Circuit, microprocessorADB3110/ADP3120Switch, CMOS, dual, DPDT, 0.4-ΩADG8888Switches, iCMOS, quad SPST, low-capacitance,<br>low-charge-injectionADG2121/ADG1212/ADG1213Switch/Wultiplexer, CMOSSPDT/211Switch/WultiplexerCMOSSwitch/WultiplexerCMOSSwitch/WultiplexerCMOSSwitch/WultiplexerSpDT/21113-0Switch/Wultiplexer                          |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SDADA4412-3Isolator, Digital, 2-channelADUM1210Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channelADT7466/ADT7476Monitor-Controllers, Temperature<br>and Fan SpeedADT7466/ADT7476MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADT7473/ADT7475MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADG1204Supervisory Circuit, microprocessorADM6384Switch, CMOS, dual, DPDT, 0.4- $\Omega$ ADG888Switches, iCMOS, quad SPST, low-capacitance,<br>low-charge-injectionADG1211/ADG1212/ADG1213Switch/Multiplexer, CMOS, SPDT/2:1, 1.3- $\Omega$ ,<br>1.8-V to 5.5-V operationADG859Temperature Sensor, digital, local.ADG859 |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SDADA4412-3Isolator, Digital, 2-channelADUM1210Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channelADT7466/ADT7476Monitor-Controllers, Temperature<br>and Fan SpeedADT7466/ADT7476MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADT7473/ADT7475MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADG1204Supervisory Circuit, microprocessorADM6384Switch, CMOS, dual, DPDT, 0.4- $\Omega$ ADG888Switches, iCMOS, quad SPST, low-capacitance,<br>low-charge-injectionADG1211/ADG1212/ADG1213Switch/Multiplexer, CMOS, SPDT/2:1, 1.3- $\Omega$ ,<br>1.8-V to 5.5-V operationADG859Temperature Sensor, digital, local.ADG859 |

| Filter, Video, triple, with selectable cutoff frequencies,<br>RGB, HD, SDADA4412-3Isolator, Digital, 2-channelADuM1210Monitor-Controllers, Temperature- and Voltage,<br>2-channel /5-channelADT7466/ADT7476Monitor-Controllers, Temperature<br>and Fan SpeedADT7473/ADT7475MOSFET Drivers, dual, 12-V, high-side bootstrap,<br>with output disableADD7110/ADP3120Multiplexer, iCMOS <sup>TM</sup> , 4:1, low-capacitance,<br>low-charge-injectionADG1204Switches, iCMOS, quad SPST, low-capacitance,<br>low-charge-injectionADG1211/ADG1212/ADG1213Switch/Multiplexer, CMOS, SPDT/2:1, 1.3- $\Omega$ ,<br>1.8-V to 5.5-V operationADG859                                                                                                                         |

#### Analog Dialogue

www.analog.com/analogdialogue dialogue.editor@analog.com Analog Dialogue is the free technical magazine of Analog Devices, Inc., published continuously for 39 years—starting in 1967. It discusses products, applications, technology, and techniques for analog, digital, and mixed-signal processing. It is currently published in two editions—online, monthly at the above URL, and quarterly in print, as periodic retrospective collections of articles that have appeared online. In addition to technical articles, the online edition has timely announcements, linking to data sheets of newly released and pre-release products, and "Potpourri"—a universe of links to important and rapidly proliferating sources of relevant information and activity on the Analog Devices website and elsewhere. The Analog Dialogue site is, in effect, a "high-pass-filtered" point of entry to the www.analog.com site—the virtual world of Analog Devices. In addition to all its current information, the Analog Dialogue site has archives with all recent editions, starting from Volume 29, Number 2 (1995), plus three special anniversary issues, containing useful articles extracted from earlier editions, going all the way back to Volume 1, Number 1.

If you wish to subscribe to—or receive copies of—the print edition, please go to www.analog.com/analogdialogue and click on <subscribe>. Your comments are always welcome; please send messages to dialogue.editor@analog.com or to these individuals: Dan Sheingold, Editor [dan.sheingold@analog.com] or Scott Wayne, Managing Editor and Publisher [scott.wayne@analog.com].

#### **AUTHORS**

**John Ardizzoni** (page 3) is an applications engineer with Analog Devices in the High-Speed Amplifier group. John graduated from Merrimack College in 1988 and joined Analog Devices in 2002. Prior to that, he worked for IBM as an applications engineer and M/A-COM as a design engineer.

Victor Chang (page 16), now a systems engineer at Raytheon Company, worked in the Central Applications group at Analog Devices in Wilmington, MA for five years. He has an MSEE from the University of Massachusetts, Lowell, and a BSEECS from the University of California, Berkeley. In addition to providing customer support for linearand converter products, Victor worked

to develop interactive Web tools to aid designers. In his spare time, he enjoys basketball, snowboarding, and traveling.

Jeritt Kent (page 16) is a senior linear field applications engineer for Analog Devices in Bellevue, Washington. He joined ADI in 1999 from Allegro Microsystems and has written articles on various engineering topics. Before 1997 he was employed at American Microsystems as a mixed-signal design engineer, specializing in CMOS. One of Jeritt's key projects was an 8-channel injector-driver ASIC for natural-gas-

powered vehicles. He has both an MEng in EE and a BSEE from the University of Idaho, Moscow.

**Eva Murphy** (page 12) is an applications engineer at ADI's facility in Limerick, Ireland. She provides applications support for general-purpose, digital-toanalog converters (DACs), switches and multiplexers, and direct-digital-synthesis (DDS) products. Joining Analog Devices in 2000, Eva holds a BEng from Cork Institute of Technology. Her interests include reading, traveling, and walking.

**Colm Slattery** (page 12) graduated in 1995 from the University of Limerick, Ireland, with a bachelor's degree in electronic engineering. After working at Microsemi in test-development engineering, he joined ADI in 1998 as a test-development engineer. He later (2001) moved to applications in the precision-data-converter product line.

## Interactive Corporate Timeline

This is a reproduction of the gateway to our 40th anniversary corporate timeline, available at www.analog.com/timeline. At that site, clicking on any year will illustrate—and tell you about—significant corporate events of that year.

Share your favorite memory of ADI by sending an email to 40thanniversary@analog.com.

#### Direct Digital Synthesis (DDS) Controls Waveforms in Test, Measurement, and Communications

By Eva Murphy [eva.murphy@analog.com] Colm Slattery [colm.slattery@analog.com]

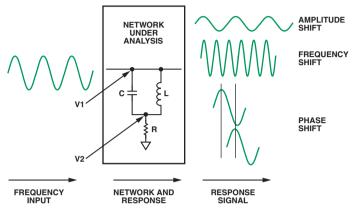

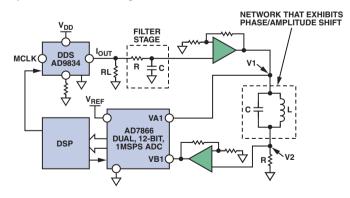

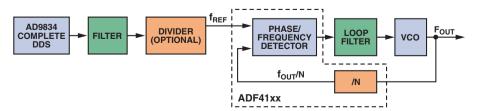

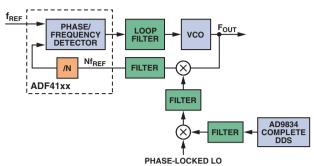

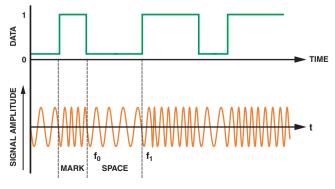

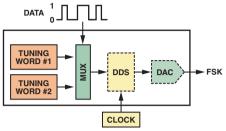

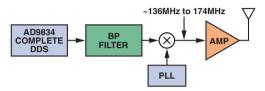

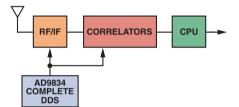

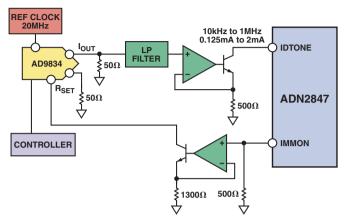

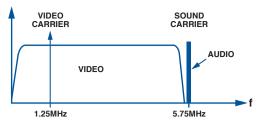

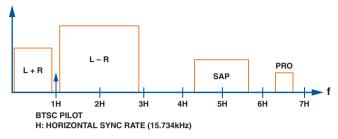

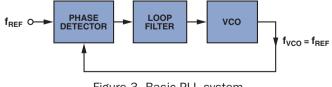

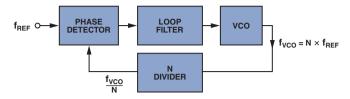

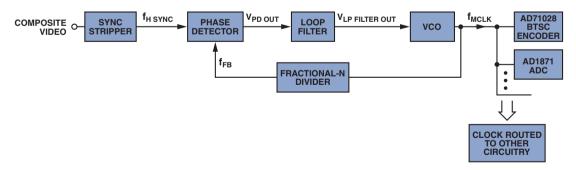

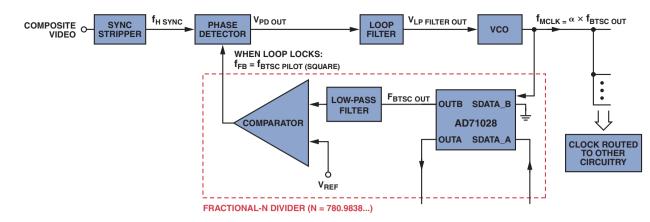

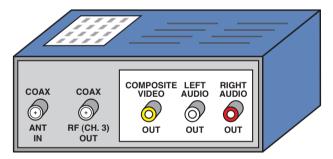

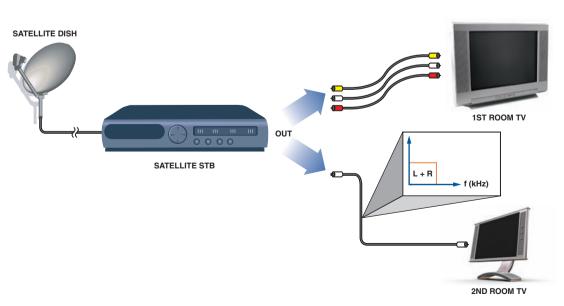

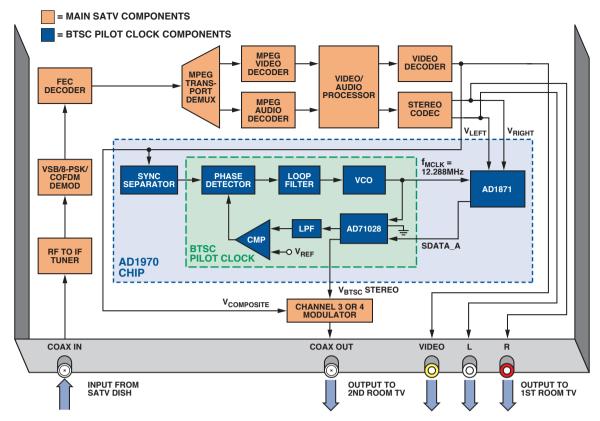

In many kinds of equipment, it is important to produce and readily control accurate waveforms of various frequencies and profiles. Examples include agile frequency sources with low phase noise and low spurious signal content for communications, and simply generated frequency stimuli for industrial and biomedical applications. In such applications, the ability to generate an adjustable waveform conveniently and cost effectively is a key design consideration.