# ADI 技术指南合集第一版第一版电路仿真和 PCB 设计

# 目录

| EMI、RFI 和屏蔽概念        | 1  |

|----------------------|----|

| RFI 整流原理             | 17 |

| 低电压逻辑接口              | 27 |

| 去耦技术                 | 41 |

| 实现数据转换器的接地并解开"AGND"和 |    |

| "DGND"的谜团            | 55 |

| 工程经理初次使用 Multisim    | 72 |

| 微带和带线设计    | 76  |

|------------|-----|

| 散热设计基础     | 83  |

| 模拟电路仿真     | 96  |

| 试验板和原型制作技术 | 111 |

| 静电放电 (ESD) | 126 |

| 高速逻辑的外理    | 135 |

# EMI、RFI和屏蔽概念

# 电磁兼容性(EMC)简介

模拟电路性能常常会因附近电气活动产生的高频信号而受到不利影响。此外,内置模拟电路的设备也可能对其外部的系统产生不利影响。参考文献1(第4页)根据IEC-60050定义给出了"电磁兼容性(EMC)"定义:

EMC是指器件、整套设备或系统在电磁环境下保持良好性能且不会向该环境中的任何器件、设备或系统引入大量电磁干扰的能力。

因此,术语"EMC"描述以下两个方面:

- 1. 电气电子系统保持正常工作且不干扰其它系统的能力。

- 2. 此类系统在额定电磁环境中按预期工作的能力。

因此,完整的EMC保证将会表明:设计中的设备应该既不会产生杂散信号,也不易受带外外部信号(即目标频率范围之外的那些信号)影响。模拟设备多数时候深受后一类EMC问题之害。此部分将重点介绍如何恰当处理这类杂散信号。

外部产生的电气活动可能产生噪声,这种噪声称为"电磁干扰(EMI)"或"射频干扰(RFI)"。 下面将从电磁干扰和射频干扰两个方面探讨EMI。对模拟设计人员来说,较具挑战性的任 务之一就是合理控制设备,防止出现因EMI而造成的不良操作。必须注意,这种情况下, EMI和/或RFI通常都是有害的。一旦进入设备内部,它既能够也会造成设备性能下降,而 且通常影响相当大。

此部分将着重介绍如何最大程度地减少因收到EMI/RFI信号而导致的不良模拟电路操作。 此类不良行为也称为"EMI或RFI敏感度",指示设备暴露于EMI/RFI时出现异常行为的倾 向。当然还有互补EMC问题,即关于杂散"辐射"。不过,与高速逻辑等相比,模拟电路通 常较少涉及到脉冲驱动的高速、高电流信号边沿(即产生此类杂散信号的信号边沿),所以 此处并未重点介绍EMC的这一方面。但无论如何,读者应当注意,这点可能很重要,尤其 是模拟电路与高速逻辑一起共同构成混合信号环境时。 由于所有这些EMC设计重点都至关重要,因此强烈建议各位读者补充阅读教程结尾部分的参考文献。实际上,为了实现针对EMI、RFI和EMC周密完善的设计,设计人员需要非常熟悉这些参考文献中的一个或多个(参见参考文献1-6)。这项课题范围极其广阔,现在也变得越来越重要,以下材料仅为其简介。

## EMI/RFI机制

要了解并合理控制EMI和RFI,首先需要将其分离成便于管理的各部分。因此,请记住,当确实出现EMI/RFI问题时,基本上都可以将其分成"来源"、"路径"和"接收器"几部分,这点非常有用。系统设计人员可以直接控制其中的接收器部分,同时还可能控制部分路径。但是,设计人员几乎不可能控制实际来源。

## EMI噪声源

干扰噪声总是可以通过这样或那样的方式耦合至模拟电路,从而破坏电路精度。这样的噪声源有很多,图1列出了其中一些。

- ♦ EMI/RFI noise sources can couple from anywhere

- ♦ Some common sources of externally generated noise:

- Radio and TV Broadcasts

- Mobile Radio Communications

- Cellular Telephones

- Vehicular Ignition

- Lightning

- Utility Power Lines

- Electric Motors

- Computers

- Garage Door Openers

- Telemetry Equipment

#### 图1:一些常见的EMI噪声源

由于几乎不可能控制这些EMI来源,那么退而求其次,就是发现和了解EMI耦合至设计中设备的可能路径。

# EMI耦合路径

EMI耦合路径实际上寥寥无几,最常见的三种路径如下:

- 1. 因传导而产生的干扰(公共阻抗)

- 2. 因容性或感性耦合而产生的干扰(近场干扰)

- 3. 电磁辐射(远场干扰)

## 噪声耦合机制

只要系统中存在阻抗不匹配或不连续,EMI能量就可能进入系统。一般而言,这种情况发生在接口处(即承载敏感模拟信号的电缆连接到PCB,并通过电源引脚的地方)。电缆连接不当或电源滤波方案不佳通常都是干扰滋生的"完美温床"。

当两个或以上的电流共享公共路径(阻抗)时,也可能会产生传导噪声。这种公共路径通常为高阻抗"接地"连接。如果两个电路共享此路径,那么一个电路的噪声电流就会在另一电路中产生噪声电压。这种潜在干扰源可以通过几个步骤来识别(参见参考文献1和2,以及教程MT-031)。

图2所示为噪声从外部来源进入电路的一些常见方式。

- Impedance mismatches and discontinuities

- **♦** Common-mode impedance mismatches → Differential Signals

- Capacitively Coupled (Electric Field Interference)

- dV/dt → Mutual Capacitance → Noise Current (Example: 1V/ns produces 1mA/pF)

- Inductively Coupled (Magnetic Field)

- di/dt → Mutual Inductance → Noise Voltage (Example: 1mA/ns produces 1mV/nH)

#### 图2: EMI如何进入设备

以电介质(空气、真空以及所有固态或液态绝缘体都属于电介质)隔开的任何两条导线之间都存在电容。如果一条导线上的电压发生变化,则另一导线上的电荷就会发生变化,而电介质中将出现位移电流。当电容或dV/dT很高时,就很容易耦合噪声。例如,1 V/ns的变化速率会引起1 mA/pF的位移电流。

如果一个电路中电流流动产生的磁通密度变化耦合至另一电路,则会在第二个电路中引入电动势。这种"互感"是一种非常麻烦的噪声源,其耦合自dI/dT值较大的电路。例如,如果互感为1 nH,则电流变化速率为1 A/ns时,会引入1 V的电动势。

# 降低公共阻抗噪声

图3中列出了可消除或降低公共阻抗噪声(因传导路径共享阻抗而出现的噪声)的一些步骤。

- Common-impedance noise

- Decouple op amp power leads at LF and HF

- Reduce common-impedance

- Eliminate shared paths

- Techniques

- Low impedance electrolytic (LF) and local low inductance (HF) bypasses

- Use ground and power planes

- Optimize system design

图3: 公共阻抗噪声的一些解决方案

这些方法应与教程MT-031中介绍的所有相关技术配合使用。

给多个电路供电的供电轨就是很好的公共阻抗例子。实际电源可能具有低输出阻抗,也可能不是,尤其是在频率发生变化时。另外,用于配电的PCB走线同时具有感性和阻性,也可能构成接地环路。使用电源层和接地层还可以降低配电阻抗。PCB上的这些专用导体层是连续的(理想情况下如此),因此实际电阻和电感极低。

在某些应用中,低电平信号会遇到高电平公共阻抗噪声,此时不可能防止干扰,而是可能需要改变系统架构。可能需要改变以下几方面:

- 1. 以差分形式传输信号

- 2. 将信号放大到较高电平,以改善信噪比

- 3. 将信号转换为电流以便传输

- 4. 将信号直接转换为数字形式

#### 近场干扰的感生噪声

"串扰"是第二常见的干扰形式。在噪声源附近(即近场)时,干扰不是以电磁波形式传送,而 串扰一词可以指代感性或容性耦合信号。

## 降低容性耦合噪声

容性耦合噪声可以通过减少耦合电容(方法是增加导线间距)来降低,但最简单的解决方法 是采用屏蔽。通过在信号源和受影响节点之间放置导电且接地的屏蔽体(称为"法拉第屏蔽 体"),可将位移电流直接路由至地,从而消除这种噪声。

使用此类屏蔽体时,值得注意的是,法拉第屏蔽体必须接地,这点非常重要。屏蔽体浮动或开路无一例外都会导致容性耦合噪声增加。如需简单回顾这种屏蔽方法,请参见本文结尾部分的参考文献2和3。

图4汇总了消除电容耦合干扰的方法。

- ♦ Reduce Level of High dV/dt Noise Sources

- Use Proper Grounding Schemes for Cable Shields

- **♦** Reduce Stray Capacitance

- Equalize Input Lead Lengths

- Keep Traces Short

- Use Signal-Ground Signal-Routing Schemes

- Use Grounded Conductive Faraday Shields to Protect Against Electric Fields

#### 图4: 降低电容耦合噪声的方法

#### 降低磁耦合噪声

图5汇总了消除磁场导致干扰的方法。

- Careful Routing of Wiring

- Use Conductive Screens for HF Magnetic Shields

- Use High Permeability Shields for LF Magnetic Fields (mu-Metal)

- Reduce Loop Area of Receiver

- Twisted Pair Wiring

- Physical Wire Placement

- Orientation of Circuit to Interference

- Reduce Noise Sources

- Twisted Pair Wiring

- Driven Shields

图5. 降低磁耦合噪声的方法

5

为了说明磁耦合噪声的影响,假设闭环面积为A cm²的电路在通量密度均方根值为B(高斯)的磁场内工作。那么,此电路中的感生噪声电压V\_可以用下式表示:

$$V_n = 2 \pi f B A \cos\theta \times 10^{-8} V$$

公式 1

在此公式中,f表示磁场频率,θ表示磁场B与环路面积为A的电路之间的角度。通过减少电路环路面积、磁场强度或入射角,便可以降低磁场耦合。要减少电路环路面积,则需要将电路导线排列得更紧密。将导线绞合在一起可以减少环路净面积。理想情况下,正负增量环路面积等于零,因此具有消除磁场耦合的效果。直接减弱磁场可能比较困难。不过,由于磁场强度和电路与干扰源的距离立方成反比,因此使受影响的电路远离磁场可以显著降低感生噪声电压。最后,如果电路与磁场垂直,则可以将耦合降至最低。如果电路的导线与磁场并行,那么入射角为零,因此感生噪声将达到最大。

虽然屏蔽体和屏蔽套对磁场的屏蔽效果远远不如对电场的屏蔽效果,但有时也会有用。低频时,采用高导磁合金等高导磁率材料的磁屏蔽体可以在一定程度上衰减磁场。高频时,只要屏蔽体的厚度大于所用导线的集肤深度(在所涉频率条件下),简单的导电屏蔽体就非常有效。注意,铜的集肤深度为6.6√f cm,其中f单位为Hz。

#### 无源元件: EMI克星

只要使用得当, 电阻、电容和电感等无源元件都是降低外部感生干扰的强有力工具。

简单的RC网络可以构成高效、经济的单极、低通滤波器。输入噪声会通过电阻转换成热量而消耗掉。但要注意固定电阻本身会产生热噪声。另外,在运算放大器或仪表放大器的输入电路中使用时,此类电阻会产生由输入偏置电流感生的失调电压。虽然使两个电阻相匹配可以将直流失调降至最低,但该噪声将保持不变。图6汇总了一些能够将EMI降至最低的常用低通滤波器。

如果应用中信号和回路导线没有实现良好地磁耦合,那么可以使用共模(CM)扼流圈来增加两者之间的互感。注意,这些注释主要适用于仪表放大器,后者接收平衡输入信号(除非构建仪表放大器,否则运算放大器本来要求用非平衡输入信号)。CM扼流圈非常容易构建,只需将差分信号导线在高导磁率(> 2000)氧化铁磁珠上绕几圈即可。磁珠的磁性允许差模电流顺畅通过,但却会抑制CM电流。

| LP Filter Type                  | ADVANTAGE                                                                                | DISADVANTAGE                                                                     |

|---------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| RC Section                      | Simple<br>Inexpensive                                                                    | Resistor Thermal Noise<br>I <sub>B</sub> x R Drop → Offset<br>Single-Pole Cutoff |

| LC Section<br>(Bifilar)         | Very Low Noise at LF<br>Very Low IR Drop<br>Inexpensive<br>Two-Pole Cutoff               | Medium Complexity<br>Nonlinear Core Effects Possible                             |

| <sup>π</sup> Section<br>(C-L-C) | Very Low Noise at LF<br>Very Low IR Drop<br>Pre-packaged Filters<br>Multiple-Pole Cutoff | Most Complex<br>Nonlinear Core Effects Possible<br>Expensive                     |

图6: 在滤波器内使用无源元件来抑制EMI

此外,还可以在扼流圈的前后连接电容,分别提供额外的CM滤波和差模滤波。这种CM扼流圈价格便宜,而且由于线路的直流电阻很低,因此热噪声和由偏置电流感生的失调极低。不过,核芯周围有磁场。为了防止与其它电路发生耦合,核芯可能需要用金属屏蔽体包围起来。同时注意,应避免核芯中出现高电平电流,因为这样可能会使氧化铁饱和。

第三种无源滤波方法是采用封装的π网络(C-L-C)。这类封装滤波器完全独立,在输入端和输出端都连接有穿心式电容,并集成一个屏蔽体以防止电感的磁场辐射噪声。这类网络价格较贵,可提供较高的衰减水平并可在宽频率范围内工作,但选择滤波器时必须确保磁珠所涉及的工作电流电平不会出现饱和。

# 降低系统的EMI敏感度

本文前面通过一些通用示例和技术概述了可用于降低或消除EMI/RFI的步骤。图7给出了一些基于系统考量的可能措施。

如需了解其它抗EMI的滤波技术示例,请参见"教程MT-070"

下文将进一步细述屏蔽原理。

- Always Assume That Interference Exists!

- Use Conducting Enclosures Against Electric and HF Magnetic Fields

- Use mu-Metal Enclosures Against LF Magnetic Fields

- Implement Cable Shields Effectively

- Use Feedthrough Capacitors and Packaged PI Filters

## 图7: 降低系统EMI/RFI敏感度

## 屏蔽概念回顾

接下来讨论屏蔽效果概念这些背景知识。有兴趣的读者可以查看教程结尾的参考文献4-9来了解更多详情。

要有效地运用屏蔽概念,需要了解干扰源、干扰源周围的环境以及干扰源与观察点(接收器)之间的距离。如果电路在干扰源附近工作(即近场或感应场),那么场特性取决干扰源。如果电路位于远处(即远场或辐射场),那么场特性取决于传输介质。

如果电路与干扰源之间的距离小于干扰波长(λ)除以 $2\pi$ (即λ/ $2\pi$ ),则电路在近场内工作。如果电路与干扰源之间的距离大于该数值,那么电路在远场内工作。例如,对于由1 ns 脉冲边沿导致的干扰,其带宽上限大约为350 MHz。350 MHz信号的波长约为32英寸(光速约为12"/ns)。将该波长除以 $2\pi$ 即可得到距离大约为5英寸,这就是近场和远场之间的界限。如果电路位于350 MHz干扰源的5英寸范围之内,那么该电路在干扰源近场内工作。如果距离大于5英寸,那么该电路在干扰源远场内工作。

无论是何种干扰类型,都具有相关的特征阻抗。该特征(即场的波阻抗)由其电场(以E表示)与其磁场(以H表示)的比值决定。在远场中,电场与磁场的比值为自由空间的特征(波阻抗),即 $Z_0=377$  Ω。在近场中,波阻抗由干扰性质以及与干扰源的距离决定。如果干扰源具有高电流和低电压(如环路天线或电源线路变压器),那么主要是磁场,波阻抗小于377 Ω。如果干扰源具有低电流和高电压(如拉杆天线或高速数字开关电路),那么主要是电场,波阻抗大于377 Ω。

可以使用导电外壳来屏蔽敏感电路,以免其受到这些外部场影响。这类材料可以形成与入射干扰的"阻抗不匹配",原因是屏蔽体的阻抗小于入射场的波阻抗。导电屏蔽体的有效性取决于以下两项:首先是因屏蔽材料反射入射波而造成的损耗。其次是因屏蔽材料吸收透射波而造成的损耗。反射损耗量取决于干扰类型及其波阻抗。但是,吸收损耗量则与干扰类型无关。无论是对于近场辐射与远场辐射,还是对于电场与磁场,该损耗量都相同。

两种介质间表面的反射损耗取决于两种介质的特征阻抗差异。对于电场,反射损耗取决于干扰频率和屏蔽材料。该损耗可以用dB表示,计算公式如下:

$$R_{e}(dB) = 322 + 10\log_{10} \left[ \frac{\sigma_{r}}{\mu_{r} f^{3} r^{2}} \right]$$

公式 2

其中, $\sigma_r$ 是屏蔽材料的相对导电率,单位为西门子每米; $\mu$ r是屏蔽材料的相对导磁率,单位为亨利每米;f是干扰频率,而r是与干扰源的距离,单位为米。

对于磁场,该损耗也取决于屏蔽材料和干扰频率。对于磁场,反射损耗的计算公式如下:

$$R_{m}(dB) = 14.6 + 10\log_{10}\left[\frac{fr^{2}\sigma_{r}}{\mu_{r}}\right]$$

公式 3

而对于平面波 $(r > \lambda/2\pi)$ ,则反射损耗的计算公式如下:

$$R_{pw}(dB) = 168 + 10\log_{10}\left[\frac{\sigma_r}{\mu_r f}\right]$$

公式 4

"吸收"是屏蔽材料的第二种损耗机制。因吸收而造成的波衰减计算公式如下:

$$A(dB) = 3.34t\sqrt{\sigma_r \mu_r f}$$

公式 5

其中,t是屏蔽材料的厚度,单位为英寸。该表达式适用于平面波、电场和磁场。由于透射场的强度相对于屏蔽材料的厚度呈指数减少,因此当屏蔽体的厚度为一个集肤深度(δ)时,则吸收损耗为9 dB。吸收损耗与厚度成正比,但却与集肤深度成反比,因此通过增加屏蔽材料厚度可以改善高频条件下的屏蔽效果。

在远场中,由于屏蔽体阻抗Z<sub>s</sub>随频率升高而增加,因此平面波的反射损耗随频率升高而减少。然而,因为集肤深度减少,所以吸收损耗会随频率升高而增加。对于电场和平面波,主要屏蔽机制为反射损耗,而在高频条件下,屏蔽机制为吸收损耗。

因此,对于高频干扰信号,铜或铝等轻便、易加工的高导电性材料可以提供足够的屏蔽效果。不过,在低频条件下,磁场的反射损耗和吸收损耗都很低。因此,很难通过屏蔽体来保护电路不受低频磁场的影响。在这类应用中,采用具有低磁阻的高导磁率材料效果最佳。这类低磁阻材料提供漏磁路径,可使磁场偏离受保护的电路。例如钢和高导磁合金就是高导磁率材料。

总而言之,常用于屏蔽的金属材料具有以下特性:对于高频干扰,采用高导电性金属,而对于低频干扰,则采用高导磁性金属。

具有适当屏蔽效果的外壳可以非常有效地防止外部干扰影响其内部器件,并可以抑制任何内部产生的干扰。不过,在实际应用中,屏蔽体上通常需要有开口,以便配置调整旋钮、开关或连接器或者提供通风。不幸的是,这些开口让高频干扰得以借机进入仪器内部,因此可能影响屏蔽效果。

评估外部场进入外壳的能力时,请使用开口的最长尺寸(而非总面积),因为开口就好比槽形天线。公式6可用于计算外壳上开口的屏蔽效果(即EMI泄漏或渗透敏感度):

Shielding Effectiveness (dB) =

$$20 \log_{10} \left( \frac{\lambda}{2 \cdot L} \right)$$

公式 6

其中, λ是干扰波长, 而L是开口的最大尺寸。

当开口的最大尺寸等于干扰频率的半波长时,穿过开口的EMI辐射达到最大(即屏蔽效果为0 dB)。根据经验应确保最长尺寸小于干扰信号的1/20波长,这时屏蔽效果为20 dB。另外,在外壳每侧分别开一些小口要优于在一侧开很多口。这是因为不同侧面上的开口会向不同方向辐射能量,这样屏蔽效果反而不会受影响。如果不得不留出开口和缝隙,那么应当合理地单独或混合使用导电垫片、网屏和涂料,将任意开口的最长尺寸限制在1/20波长以内。穿过外壳的所有电缆、走线、连接器、指示器或控制轴都应该用环绕金属屏蔽体包裹,并且该屏蔽体应该在入口点处连接到外壳上。在那些使用无屏蔽电缆/走线的应用中,建议在屏蔽体入口点处连接滤波器。

# 关于电缆和屏蔽体的基本要点

虽然其他地方已经详细说明,但此处还值得一提的是,电缆及其屏蔽体使用不当可能成为辐射干扰和传导干扰的重要来源。这里就不再对这些问题做长篇大论,有兴趣的读者可以查看参考文献2、3、5和6来了解背景知识。

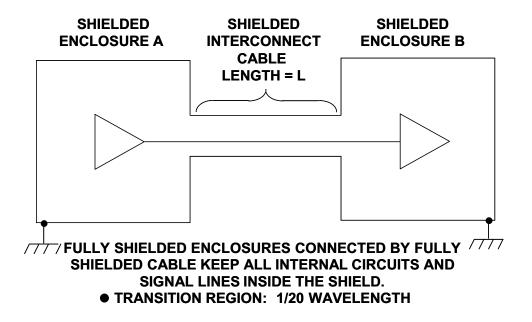

如图8所示,适当的电缆/外壳屏蔽可以将敏感电路和信号"完全限制在屏蔽体内",屏蔽效果丝毫不受影响。

图8: 屏蔽互连电缆可以是长线或短线, 具体取决于工作频率

如图中所示,外壳和屏蔽体必须适当接地,否则会起到天线作用,进而导致辐射干扰和传导干扰变得更糟(而不是变好)。

视干扰类型(拾取/辐射、低频/高频),需以不同的方式来实现适当的电缆屏蔽,并且与电缆长度密切相关。第一步是确定电缆长度在相关频率下属于"长线"还是"短线"。如果电缆长度小于最高干扰频率的1/20波长,那么视为短线。否则,则视为长线。

例如,50/60 Hz时,长度小于150英里的所有电缆都属于短线,而这些低频电场的主要耦合机制为容性耦合。因此,对于长度小于150英里的所有电缆,整条电缆上的干扰幅度都相同。

如果应用中电缆长度属于长线或需要针对高频干扰提供保护,那么首选方法是将电缆屏蔽体"两端"都连接到低阻抗点。正如下文所述,可以是直接链接(驱动端)或容性连接(接收器端)。如果未接地,未端接的传输线路效应可能导致电缆出现反射和驻波。当频率为10 MHz及以上时,屏蔽体环焊(360°)和金属连接器需要与地之间具有低阻抗连接。

总而言之,要针对低频(<1 MHz)电场干扰提供保护,可以在一端将屏蔽体接地。对于高频干扰(>1 MHz),首选方法是将屏蔽体两端都接地,即在屏蔽体和连接器之间使用360°环焊,而连接器和外壳之间保持金属间导通。

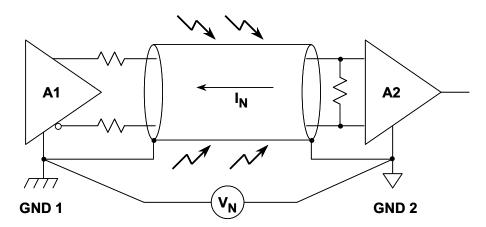

不过,在实际操作中,屏蔽体两端都直接接地时有一点需要注意,就是这样做会构成低频接地环路,如图9所示。

- ♦ V<sub>N</sub> Causes Current in Shield (Usually 50/60Hz)

- ♦ Differential Error Voltage is Produced at Input of A2 Unless:

- A1 Output is Perfectly Balanced and

- A2 Input is Perfectly Balanced and

- Cable is Perfectly Balanced

图9: 屏蔽双绞线中的接地环路可能导致误差

只要两个系统A1和A2相距较远,各系统的地电位(即 $V_N$ )通常都存在差异。此电位差的频率通常为线路频率(50或60 Hz)及其倍数。但是,如果屏蔽体按照图中所示两端都直接接地,那么屏蔽体中会出现噪声电流IN。在完美平衡的系统中,系统的共模抑制能力无穷大,因此这一电流不会在接收器A2处产生任何差分误差。然而,驱动器、其阻抗、电缆和接收器中永远不可能实现完美平衡,因此会有一部分屏蔽电流以差分噪声信号形式出现在A2的输入端。下面针对各示例说明屏蔽体正确接地方式。

如上所述,电缆屏蔽体会受低频和高频干扰影响。良好的设计要求:如果电缆相对于干扰 频率为长线(射频干扰通常就是如此),则屏蔽体两端都应接地。

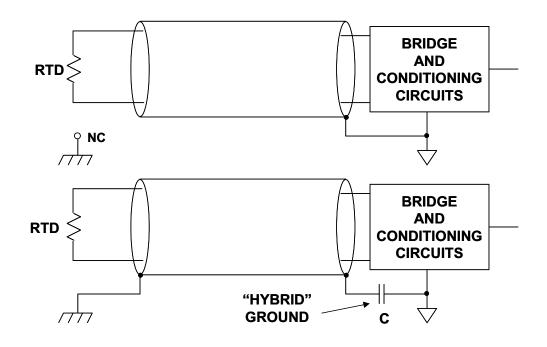

图10所示为远程无源RTD传感器通过屏蔽电缆连接到电桥和调理电路。正确的接地方式如图中上部所示,其中屏蔽体在接收端接地。

图10: 屏蔽电缆(带无源传感器)的混合接地

不过,出于安全考虑,该屏蔽体的远端可能也要接地。这种情况下,可以利用低电感陶瓷电容(0.01 μF至0.1 μF)在接收端接地,这样仍可提供高频接地。该电容可用作屏蔽体上射频信号的地,但却会阻止低频线路电流在屏蔽体中流动。这种技术通常称为"混合接地"。

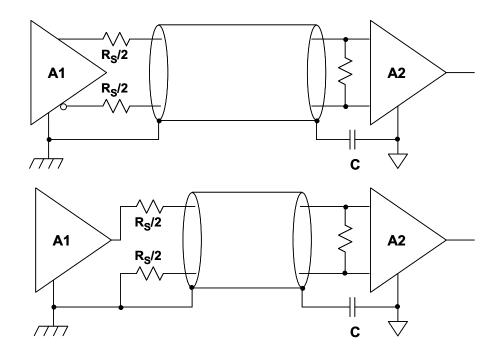

图11所示为使用有源远程传感器和/或其它电子器件的情况。这两种情况下,无论是平衡驱动器(上部)还是单端驱动器(下部),混合接地都同样适合。两种情况下,电容"C"会断开低频接地环路,同时为图中右侧A2接收端的屏蔽电缆提供有效的射频接地。

此外,对于所使用的源端接电阻 $R_s$ ,还有一些细微之处应当注意。在平衡驱动和单端驱动情形下,平衡线路上的驱动信号均由净阻抗 $R_s$ 产生,而后者又作为两个 $R_s$ /2分散在两个双绞引脚上。在图中上部的全差分驱动情形下,这点比较直观,一个取值为 $R_s$ /2的电阻与A1的互补输出串联。

在图中下部的单端驱动情形下,注意仍然使用了两个R<sub>s</sub>/2电阻,其中一个电阻与两个引脚串联。此处,接地哑回路引脚电阻可以为差分线路提供阻抗平衡的接地连接驱动,从而帮助提高系统整体抗扰度。注意,这种实施方案仅适用于A2处具有平衡接收器的那些应用,如图所示。

图11: 平衡屏蔽电缆的阻抗平衡驱动可帮助 提高平衡信号源或单端信号源的抗扰度

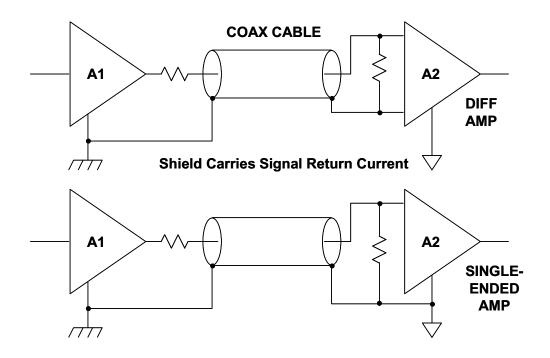

同轴电缆与屏蔽双绞线的不同之处在于,信号电流回路要穿过屏蔽体。因此,理想的状况是在驱动端将屏蔽体接地,而在差分接收器(A2)端则允许屏蔽体悬空,如图12的上部所示。不过,为使这种技术有效,接收器必须是差分类型且必须具有良好的高频CM抑制能力。

然而,接收器可能是单端类型,如标准单运放型电路中的典型元件。图12中的下部示例就是如此,因此这种情况下就必须将同轴电缆屏蔽体两端都接地。

图12. 同轴电缆可以使用平衡接收器或单端接收器

# 参考文献:

- 1. Tim Williams, EMC for Product Designers, 2<sup>nd</sup> Ed., Newnes, Oxford, 1996, ISBN: 0 7506 2466 3.

- Henry Ott, Noise Reduction Techniques In Electronic Systems, 2<sup>nd</sup> Ed., John Wiley & Sons, New York, 1988, ISBN 0-471-85068-3.

- 3. Mark Montrose, EMC and the Printed Circuit Board, IEEE Press, 1999, ISBN 0-7803-4703-X.

- 4. Ralph Morrison, *Grounding And Shielding Techniques in Instrumentation*, 3<sup>rd</sup> Ed., John Wiley & Sons, New York, 1986, ISBN 0-471-83805-5.

- 5. Daryl Gerke and William Kimmel, "Designer's Guide to Electromagnetic Compatibility," *EDN*, January 20, 1994.

- 6. Designing for EMC (Workshop Notes), Kimmel Gerke Associates, Ltd., 1994.

- 7. Daryl Gerke and William Kimmel, "EMI and Circuit Components," EDN, September 1, 2000.

- 8. Alan Rich, "Understanding Interference-Type Noise," <u>Analog Dialogue</u>, Vol. 16, No. 3, 1982, pp. 16-19 (also available as <u>application note AN-346</u>).

- 9. Alan Rich, "Shielding and Guarding," <u>Analog Dialogue</u>, Vol. 17, No. 1, 1983, pp. 8-13 (also available as application note AN-347).

- 10. James Wong, Joe Buxton, Adolfo Garcia, James Bryant, "Filtering and Protection Against EMI/RFI" and "Input Stage RFI Rectification Sensitivity", Chapter 1, pg. 21-55 of *Systems Application Guide*, 1993, Analog Devices, Inc., Norwood, MA, ISBN 0-916550-13-3.

- 11. Adolfo Garcia, "EMI/RFI Considerations", <u>Chapter 7, pg 42-80 of High Speed Design Techniques</u>, 1996, Analog Devices, Inc., Norwood, MA, 1993, ISBN 0-916550-17-6.

- 12. Walt Kester, Walt Jung, Chuck Kitchen, "Preventing RFI Rectification", Chapter 10, pg 10.39-10.43 of <u>Practical Design Techniques for Sensor Signal Conditioning</u>, Analog Devices, Inc., Norwood, MA, 1999, ISBN 0-916550-20-6.

- 13. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

- 14. *B4001 and B4003 common-mode chokes*, Pulse Engineering, Inc., 12220 World Trade Drive, San Diego, CA, 92128, 619-674-8100, <a href="http://www.pulseeng.com">http://www.pulseeng.com</a>

- 15. *Understanding Common Mode Noise*, Pulse Engineering, Inc., 12220 World Trade Drive, San Diego, CA, 92128, 619-674-8100, <a href="https://www.pulseeng.com">http://www.pulseeng.com</a>

- Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 11

- 17. Walt Kester, <u>Analog-Digital Conversion</u>, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as <u>The Data Conversion Handbook</u>, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

- 18. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Chapter 7. Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 7.

# 一些与EMC和信号完整性相关的实用链接:

- 1. Kimmel Gerke Associates website, http://www.emiguru.com

- 2. Henry Ott website, http://www.hottconsultants.com

- 3. IEEE EMC website, <a href="http://www.ewh.ieee.org/soc/emcs">http://www.ewh.ieee.org/soc/emcs</a>

- 4. Mark Montrose website, <a href="http://www.montrosecompliance.com/index.html">http://www.montrosecompliance.com/index.html</a>

- 5. Tim Williams website, http://www.elmac.co.uk

- 6. Eric Bogatin website, <a href="http://www.bethesignal.com">http://www.bethesignal.com</a>

- 7. Howard Johnson website, <a href="http://signalintegrity.com">http://signalintegrity.com</a>

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

# RFI整流原理

# 输入级RFI整流灵敏度

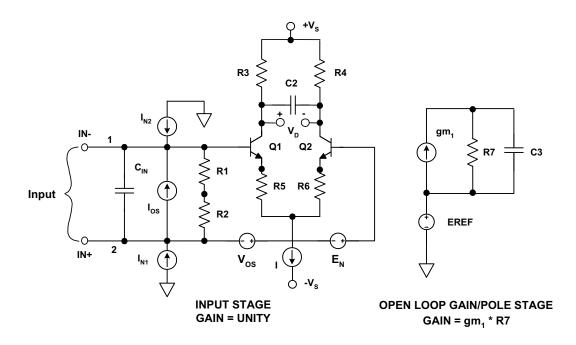

模拟集成电路中有一种众所周知却又了解不深的现象,即RFI整流,在运算放大器和仪表放大器中尤为常见。放大极小信号时,这些器件可以对大幅度带外HF信号进行整流,即RFI。因此,除所需信号外,输出端还会出现直流误差。不需要的HF信号可以通过多种途径进入敏感模拟电路。引入和引出电路的导体为进入电路的干扰耦合提供了通路。这些导体会通过容性、感性或辐射耦合拾取噪声。杂散信号会和所需信号一起出现在放大器输入端。杂散信号的幅度虽然可能只有几十毫伏,但是也会产生一些问题。简言之,敏感低带宽直流放大器未必总能抑制带外杂散信号。对简单的线性低通滤波器而言,情况确实如此,而运算放大器和仪表放大器实际上会对高电平HF信号进行整流,从而导致非线性和异常失调。本指南将讨论RFI整流的分析和预防方法。

## 背景知识:运算放大器和仪表放大器RFI整流灵敏度测试

几乎所有的仪表放大器和运算放大器输入级都采用某种类型的射极耦合BJT或源极耦合FET差分对。根据器件工作电流、干扰频率及其相对幅度,这些差分对可以像高频检波器一样工作。检波过程会在干扰的谐波频谱成分上产生噪声,同样也会在直流分量上产生噪声!从干扰中检测到的直流成分会转换放大器偏置电平,导致结果不准确。

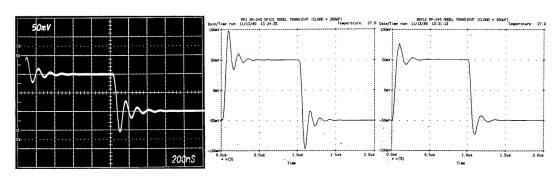

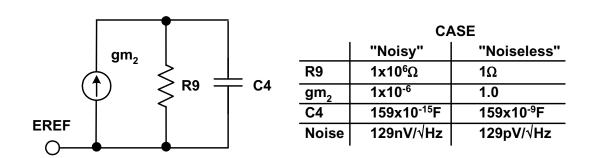

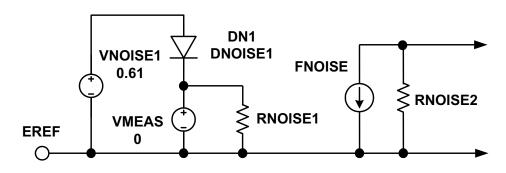

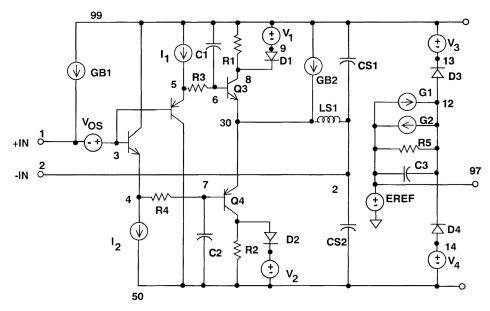

运算放大器和仪表放大器中的RFI整流效果可以通过相对简单的测试电路来评估,如RFI整流测试配置中所述(参见参考文献1第1至38页)。在这些测试中,运算放大器或仪表放大器增益配置为-100(运算放大器)或100(仪表放大器),直流输出在100 Hz低通滤波器后测量,以防来自其它信号的干扰。测试激励选用100 MHz、20 mV<sub>p-p</sub>信号,远高于测试器件的频率限制。操作时,测试可以评估存在激励时观察到的直流输出偏移。该测量的理想直流偏移为零,给定器件的实际直流偏移表示相对RFI整流灵敏度。采用BJT和FET技术的器件都可以通过该方法来测试,因为这些器件在高低电源电流水平下都可以工作。

在参考文献1中的原始运算放大器测试中,有些FET输入器件(<u>OP80</u>、<u>OP42</u>、<u>OP249</u>和 <u>AD845</u>)的输出电压不具有可观察的偏移,而其它有些器件则表现出小于10 μV的偏移(折合到输入端)。在BJT输入运算放大器中,偏移量会随着器件电源电流的增加而减小。只有两款器件不具有可观察的输出电压偏移(<u>AD797</u>和<u>AD827</u>),其它器件(<u>OP200</u>和<u>OP297</u>)的偏移则小于10 μV(折合至输入端)。可想而知,其它运算放大器在接受此类测试时也会表现出类似模式。

通过这些测试,可以概括出RFI整流的一些特点。首先,器件耐受性似乎与电源电流成反比,也就是说,在低静态电源电流下偏置的器件具有最高的输出电压偏移。其次,具有FET输入级的IC似乎比具有BJT的IC不易受整流影响。注意,无论是运算放大器还是仪表放大器,这些特点都是独立的。实际上,这意味着低功耗运算放大器或仪表放大器更易受RFI整流影响。而且,FET输入运算放大器(或仪表放大器)更不易受RFI整流的影响,在较高电流下工作时尤为如此。

根据上述数据和BJT与FET的基本差异,我们可以总结一下之前了解的内容。双极性晶体管效应受正偏PN结(基极-发射极结)的控制,该结点的I-V特性具有指数特性和明显的非线性。另一方面,FET特性受施加到反向偏置PN结二极管上电压的控制(栅极-源极结)。FET的I-V特性满足平方律,因此,本身就比BJT更具有线性。

对低电源电流器件而言,电路中的晶体管经过偏置后,电流远低于其峰值打集电极电流。虽然IC构建所用的工艺涉及的器件f<sub>T</sub>可达几百MHz,但是晶体管在低电流水平下工作时,电荷跃迁时间会增加。采用的阻抗水平也使这些器件中的RFI整流变得更差。在低功耗运算放大器中,阻抗约为几百到几千千欧,而在中等电源电流设计中,阻抗可能不超过几千欧。在这些因素的共同作用下,低功耗器件的RFI整流特性变差。

图1总结了关于RFI整流灵敏度的一般性观察,运算放大器和仪表放大器均适用。

- ♦BJT input devices rectify readily

- Forward-biased B-E junction

- Exponential I-V Transfer Characteristic

- ◆FET input devices less sensitive to rectifying

- Reversed-biased p-n junction

- Square-law I-V Transfer Characteristic

- ◆Low I<sub>supply</sub> devices versus High I<sub>supply</sub> devices

- Low I<sub>supply</sub> ⇒ Higher rectification sensitivity

- High I<sub>supply</sub> ⇒ Lower rectification sensitivity

图1:关于运算放大器和仪表放大器输入级RFI整流灵敏度的一些一般性观察

# 分析方法: BJT RFI整流

实验表明,与具有FET输入的类似器件相比,BJT输入器件具有更高的RFI整流灵敏度,可 以采用分析性更强的方法来解释这一现象。

RF电路设计人员早就知道,由于具备非线性I-V特性,PN结二极管是有效的整流器。HF 正弦波输入的BJT晶体管电流输出频谱分析表明,器件偏置越接近"膝部",非线性就越 高。这会进而使其用作检波器时更为有效。这一点在低功耗运算放大器中尤为重要,此 时输入晶体管在极低集电极电流时会发生偏置。

参考文献1中说明了BJT集电极电流的整流分析方法,在此恕不赘述,除非需要作出重要 结论。这些结果表明,原始二次二阶项可以简化为频率相关项Δi<sub>2</sub>(AC)(两倍输入频率下) 和直流项Δi<sub>.</sub>(DC)。后一项可以采用公式2表示,整流直流项的最终形式为:

该公式表明,二阶项的直流成分与HF噪声幅度Vx的平方以及晶体管的静态集电极电流Ic 成正比。为了表明整流的这一特点,注意,在Ic为1 mA条件下工作、具有10 mV<sub>nest</sub>高频信 号冲击的双极性晶体管的直流集电极电流变化约为38 μA。

减少整流集电极电流需要减少静态电流或干扰幅度。由于运算放大器和仪表放大器输入 级很少提供可调整静态集电极电流,迄今为止,减少干扰噪声Vx水平还是最佳(也几乎是 唯一)解决方案。例如,将干扰幅度减少2倍至5 mV<sub>peak</sub>后,会使整流集电极电流产生4到1的 净减少量。显然,这说明必须使杂散HF信号远离RFI敏感放大器输入端。

#### 分析方法: FET RFI整流

参考文献1中也说明了JFET漏极电流的整流分析方法,在此恕不赘述。类似的方法也用于 FET漏极电流整流分析,该电流与施加到其栅极的小电压Vx成函数关系。公式2概括了 FET漏极电流二阶整流项的评估结果。和BJT一样、FET二阶项也有交流和直流成分。此 处给出了整流漏极电流直流项的简化公式,其中整流直流漏极电流与杂散信号,即V、幅 度的平方成正比。

但是,公式2也说明,由FET和BJT产生的整流度的差异非常重要。

$$\Delta i_{D}(DC) = \left(\frac{V_{X}}{V_{P}}\right)^{2} \bullet \frac{I_{DSS}}{2}$$

公式 2

但是,在BJT中,集电极电流的变化与其静态集电极电流水平存在直接关系,JFET漏极电流的变化与处于零栅极-源极电压的漏极电流 $I_{DSS}$ 成正比,与其通道夹断电压 $V_p$ 的平方成反比,参数为几何参数,取决于过程。通常,用于仪表放大器和运算放大器输入级的JFET偏置时的静态电流约0.5· $I_{DSS}$ 。因此,JFET漏极电流的变化与其静态漏极电流无关,所以也和工作点无关。

图2所示为BJT和FET之间二阶整流直流项的定量比较。本例中,双极性晶体管具有576  $\mu$ m² 的单位发射面积,相对于用于20  $\mu$ A I<sub>DSS</sub>和2 V夹断电压的单位面积JFET。每个器件都在10  $\mu$ A 条件下偏置,工作温度T<sub>A</sub> = 25°C。

♦ BJT:

Emitter area = 576μm²

$$I_{DSS} = 20\mu A (Z/L=1)$$

$I_{C} = 10\mu A$

$V_{P} = 2V$

$V_{T} = 25.68mV @ 25°C$

$I_{D} = 10\mu A$

$$\Delta i_{C} = \left(\frac{V_{X}}{V_{T}}\right)^{2} \bullet \frac{I_{C}}{4}$$

$$= \frac{V_{X}^{2}}{264}$$

$$\Delta i_{D} = \left(\frac{V_{X}}{V_{P}}\right)^{2} \bullet \frac{I_{DSS}}{2}$$

♦ Conclusion: BJTs ~1500 more sensitive than JFETs!

#### 图2: BJT与JFET相对灵敏度比较

在相同的静态电流水平下,双极性晶体管中集电极电流的变化比JFET漏极电流的变化约大1500倍,这一结论非常重要。这就可以解释为什么FET输入放大器表现出的灵敏度小于大幅度HF激励。因此,它们可以提供更多RFI整流抗扰度。

根据上述内容,可以作出如下总结:由于用户几乎无法查看放大器的内部电路,防止因 RFI导致IC电路性能下降对IC外部电路而言就显得尤为重要。 上述分析表明,无论采用哪种类型的放大器,RFI整流都与干扰信号幅度的平方成正比。 因此,为了尽可能减少精密放大器中的RFI整流,必须在输入级之前减少或消除干扰电平。减少或消除干扰噪声的最直接方法是适当滤波。

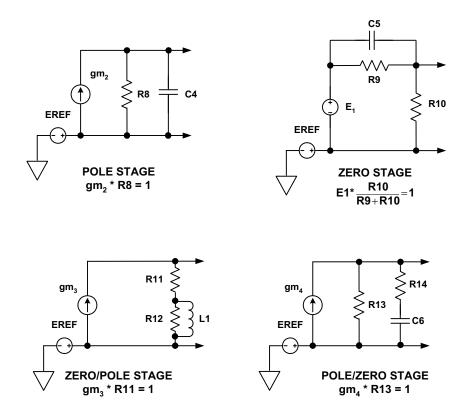

# 减少运算放大器和仪表放大器电路中的RFI整流

EMI和RFI会严重影响高精度模拟电路的直流性能。由于带宽相对较低,精密运算放大器和仪表放大器不会精确放大MHz范围内的RF信号。但是,如果这些带外信号能够通过精密放大器的输入、输出或电源引脚耦合至精密放大器,这些信号就会通过各种放大器结点进行内部整流,并最终在输出端导致不必要的直流失调。之前关于该现象的理论探讨已经说明其基本机制。下一步要介绍合适的滤波如何减少或消除这些误差。

合适的电源去耦可以将IC电源引脚上的RFI降至最低。放大器输入和输出还需要在器件级进一步探讨。此时,假定系统级EMI/RFI方法已经实现,如紧凑的RFI外形、正确接地的屏蔽层、电源轨滤波等。这些后续步骤可视为电路级EMI/RFI防护。

# 运算放大器输入

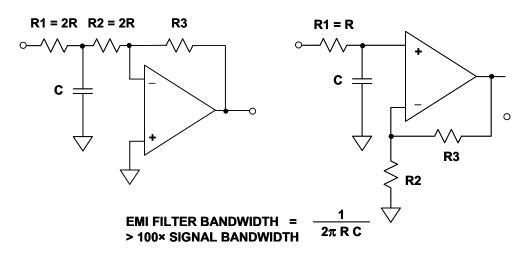

防止输入级整流的最佳方法是采用靠近运算放大器输入的低通滤波器,如图3所示。

图3: 用于运算放大器电路的简单EMI/RFI噪声滤波器

在左侧示意图的反相运算放大器中,滤波器电容C位于等值电阻R1-R2之间。由此可以得出简单的转折频率表达式,如图所示。在极低频率或直流情况下,电路的闭环增益为-R3/(R1+R2)。注意,C不能直接连接至运算放大器的反相输入,否则会产生不稳定性。所选的滤波器带宽至少为信号带宽的100倍,以便将信号损失降至最低。

在右侧示意图的同相运算放大器中,电容C可以直接连接至运算放大器输入,阻值为"R"的输入电阻会和反相运算放大器产生相同的转折频率。两种情况下都应采用低电感芯片式电容,如NP0陶瓷电容。电容在任何情况下都不应出现损耗或电压系数问题,因此只能选用上述NP0陶瓷电容或薄膜型电容。

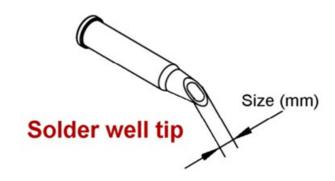

需要注意的是,可以用铁氧体磁珠代替R1,但是,铁氧体磁珠阻抗无法精确控制,一般不超过100 Ω(10 MHz至100 MHz时)。因此,需要采用容值较大的电容来衰减低频。

# 仪表放大器输入

由于存在共模(CM)EMI/RFI,精密仪表放大器对直流失调误差尤为敏感。这和运算放大器中存在的问题很像。而且,和运算放大器相比,采用低功耗仪表放大器时,EMI/RFI灵敏度问题尤为严重。

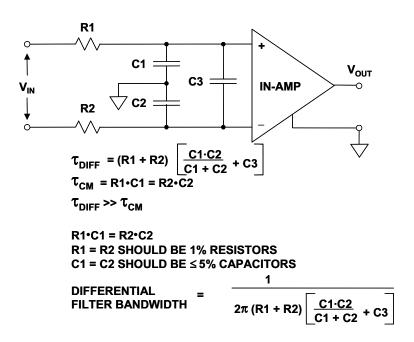

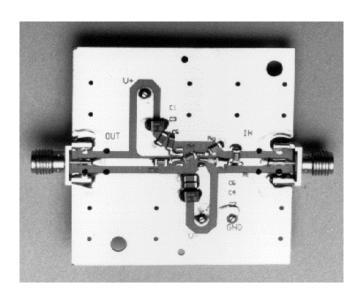

图4所示为仪表放大器器件级应用正确的通用滤波方法。实际上,该电路中的仪表放大器可以采用各种器件中的任何一种。仪表放大器之前相对复杂的平衡RC滤波器可以处理所有的高频滤波。仪表放大器可以通过其增益设置电阻,针对应用所需的增益进行编程(图中未显示)。

图4:仪表放大器通用共模/差模RC EMI/RFI滤波器

注意,在滤波器中,共模(R1-C1和R2-C2)和差模(DM)信号(R1+R2,以及C3 || 串联的C1-C2)均受到完全平衡的滤波。如果R1-R2和C1-C2匹配不佳, $V_{\rm IN}$ 的部分输入共模信号就会转换为仪表放大器输入端的差模信号。因此,C1和C2相互间至少有5%匹配。R1和R2应为1%金属薄膜电阻,以利于匹配。假定从 $V_{\rm IN}$ 端获得的源阻抗相对R1-R2较低,且能够匹配。在这种滤波器中,所选的C3应远大于C1或C2(C3  $\geq$  C1、C2),以便抑制由于R1-C1和R2-C2时间常数不匹配引起共模(CM)-差模(DM)转换,从而导致的杂散差分信号。

整体滤波器带宽应至少为输入信号带宽的100倍。实际上,滤波器元件应对称安装在具有 大面积接地层的PC电路板上,而且必须靠近仪表放大器输入端,以便实现最佳性能。

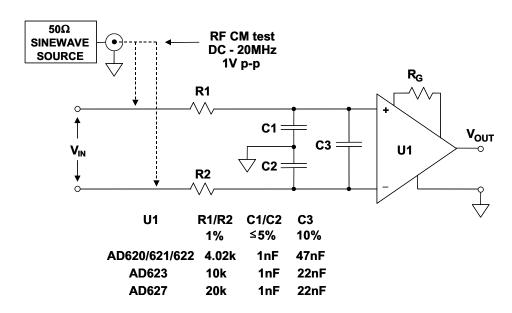

图5所示为该滤波器系列,适合各种不同的仪表放大器。RC元件应按照表中要求,根据不同的仪表放大器量身定制。选择这些滤波器元件是为了使低EMI/RFI灵敏度和低噪声增加量达到适度平衡(与无滤波器的相关仪表放大器相比)。

图5:适用于AD620系列、AD623、AD627和其它仪表放大器的灵活 共模和差模RC EMI/RFI滤波器

为了测试配置的EMI/RFI灵敏度,可以向输入电阻施加1 Vp-p的共模信号,如图所示。采用常用的仪表放大器(如AD620),在增益为1000的条件下工作时,获得的最大RTI输入失调电压偏移在20 MHz范围内为1.5 μV。在AD620滤波器示例中,差分带宽约为400 Hz。

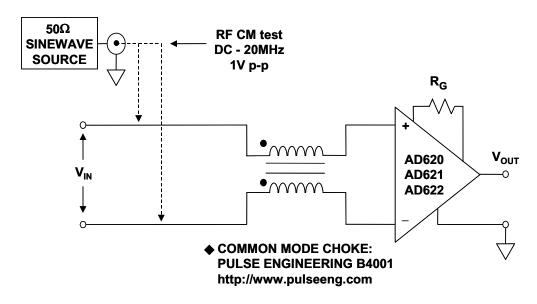

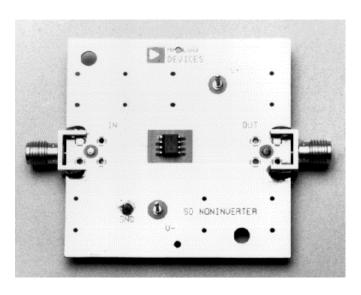

共模扼流圈提供简单的单器件EMI/RFI保护,可以替代无源RC滤波器,如图6所示。

图6: 为简明起见,以及实现最低噪声EMI/RFI滤波操作,共模扼流圈适用于 AD620系列仪表放大器

除了采用的元件数量较少以外,通过电阻的消除作用,基于扼流圈的滤波器还具有低噪声。但是,选择合适的共模扼流圈至关重要。图6所示电路中采用的扼流圈是Pulse Engineering B4001。从DC至20 MHz(G = 1000)测得的最大RTI失调偏移为4.5 µV。可以采用现成的扼流圈(如B4001),也可以另行制造。绕组的平衡非常重要,因此,建议采用双线绕组。当然,磁芯材料必须能够在预期频带内工作。注意,和图5中的RC滤波器系列不同,只采用扼流圈的滤波器无法提供差分滤波。通过增加图5所示的R1-C3-R2连接,可以在扼流圈后采用第二级设置选择增加差模滤波。

欲了解关于仪表放大器EMI/RFI滤波的更多信息,请参见参考文献1-9。

#### 放大器输出和EMI/RFI

除了对输入和电源引脚进行滤波外,还需要防止放大器输出受到EMI/RFI的影响,在需要驱动用作天线的较长电缆时尤其必须注意。从输出线路收到的RF信号可以耦合回其受到整流的放大器输入端,并以失调偏移的形式再次出现在输出端。

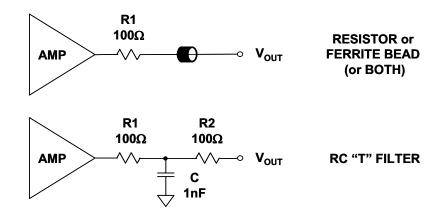

电阻和/或铁氧体磁珠(或两者)与输出串联后,即构成最简单廉价的输出滤波器,如图7 (上方电路)所示。

增加图7所示的电阻-电容-电阻"T"型电路(下方电路)后,可以改进该滤波器,只会略微变得复杂一些。输出电阻和电容会使大部分高频能量移出放大器,使该配置即使在低功耗有源器件中也同样适用。当然,必须仔细选择滤波器元件的时间常数,将所需输出信号下降程度降至最低。

本例中,所选的RC元件约为3 MHz信号带宽,适用于仪器仪表或其他低带宽级应用。

图7:应防止运算放大器和仪表放大器输出受到EMI/RFI的影响,尤其在驱动 长电缆的情况下

# 参考文献:

- 1. James Wong, Joe Buxton, Adolfo Garcia, James Bryant, "Filtering and Protection Against EMI/RFI" and "Input Stage RFI Rectification Sensitivity", Chapter 1, pg. 21-55 of *Systems Application Guide*, 1993, Analog Devices, Inc., Norwood, MA, ISBN 0-916550-13-3.

- 2. Adolfo Garcia, "EMI/RFI Considerations", <u>Chapter 7, pg 69-88 of High Speed Design Techniques</u>, 1996, Analog Devices, Inc., Norwood, MA, 1993, ISBN 0-916550-17-6.

- Walt Kester, Walt Jung, Chuck Kitchen, "Preventing RFI Rectification", Chapter 10, pg 10.39-10.43 of <u>Practical Design Techniques for Sensor Signal Conditioning</u>, Analog Devices, Inc., Norwood, MA, 1999, ISBN 0-916550-20-6.

- 4. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

- 5. *B4001 and B4003 common-mode chokes*, Pulse Engineering, Inc., 12220 World Trade Drive, San Diego, CA, 92128, 619-674-8100, <a href="http://www.pulseeng.com">http://www.pulseeng.com</a>

- 6. *Understanding Common Mode Noise*, Pulse Engineering, Inc., 12220 World Trade Drive, San Diego, CA, 92128, 619-674-8100, <a href="http://www.pulseeng.com">http://www.pulseeng.com</a>

- Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

- 8. Walt Kester, <u>Analog-Digital Conversion</u>, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as <u>The Data Conversion Handbook</u>, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

- 9. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Chapter 7. Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 7.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

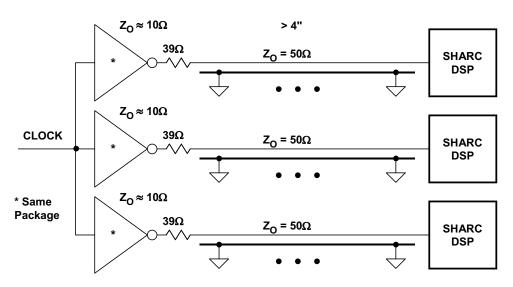

# 低电压逻辑接口

## 简介

目前,对更快、更小、成本更低的产品的旺盛需求推动着降低电源电压这一革命性的发展趋势。在这种需求的推动下,硅尺寸从20世纪80年代初的2 µm减小到0.90 nm和45 nm,这种小尺寸的硅被广泛用于当今的最新FPGA、微处理器和DSP设计当中。随着器件尺寸的不断缩小,实现器件最佳性能的电压也降至了5 V以下。这体现在当今的FPGA、微处理器和DSP之中,其最佳内核工作电压最低达1 V或者更低。

对低电压DSP的强烈兴趣十分清楚地体现在了5 V和3.3 V器件的销量变化中。3.3 V DSP的销售增长速度达DSP市场中所有其他器件的两倍以上(所有DSP器件的销量增长速度为30%,3.3 V器件则超过了70%)。在大批量/高增长便携式市场对具有低电压DSP全部特性的信号处理器的需求保持高速增长的背景下,这一趋势将继续下去。

一方面,低电压IC的工作在低功耗模式下,有利于缩小芯片面积,提高速度。另一方面,低电压IC必须与其他IC连接,而这些IC却工作于更大的 $V_{DD}$ 电源电压,因而会导致接口兼容性问题。尽管更低的工作电压意味着更小的信号摆幅、更小的开关噪声,从而低电源电压IC的噪声裕量也更低。

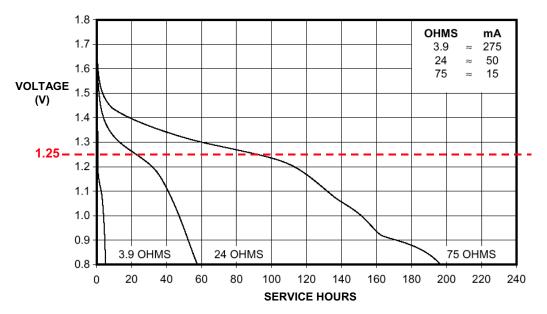

2.5 V器件之所以大行其道,其部分原因在于,它们支持2个AA碱性电池供电。图1展示了AA电池在各种负载条件下的典型放电特性(参考文献2)。请注意,在15 mA的负载电流下,电压可以维持在+1.25 V以上(两节电池串联则为2.5 V)近100小时。因此,可以在2.5 V±10%(2.25 V - 2.75 V)的电源电压下有效地进行低功耗工作的IC对于便携式设计十分有用。

Courtesy: Duracell, Inc., Berkshire Corporate Park, Bethel, CT 06801 http://www.duracell.com

图1: 金霸王MN1500 "AA"碱性电池的放电特性

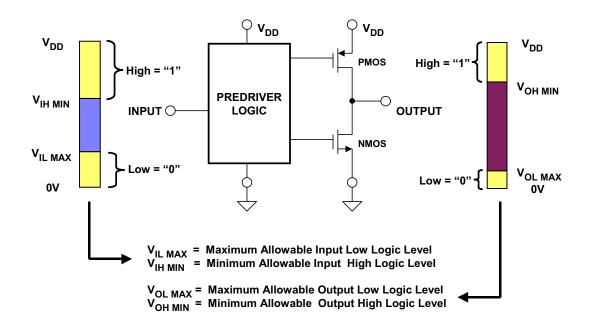

为了了解工作于不同 $V_{DD}$ 电源电压下的IC接口兼容性的问题,不妨先看看典型CMOS逻辑级的结构,如图2所示。

图2: 典型CMOS IC输出驱动器的配置

注意,输出驱动器级由一个PMOS和一个NMOS晶体管构成。当输出为高时,PMOS晶体管通过低导通电阻( $R_{ON}$ )把输出连接至+ $V_{DD}$ 电源,NMOS晶体管关闭。当输出为低时,NMOS晶体管通过导通电阻把输出连接至地,PMOS晶体管关闭。CMOS输出级的 $R_{ON}$ 在5  $\Omega$ 至50  $\Omega$ 之间不等,具体取决于晶体管的尺寸,而尺寸又决定着输出电流驱动能力。

典型逻辑IC的电源和地是分离于输出驱动器和电路其余部分之间的(包括前置驱动器)。这是为了维持干净的电源,以减少噪声和地反弹对I/O电平的影响。这一点越来越重要,因为在I/O驱动器规格中,尤其是在低电压下,增加容差和顺度是至关重要的。

图2同时展示了决定着产生有效高逻辑电平或低逻辑电平所需要的最低和最高输入和输出电压的"条形"。注意,对于CMOS逻辑来说,实际输出逻辑电平取决于晶体管的驱动电流和和RON。对于轻负载,输出逻辑电平非常接近0 V和+V<sub>DD</sub>。另一方面,输入逻辑阈值取决于IC的输入电路。

"输入"条中有三个部分。最下面的部分展示的是被理解为逻辑低电平的输入范围。对于5 V TTL,该范围在0 V和0.8 V之间。中间部分为被理解为既不是逻辑低电平也不是逻辑高电平的输入电压范围。最上面的部分展示的是被理解为逻辑高电平的输入范围。对于5 V TTL,该范围为2 V 至5 V。

类似地,"输出"条中也有三个部分。最下面的范围表示逻辑低电平输出的容许电压。对于 5 V TTL, IC必须输出0 V至0.4 V的电压。中间部分所示电压范围不是有效的高电平或低电平——除非在电平之间过渡时,否则器件不得发送处于该部分的电平。最上面的范围表示逻辑高电平输出信号的容许电压范围。对于5 V TTL,该电压在2.4 V和5 V之间。图表中并未反映逻辑标准输入允许的10%过冲/下冲容差。

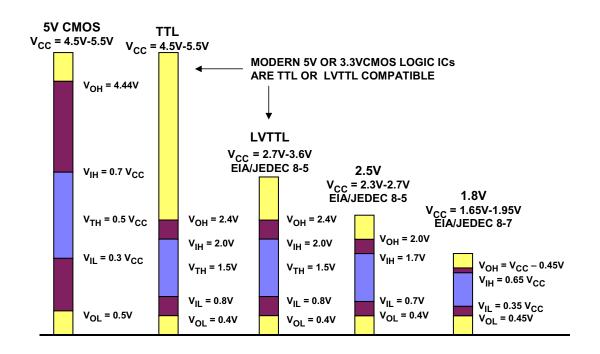

图3总结了基于这些定义的现有逻辑标准。注意,经典CMOS逻辑(如4000系列)的输入阈值定义为0.3  $V_{DD}$ 和0.7  $V_{DD}$ 。然而,目前使用的多数CMOS逻辑电路兼容TTL和LVTTL电平,它们是目前DSP的主流5 V和3.3 V工作电压标准。注意,5 V TTL和3.3 V LVTTL输入和输出阈值电压是相同的。其差异体现在容许高电平的上限方面。

图3: 标准逻辑电平

国际标准组织JEDEC(联合电子设备工程委员会)制定了2.5 V标准(JEDEC 8-5号标准)和1.8 V标准(参考文献3)。还有众多其他低电压标准,比如GTL(射补收发器逻辑)、BTL(基架收发器逻辑)、ECL(射极耦合逻辑)、PECL(正ECL逻辑)和LVDS。然而,多数这些标准都是针对具体的应用市场,并非针对通用半导体系统。

从图3可以看出,对连接两个工作于不同标准的IC时可能存在的问题进行可视化是有可能的。一个例子是把一个5 V TTL器件连接至一个3.3 V LVTTL IC。5 V TTL高电平超过了LVTTL的处理能力(>3.3 V)。这可能给LVTTL芯片造成永久性损坏。另一个可能的问题是在系统中用2.5 V IC驱动5 V CMOS器件。来自2.5 V器件的逻辑高电平不足以达到5 V CMOS输入的逻辑高电平的条件(V<sub>IH MIN</sub> = 3.5 V)。这些例子展示了两类潜在的逻辑电平兼容性问题——要么是用过高的电压驱动器件,要么驱动电压过低,达不到接收IC端的有效逻辑高电平的要求。这些接口问题带来了两个重要的概念:电压容差和电压顺度。

# 电压容差和电压顺度

电压容差型器件的I/O引脚可以承受大于其 $V_{DD}$ 的电压。例如,如果一个器件的 $V_{DD}$ 为 2.5 V,可以接受等于3.3 V的输入电压,并且其输出端可以承受3.3 V的电压,则称该2.5 V器件的容差电压为3.3 V。输入电压容差的意义是显而易见的,但输出电压容差却需要稍加说明。在高电平状态下,2.5 V CMOS驱动器输出的表现类似于连接至2.5 V电压的小电阻 (PMOS FET的 $R_{ON}$ )。显然,把该器件的输出直接连接到3.3 V的电压,过高的电流很可能会

损坏器件。然而,如果2.5 V器件有一个三态输出,连接着一个同样由3.3 V IC驱动的总线,则其意义将更加明显。即使2.5 V IC处于关闭(第三态)条件,3.3 V IC也可驱动高于2.5 V的总线电压,结果可能损坏2.5 V IC输出。

电压顺从型器件可以接收来自工作电压大于其自身 $V_{DD}$ 的器件的信号,也可把信号发送到此类器件。例如,如果一个器件的 $V_{DD}$ 为2.5 V,并可向3.3 V器件发送信号或者从其接收信号,则称该2.5器件的顺从电压为3.3 V。

5 V CMOS与3.3 V LVTTL器件之间的接口展现了电压容差的缺乏; LVTTL IC输入由5 V CMOS 器件输出过驱。2.5 V JEDEC与5 V CMOS器件之间的接口展示了电压顺度的缺乏; EDEC IC 的高输出电平不符合5 V CMOS器件的输入电平要求。

# 利用NMOS FET"总线开关"连接5V系统和3.3V系统

在连接工作于不同电压标准的IC时,我们往往被迫添加额外的分离式元件,以确保电压容差和电压顺度。例如,为了在5 V和3.3 V逻辑之间实现电压容差,可以使用ADG3257一类的总线开关电压转换器(另见参考文献4和5)。总线开关将限制应用于IC的电压。这是为了避免应用大于接受器件容许范围的高输入电压。

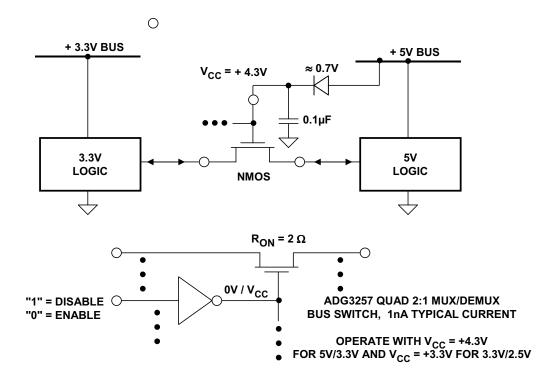

举例来说,可以在5 V CMOS和3.3 V LVTTL IC之间放置一个总线开关,此时,这两种器件就可以正常发送数据了,如图4所示。基本而言,总线开关是一种NMOS FET。如果将4.3 V 的电压置于FET的栅极上,则最大可通过信号为3.3 V(比栅极电压约低1 V)。如果输入和输出均低于3.3 V,则NMOS FET将充当低电阻( $R_{ON}\approx 2~\Omega$ )。随着输入接近3.3 V,FET导通电阻会增大,从而限制信号输出。ADG3257是一款四通道2:1 Mux/Demux总线开关,具有一个栅极驱动使能引脚,如图4下半部分所示。ADG3257的 $V_{CC}$ 设置栅极驱动的高电平。

图4: 采用NMOS FET的+5 V/+3.3 V 双向接口实现电压容差

在5 V/3.3 V系统板上实现4.3 V电源电压的一种方式是在5 V电源和总线开关 $V_{cc}$ 之间放置一个硅二极管,如图4所示。对于3.3 V/2.5 V应用, $V_{cc}$ 引脚可以直接连接至+3.3 V电源。有些总线开关设计用于直接工作于3.3 V或5 V的电源电压,并在内部产生内部栅极偏置电平。

在这种混合型逻辑设计中,总线开关可以消除电压容差问题。总线开关有一个便利的特性,即它们是双向的;借助该特性,设计人员可以在两个IC之间放一个总线转换器,而无需为输入和输出信号创建额外的路由逻辑。

总线开关会增加总功耗以及系统布局所需要的总面积。由于电压总线开关通常为CMOS电路,因此,其额定功耗都很低。连续功耗增加部分的平均值为每个封装5 mW(10个开关),这与通过电路的信号频率无关。总线开关每个封装一般有8到20个I/O引脚,大约占用25至50 mm²的电路板空间。

在电路中增加接口逻辑的一个顾虑是可能导致传播延迟增加。增加传播延迟可能给设计带来诸多时序问题。总线开关的传播延迟值非常低。

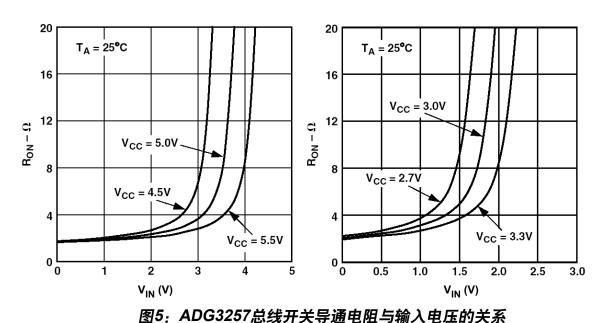

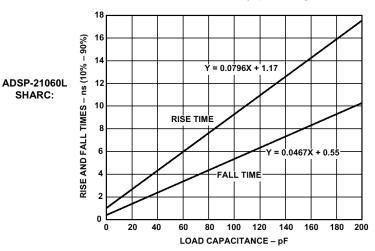

实际上,总线开关不会增加传播延迟(ADG3257的典型值为0.1 ns),只会增加在由理想电压源驱动时的开关的典型 $R_{ON}$ 以及负载电容的RC延迟。由于时间常数一般比典型驱动信号的上升/下降时间要小得多,所以总线开关只会为系统增加极小的传播延迟。因此,低 $R_{ON}$ 是总线开关的关键特性,因为开关导通电阻和总线电容会形成一个单极滤波器,结果会增加延迟、降低最大数据速率。ADG3257的典型导通电容为10 pF,再加上4  $\Omega$ 的 $R_{ON}$ ,结果会产生约90 ps的上升/下降时间。图5所示为ADG3257的导通电阻和5.5、5、4.5、3.3、3.0以及2.7 V电源输入电压的函数关系。作为输入电压函数的最大导通电压如图6所示。

T<sub>A</sub> = 25°C  $V_{CC} = 5.5V$  $V_{CC} = 3.6V$  $T_A = 25^{\circ}C$ 3 OUTPUT VOLTAGE - V OUTPUT VOLTAGE – V  $V_{CC} = 5.0V$  $V_{CC} = 3.3V$  $V_{CC} = 4.5V$ 2  $V_{CC} = 3.0V$ 0.5 3.5 1.0 1.5 2.0 2.5 3.0 INPUT VOLTAGE - V INPUT VOLTAGE - V

图6: ADG3257总线开关最大导通电压与输入电压的关系

Page 7 of 14 33

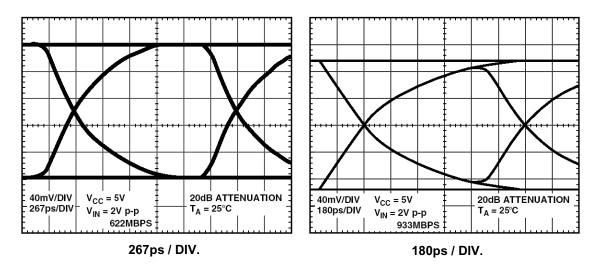

ADG3257在622 Mbps和933 Mbps工作频率下的眼图如图7所示。

图7: 622 Mbps和933 Mbps数据速率下的眼图

#### 3.3V/2.5V接口

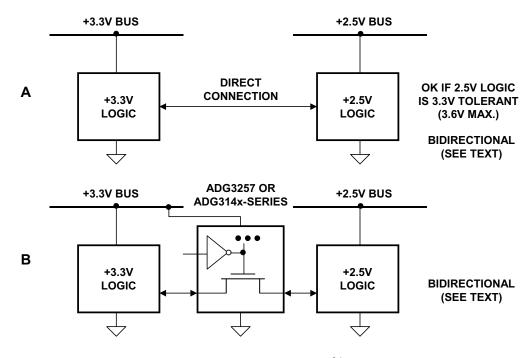

图8展示了3.3 V至2.5 V逻辑接口的两种可能性。上部图示(A)展示的是直接连接模式。只要 2.5 V IC输入端的容差电压为3.3 V,则该模式有效。如果2.5 V IC不能承受3.3 V,则可使用 ADG3231一类的低电压总线开关。在多数情况下,3.3 V和2.5 V两种系统之间的连接可以是 双向的,即使2.5 V逻辑 $V_{\rm CH}$ 的额定值与3.3 V逻辑的 $V_{\rm H}$ 额定值都是+2.0 V(参见前面的图3)。 这一点需要进一步的讨论。

图8: +3.3 V至+2.5 V接口

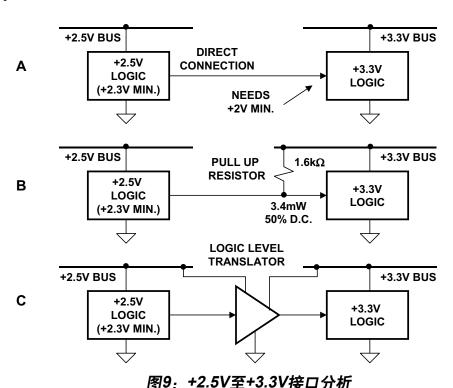

图9A所示为2.5 V和3.3 V逻辑之间的直接连接。为了使该连接有效,据JEDEC规范, 2.5 V输出的最小值不得低于2 V。当2.5 V输出端无负载时, 3.3 V IC输入通过PMOS晶体管驱动器的导通电阻直接连接至+2.5 V。这为2.5 V的额定电源电压提供了0.5 V的噪声裕量。然而, 2.5 V总线的容差允许其下降至2.3 V的最小值,此时,噪声裕量降至0.3 V。这在相对安静的环境中可能仍然有效,但是,如果电源电压存在噪声,则可能有些牵强。

如图9B所示,增加一个1.6 kΩ上拉电阻,在3.3 V器件输入电流的作用下,可以确保2.5 V输出不会降至2.5 V以下,但2.3 V电源的噪声裕量下降问题仍然存在。在50%的占空比下,电阻给每个输出端增加约3.4 mW的功耗。

图9C展示了2.5 V和3.3 V逻辑之间更可靠的一种接口,其中使用了ADG3231一类的逻辑转换器。这就解决了(A)和(B)两种情况下的全部噪声裕量问题,每个输出端只需大约2 μA(最大值)的功耗。

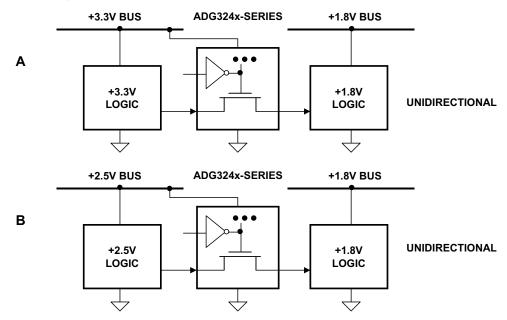

3.3V/2.5V、3.3V/1.8V、2.5V/1.8V接口

ADG3241、ADG3242、ADG3243、ADG3245、ADG3246、ADG3247、ADG3248和 ADG3249是针对3.3 V或2.5 V电源而优化过的低电压总线开关。该系列包括1位、2位、8位、10 位和双通道8位开关,全部都是双端口开关。ADG3241、ADG3242、ADG3245、ADG3246、ADG3247和ADG3249具有2.5 V或1.8 V可选电平转换能力。该系列为3.3 /2.5 V、

3.3 /1.8 V和2.5 /1.8 V单向接口提供了一种快速的低功耗解决方案。图10所示ADG32xx系列分别用作3.3 /1.8 V电平转换器和2.5 /1.8 V转换器。

图10: +3.3 V至+1.8 V、2.5 V至+1.8 V单向接口

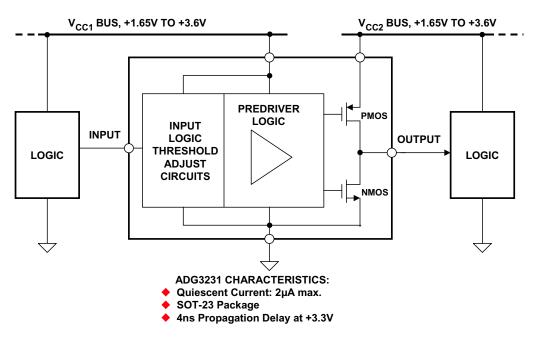

从1.8 V转换至2.5 V,从1.8 V转换至3.3 V(如前所述,有时是从2.5 V转换至3.3 V)要求使用类似于图11所示ADG3231一类的逻辑转换器。两个电压总线的值可以为1.65 V和3.6 V之间的任意值。ADG3231是一款采用SOT-23封装的单通道转换器,ADG3232是一款同样采用SOT-23封装的2:1多路复用器/电平转换器。

图11: ADG3231低电压逻辑电平转换器

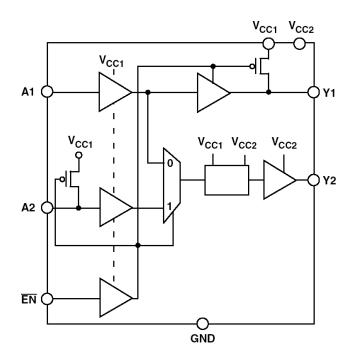

ADG3233是一款采用亚微米工艺设计的旁路开关,可支持最低1.65 V的工作电压。该器件可以保证在1.65 V至3.6 V的电源电压范围内正常工作,采用双电源电压,支持双向电平转换,也就是将低电压转换为高电压,反之亦然。信号路径是单向的,也就是说数据只能从A流向Y。这类器件可以用于要求旁路功能的应用之中。非常适合JTAG链中或者菊花链环路中的旁路器件。一个开关可以用于一个器件或多个器件,从而轻松旁路链中的一个或多个器件。这在测试JTAG链或菊花链应用中的器件时特别有用,用户不必更改特定器件的设置,从而节省时间开销。

这款旁路开关采用所需引脚数量的两种最小封装。8引脚SOT-23封装仅需8.26 mm×8.26 mm 电路板空间,而MSOP封装则占用大约15 mm×15 mm电路板面积。图12所示为ADG3233的功能框图。

图12: ADG3233低电压1.65 V至3.6 V 逻辑电平转换器和旁路开关

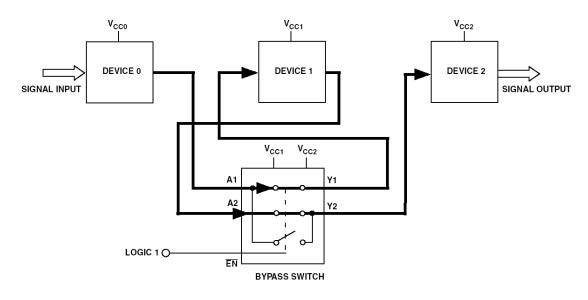

图13所示旁路开关用于正常模式。在该模式下,信号路径是从A1到Y1及从A2到Y2。该器件将把应用到A1的信号的电平转换为一种 $V_{\rm CCl}$ 逻辑电平(这种电平转换可以针对高电平电源,也可针对低电平电源),并把信号路由至Y1输出,该输出在 $V_{\rm CCl}$ 电源下为标准 $V_{\rm Ol}/V_{\rm OH}$ 电平。然后,信号通过器件1,再回到旁路开关A2输入引脚。A2的逻辑电平输入是针对 $V_{\rm CCl}$ 电源而言的。信号的电平将从 $V_{\rm CCl}$ 转换至 $V_{\rm CCl}$ ,并路由到旁路开关的Y2输出引脚。Y2输出逻辑电平是针对 $V_{\rm CCl}$ 电源而言的。

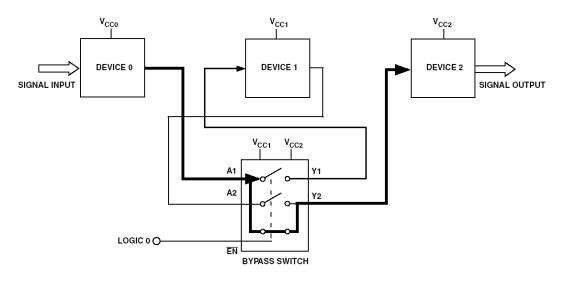

图14展示的是用在旁路操作中的器件。现在的信号路径是从A1直接到Y2,从而完全绕过了器件1。信号的电平将转换至一种 $V_{\text{CC2}}$ 逻辑电平,并提供给Y2,在这里,信号可以直接应用至器件2的输入引脚。在旁路模式下,Y1上拉至 $V_{\text{CC1}}$ 。图13和图14中的三种电源可以是任意电源组合,即 $V_{\text{CC0}}$ 、 $V_{\text{CC1}}$ 和 $V_{\text{CC2}}$ 可以是任意电源组合,如1.8 V、2.5 V和3.3 V。

图13: 正常模式下的ADG3233旁路开关

图14: 旁路模式下的ADG3233旁路开关

#### 内部形成的电压容差和电压顺度

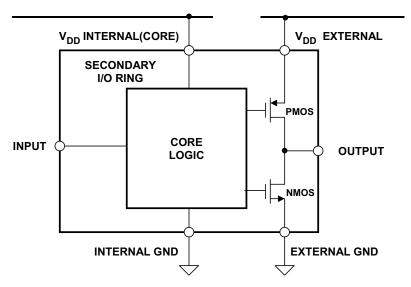

现代高性能CMOS DSP和微处理器一般采用1 V至2 V的内核电压。这种低电压会带来最佳的速度-功耗性能。然而,内核中的逻辑电平并不兼容标准的2.5 V或3.3 V I/O接口。这个问题一般以图15所示方式解决,其中,逻辑内核以低电压工作,但输出驱动器则以2.5 V或3.3 V 标准电源电压工作。

$V_{DD}$  EXTERNAL = +2.5V OR +3.3V  $V_{DD}$  CORE = +0.9V TO +1.8V (DEPENDING ON PROCESSOR) INPUT +2.5V or +3.3V TOLERANT

图15: 具有次级I/O环的CMOS IC的内部顺度和容差

许多IC制造商采取的技术是提供一个次级I/O环,即I/O驱动器由2.5 V或3.3 V电源驱动,因此,这种器件可以兼容2.5 V或3.3 V逻辑电平。注意,输入必须能顺从并承受I/O电源电压。在这种双电源逻辑IC的设计中,需要考虑多种问题:

- 上电时序控制:如果需要用两个电源来提供额外的IC容差/顺度,那么该上电时序是什么?是要求电源同时开启,还是要求器件只在内核上或仅在I/O环上提供电压?如果内核电压是用低压差线性调节器从I/O电源电压产生的,则可以很容易地解决这个问题。时序控制电路也可用来解决这些问题。

- 工艺支持和静电放电(ESD)保护:以IC制造工艺生产的晶体管必须能承受并驱动高电压。高电压晶体管会形成额外的制造成本,因为它们需要更多的处理步骤以形成高电压容差。采用标准晶体管的设计需要额外的电路。I/O驱动器也必须为器件提供ESD保护。多数电流设计把过压限制为超过电源电压的一个二极管压降(0.7 V)以下。更大的过压保护要求采用更多的串联二极管。

- 内部高电压的产生: PMOS晶体管需要置于一个基板阱中,后者与最高的片上电压相关联,以避免横向二极管开启、消耗过多的电流。该高电压既可以用电荷泵在片上产生,也可用外部电源产生。这种要求可能使设计复杂化,因为我们无法有效利用电荷泵来产生较高的电压,并同时实现低待机电流。多数情况下,该电压以外部方式提供。

- 芯片面积: 芯片尺寸是降低成本、提高产量的一个主要因素。容差电路和顺从电路可能要求更多或更大的I/O器件来实现目标性能水平。

- 测试:由于内核和I/O可以在不同电压下工作,因此,测试器件在各种可能电压组合下的特性是非常复杂的,会增加IC的总体成本。

## 参考文献

- 1. P. Alfke, "Low-Voltage FPGAs Allow 3.3V/5V System Design," *Electronic Design*, p. 70-76, August 18, 1997.

- 2. AA Alkaline Battery Discharge Characteristics, Duracell Inc., Berkshire Corporate Park, Bethel, CT 06801, www.duracell.com.

- 3. Joint Electron Device Engineering Council (JEDEC), <a href="www.jedec.org">www.jedec.org</a>, Standard JESD8-5, October 1995, and Standard JESD8-7, February, 1997,

- 4. QS3384 Data Sheet, Integrated Device Technology (IDT), Inc., 2975 Stender Way, Santa Clara, CA 95054, www.idt.com

- 5. Pericom Semiconductor Corporation, 2380 Bering Drive, San Jose, CA 95131, http://www.pericom.com

- 6. H. Johnson, M. Graham, High Speed Digital Design, Prentice Hall, 1993.

- 7. Eva Murphy and Catherine Redmond, "Bus Switches for Speed, Safety, and Efficiency: What They Are and What You Should Know about Them," *Analog Dialogue* 36-06, Analog Devices, Inc., 2002.

- 8. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

- 9. Walt Kester, <u>Analog-Digital Conversion</u>, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as *The Data Conversion Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

## 去耦技术

#### 何谓正确去耦?有何必要性?

如果电源引脚上存在纹波和/或噪声,大多数IC都会有某种类型的性能下降。数字IC的噪声裕量会降低,时钟抖动则可能增加。对于高性能数字IC,例如微处理器和FPGA,电源额定容差(例如±5%)包含直流误差、纹波和噪声之和。只要电压保持在容差内,数字器件便符合规范。

说明模拟IC对电源变化灵敏度的传统参数是电源抑制比(PSRR)。对于放大器,PSRR是输出电压变化与电源电压变化之比,用比率(PSRR)或dB(PSR)表示。PSRR可折合到输出端(RTO)或输入端(RTI)。RTI值等于RTO值除以放大器增益。

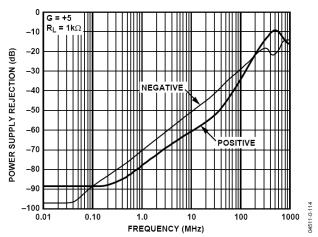

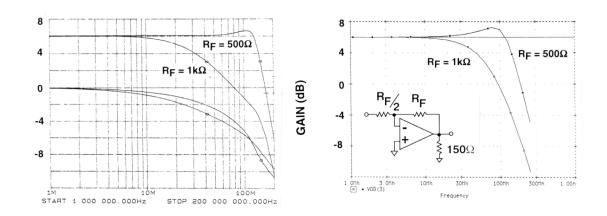

图1显示典型高性能放大器(AD8099) PSR随频率、以大约6 dB/8倍频程(20 dB/10倍频程)下降的情况。图中显示了采用正负电源两种情况下的曲线图。尽管PSR在直流下是90 dB,但较高频率下会迅速降低,此时电源线路上有越来越多的无用能量会直接耦合至输出。因此必须一开始就要防止此高频能量进入芯片。一般通过组合电解电容(用于低频去耦)、陶瓷电容(用于高频去耦)来完成,也有可能使用铁氧体磁珠。

数据转换器以及其他模拟和混合信号电路的电源抑制可能在数据手册中都有相关规定。不过,在数据手册的应用部分,经常会针对几乎所有的线性和混合信号IC推荐电源去耦电路。用户应始终遵循这些建议,以确保器件正常工作。

图1: AD8099高性能运算放大器的电源抑制 与频率的关系

低频噪声需要较大的电解电容,用作瞬态电流的电荷库。将低电感表面贴装陶瓷电容直接连接到IC电源引脚,便可最大程度地抑制高频电源噪声。所有去耦电容必须直接连接到低电感接地层才有效。此连接需要短走线或过孔,以便将额外串联电感降至最低。

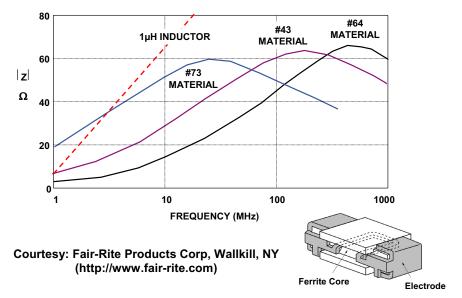

铁氧体磁珠(以镍、锌、锰的氧化物或其他化合物制造的绝缘陶瓷)也可用于在电源滤波器中去耦。铁氧体在低频下(<100 kHz)为感性,因此对低通LC滤波器有用。100 kHz以上,铁氧体成阻性(高Q)。铁氧体阻抗与材料、工作频率范围、直流偏置电流、匝数、尺寸、形状和温度成函数关系。

铁氧体磁珠并非始终必要,但可以增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会饱和,特别是在运算放大器驱动高输出电流时。当铁氧体饱和时,它就会变为非线性,失去滤波特性。

请注意,某些铁氧体甚至可能在完全饱和前就是非线性。因此,如果需要功率级,以低失 真输出工作,当原型在此饱和区域附近工作时,应检查其中的铁氧体。

图2总结了正确去耦的重要方面。

- A large electrolytic capacitor (typically 10 μF 100 μF) no more than 2 in. away from the chip.

- The purpose of this capacitor is to be a reservoir of charge to supply the instantaneous charge requirements of the circuits locally so the charge need not come through the inductance of the power trace.

- A smaller cap (typ. 0.01 μF 0.1 μF) as physically close to the power pins of the chip as is possible.

- The purpose of this capacitor is to short the high frequency noise away from the chip.

- ♦ All decoupling capacitors should connect to a large area low impedance ground plane through a via or short trace to minimize inductance.

- Optionally a small ferrite bead in series with the supply pin.

- Localizes the noise in the system.

- Keeps external high frequency noise from the IC.

- Keeps internally generated noise from propagating to the rest of the system.

图2: 何谓正确去耦?

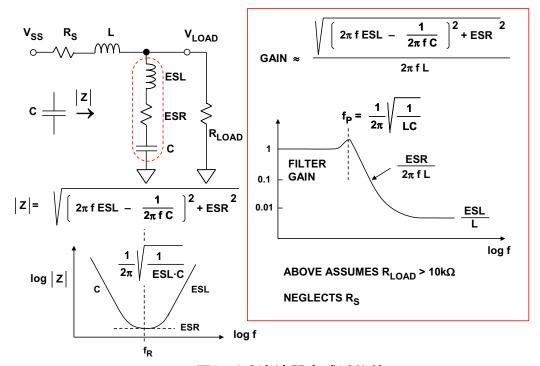

## 实际电容及其寄生效应

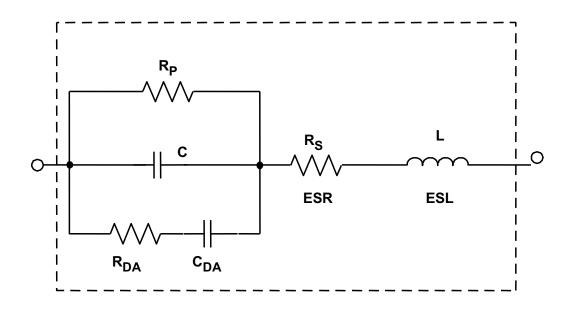

图3显示了一个非理想电容的模型。电阻R<sub>p</sub>代表绝缘电阻或泄漏,与标称电容C并联。第二个电阻R<sub>c</sub>(等效串联电阻或ESR)与电容串联,代表电容引脚和电容板的电阻。

图3: 实际电容等效电路包括寄生元件

电感L(等效串联电感或ESL)代表引脚和电容板的电感。最后,电阻R<sub>DA</sub>和电容CDA一起构成称为电介质吸收或DA现象的简化模型。在采样保持放大器(SHA)之类精密应用中使用电容时,DA可造成误差。但在去耦应用中,电容的DA一般不重要。

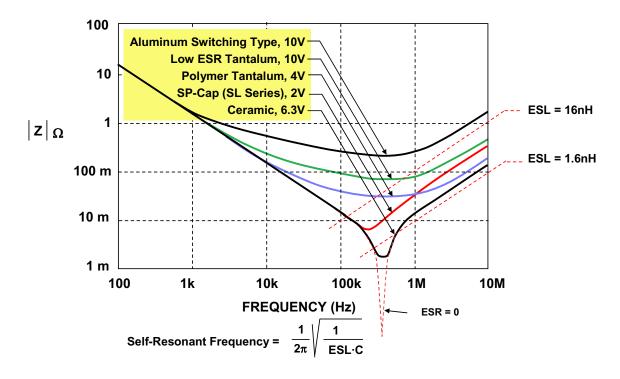

图4显示了各种100 μF电容的频率响应。理论上,电容阻抗将随着频率增加呈单调下降。实际操作中,ESR使阻抗曲线变得平坦。随着频率不断升高,阻抗由于电容的ESL而开始上升。"膝部"的位置和宽度将随着电容结构、电介质和等效器件的值而变化。因此常常可以看到较大值电容与较小值电容并联。较小值电容通常具有较低ESL,与较高频率的电容看似相同。这可以在更宽频率范围内扩展并联组合的总体性能。

图4: 各种100µF电容的阻抗

电容自谐振频率就是电容电抗 $(1/\omega C)$ 等于ESL电抗 $(\omega ESL)$ 的频率。对这一谐振频率等式求解得到下式:

$$f_{\text{RESONANCE}} = \frac{1}{2\pi\sqrt{\text{ESL}\cdot\text{C}}}$$

. 等式 1

所有电容将显示大致形状与图示类似的阻抗曲线。虽然实际曲线图有所不同,但大致形状相同。最小阻抗由ESR决定,高频区域由ESL决定(后者很大程度上受封装样式影响)。

# 去耦电容类型

图5显示适合去耦的各种常见电容类型。电解系列具有宽值范围、高电容体积比和广泛的工作电压,是极佳的高性价比低频滤波器元件。它包括通用铝电解开关类型,提供10 V以下直至约500 V的工作电压,尺寸为1 μF至数千μF(以及成比例的外形尺寸)。

44

| TECHNOLOGY                                                                  | ADVANTAGES                                                                 | DISADVANTAGES                                                               | APPLICATIONS                                                         |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------|

| Aluminum Electrolytic,<br>Switching Type.<br>Avoid general purpose<br>types | •High CV<br>product/cost<br>•Large energy storage<br>•Best for 100V - 400V | •Temperature related<br>wearout<br>•High ESR/size<br>•High ESR @ low temp   | Consumer products     Large bulk storage                             |

| Solid Tantalum                                                              | •High CV product/size •Stable @ cold temp •No wearout                      | •Fire hazard with reverse voltage •Expensive •Only rated up to 50V          | Popular in military     Concern for tantalum     raw material supply |

| Aluminum-Polymer,<br>Special-Polymer,<br>Poscap, Os-Con                     | •Low ESR •Z stable over temp •Relatively small case                        | •Rapid degradation<br>above 105°C<br>•Relatively high cost                  | •Newest technology •CPU core regulators                              |

| Ceramic                                                                     | •Lowest ESR, ESL •High ripple current •X7R good over wide temp             | CV product limited     Microphonics     C decreases with increasing voltage | •Excellent for HF<br>decoupling<br>•Good to 1GHz                     |

| Film (Polyester, Teflon, polypropylene, polystyrene, etc.                   | •Hi Q in large sizes •No wearout •High voltage                             | •CV product limited •Not popular in SMT •High cost                          | •High voltage, current •AC •Audio                                    |

图5: 常见电容类型

所有电解电容均有极性,因此无法耐受约一伏以上的反向偏置电压而不造成损坏。此类器件具有相对较高的泄漏电流(可能为数十μA),很大程度上取决于特定系列的设计、电气尺寸、额定电压及施加电压。不过,泄漏电流不可能是基本去耦应用的主要因素。

大多数去耦应用不建议使用"通用"铝电解电容。不过,铝电解电容的一个子集是"开关型",设计并规定用于在最高达数百kHz的频率下处理高脉冲电流,且仅具有低损耗。此类电容在高频滤波应用中可直接媲美固态钽电容,且具有更广泛的可用值。

固态钽电解电容一般限于50 V或更低的电压,电容为500 μF或更低。对于给定尺寸,钽电容比铝开关电解电容呈现出更高的电容体积比,且具有更高的频率范围和更低的ESR。一般也比铝电解电容更昂贵,对于浪涌和纹波电流,必须谨慎处理应用。

最近,使用有机或聚合物电解质的高性能铝电解电容也已问世。这些电容系列拥有略低于 其他电解类型的ESR和更高的频率范围,另外低温ESR下降也最小。此类器件使用铝聚合 物、特殊聚合物、Poscap和Os-Con等标签。 陶瓷或多层陶瓷(MLCC)具有尺寸紧凑和低损耗特性,通常是数MHz以上的首选电容材料。不过,陶瓷电介质特性相差很大。对于电源去耦应用,一些类型优于其他类型。在 X7R的高K电介质公式中,陶瓷电介质电容的值最高可达数μF。在高达200 V的额定电压下推荐Z5U和Y5V。X7R型在直流偏置电压下的电容变化小于Z5U和Y5V型,因此是较佳选择。

NP0(也称为COG)型使用更低的介电常数公式,通常具有零TC和低电压系数(不同于较不稳定的高K型)。NP0型的可用值限于0.1 μF或更低, 0.01 μF是更实用的上限值。

多层陶瓷(MLCC)表面贴装电容的极低电感设计可提供近乎最佳的RF旁路,因此越来越频繁地用于10 MHz或更高频率下的旁路和滤波。更小的陶瓷芯片电容工作频率范围可达1 GHz。对于高频应用中的这些及其他电容,可通过选择自谐振频率高于最高目标频率的电容,确保有效值。

薄膜型电容一般使用绕线,增加了电感,因此不适合电源去耦应用。此类型更常用于音频 应用,此时需要极低电容和电压系数。

#### 局部高频去耦建议

图6显示了高频去耦电容必须尽可能靠近芯片的情况。否则,连接走线的电感将对去耦的有效性产生不利影响。

图6:高频电源滤波器 需要通过较短的低电感路径(接地层)去耦

左图中,电源引脚和接地连接尽可能短,所以是最有效的配置。然而右图中,PCB走线内的额外电感和电阻将造成去耦方案的有效性降低,且增加封闭环路可能造成干扰问题。

#### 由LC去耦网络构成的谐振电路

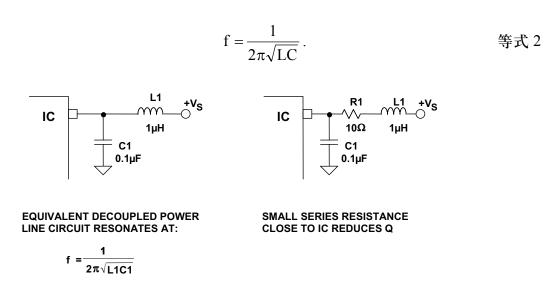

许多去耦应用中,电感或铁氧体磁珠与去耦电容串联,如图7所示。电感L与去耦电容C串联后构成谐振或"调谐"电路,主要特性是显示谐振频率下的显著阻抗变化。谐振频率计算公式如下:

图7: 由电源线路去耦构成的谐振电路

去耦网络的总体阻抗在谐振频率下可表现出峰化现象。峰化程度取决于调谐电路的相对Q(品质因子)值。谐振电路的Q衡量其对电阻的电抗。计算公式如下:

$$Q = \frac{2\pi fL}{R}.$$

等式 3

正常走线电感和0.01 μF至0.1 μF的典型去耦电容将在高于数MHz的频率下产生谐振。例如, 0.1 μF和1 nH将在16 MHz下产生谐振。

不过,由100 μF电容和1 μF电感组成的去耦网络在16 kHz下产生谐振。如果不予检查,一旦此频率出现在电源线路上,可带来谐振问题。该效应可通过降低电路Q降至最低。在电源线路内靠近IC的地方插入小电阻(~10 Ω)便可轻松完成,如右例所示。电阻应尽可能压低,最大程度地减小电阻两端的IR压降。也可用小铁氧体磁珠替代电阻,它在谐振频率下主要表现为阻性。

47

使用铁氧体磁珠代替电感可以减少谐振问题,因为铁氧体磁珠在100 kHz以上表现为阻性, 所以会降低电路的有效Q值。典型铁氧体磁珠阻抗如图8所示。

图8: 铁氧体磁珠阻抗与1µH电感的比较

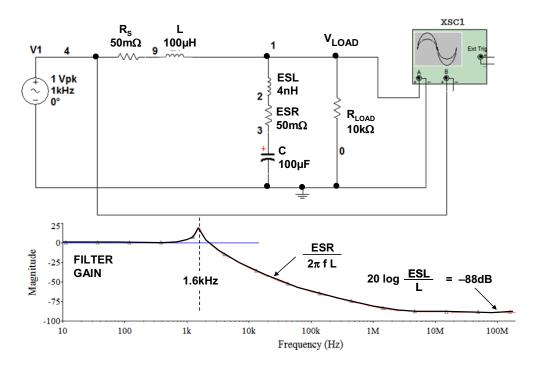

简单LRC去耦网络的响应可以使用基于SPICE的程序轻松仿真,例如National Instruments Multisim™, ADI公司版。典型电路模型如图9所示,仿真响应如图10所示。

图9: LC滤波器衰减近似值

图10: 使用NI Multisim™ Analog Devices® 版仿真LC网络增益

#### 不良去耦技术对性能的影响

本节考察不良去耦技术对两种基础元件:运算放大器和ADC的影响。

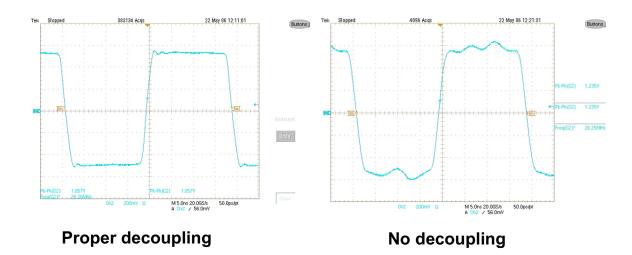

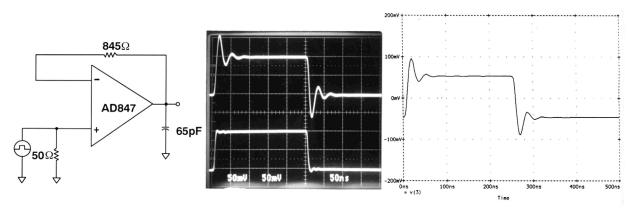

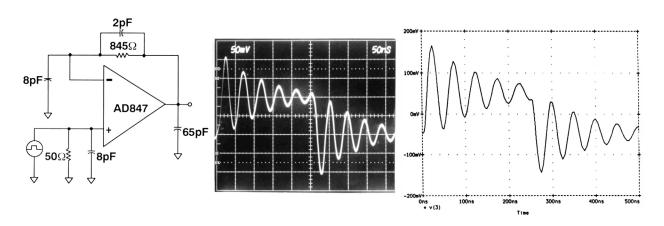

图11显示1.5 GHz高速电流反馈运算放大器 AD8000 的脉冲响应。两种示波器图表均使用评估板获得。左侧走线显示正确去耦的响应,右侧走线显示同一电路板上去除去耦电容后的相同响应。两种情况中,输出负载均为 $100~\Omega$ 。

图11: 去耦对AD8000运算放大器性能的影响

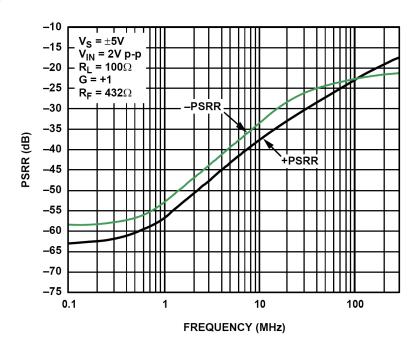

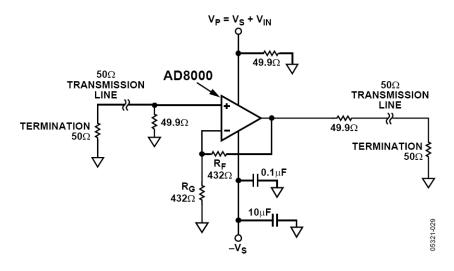

图12显示AD8000的PSRR,它与频率成函数关系。请注意,较高频率下PSRR下降至相对较低值。这意味着电源线路上的信号很容易传播至输出电路。图13显示用于测量AD8000 PSRR的电路。

图12: AD8000电源抑制比(PSRR)

图13: AD8000正PSRR测试设置

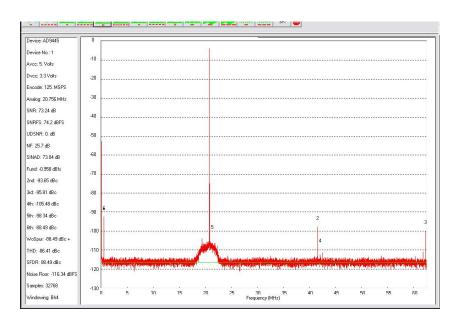

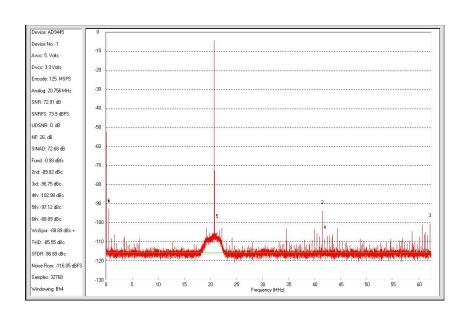

现在考察正确及错误去耦对14位、105/125MSPS高性能数据转换器ADC <u>AD9445</u>的影响。 虽然转换器通常无PSRR规格,但正确去耦仍非常重要。图14显示正确设计电路的FFT输 出。这种情况下,对AD9445使用评估板。注意频谱较为干净。

图14: 正确去耦时AD9445评估板的FFT坐标图

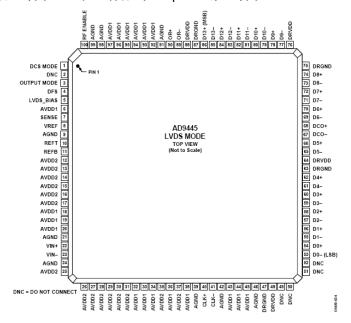

AD9445的引脚排列如图15所示。请注意,电源和接地引脚有多个。这是为了降低电源阻抗(并联引脚)。

模拟电源引脚有33个。18个引脚连接到AVDD1(电压为+3.3 V ± 5%), 15个引脚连接到AVDD2 (电压为+5 V ± 5%)。DVDD(电压为+5 V ± 5%)引脚有4个。在本实验中所用的评估板上,每个引脚具有陶瓷去耦电容。此外还有数个10 μF电解电容。

图15: AD9445引脚排列图

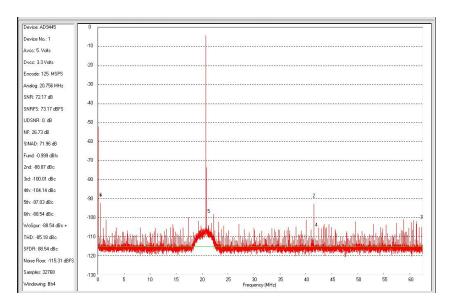

图16显示了从模拟电源去除去耦电容后的频谱。请注意,高频杂散信号增加了,还出现了一些交调产物(低频成分)。

信号SNR已显著降低。

本图与上图的唯一差异是去除了去耦电容。同样使用AD9445评估板进行测量。

图16: 从模拟电源去除电容后AD9445评估板的FFT坐标图

图17显示从数字电源去除去耦电容的结果。注意杂散同样增加了。另外应注意杂散的频率分布。这些杂散不仅出现在高频下,而且跨越整个频谱。本实验使用转换器的LVDS版本进行。

可以想象,CMOS版本会更糟糕,因为LVDS的噪声低于饱和CMOS逻辑。

图17: 从数字电源去除电容后AD9445评估板的SNR图

### 参考文献:

- 1. Henry W. Ott, *Noise Reduction Techniques in Electronic Systems, 2<sup>nd</sup> Edition*, John Wiley, Inc., 1988, ISBN: 0-471-85068-3.

- 2. Paul Brokaw, "An IC Amplifier User's Guide to Decoupling, Grounding and Making Things Go Right for a Change", <u>Analog Devices, AN-202</u>.

- 3. Paul Brokaw, "Analog Signal-Handling for High Speed and Accuracy," Analog Devices, AN-342.

- 4. Jerald Graeme and Bonnie Baker,"Design Equations Help Optimize Supply Bypassing for Op Amps," *Electronic Design, Special Analog Issue*, June 24, 1996, p.9.

- 5. Jerald Graeme and Bonnie Baker, "Fast Op Amps Demand More Than a Single-Capacitor Bypass," *Electronic Design, Special Analog Issue*, November 18, 1996, p.9.

- 6. Jeffrey S. Pattavina, "Bypassing PC Boards: Thumb Your Nose at Rules of Thumb," *EDN*, Oct. 22, 1998, p.149.

- 7. Howard W. Johnson and Martin Graham, *High-Speed Digital Design*, PTR Prentice Hall, 1993, ISBN-10: 0133957241, ISBN-13: 978-0133957242.

- 8. Ralph Morrison, *Solving Interference Problems in Electronics*, John Wiley, 1995, ISBN-10: 0471127965, ISBN-13: 978-0471127963

- 9. C. D. Motchenbacher and J. A. Connelly, Low Noise Electronic System Design, John Wiley, 1993, ISBN-10: 0471577421, ISBN-13: 978-0471577423.

- 10. Mark Montrose, *EMC and the Printed Circuit Board*, Wiley-IEEE Press, 1999, ISBN-10: 078034703X, ISBN-13: 978-0780347038.

- 11. Bonnie Baker, A Baker's Dozen: Real Analog Solutions for Digital Designers, Elsevier/Newnes, 2005, ISBN-10: 0750678194, ISBN-13: 978-0750678193.

- 12. Jerald Graeme, *Optimizing Op Amp Performance*, McGraw Hill, 1996, ISBN-10: 0070245223, ISBN-13: 978-0070245228.

- Tamara Schmitz and Mike Wong, <u>Choosing and Using Bypass Capacitors (Part 1 of 3)</u>, <u>Planet Analog</u>, June 19, 2007.

- Tamara Schmitz and Mike Wong, <u>Choosing and Using Bypass Capacitors (Part 2 of 3)</u>, <u>Planet Analog</u>, June 21, 2007.

- 15. Tamara Schmitz and Mike Wong, <u>Choosing and Using Bypass Capacitors (Part 2 of 3)</u>, <u>Planet Analog</u>, June 27, 2007.

- 16. Yun Chase, "Introduction to Choosing MLC Capacitors for Bypass/Decoupling Applications," AVX Corporation, Myrtle Beach, SC.

- 17. Panasonic SP-Capacitor Technical Guide, Panasonic, Inc.

- 18. National Instruments Multisim<sup>TM</sup>, Analog Devices' Edition

- 19. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

- 20. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Chapter 7. Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 7.

- 21. Walt Kester, *High Speed System Applications*, Analog Devices, 2006, ISBN-10: 1-56619-909-3, ISBN-13: 978-1-56619-909-4, Part 4.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

## 实现数据转换器的接地并解开"AGND"和"DGND"的谜团

作者: Walt Kester、James Bryant、Mike Byrne

## 简介

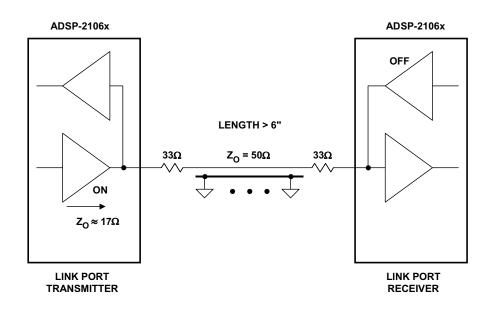

目前的信号处理系统一般需要混合信号器件,例如模数转换器(ADC)、数模转换器(DAC)和快速数字信号处理器(DSP)。由于需要处理宽动态范围的模拟信号,因此拥有高性能ADC和DAC显得更加重要。在恶劣的数字环境内,能否保持宽动态范围和低噪声与采用良好的高速电路设计技术密切相关,包括适当的信号路由、去耦和接地。

过去,一般认为"高精度、低速"电路与所谓的"高速"电路有所不同。对于ADC和DAC,采样(或更新)频率一般用作区分速度标准。不过,以下两个示例显示,实际操作中,目前大多数信号处理IC真正实现了"高速",因此必须作为此类器件来对待,才能保持高性能。DSP、ADC和DAC均是如此。

所有适合信号处理应用的采样ADC(内置采样保持电路的ADC)均采用具有快速上升和下降时间(一般为数纳秒)的高速时钟工作,即使吞吐量看似较低也必须视为高速器件。例如,中速12位逐次逼近型(SAR) ADC可采用10 MHz内部时钟工作,而采样速率仅为500 kSPS。

$\Sigma$ - $\Delta$ 型ADC具有高过采样比,因此还需要高速时钟。即使是高分辨率、所谓的"低频" $\Sigma$ - $\Delta$ 工业测量ADC(吞吐速率10 Hz至7.5 kHz)也采用5 MHz或更高时钟工作,并且提供高达24位的分辨率(例如ADI公司的AD77xx系列)。

更复杂的是,混合信号IC具有模拟和数字两种端口,因此如何使用适当的接地技术就更加茫然。此外,某些混合信号IC具有相对较低的数字电流,而另一些具有高数字电流。许多情况下,两种类型必须区分对待,才能实现最佳接地。

数字和模拟设计工程师倾向于从不同角度考察混合信号器件,本教程旨在确立适用于大多数混合信号器件的一般接地原则,而不必了解内部电路的具体细节。

### 接地层和电源层

保持低阻抗大面积接地层对目前所有的模拟和数字电路都很重要。接地层不仅用作去耦高频电流(源于快速数字逻辑)的低阻抗返回路径,还能将EMI/RFI辐射降至最低。由于接地层的屏蔽作用,电路受外部EMI/RFI的影响也会降低。

接地层还允许使用传输线路技术(微带线或带状线)传输高速数字或模拟信号,此类技术需要可控阻抗。

由于"母线(buss wire)"在大多数逻辑转换等效频率下具有阻抗,将其用作"地"完全不能接受。例如,#22标准导线具有约20 nH/英寸的电感。由逻辑信号产生的压摆率为10 mA/ns的瞬态电流,在此频率下流经1英寸该导线将形成200 mV的无用压降:

$$\Delta v = L \frac{\Delta i}{\Delta t} = 20 \text{ nH} \times \frac{10 \text{ mA}}{\text{ns}} = 200 \text{ mV}.$$

\$\times \tilde{\textstyle \textstyle \textstyle

对于具有2 V峰峰值范围的信号,此压降会转化为约10%的误差(大约3.5位精度)。即使在全数字电路中,该误差也会大幅降低逻辑噪声裕量。

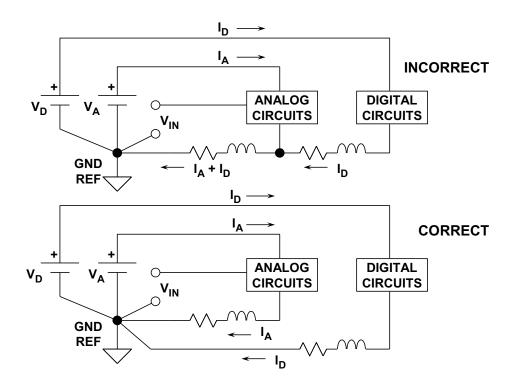

图1为数字返回电流调制模拟返回电流的典型情况(顶图)。接地返回导线电感和电阻由模拟和数字电路共享,这会造成相互影响,最终产生误差。一个可能的解决方案是让数字返回电流路径直接流向GND REF,如底图所示。这就是"星型"或单点接地系统的基本概念。在包含多个高频返回路径的系统中很难实现真正的单点接地,因为各返回电流导线的物理长度将引入寄生电阻和电感,所以获得低阻抗高频接地就很困难。实际操作中,电流回路必须由大面积接地层组成,以便实现高频电流下的低阻抗。如果无低阻抗接地层,则几乎不可能避免上述共享阻抗,特别是在高频下。

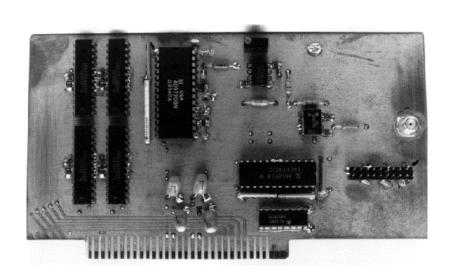

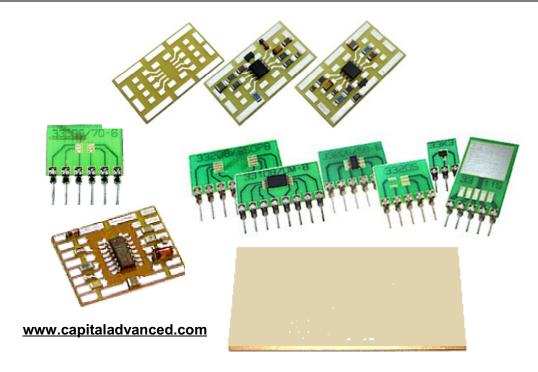

图1:流入模拟返回路径的数字电流产生误差电压

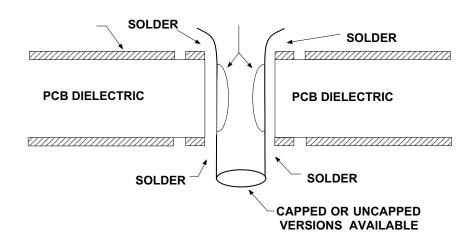

所有集成电路接地引脚应直接焊接到低阻抗接地层,从而将串联电感和电阻降至最低。对于高速器件,不推荐使用传统IC插槽。即使是"小尺寸"插槽,额外电感和电容也可能引入无用的共享路径,从而破坏器件性能。如果插槽必须配合DIP封装使用,例如在制作原型时,个别"引脚插槽"或"笼式插座"是可以接受的。以上引脚插槽提供封盖和无封盖两种版本(AMP产品型号5-330808-3和5-330808-6)。由于使用弹簧加载金触点,确保了IC引脚具有良好的电气和机械连接。不过,反复插拔可能降低其性能。

### 低频和高频去耦

每个电源在进入PC板时,应通过高质量电解电容去耦至低阻抗接地层。这样可以将电源 线路上的低频噪声降至最低。在每个独立的模拟级,各IC封装电源引脚需要更局部、仅 针对高频的滤波。

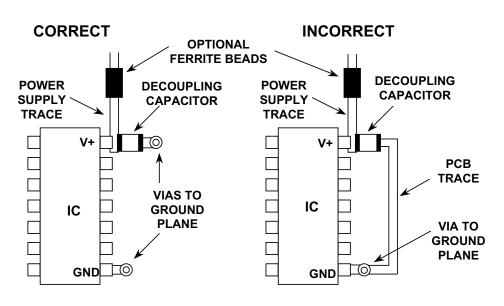

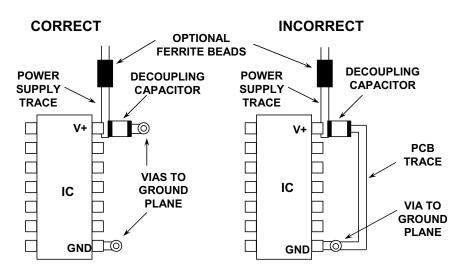

图2显示了此技术,图示左侧为正确实施方案,右侧为错误实施方案。左侧示例中,典型的0.1 μF芯片陶瓷电容借助过孔直接连接到PCB背面的接地层,并通过第二个过孔连接到IC的GND引脚上。相比之下,右侧的设置不太理想,给去耦电容的接地路径增加了额外的PCB走线电感,使有效性降低。

图2: 局部高频电源滤波器通过较短的低电感路径(接地层)提供最佳滤波和去耦

所有高频(即≥10 MHz)IC应使用类似于图2的旁路方案实现最佳性能。铁氧体磁珠并非100%必要,但会增强高频噪声隔离和去耦,通常较为有利。这里可能需要验证磁珠永远不会在IC处理高电流时饱和。

请注意,对于一些铁氧体,即使在完全饱和前,部分磁珠也可能变成非线性,所以如果需要功率级在低失真输出下工作,应检查这一点。

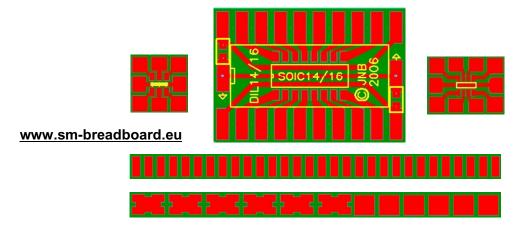

### 双面和多层印刷电路板

系统内的每个PCB至少应有完整的一层专用于接地层。理想情况下,双面电路板的一面 应完全用于接地层,另一面用于互连。但在实际操作中,这不可能,因为必须去除部分 接地层,用于配置信号和电源跨越、过孔和通孔。尽管如此,还是应尽可能节约面积,至少保留75%。完成初始布局后,请仔细检查接地层,确保没有隔离的接地"孤岛",因为 位于接地"孤岛"内的IC接地引脚没有通向接地层的电流返回路径。另外应检查接地层的相 邻大面积间有无薄弱连接,否则可能大幅降低接地层有效性。毫无疑问,自动路由电路 板布局技术一般不适合混合信号电路板上的布局,因此强烈建议手动干预。

用表面贴装IC高密度集成的系统有大量互连,必须使用多层电路板。这样,至少一整层可专用于接地。简单的4层电路板有内部接地和电源层,外面两层用于表面贴装元件的互连。电源层和接地层彼此相邻可以提供额外的层间电容,有助于电源的高频去耦。大多数系统中,4层也嫌不足,还需要其他层用于信号和电源的路由。

## 多卡混合信号系统

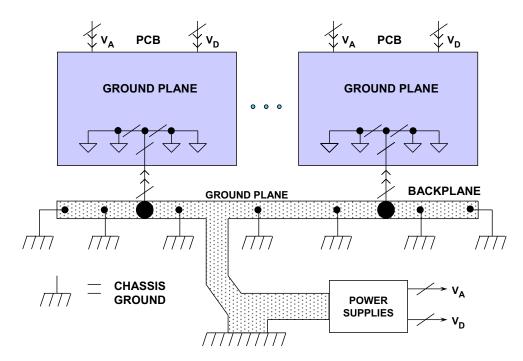

在多卡系统中,降低接地阻抗的最佳方式是使用"母板"PCB作为卡间互连背板,从而为背板提供连续接地层。PCB连接器的引脚应至少有30至40%专用于接地,这些引脚应连接到背板母板上的接地层。最后,实现整体系统接地方案有两种可能途径:

- 1. 背板接地层可通过多个点连接到机壳接地,从而扩散各种接地电流返回路径。该方 法通常称为"多点"接地系统,如图3所示。

- 2. 接地层可连接到单个系统"星型接地"点(一般位于电源)。

前一个方法最常用于全数字系统,不过,只要数字电路引起的接地电流足够低且扩散到 大面积上,也可用于混合信号系统。PC板、背板直到机壳都一直保持低接地阻抗。不 过,接地与金属板壳连接的部位必须具有良好的电气接触。这需要自攻金属板螺丝或"咬 合"垫圈。机壳材料使用阳极氧化铝时必须特别小心,此时机壳表面用作绝缘体。

图3: 多点接地概念

59

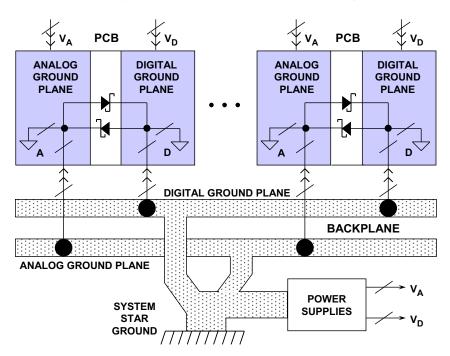

第二种方法("星型接地")通常用于模拟和数字接地系统相互分离的高速混合信号系统,需进一步讨论。

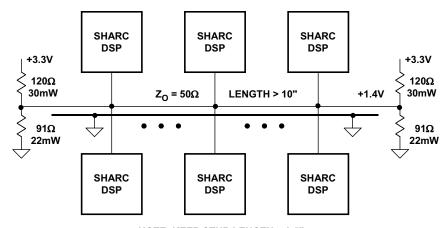

### 分离模拟和数字接地层

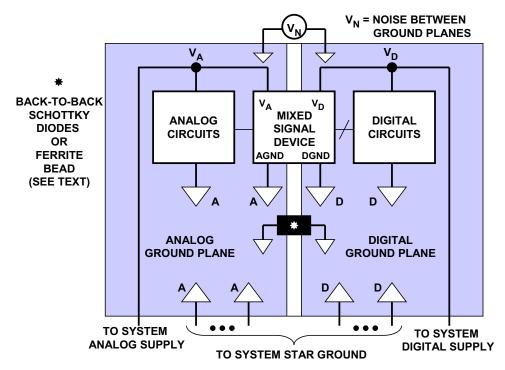

在使用大量数字电路的混合信号系统中,最好在物理上分离敏感的模拟元件与多噪声的数字元件。另外针对模拟和数字电路使用分离的接地层也很有利。避免重叠可以将两者间的容性耦合降至最低。分离的模拟和数字接地层通过母板接地层或"接地网"(由连接器接地引脚间的一连串有线互连构成),在背板上继续延伸。如图4所示,两层一直保持分离,直至回到共同的系统"星型"接地,一般位于电源。接地层、电源和"星型"接地间的连接应由多个总线条或宽铜织带构成,以便获得最小的电阻和电感。每个PCB上插入背对背肖特基二极管,以防止插拔卡时两个接地系统间产生意外直流电压。此电压应小于300 mV,以免损坏同时与模拟和数字接地层相连的IC。推荐使用肖特基二极管,它具有低电容和低正向压降。低电容可防止模拟与数字接地层间发生交流耦合。肖特基二极管在约300 mV时开始导电,如果预期有高电流,可能需要数个并联的二极管。某些情况下,铁氧体磁珠可替代肖特基二极管,但会引入直流接地环路,在高精度系统中会很麻烦。

图4: 分离模拟和数字接地层

接地层阻抗必须尽可能低,直至回到系统星型接地。两个接地层间高于300 mV的直流或 交流电压不仅会损坏IC,还会导致逻辑门的误触发以及可能的闭锁。

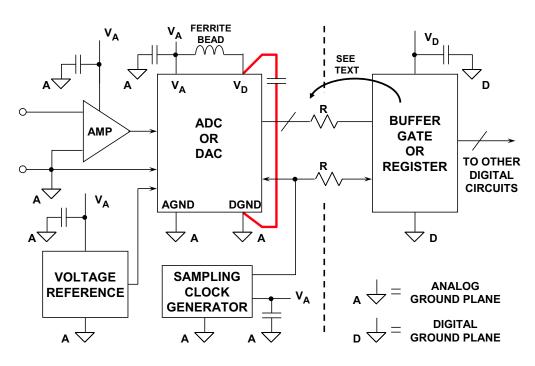

### 具有低数字电流的接地和去耦混合信号IC

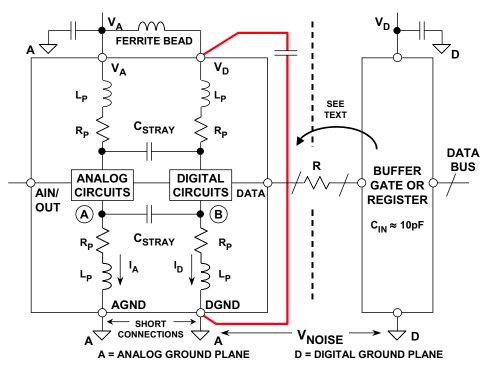

敏感的模拟元件,例如放大器和基准电压源,必须参考和去耦至模拟接地层。具有低数字电流的ADC和DAC(和其他混合信号IC)一般应视为模拟元件,同样接地并去耦至模拟接地层。乍看之下,这一要求似乎有些矛盾,因为转换器具有模拟和数字接口,且通常有指定为模拟接地(AGND)和数字接地(DGND)的引脚。图5中的图示有助于解释这一表面困境。

图5: 具有低内部数字电流的混合信号IC的正确接地

同时具有模拟和数字电路的IC(例如ADC或DAC)内部,接地通常保持独立,以免将数字信号耦合至模拟电路内。图5显示了一个简单的转换器模型。将芯片焊盘连接到封装引脚难免产生线焊电感和电阻,IC设计人员对此是无能为力的,心中清楚即可。快速变化的数字电流在B点产生电压,且必然会通过杂散电容C<sub>STRAY</sub>耦合至模拟电路的A点。此外,IC 封装每个引脚间约有0.2 pF的杂散电容,同样无法避免! IC设计人员的任务是排除此影响让芯片正常工作。不过,为了防止进一步耦合,AGND和DGND应通过最短的引线在外部连在一起,并接到模拟接地层。DGND连接内的任何额外阻抗将在B点产生更多数字噪声;继而使更多数字噪声通过杂散电容耦合至模拟电路。请注意,将DGND连接到数字接地层会在AGND和DGND引脚两端施加V<sub>NOISE</sub>,带来严重问题!

IC上的"DGND"名称表示此引脚连接到IC的数字地,但并不意味着此引脚必须连接到系统的数字地。

这种安排确实可能给模拟接地层注入少量数字噪声。但这些电流非常小,只要确保转换器输出不会驱动较大扇出(通常不会如此设计)就能降至最低。将转换器数字端口上的扇出降至最低,还能让转换器逻辑转换少受振铃影响,尽可能减少数字开关电流,从而降低耦合至转换器模拟端口的可能。通过插入小型有损铁氧体磁珠,如图5所示,逻辑电源引脚( $V_D$ )可进一步与模拟电源隔离。转换器的内部瞬态数字电流将在小环路内流动,从 $V_D$  经去耦电容到达DGND(此路径用图中粗实线表示)。因此瞬态数字电流不会出现在外部模拟接地层上,而是局限于环路内。 $V_D$ 引脚去耦电容应尽可能靠近转换器安装,以便将寄生电感降至最低。这些去耦电容应为低电感陶瓷型,通常介于0.01  $\mu$ F和0.1  $\mu$ F之间。

## 小心对待ADC数字输出

将缓冲寄存器放置在转换器旁(如图5所示)不失为好办法,可将转换器数字线路与数据总线上的噪声隔离开。寄存器也有助于将转换器数字输出上的负载降至最低,同时提供数字输出与数据总线间的法拉第屏蔽。尽管许多转换器具有三态输出/输入,但此隔离寄存器依然代表着一种良好的设计方式。某些情况下,可能需要在模拟接地层上紧靠转换器输出添加额外的缓冲寄存器,以提供更好的隔离。

ADC输出与缓冲寄存器输入间的串联电阻(图5中标示为"R")有助于将数字瞬态电流降至最低,这些电流可能影响转换器性能。电阻可将数字输出驱动器与缓冲寄存器输入的电容隔离开。此外,由串联电阻和缓冲寄存器输入电容构成的RC网络用作低通滤波器,以减缓快速边沿。

典型CMOS栅极与PCB走线和通孔结合在一起,将产生约10 pF的负载。如果无隔离电阻,1 V/ns的逻辑输出压摆率将产生10 mA的动态电流:

$$\Delta I = C \frac{\Delta v}{\Delta t} = 10 \text{ pF} \times \frac{1 \text{ V}}{\text{ns}} = 10 \text{ mA}.$$

\$\text{\$\times \pi 2}\$

驱动10 pF的寄存器输入电容时,500 Ω串联电阻可将此输出电流降至最低,并产生约11 ns的上升和下降时间:

$$t_r = 2.2 \times \tau = 2.2 \times R \cdot C = 2.2 \times 500 \Omega \times 10 \text{ pF} = 11 \text{ ns}.$$

公式3

TTL寄存器具有较高输入电容,可略微增加动态开关电流,应避免使用。

缓冲寄存器和其他数字电路应接地并去耦至PC板的数字接地层。请注意,模拟与数字接地层间的任何噪声均可降低转换器数字接口上的噪声裕量。由于数字噪声抗扰度在数百或数千毫伏水平,因此一般不太可能有问题。模拟接地层噪声通常不高,但如果数字接地层上的噪声(相对于模拟接地层)超过数百毫伏,则应采取措施减小数字接地层阻抗,从而将数字噪声裕量保持在可接受的水平。任何情况下,两个接地层之间的电压不得超过300 mV,否则IC可能受损。

另外最好分离模拟与数字电路的电源,即使两者电压相同。模拟电源应当用于为转换器供电。如果转换器具有指定的数字电源引脚 $(V_D)$ ,应采用独立模拟电源供电,或者如图所示进行滤波。所有转换器电源引脚应去耦至模拟接地层,所有逻辑电路电源引脚应去耦至数字接地层,如图6所示。

图6:接地和去耦点

某些情况下,不可能将V<sub>D</sub>连接到模拟电源。一些较新的高速IC可能采用+5 V电源为模拟电路供电,而采用+3 V电源为数字接口供电,以便与3 V逻辑接口。这种情况下,IC的+3 V引脚应直接去耦至模拟接地层。另外建议将铁氧体磁珠与电源走线串联,以便将引脚连接到+3 V数字逻辑电源。

采样时钟产生电路应与模拟电路同样对待,也接地并深度去耦至模拟接地层。采样时钟上的相位噪声会降低系统SNR,下文将予以讨论。

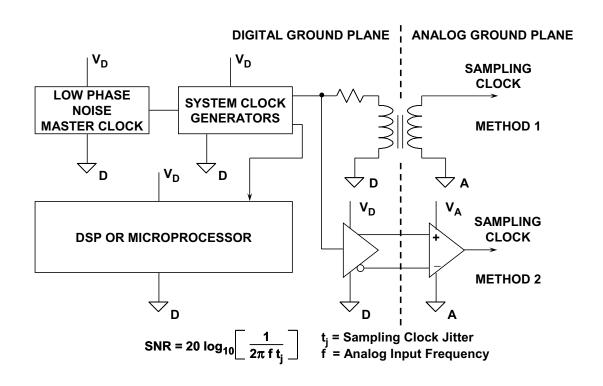

### 采样时钟考量

在高性能采样数据系统中,应使用低相位噪声振荡器产生ADC(或DAC)采样时钟,因为采样时钟抖动会调制模拟输入/输出信号,并提高噪声和失真底。采样时钟发生器应与高噪声数字电路隔离开,同时接地并去耦至模拟接地层,与处理运算放大器和ADC一样。

采样时钟抖动对ADC信噪比的(SNR)影响可用以下公式近似计算:

$$SNR = 20 \log_{10} \left[ \frac{1}{2\pi \text{ft}_{j}} \right],$$

公式4

其中SNR是完美无限分辨率ADC的SNR,此时唯一的噪声源来自均方根采样时钟抖动tj。注意,以上公式中的f是模拟输入频率。通过简单示例可知,如果tj=50 ps rms,f=100 kHz,则SNR=90 dB,相当于约15位的动态范围。时钟抖动对SNR的这一影响在<u>教程MT-007</u>中有详细论述。

应注意,以上示例中的t<sub>j</sub>是外部时钟抖动和内部ADC时钟抖动(称为孔径抖动)的方和根 (rss)值。不过,在大多数高性能ADC中,内部孔径抖动与采样时钟上的抖动相比可以忽略。

理想情况下,采样时钟振荡器应参考分离接地系统中的模拟接地层。不过由于系统限制,此方法未必可行。许多情况下,采样时钟必须从数字接地层上产生的更高频率、多用途系统时钟获得,接着必须从数字接地层上的原点传递至模拟接地层上的ADC。两层之间的接地噪声直接添加到时钟信号,并产生过度抖动。抖动可造成信噪比降低,还会产生干扰谐波。

通过使用图7所示的小RF变压器或高速差分驱动器和接收机IC,发射采样时钟信号作为差分信号,可在某种程度上解决此问题。许多高速ADC具有差分采样时钟输入,更便于采用此方法。如果使用有源差分驱动器和接收机,应选择ECL、低电平ECL或LVDS,从而将相位抖动降至最低。在+5 V单电源系统中,ECL逻辑可连接在地与+5 V(PECL)电源之间,并将输出交流耦合至ADC采样时钟输入。不管是哪种情况,原始主系统时钟必须从低相位噪声振荡器产生,而不是DSP、微处理器或微控制器的时钟输出。

为了促进系统时钟管理,ADI公司提供一系列时钟产生和分配产品和全套锁相环(PLL)。

图7: 从数模接地层进行采样时钟分配

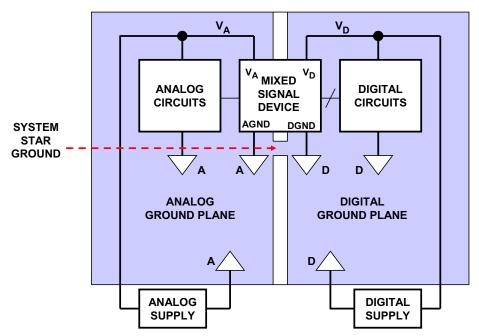

# 混合信号接地的困惑根源:对多卡系统应用单卡接地概念

大多数ADC、DAC和其他混合信号器件数据手册是针对单个PCB讨论接地,通常是制造商自己的评估板。将这些原理应用于多卡或多ADC/DAC系统时,就会让人感觉困惑茫然。通常建议将PCB接地层分为模拟层和数字层。另外建议将转换器的AGND和DGND引脚连接在一起,并且在同一点连接模拟接地层和数字接地层,如图8所示。这样就基本在混合信号器件上产生了系统"星型"接地。

所有高噪声数字电流通过数字电源流入数字接地层,再返回数字电源,与电路板敏感的模拟部分隔离开。系统星型接地结构出现在混合信号器件中模拟和数字接地层连接在一起的位置。该方法一般用于具有单个PCB和单个ADC/DAC的简单系统,通常不适合多卡混合信号系统。在不同PCB(或适用情况的相同PCB上)上具有数个ADC或DAC的系统中,模拟和数字接地层在数个点连接,使得建立接地环路成为可能,而单点"星型"接地系统则不可能。鉴于以上原因,此接地方法不适用于多卡系统,上述方法应当用于具有低数字电流的混合信号IC。

图8: 混合信号IC接地: 单个PC板(典型评估/测试板)

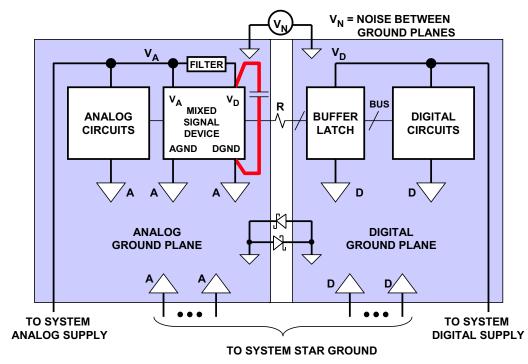

# 总结: 多卡系统中具有低数字电流的混合信号器件的接地

图9总结了上述具有低数字电流的混合信号器件的接地方法。由于小数字瞬态电流流入去 耦电容 $V_D$ 与DGND(显示为粗实线)间的小环路,模拟接地层未被破坏。混合信号器件适合 作为模拟元件的所有应用。接地层间的噪声 $V_N$ 会降低数字接口上的噪声裕量,但如果使用低阻抗数字接地层保持在300 mV以下,且一直回到系统星型接地,则一般无不利影响。

不过, $\Sigma$ - $\Delta$ 型ADC、编解码器和DSP等具有片内模拟功能的混合信号器件数字化密集度越来越高。再加上其他数字电路,使数字电流和噪声越来越大。例如, $\Sigma$ - $\Delta$ 型ADC或DAC含有复杂的数字滤波器,会大量增加器件内的数字电流。上述方法依靠 $V_D$ 与DGND间的去耦电容,将数字瞬态电流隔离在小环路内。不过,如果数字电流太大,且具有直流或低频成分,去耦电容可能因过大而变得不可行。在 $V_D$ 与DGND间的环路外流动的任何数字电流必须流经模拟接地层。这可能会降低性能,特别是在高分辨率系统中。

图9: 具有低内部数字电流的混合信号IC的接地: 多个PC板

要预测流入模拟接地层的多大数字电流会让系统无法接受很困难。目前我们只能推荐可能提供较佳性能的替代接地方法。

## 总结: 多卡系统中具有高数字电流的混合信号器件的接地(请谨慎使用本方法!)

图10中显示了适合高数字电流混合信号器件的替代接地方法。混合信号器件的AGND连接到模拟接地层,而DGND连接到数字接地层。数字电流与模拟接地层隔离开,但两个接地层之间的噪声直接施加于器件的AGND与DGND引脚间。为了成功实施本方法,混合信号器件内的模拟和数字电路必须充分隔离。

AGND与DGND引脚间的噪声不得过大,以免降低内部噪声裕量或损坏内部模拟电路。

图10显示可选用连接模拟和数字接地层的肖特基二极管(背对背)或铁氧体磁珠。肖特基二极管可防止两层两端产生大的直流电压或低频电压尖峰。如果这些电压超过300 mV,由于是直接出现在AGND与DGND引脚之间,可能会损坏混合信号IC。作为背对背肖特基二极管的备选器件,铁氧体磁珠可在两层间提供直流连接,但在高于数MHz的频率下,由于铁氧体磁珠变为电阻,会导致隔离。这可以保护IC不受AGND与DGND间直流电压的影响,但铁氧体磁珠提供的直流连接可能引入无用的直流接地环路,因此可能不适合高分辨率系统。

图10: 具有高数字电流的混合信号IC的替代接地法: 多个PC板

AGND与DGND引脚在具有高数字电流的特殊IC内分离时,必要时应设法将其连接在一起。通过跳线和/或带线选项,可以尝试两种方法,看看哪一种提供最佳的系统整体性能。

### 接地总结

没有单一一种接地方法能始终保证最佳性能!本节根据所考虑的特定混合信号器件特性提出了几种可能的选项。但在实施初始PC板布局时,提供尽可能多的选项会很有帮助。

PC板必须至少有一层专用于接地层! 初始电路板布局应提供非重叠的模拟和数字接地层,如果需要,应在数个位置提供焊盘和过孔,以便安装背对背肖特基二极管或铁氧体磁珠。提供焊盘和过孔也极为重要,需要时可以使用跳线将模拟和数字接地层连接在一起。目前,预测"多点"(单一接地层)还是"星型"接地(分离模拟和数字接地层)方法能提供最佳整体系统性能还很困难,因此,可能需要使用跳线对最终PC板做一些实验。

如有疑问,最好先分离模拟和数字接地层,以后再用跳线连接,而不要一开始就使用单一接地层,随后又尝试分离!

#### 混合信号系统的一些通用PC板布局指南

很显然,多关注系统布局并防止不同信号彼此干扰,可以将噪声降至最低。高电平模拟信号应与低电平模拟信号隔离开,两者均应远离数字信号。我们曾经在波形采样和重建系统中发现,采样时钟(数字信号)与模拟信号一样易受噪声影响,同时与数字信号一样易于产生噪声,因此必须与模拟和数字系统都隔离开。如果在时钟分配中使用时钟驱动器封装,应仅有一个频率时钟通过单个封装。在相同封装内的不同频率时钟间共享驱动器将产生过度抖动和串扰,并降低性能。

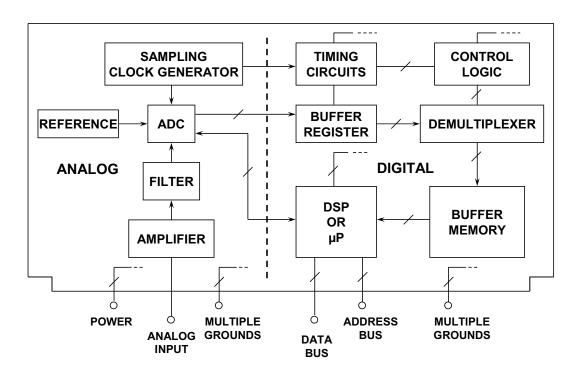

在敏感信号穿过的地方,接地层可发挥屏蔽作用。图11显示了数据采集电路板的良好布局,其中所有敏感区域彼此隔离开,且信号路径尽量短。虽然实际布局不太可能如此整洁,但基本原则仍然适用。

执行信号和电源连接时有许多要点需要考虑。首先,连接器是系统中所有信号传输线必须并行的几个位置之一,因此它们必须与接地引脚分开(形成法拉第屏蔽),以减少其间的耦合。

多接地引脚非常重要还有另一原因:可以降低电路板与背板间结点的接地阻抗。对于新电路板,PCB连接器单一引脚的接触电阻很低(10 mΩ水平),随着电路板变旧,接触电阻可能升高,电路板性能会受影响。因此通过分配额外PCB连接器引脚来增加接地连接很有必要(PCB连接器上所有引脚中约30至40%应为接地引脚)。出于同样的理由,每个电源连接应有数个引脚,当然数量不必像接地引脚一样多。

图11: 在PCB布局中应将模拟和数字电路分开

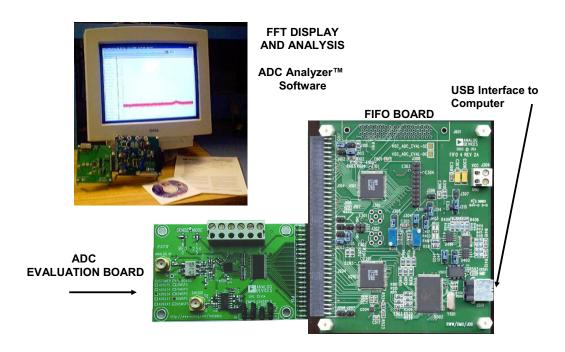

ADI公司和其他高性能混合信号IC制造商提供评估板来协助客户进行初始评估和布局。 ADC评估板一般包含片上低抖动采样时钟振荡器、输出寄存器和适当的电源和信号连接器。另外还有额外的支持电路,例如ADC输入缓冲放大器和外部基准电压。

评估板布局已针对接地、去耦和信号路由进行优化,可用作系统内ADC PC板布局的模型。实际评估板布局通常由ADC制造商以电脑CAD文件形式(Gerber文件)提供。许多情况下,器件数据手册都会提供各层的布局。

# 参考文献

- 1. Ralph Morrison, Grounding and Shielding Techniques, 4<sup>th</sup> Edition, John Wiley, Inc., 1998, ISBN: 0471245186.

- 2. Henry W. Ott, *Noise Reduction Techniques in Electronic Systems*, 2<sup>nd</sup> Edition, John Wiley, Inc., 1988, ISBN: 0-471-85068-3.

- 3. Paul Brokaw, "An IC Amplifier User's Guide to Decoupling, Grounding and Making Things Go Right for a Change", Analog Devices Application Note <u>AN-202</u>.

- 4. Paul Brokaw and Jeff Barrow, "Grounding for Low- and High-Frequency Circuits," Analog Devices Application Note <u>AN-345</u>.

- 5. Howard W. Johnson and Martin Graham, *High-Speed Digital Design*, PTR Prentice Hall, 1993, ISBN: 0133957241.

- 6. Ralph Morrison, Solving Interference Problems in Electronics, John Wiley, 1995.

- 7. Crystal Oscillators: MF Electronics, 10 Commerce Drive, New Rochelle, NY, 10801, 914-576-6570.

- 8. Mark Montrose, EMC and the Printed Circuit Board, IEEE Press, 1999 (IEEE Order Number PC5756).

- 9. John Ardizzoni, "A Practical Guide to High-Speed Printed-Circuit-Board Layout," Analog Dialogue, Vol. 39, Sept. 2005.

- 10. Grant, Doug and Scott Wurcer, "Avoiding Passive-Component Pitfalls," Analog Devices Application Note <u>AN-348</u>

- 11. Walt Kester, *Analog-Digital Conversion*, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as *The Data Conversion Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

亚洲技术支持中心・电话: 4006-100-006・电子邮箱: china.support@analog.com・网址: www.analog.com

# 工程经理初次使用Multisim

作者: 佚名, ADI公司

#### 引言

本文以第一人称讲述ADI公司经理初次使用NI Multisim™ 器件评估软件——Analog Devices™版仿真工具设计简 单运算放大器的过程。

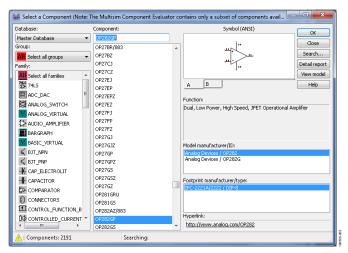

#### 简介

作为一名在模拟电路领域有着几十年经验的工程经理,我迄今为止还没有用过SPICE或其它仿真软件,说起来有些惭愧。最近,我在电脑上安装了Analog Devices版的Multisim,下面我要尝试能否设计出一个简单可行的运算放大器电路。我锁好办公室大门,打开Multisim,开始探索模拟仿真世界。

#### 开始使用

当然, Multisim的"Help(帮助)"菜单下有各种指南; 但是, 和大多数工程师一样, 我决定跳过这一步, 直接进入程序。难度会有多大?

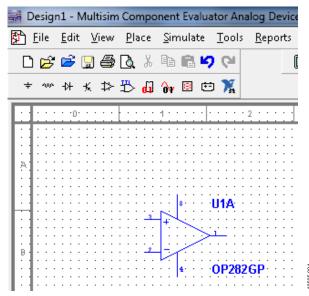

打开程序,先看一下菜单。不妨先从"Place(放置)"菜单项(见图1)入手。

图1. Multisim菜单工具栏

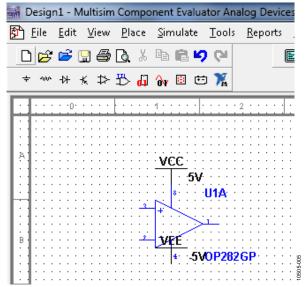

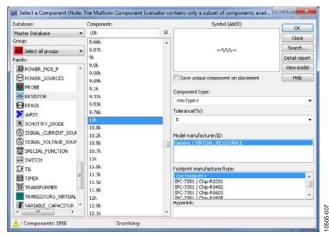

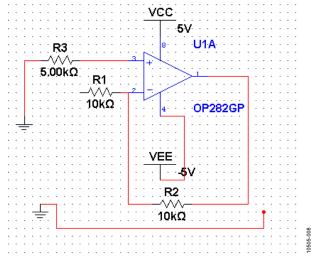

单击"Place(放置)"后,选择"Component(器件)"菜单(见图 2),现在可以选择运算放大器了,我选中了OP282GP。

图2 选择运算放大器

#### 选择器件

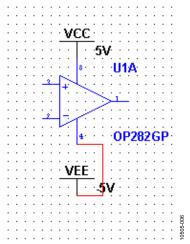

现在,选择屏幕上显示的其中一个字母(A或B)(见图3)。这些字母似乎是表示放大器的不同通道(虽然这是一个双通道运算放大器),我选择A。目前为止,一切顺利。接下来,会弹出另一个窗口,显示更多可选的同一器件。单击"Cancel(取消)",因为现在选择一项已经足够了。屏幕最后显示图4的画面。

图3. 去除双运算放大器中的第二个运算放大器

# **MT-226**

图4. 准备接受更多连接的单运算放大器

接着,我注意到有很多方法可以放置器件。在网格的任意位置右击,就会显示一个窗口,可以轻松"Select a Component(选择一个器件)",如图2所示。

现在可以考虑保存了。我保存好文件,将电路命名为AMP Block1。

#### 连接电源

看着屏幕上显示的器件,我决定连接电源。我没有看到能提供电源的菜单,不过后来我发现可以通过"Component (器件)"菜单完成。

右击菜单栏时,跳出一个下拉框,可以选择电源器件。我不大清楚怎么操作,就把光标移到可能的电源上。一个是"数字地",另一个是"地"。我知道需要模拟地,于是就选择了"地"。然后放在图中。

接下来,选择VCC,再单击放大器的引脚8;它会自动连接。VEE应该也是这样操作。确实如此,但是放在了引脚4线路上方,看起来有些别扭(见图5)。把它拖到下方后,看着顺眼些(见图6)。电源上已经有了+和-5 V。有了这些值后,器件就可以工作了,于是我暂时将其搁置。

图5. 第一次尝试连接VEE

图6. 拖放VEE, 使得看着顺眼些

#### 增加申阻

我所关注的是放大器,反相增益放大器就比较简单,下面我要增加一些电阻。同样,还是用之前选择放大器的 "Place(放置)"菜单。但是,我发现屏幕的左侧有各种器件可供选择。我从"Family(系列)"中选择"RESISTOR(电阻)"(见图7),阻值选择"10 kΩ",然后单击"OK(确认)",放置电阻,连接至引脚2。菜单自动弹出,我在同一个节点上又放置了另一个10 kΩ的电阻。菜单又一次弹出。虽然这是一个JFET运算放大器,但是同相输入还需要一个电阻,我选择了一个5 kΩ的电阻,本来没有它我可以做得更好。稍后可以检查这么做是否增加了噪声,究竟是不是正确的决定。

图7. 选择电阻值

现在可以将5 kΩ电阻接地。单击该电阻,将其拖到接地符号上。连接成功。如果想要旋转电阻,可以选择 "Control-R(控制电阻)"。10 kΩ反馈电阻位于放大器上方,于是我把它拖低一些。现在我发现它并未连接到输入端,无法连接了。看了一下菜单之后,我决定依次选择"Place (放置)"和"Junction(结点)"。试了几次后,我终于将三个器件连接到同一个节点(见图8)。

图8. 所有电阻均放置到位, 但某些连接缺失

现在,我觉得离成功不远了。我准备增加另一个结点,这样就有了输出。

#### 完成

做完这些以后,差不多快完成了。我不知道如何连接输入和输出,也不知道如何进行其它操作。于是我决定切换 "Simulation(仿真)"开关。窗口底部出现了提示(见图9)。

图9. 电路中无错误

情况还算不错,没有出现错误。我觉得需要有输入,还需要有一些设置来测量输出。

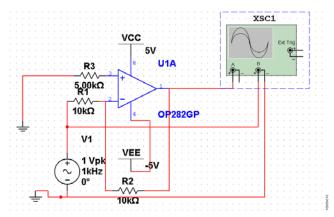

浏览了一遍菜单后,我依次选择"Place > Component > Sources (放置 > 器件 > 源)",然后选择"SIGNAL\_VOLTAGE\_SOURC ES"。接着选择"AC\_VOLTAGW",把它连接到10 kΩ输入电阻。

接下来,需要想办法查看输出。在选项"Simulate > Instruments(仿真 > 仪器)"中,我找到了示波器。我选中示波器,然后将一个通道连接至AC\_VOLTAGW的输出,将另一个通道连接至放大器的输出。将一个示波器通道接地。后来,我发现大多数情况下不需要这么做。现在可以试一下了(见图10)。

图10. 将输入源和示波器连接至输出

单击右上方的"Simulate(仿真)"按钮时,没有任何反应。

于是, 我双击示波器, 竟然成功了(见图11)!

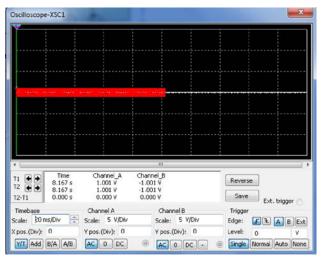

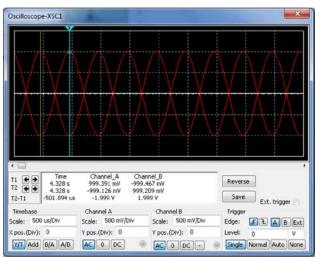

图11. 示波器显示

我迅速更改刻度,得到了图12所示的结果。

图12. 更改刻度后的示波器显示

第一次仿真完成。虽然只是一个简单的反相放大器,却是 将来进行更多仿真的开始。我可以轻松设计出一个滤波器 了。另外,我可能还会试着检查应用中的噪声是否足够 低。至少,现在我可以打开办公室门了。

#### 修订历史

2012年1月—修订版0:初始版

# 微带线和带状线设计

## 简介

人们撰写了大量文章来阐述如何端接PCB走线特性阻抗以避免信号反射。但是,妥善运用 传输线路技术的时机尚未说清楚。

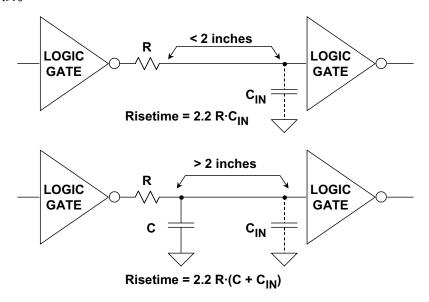

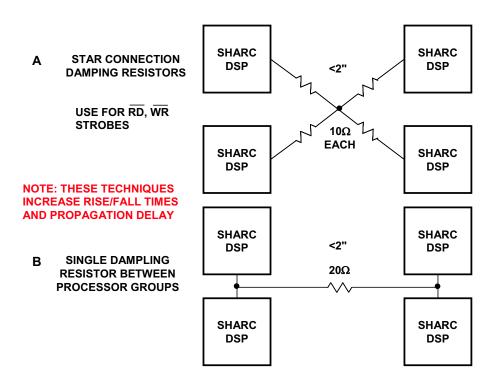

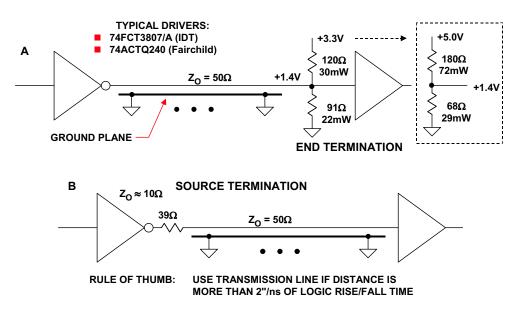

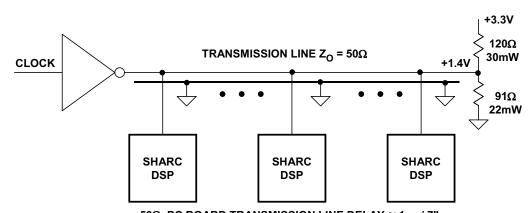

下面总结了针对逻辑信号的一条成熟的适用性指导方针。

当PCB走线单向传播延时等于或大于施加信号上升/下降时间(以最快边沿为准)时端接传输线路特性阻抗。

例如,在 $E_r$  = 4.0介电质上2英寸微带线的延时约270 ps。严格贯彻上述规则,只要信号上升时间不到~500 ps,端接是适当的。

更保守的规则是使用2英寸(PCB走线长度)/纳秒(上升/下降时间)规则。如果信号走线超过此走线长度/速度准则,则应使用端接。

例如,如果高速逻辑上升/下降时间为5 ns,PCB走线等于或大于10英寸(其中测量长度包括曲折线),就应端接其特性阻抗。

在模拟域内,必须注意,运算放大器和其他电路也应同样适用这条2英寸/纳秒指导方针,以确定是否需要传输线路技术。例如,如果放大器必须输出最大频率 $f_{max}$ ,则等效上升时间 $t_{max}$ 和关。这个限制上升时间 $t_{max}$ 可计算如下:

$$t_r = 0.35/f_{max}$$

等式 1

然后将t<sub>,</sub>乘以2英寸/纳秒来计算最大PCB走线长度。例如,最大频率100 MHz对应于3.5 ns的上升时间,所以载送此信号的7英寸或以上走线应视为传输线路。

### PCB板上受控阻抗走线的设计

在受控阻抗设计中,可以采用多种走线几何形状,既可与PCB布局图合二为一,也可与其相结合。在下面的讨论中,基本模式遵循IPC标准2141A的规定(见参考文献1)。

请注意,下面的图示中将使用术语"接地层"。需要了解的是,该接地层实际上是一个大面积、低阻抗的参考层。在实践中,可能是一个接地层或电源层,假定二者的交流电位均为零。

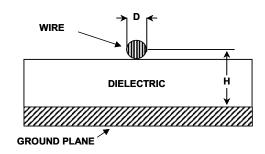

首先是简单的平面上布线形式的传输线路,也称微带线。图1所示为横截面视图。这类传输线路可能是实验板中使用的信号线。其构成非常简单,一条分立的绝缘线以固定间距分布于接地层上。介电质既可能是线材的绝缘层,也可能是该绝缘层与空气的结合体。

图1:一种阻抗既定的微带线传输线路由一条分布于接地层的绝缘线形成

该线路的阻抗(单位: 欧姆)可以用等式2估算。其中, D为导体直径, H为线材在接地层上的间距, ε,为介电常数。

$$Z_{O}(\Omega) = \frac{60}{\sqrt{\epsilon_{r}}} ln \left[ \frac{4H}{D} \right].$$

等式 2

对于与PCB相融合的图形,有多种几何模型可供选择,分为单端和差分两类。这些在IPC 标准2141A(见参考文献1)中有详细说明,这里对两个常见示例略加说明。

在开始进行任何基于PCB传输线路设计时,必须知道,有大量的等式都声称适用于此类设计。此时,一个极其重要的问题就是,"哪些等式是精确的呢?"不幸的是,没有一个等式是完全精确的!所有现有等式都是近似值,因而,其精度不尽相同,取决于具体情况。最知名也是引用最多的是参考文献1中给出的等式,但是,即使这些等式也存在一些应用问题。

参考文献2针对不同几何图形,在试验PCB样品上对参考文献1中的等式进行了评估。结果发现,预测精度因目标阻抗而异。下面引述的等式均来自参考文献1,这里只是作为设计的起点,实际设计时,还需要进一步的分析、测试和进行设计验证。原则就是,要仔细研究,谨慎面对PCB走线阻抗等式。

Page 2 of 7 77

### 微带线PCB传输线路

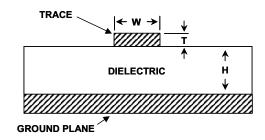

对于其中一面为接地层的简单双面PCB设计,可以在另一面设计一条信号走线以控制阻抗。这种几何图形被称为表面微带,简称微带。

图2中的双层PCB横截面视图展示了这种微带几何图形。

图2: 一种阻抗既定微带传输线路由一条分布于接地层、 采用适当几何图形的PCB走线形成

对于给定的PCB基板和铜重量,需要注意的是,W(信号走线宽度)以外的所有参数都是事 先确定的。因而,可用等式3来设计一种PCB走线,以匹配电路要求的阻抗。若信号走线 宽W、厚T,且由介电常数为ε<sub>r</sub>的PCB电介质以距离H与接地层(或电源层)相分离,则其特性阻抗为:

$$Z_{o}(\Omega) = \frac{87}{\sqrt{\varepsilon_{r} + 1.41}} \ln \left[ \frac{5.98H}{(0.8W + T)} \right]$$

等式 3

请注意,在这些表达式中,测量值均为常用单位(mil)。

这些传输线路不但有特性阻抗,也有特性电容。其计算单位为pF/in,如等式4所示。

$$C_{0}(pF/in) = \frac{0.67(\epsilon_{r} + 1.41)}{\ln[5.98H/(0.8W + T)]}$$

等式 4

作为包括这些计算的示例,一块双层板可能用20 mil宽(W)、1盎司(T=1.4)的铜走线,并由 10 mil (H) FR-4 ( $\epsilon_r$  = 4.0)的介电材料分离。结果,该微带线的阻抗为50 Ω左右。对于其他标准阻抗(如75 Ω的视频标准阻抗),使"W"调整为8.3 mil左右即可。

78 Page 3 of 7

### 微带线设计的一些指导原则

本例涉及到一个有趣且微妙的要点。参考文献2讨论了与微带PCB阻抗相关的有用指导原则。若介电常数为4.0 (FR-4),结果显示,当W/H为2/1时,阻抗将接近50  $\Omega$ (与第一个示例类似,其中,W = 20 mil)。

仔细的读者会发现,根据等式3预测, $Z_0$ 应为46  $\Omega$ 左右,与参考文献2提到的精度(>5%)相吻合。IPC微带线等式在50  $\Omega$ 与100  $\Omega$ 之间最精确,但当阻抗低于或超过该范围时,其精度则大幅下降。

根据等式5,也可以计算微带线的传播延迟。这是微带信号走线的单向通过时间。有趣的是,对于给定的几何模型,延迟常数(单位:ns/ft)仅为介电常数而非走线维度的函数(见参考文献6)。请注意,这可以带来极大的便利。意味着,当给定PCB基板(并给定ε<sub>r</sub>)时,各种阻抗线路的传播延迟常数是固定不变的。

该延迟常数也可以ps/in为单位,这样更适用于小型PCB。即:

因此,举例来说,对于PCB介电常数4.0,不难发现微带线的延迟常数约为1.63 ns/ft,合 136 ps/in。这两条额外的准则对于设计PCB走线中信号的时序具有参考意义。

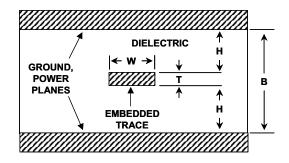

### 对称带状线PCB传输线路

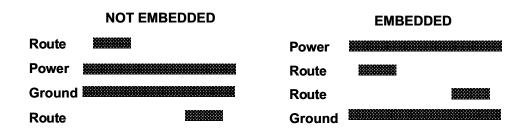

从多种角度来看,多层PCB是一种更好的PCB设计方法。在这种模式下,信号走线嵌入电源层与接地层之间,如图3中的横截面视图所示。低阻抗交流接地层和嵌入的信号走线形成一条对称带状线传输线路。

从图中可以看出,高频信号走线的电流回路直接位于接地层/电源层上的信号走线的上方和下方。因此,高频信号被完全限制在PCB板内部,结果使放射降至最低,为输入杂散信号提供了天然的屏障。

Page 4 of 7 79

图3: 一种阻抗既定的对称带状线传输线路由一条嵌于等距接地层和/ 或电源层之间、采用适当几何图形的PCB走线形成

该设计的特性阻抗同样取决于几何图形以及PCB介电质的 $\epsilon_r$ 。该带状传输线路的 $Z_o$ 可表示为:

$$Z_{O}(\Omega) = \frac{60}{\sqrt{\varepsilon_{r}}} \ln \left[ \frac{1.9(B)}{(0.8W + T)} \right].$$

\(\xi \tau\_{0}\)

这里的所有维度同样以mil为单位,B为两个层的间距。在这种对称几何图形中,需要注意的是,B同样等于2H+T。参考文献2指出,参考文献1中的这个等式的精度通常在6%左右。

适用于 $\varepsilon_r$  = 4.0的对称带状线的另一条便利准则是,使B成为W的倍数,范围为2至2.2。结果将得到约50 $\Omega$ 的带状线阻抗。当然,这条法则是以另一近似法为基础的,忽略了T。尽管如此,该法则对于粗略估算还是很有用的。

对称带状线同样有一个特性电容,其计算单位为pF/in,如等式8所示。

$$C_{o}(pF/in) = \frac{1.41(\epsilon_{r})}{\ln[3.81H/(0.8W+T)]}$$

. 等式 8

对称带状线的传播延迟如等式9所示。

$$t_{pd}(ns/ft) = 1.017\sqrt{\varepsilon_r}$$

等式 9

或者以ps为单位:

$$t_{pd}(ps/in) = 85\sqrt{\epsilon_r}$$

等式 10

80 Page 5 of 7

当PCB介电常数为4.0时,可以发现,对称带状线的延迟常数几乎正好为2 ns/ft,合170 ps/in。

### 走线嵌入法的利弊

根据上述讨论,在设计阻抗既定的PCB走线时,既可以置于一个表层之上,也可嵌入两层之间。当然,在这些阻抗因素之外,还有许多其他考虑因素。

嵌入式信号确实存在一个明显的大问题——隐藏电路走线的调试非常困难,甚至无法做到。图4总结了嵌入式信号走线的利弊。

- Advantages

- Signal traces shielded and protected

- Lower impedance, thus lower emissions and crosstalk

- Significant improvement > 50MHz

- Disadvantages

- Difficult prototyping and troubleshooting

- Decoupling may be more difficult

- Impedance may be too low for easy matching

图4: 多层PCB设计中嵌入与不嵌入信号走线的利弊

设计多层PCB时也可能不使用嵌入式走线,如最左边的横截面视图所示。可以将这种嵌入式设计看作一种双重双层PCB设计(共有四层铜)。顶部的走线与电源层构成微带,底部的走线则与接地层构成微带。在本例中,两个外层的信号走线可以方便地供测量和故障排查使用。但这种设计并未利用各层的屏蔽作用。

这种非嵌入式设计的辐射量较大,更容易受到外部信号的影响,而右侧的嵌入式设计采用了嵌入法,则很好地利用了各层的优势。就如诸多其他工程设计一样,PCB设计中到底采用嵌入法还是非嵌入法是折衷的结果。这里的折衷则体现在减少辐射与方便测试之间。

Page 6 of 7 81

## 参考文献:

- Standard IPC-2141A, "Controlled Impedance Circuit Boards and High Speed Logic Design," 2004, <u>Institute for Interconnection and Packaging Electronic Circuits</u>, 3000 Lakeside Drive, 309 S, Bannockburn, IL 60015, 847-615-7100.

- 2. Eric Bogatin, BTS015, PCB Impedance Design: Beyond the IPC Recommendations, BeTheSignal.com.

- 3. Eric Bogatin, Signal Integrity Simplified, Prentice Hall PTR, 2003, ISBN-10: 0130669466, ISBN-13: 978-0130669469.

- 4. Andrew Burkhardt, Christopher Gregg, Alan Staniforth, "Calculation of PCB Track Impedance," Technical Paper S-19-5, presented at the *IPC Printed Circuits Expo '99 Conference*, March 14–18, 1999.

- 5. Brian C. Wadell, *Transmission Line Design Handbook*, Artech House, Norwood, MA, 1991, ISBN: 0-89006-436-9.

- 6. William R. Blood, Jr., <u>MECL System Design Handbook (HB205/D, Rev. 1A May 1988)</u>, ON Semiconductor, August, 2000.

- 7. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 12

- 8. Walt Kester, <u>Analog-Digital Conversion</u>, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 9. Also available as <u>The Data Conversion Handbook</u>, Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 9.

- 9. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Chapter 7. Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 7.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

82 Page 7 of 7

# 散热设计基础

### 简介

出于可靠性原因,处理大功率的集成电路越来越需要达到热管理要求。所有半导体都针对结温 $(T_j)$ 规定了安全上限,通常为150°C(有时为175°C)。与最大电源电压一样,最大结温是一种最差情况限制,不得超过此值。在保守设计中,一般留有充分的安全裕量。请注意,这一点至关重要,因为半导体的寿命与工作结温成反比。简单而言,IC温度越低,越有可能达到最长寿命。

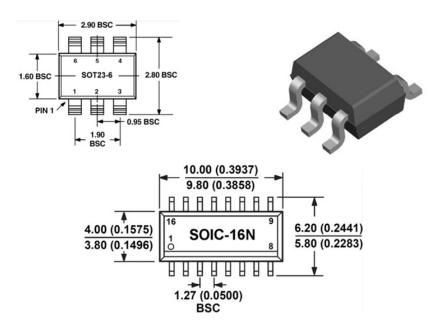

这种功率和温度限制是很重要的,典型的数据手册中都有描述,如图1所示。图中所示为一款8引脚SOIC器件AD8017AR。

The maximum power that can be safely dissipated by the AD8017 is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated device is determined by the glass transition temperature of the plastic, approximately +150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package. Exceeding a junction temperature of +175°C for an extended period can result in device failure.

# 图1: AD8017AR(ADI散热增强型SOIC封装器件) 数据手册中关于最大功耗的声明

与这些声明相关的是一些工作条件,比如器件功耗、印刷电路板(PCB)的封装安装细则等。对于AD8017AR,其在25°C的环境温度下的额定功耗为1.3 W。其假设是8引脚SOIC封装配合的是一块双层PCB板,以大约4 in² (~2500 mm²)的2盎司铜实现散热。下面将预测该器件在其他条件下的安全工作情况。

## 散热设计基础

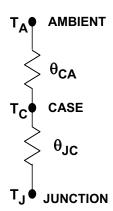

一般用符号 $\theta$ 来表示热阻。热阻的单位为°C/W。除非另有说明,热阻指热量在从热IC结点传导至环境空气时遇到的阻力。也可更具体地表示为 $\theta_{JA}$ ,即结至环境热阻。 $\theta_{JC}$ 和 $\theta_{CA}$ 是 $\theta$ 的两种其他形式,详见下文。

一般地,热阻θ等于100°C/W的器件在1W功耗下将表现出100°C的温差,该值在两个参照点之间测得。请注意,这是一种线性关系,因此,在该器件中,1W的功耗将产生100°C的温差(如此等等,不一而足)。对于AD8017AR,θ约为95°C/W,因此,1.3 W的功耗将产生大约124°C结至环境温差。当然,预测内部温度时使用的正是这种温度的上升,其目的是判断设计的热可靠性。当环境温度为25°C时,允许约150°C的内部结温。实际上,多数环境温度都在25°C以上,因此,可以处理的功耗会稍低。

对于任意功耗P(单位: W),都可以用以下等式来计算有效温差 $(\Delta T)(单位: ^{\circ}C)$ :

其中,θ为总适用热阻。图2总结了一些基本的热关系。

- $\bullet$   $\theta$  = Thermal Resistance (°C/W)

- ◆ P = Total Device Power Dissipation (W)

- ◆ T = Temperature (°C)

- ♦  $\Delta$ T = Temperature Differential = P × θ

- $\bullet$   $\theta_{1A}$  = Junction-Ambient Thermal Resistance

- $\theta_{JC}$  = Junction-Case Thermal Resistance

- $\bullet$   $\theta_{CA}$  = Case-Ambient Thermal Resistance

- $\bullet$   $\theta_{JA} = \theta_{JC} + \theta_{CA}$

- $\bullet$  T<sub>J</sub> = T<sub>A</sub> + (P ×  $\theta$ <sub>JA</sub>)

- **♦** Note: T<sub>J(Max)</sub> = 150°C (Sometimes 175°C)

### 图2:基本热关系

请注意,串行热阻(如右侧的两个热阻)模拟的是一个器件可能遇到的总热阻路径。因此,在计算时,总 $\theta$ 为两个热阻之和,即 $\theta_{JA} = \theta_{JC} + \theta_{CA}$ 。给定环境温度 $T_A$ 、P和 $\theta$ ,即可算出 $T_J$ 。根据图中所示关系,要维持一个低的 $T_J$ ,必须使 $\theta$ 或功耗(或者二者同时)较低。低 $\Delta T$ 是延长半导体寿命的关键,因为,低 $\Delta T$ 可以降低最大结温。

在IC中,一个温度参照点始终是器件的一个节点,即工作于给定封装中的芯片内部最热的点。其他相关参照点为 $T_c$ (器件)或 $T_A$ (周围空气)。结果又引出了前面提到的各个热阻,即 $\theta_{Jc}$ 和 $\theta_{TA}$ 。

先来看看最简单的情况, $\theta_{JA}$ 为在给定器件的结与环境空气之间测得的热阻。该热阻通常适用于小型、功耗相对较低的IC(如运算放大器),其功耗往往为1 W或以下。一般而言,对于8引脚DIP塑封或者更优秀的SOIC封装,运算放大器以及其他小型器件的典型 $\theta_{JA}$ 值处于90-100°C/W水平。

需要明确的是,这些热阻在很大程度上取决于封装,因为不同的材料拥有不同水平的导热性。一般而言,导体的热阻类似于电阻,铜最好,其次是铝、钢等。因此,铜引脚架构封装具有最高的性能,即最低的θ。

#### 散热

根据定义,散热器是附加于IC之上的一种额外低热阻器件,其作用是辅助散热。散热器具有自己的热阻,表示为 $\theta_{CA}$ ,单位为°C/W。然而,当今的多数运算放大器在安装散热器时相当麻烦(较老的TO-99金属帽壳型封装除外)。考虑了散热器安装的器件具有明显的特征,其 $\theta_{JC}$ 远低于 $\theta_{JA}$ 。这种情况下, $\theta$ 将由一个以上的组分构成。热阻采用加法即可,结果使净值计算变得相对简单。例如,在给定相关 $\theta_{JC}$ 时,要计算净 $\theta_{JA}$ ,只需将散热器的热阻 $\theta_{CA}$ 或者壳到环境热阻与 $\theta_{JC}$ 相加即可:

$$\theta_{JA} = \theta_{JC} + \theta_{CA}$$

等式 2

结果得到针对具体环境的θια。

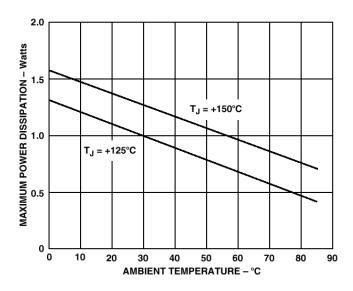

然而更广泛地讲,现代IC并不使用市场上有售的散热器。相反,在需要消耗大量功率时(比如 $\geq 1$  W),以低热阻铜PCB走线作为散热器。在这种情况下,制造商提供的对散热最有用的加工数据是示例PCB布局的边界条件以及这些条件下产生的 $\theta_{JA}$ 。如前所述,这是针对AD8017AR提供的具体信息。通过这种方式,展示此类条件下热关系的示例数据如图3所示。这些数据适用于装有一个散热器的AD8017AR,该散热器的面积约为4平方英寸,采用一块双层2盎司铜PCB板。

这些曲线展示的是AD8017在最大结温150°C和125°C下的最大功耗与温度特性之间的关系。这种曲线通常称为减额曲线,因为,容许功耗随环境温度而下降。

图3: AD8017AR运算放大器的热额定曲线

AD8017AR采用的是ADI专有的散热增强型(Thermal Coastline) IC封装,在不增加SO-8封装尺寸的情况下允许消耗更多的功率。对于 $150^{\circ}$ C的 $T_{J(max)}$ ,上部曲线显示的是该封装的容许功耗,在 $25^{\circ}$ C的环境温度下为1.3 W。如果使用更保守的 $125^{\circ}$ C  $T_{J(max)}$ ,则适用两条曲线中的下部曲线。

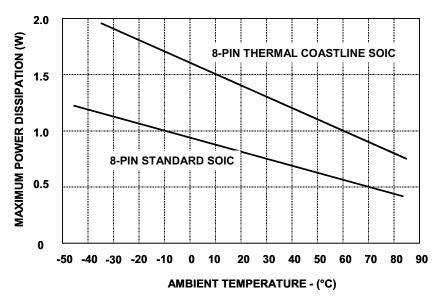

图4展示了8引脚标准SOIC封装与ADI散热增强型封装的性能比较结果。请注意,散热增强型封装在25°C下的容许功耗为1.3 W,而标准封装仅为0.8 W。在散热增强型封装中,热传导增强了,这正是封装 $\theta_{\text{LA}}$ 较低的原因所在。

图4:标准(下)和ADI散热增强型(上)8引脚SOIC封装的热额定曲线

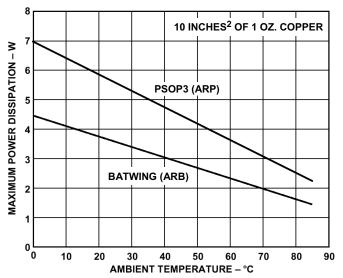

甚至可以支持更高的功耗,因为使用IC封装后,可以增进从芯片到PCB板的热传导。其中一个示例是AD8016 ADSL线路驱动器件,该器件提供两种封装选项,25℃下的额定功耗分别为5.5 W和3.5 W,如图5所示。

以额定功耗较高的AD8016ARP PSOP3封装为例,当搭配一个 $10 \text{ in}^2$ 、1盎司散热层时,该组合可以在 $70^{\circ}$ C的环境温度下处理最高3W的功耗,如图中的上部曲线所示。这相当于 $18^{\circ}$ C/W的 $\theta_{1a}$ ,这种情况下,该值适用于 $125^{\circ}$ C的最大结温。

图5:AD8016 BATWING(下)和PSOP3(上) 封装的热特性曲线(其中,T<sub>J(Max)</sub>=125°C)

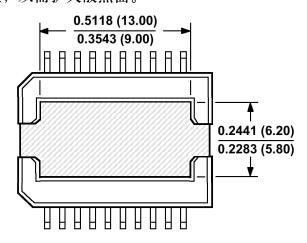

PSOP3版的AD8016之所以具有如此出色的功耗处理能力是因为采用了一块大面积铜片。 在内部,IC芯片直接置于铜片上,底部表面裸露情况如图6所示。其目的是将该表面直接 焊接到PCB板上的一个铜层上,从而扩大散热面。

图6: AD8016 20引脚PSOP3封装的底视图展示了 辅助散热铜片(中心的灰色区域)

AD8016的两种封装选项均有静止空气和流动空气两种特性,但是,上面给出的热数据适用于不使用定向气流的情况。因此,增加气流会进一步降低热阻(见参考文献2)。

为了设计出可靠的低热阻运算放大器,以下列出几条设计注意事项。可根据实际情况,考虑所有要点。

- 1. 对于PCB散热器,要使用面积尽量大的铜片,以"效益递减"点为度。

- 2. 与1)相结合,要使用多个(外部)PCB层,用多个过孔连接起来。

- 3. 根据实际情况尽量使用质量较重的铜(最好是2盎司或以上)。

- 4. 在系统中提供充足的天然通风出入口,以便热能从热的PCB表面自由散开。

- 5. 使功耗消散PCB层垂直朝向,促进散热器区域的气流对流。

- 6. 针对精密运算放大器应用、考虑使用外部功率缓冲级。

- 7. 对于需要在有限空间下耗散数瓦特的情况,考虑使用强制通风方法。

- 8. 不要在散热走线上覆盖阻焊层。

- 9. 不要在供电IC上使用过大的电源电压。

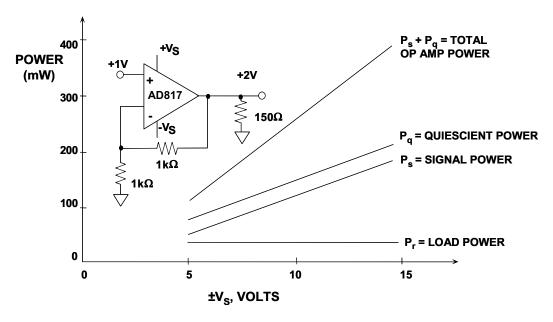

多数情况下,以上各项都是显而易见的。然而,第9项却需要稍加说明。每当应用只需要适中的电压摆幅时(如标准视频、2 V p-p),通常可以使用宽电源电压范围。但是,如图7中的数据所表明的那样,在较高的电源电压下,运算放大器驱动器的运行会产生较大的IC功耗,即使负载功率恒定不变亦是如此。

在这种情况下,只要应用的失真性能不恶化,就应该为IC提供较低的电压,如±5 V而非±15 V。 以上示例数据是以直流为基础计算所得,与正弦波或噪声类波形(如DMT信号)相比,直流 会增加驱动器的功耗(见参考文献2)。一般原则仍然适用于这些交流波形,换言之,当负 载电流高、电压低时,运算放大器的功耗就高。

图7: 视频运算放大器驱动器在各种电源电压、 低电压输出摆幅下的功耗

虽然上述AD8016和AD8017两款散热增强型封装有较大的机会处理高功耗,但日益流行的小型IC封装实际上却朝着相反的方向发展。毫无疑问,当今的小型封装确实会牺牲较大散热性能。但是必须了解的是,这是为了缩小运算放大器封装的尺寸,最终是为提高整个系统的PCB板密度。

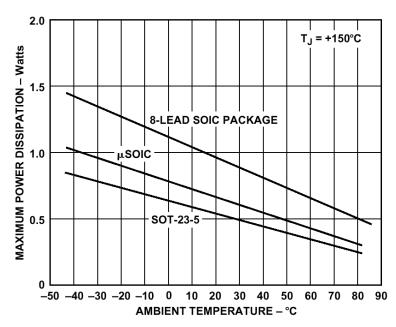

这几点反映在<u>AD8057</u>和<u>AD8058</u>系列单通道和双通道运算放大器的热额定值中,如图8所示。AD8057和AD8058运算放大器提供三种不同的封装,分别为SOT-23-5、8引脚μSOIC以及标准SOIC封装。

如数据所示,随着封装尺寸的缩小,能够消散的功率也会显著减少。对于此类微型封装来说,由于引脚架构是唯一的散热通道,因而其热性能会下降。上述封装的 $\theta_{JA}$ 分别为 240°C/W、200°C/W和160°C/W。请注意,这是封装限制,而非器件限制。采用相同封装的其他IC具有类似特性。

Figure 8: Comparative Thermal Performance for Several AD8057/58 Op Amp Package Options

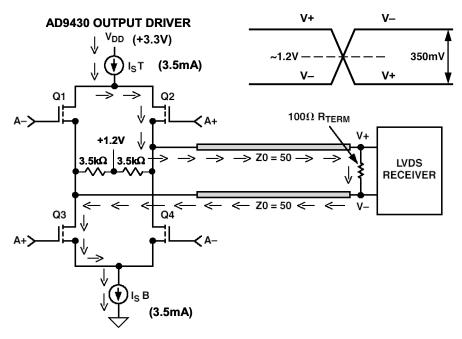

### 数据转换器散热考虑

表面上看,我们可能会假定,ADC或DAC的功耗在既定电源电压会保持不变。然而,许多数据转换器(尤其是CMOS类)的功耗高度依赖于输出数据负载和采样时钟频率。由于许多新型高速转换器在最差工作条件下可能消耗最多1.5 W至2 W的功率,因此,我们必须清楚地了解这一点,以确保安装封装时,使最高预期工作温度下的结温保持于可接受限值之内。

指南MT-031谈到接地强调称,高性能ADC(尤其是带有并行输出者)的数字输出的负载不宜过大(5-10 pF),以防止数字瞬变电流导致SNR和SFDR下降。然而,即使在小输出负载下,多数CMOS和BiCMOS ADC的功耗也仍然是采样时钟频率的函数,有时则为模拟输入频率和幅度的函数。

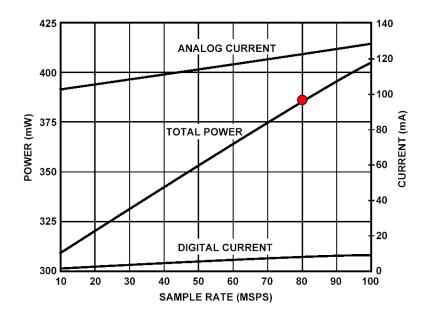

例如,图9展示了AD9245 14位、80 MSPS、3 V CMOS ADC在数据线路的模拟输入为2.5 MHz 且输出负载为5 pF时,功耗与频率之间的关系。图中分别展示了数字和模拟电源电流以及总功耗。请注意,当采样频率在10 MSPS与80 MSPS之间变化时,总功耗可能在310 mW 至380 mW范围内变化。

图9: AD9245 14位、80 MSPS、3 V CMOS ADC 功耗与采样速率的关系(输入为2.5 MHz;输出负载为5 pF)

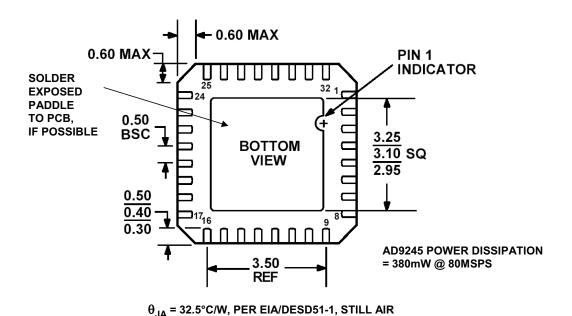

AD9245采用32引脚无铅芯片级封装,如图10所示。封装的底视图显示的是裸露的焊盘,该焊盘应焊接到PC板的接地层以获得最佳的热传导效果。最差情况封装结至环境热阻 $\theta_{JA}$ 的额定值为32.5°C/W,当功耗为380mW时,结温将比环境温度高32.5°C×0.38 = 12.3°C。当最高工作温度为+85°C时,结温为85°C + 12.3°C = 97.3°C。

图10: AD9245 CP-32引脚架构芯片级封装(LFCSP)(底视图)

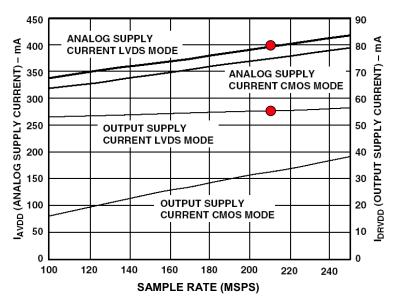

AD9430是一款高性能12位、170/210 MSPS 3.3 V BiCMOS ADC。有两种输出模式可用:双通道105 MSPS解复用CMOS输出和210 MSPS LVDS输出。功耗为采样频率的函数,如图11 所示。其中展示了CMOS和LVDS模式下当模拟输入频率为10.3 MHz时的模拟和数字电源电流。请注意,在LVDS模式下,当采样频率为210 MSPS时,总电源电流约为455 mA——总功耗为1.5 W。

TOTAL CURRENT @ 210MSPS, LVDS MODE = 55mA + 400mA = 455mATOTAL POWER DISSIPATION =  $3.3V \times 455mA = 1.5W$

图11: AD9430 12位170 /210 MSPS ADC电源电流与 采样速率的关系(输入频率为10.3 MHz)

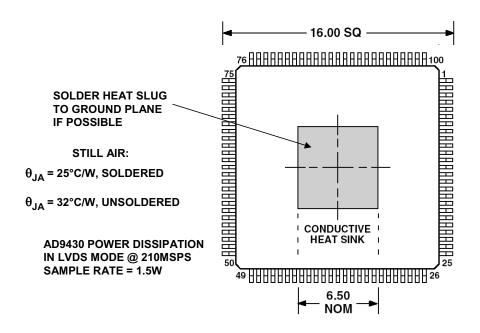

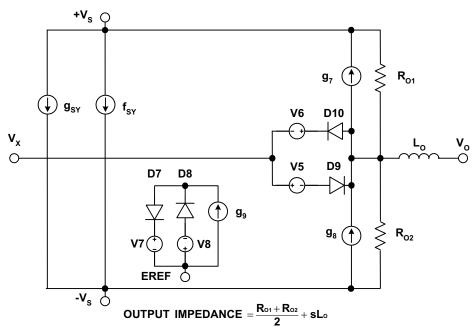

AD9430采用100引脚薄型塑封四方扁平封装,带一个裸露焊盘(TQFP/EP),如图12所示。 导电焊盘与芯片接地面相连,应焊接到PC板接地层。当焊接到接地层时,该封装在静止 空气中的 $\theta_{JA}$ 为25°C/W。结果,当功耗为1.5 W时,结温将比环境温度高25°C×1.5 = 37.5°C。 当最高工作温度为+85°C时,结温为85°C + 37.5℃ = 122.5℃。

图12: AD9430 100引脚e-PAD TQFP

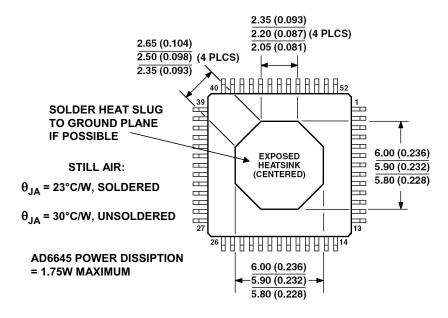

AD6645是一款高性能14位、80/105 MSPS ADC,采用高速互补双极性工艺(XFCB)制成,具有较高的SFDR (89 dBc)和SNR (75 dB)。尽管其功耗(为采样频率的函数)变化不大,该器件的最大功耗为1.75 W。采用的是散热增强型52引脚PowerQuad 4°封装,带一个裸露焊盘,如图13所示。

图13: AD6645 52引脚Power-Quad 4 (LQFP\_ED) (SQ-52) 散热增强型封装(底视图)

建议把裸露的中央散热器焊接到PC板接地层上,以使封装在静止空气中的 $\theta_{JA}$ 减至23°C/W。对于1.75 W的功耗,结温将比环境温度高23°C×1.75 = 40.3°C。当最高工作温度为+85°C,结温为85°C + 40.3°C = 125.3°C。可以用200 LFPM的气流使封装的热阻降至17°C/W,从而使结温降至比环境温度高30°C的水平。换言之,对于+85°C的工作环境温度,结温为115°C。