# ADI 技术指南合集 第一版 放大器

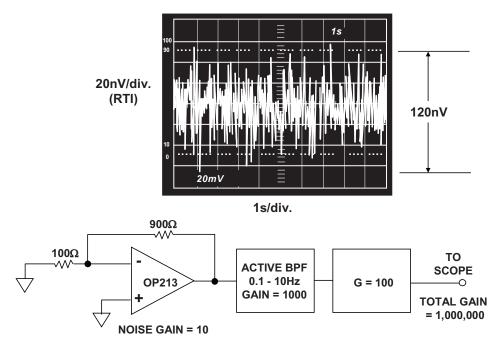

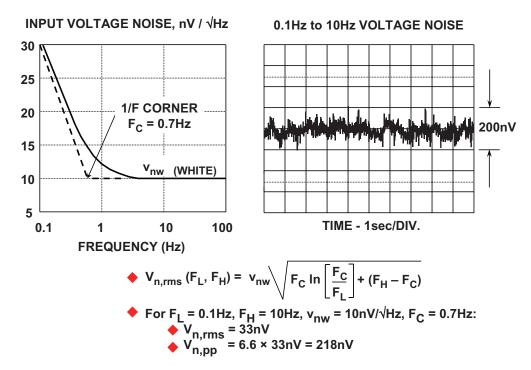

# 目录

| Bainter 陷波滤波器1                  |  |

|---------------------------------|--|

| 三运算放大器仪表放大器基本结构3                |  |

| 二阶系统的运算放大器总输出噪声计算8              |  |

| 从低通到带通滤波器的转换11                  |  |

| 从低通到带阻(陷波)滤波器的转换14              |  |

| 从低通到高通滤波器的转换17                  |  |

| 仪表放大器基础19                       |  |

| 仪表放大器桥式电路误差预算分析24               |  |

| 仪表放大器直流误差源26                    |  |

| 仪表放大器输入 RFI 保护31                |  |

| 仪表放大器输入过压保护37                   |  |

| 全波整流器42                         |  |

| 全通滤波器45                         |  |

| 切比雪夫响应47                        |  |

| 半波整流器59                         |  |

| 单极点系统的运算放大器总输出噪声计算61            |  |

| 双 T 陷波滤波器64                     |  |

| 双放大器带通 (DABP) 滤波器65             |  |

| 双运放仪表放大器基本配置67                  |  |

| 反相放大器72                         |  |

| 反相求和放大器73                       |  |

| 反馈电容反馈电容对电压反馈 (VFB) 和电流反馈 (CFB) |  |

| 型运算放大器的影响75                     |  |

| 四次(双二阶)滤波器79                    |  |

| 在电压反馈 (VFB) 和电流反馈 (CFB)         |  |

| 运算放大器之间选择81                     |  |

| 多反馈带通滤波器设计示例87                  |  |

| 多反馈滤波器89                        |  |

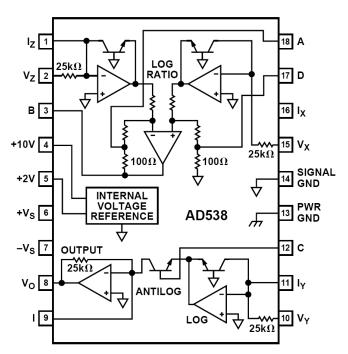

| 对数放大器基础知识92                     |  |

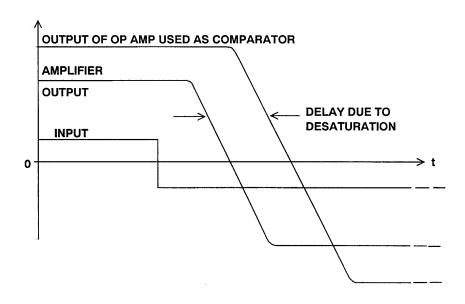

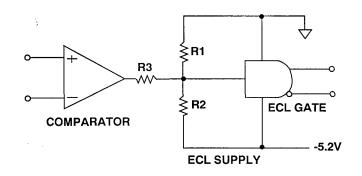

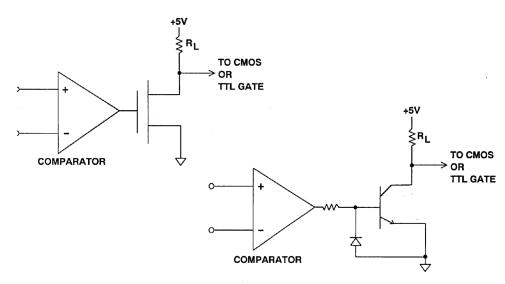

| 将运算放大器用作比较器98                   |  |

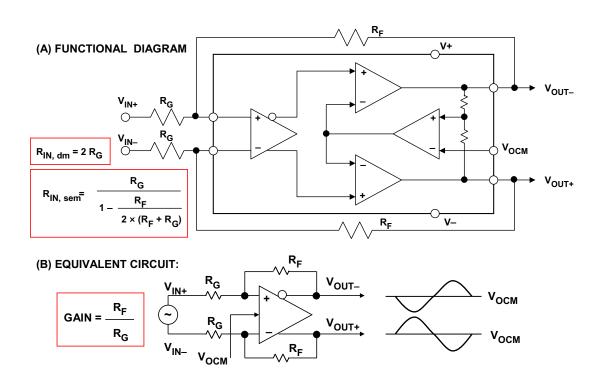

| 差分驱动器分析104                      |  |

| 差动放大器和电流检测放大器113                |  |

| 巴特沃兹响应119                       |  |

| 放大器类型123                        |  |

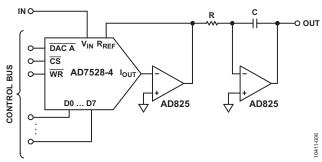

| 数字编程状态变量滤波器126                  |  |

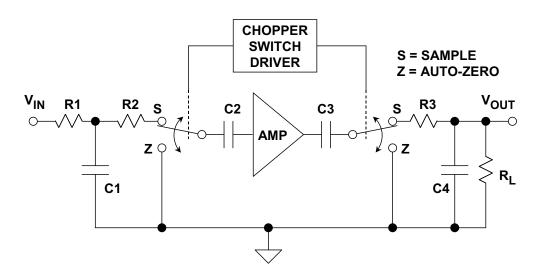

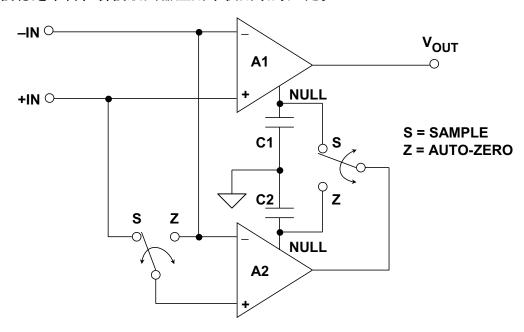

| 斩波稳定(自稳零)型精密运算放大器129            |  |

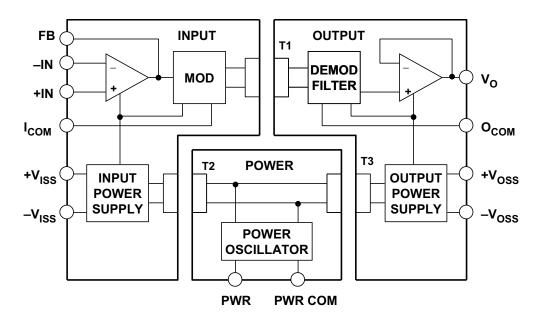

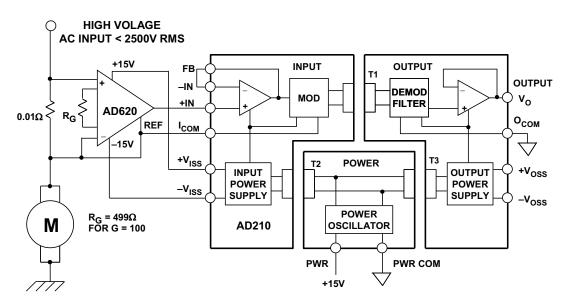

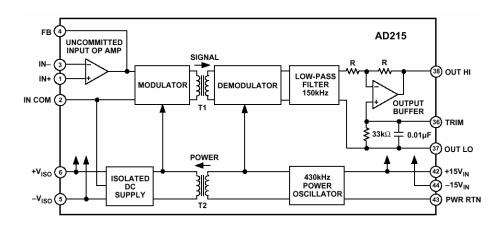

| 模拟隔离放大器135                      |  |

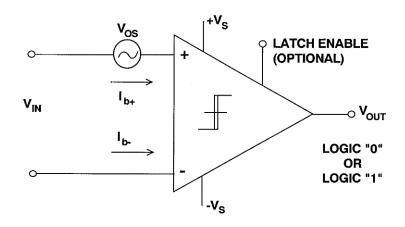

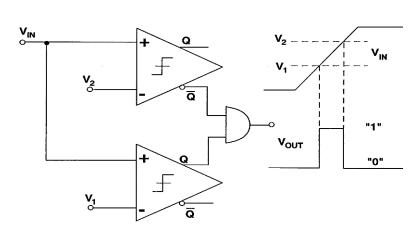

| 比较器141                          |  |

| 滤波器中的 F0 和 Q148             |

|-----------------------------|

| 状态变量滤波器151                  |

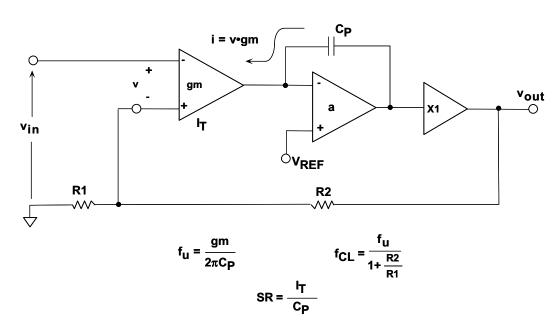

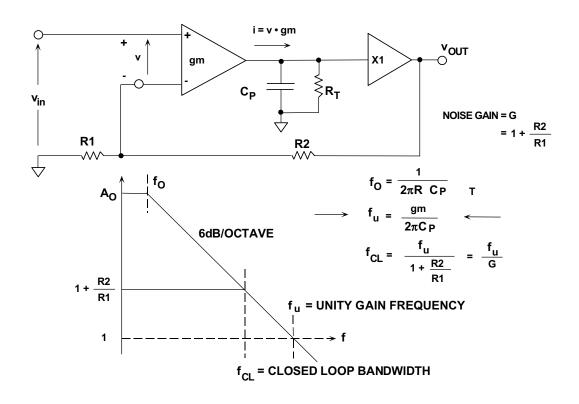

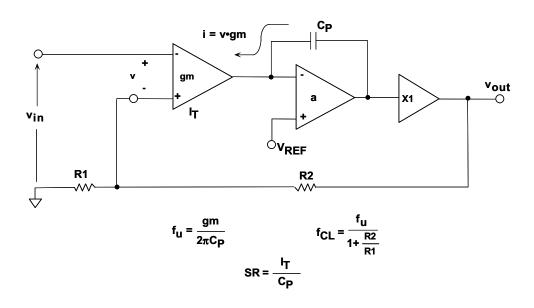

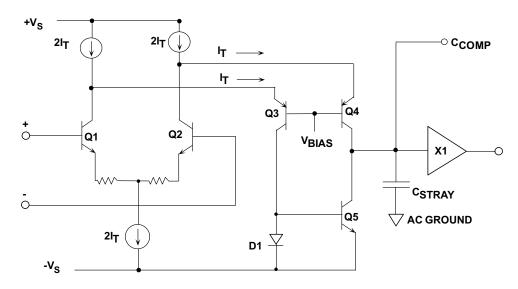

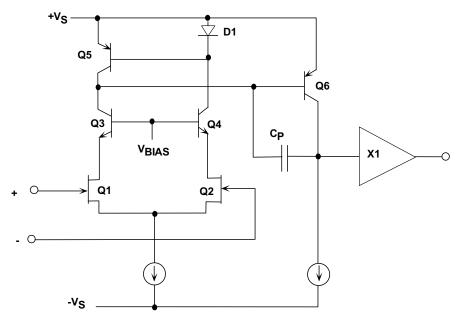

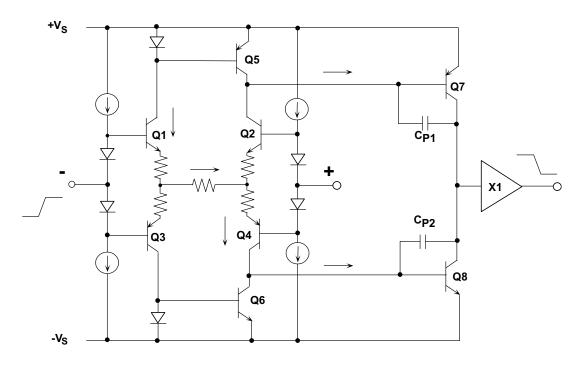

| 理想的电压反馈型 (VFB) 运算放大器154     |

| 电压反馈型运算放大器的增益和带宽160         |

| 电流反馈 (CFB) 运算放大器168         |

| 电流反馈运算放大器噪声考虑因素174          |

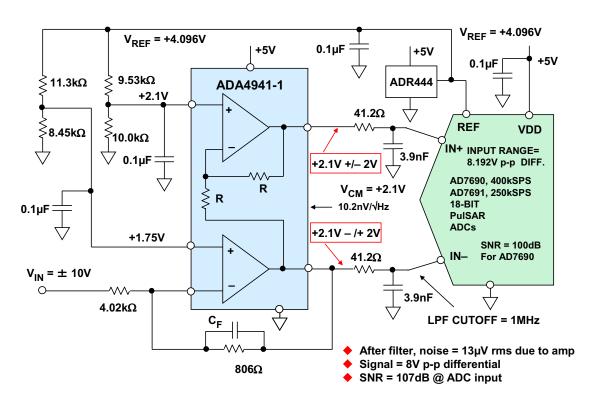

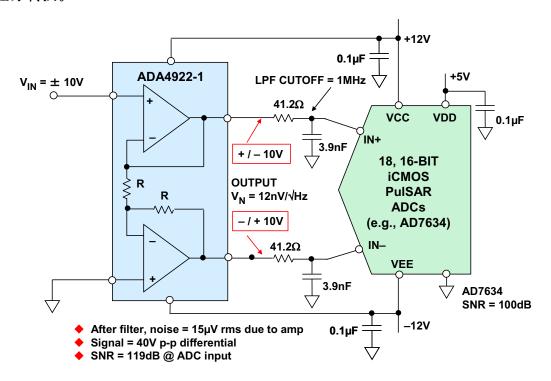

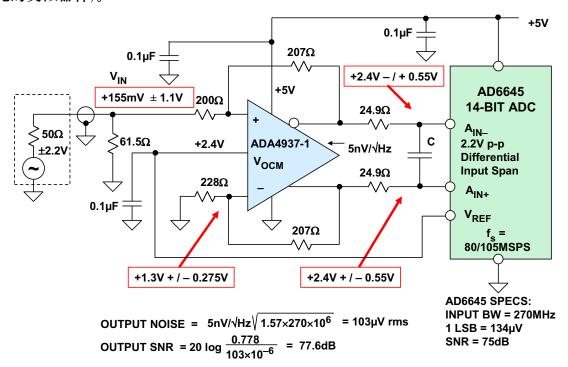

| 精密 ADC 用差分驱动器176            |

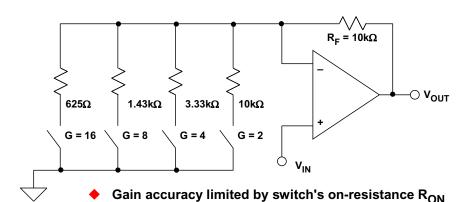

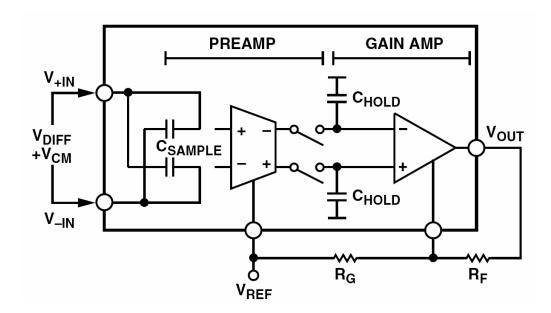

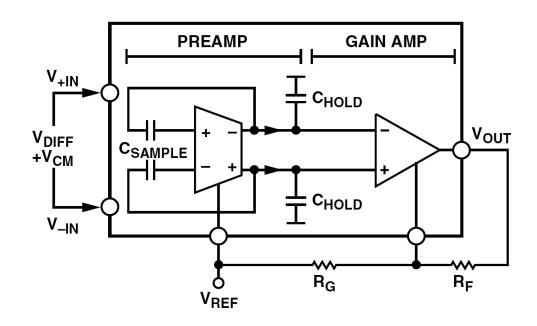

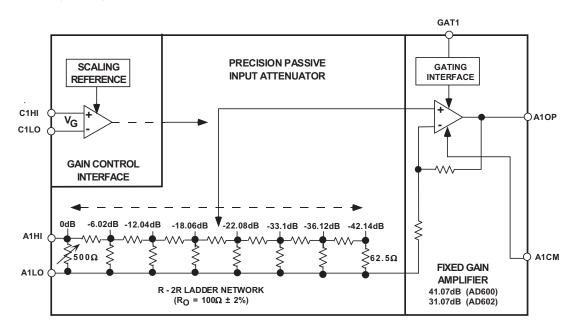

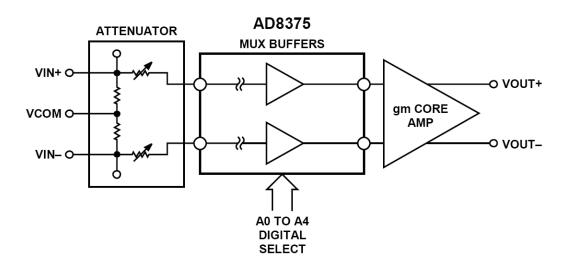

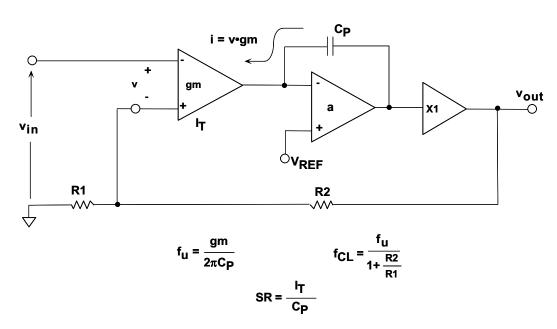

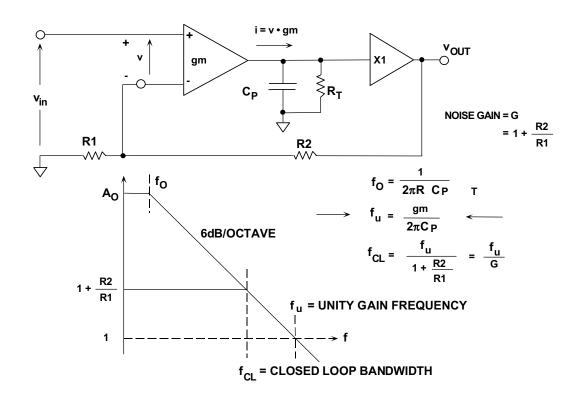

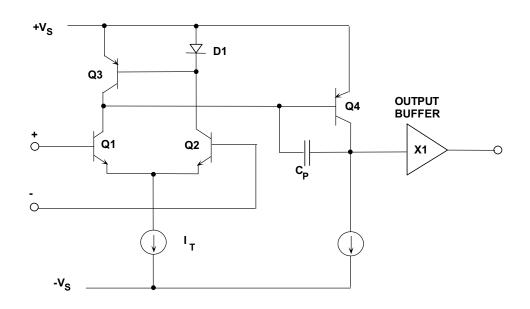

| 精密可变增益放大器 (VGA)181          |

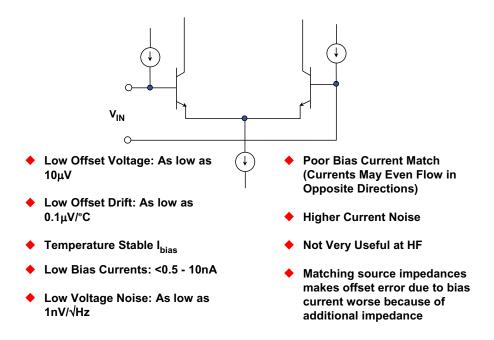

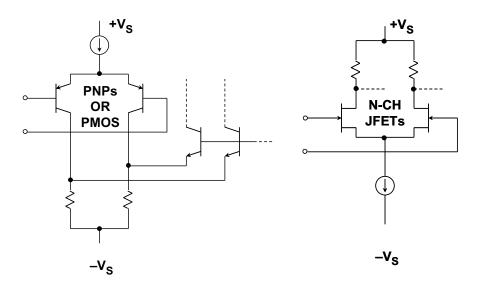

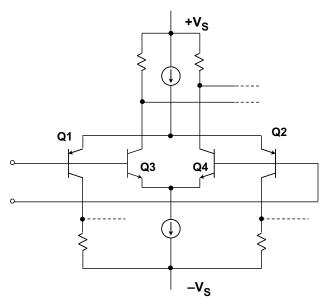

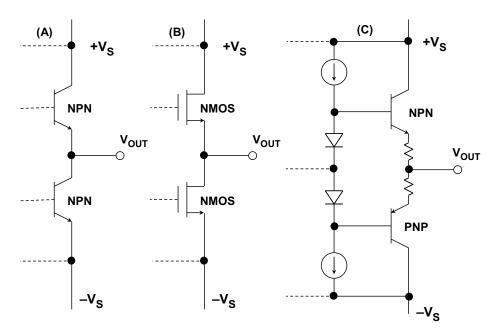

| 精密运算放大器191                  |

| 自稳零仪表放大器195                 |

| 补偿输入电容对电流电压转换器所用电压反馈和       |

| 电流反馈型运算放大器的影响198            |

| 贝塞尔响应203                    |

| 运算放大器共模抑制比 (CMRR)206        |

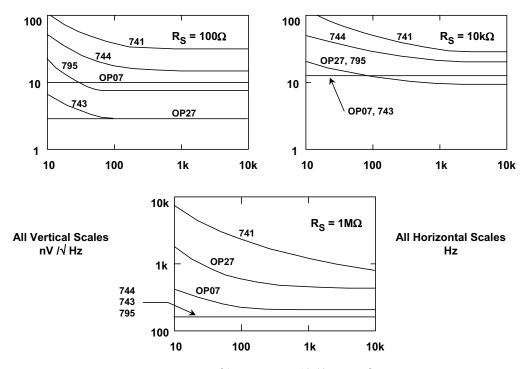

| 运算放大器噪声209                  |

| 运算放大器噪声216                  |

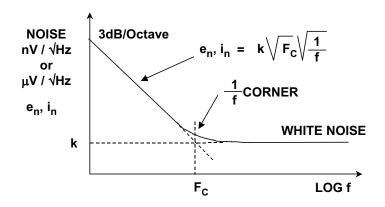

| 运算放大器噪声关系: 1/f 噪声、均方根 (RMS) |

| 噪声与等效噪声带宽226                |

| 运算放大器噪声指数:不要被误导232          |

| 运算放大器失真: HD、THD、            |

| THD + N, IMD, SFDR, MTPR238 |

| 运算放大器带宽和带宽平坦度246            |

| 运算放大器建立时间252                |

| 运算放大器开环增益与开环增益非线性256        |

| 运算放大器总输出失调电压计算261           |

| 运算放大器电源抑制比 (PSRR) 与电源电压263  |

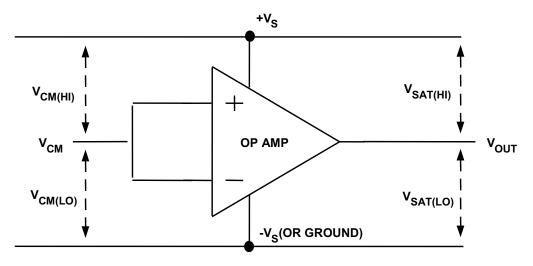

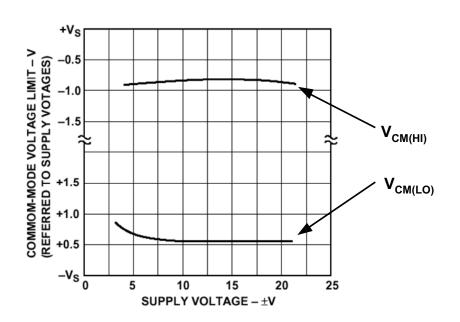

| 运算放大器输入、输出、单电源和轨到轨问题266     |

| 运算放大器输入偏置电流278              |

| 运算放大器输入和输出共模与差分电压范围283      |

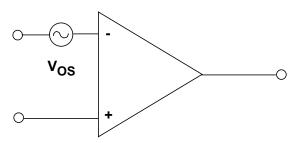

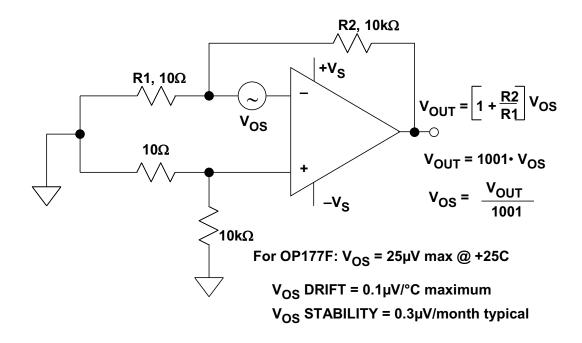

| 运算放大器输入失调电压287              |

| 运算放大器输入阻抗297                |

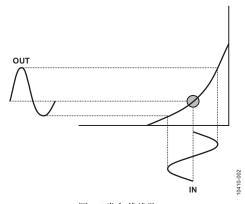

| 运算放大器输出相位反转和输入过压保护300       |

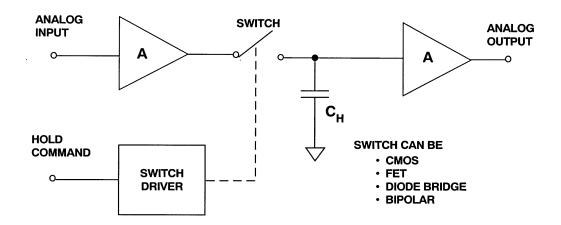

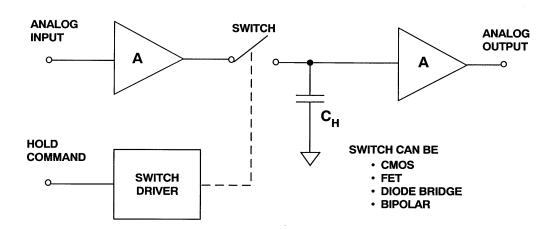

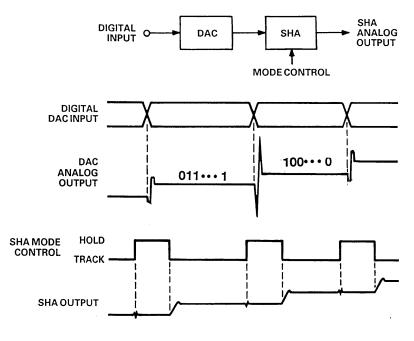

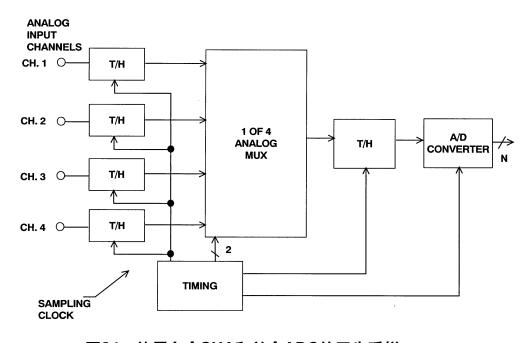

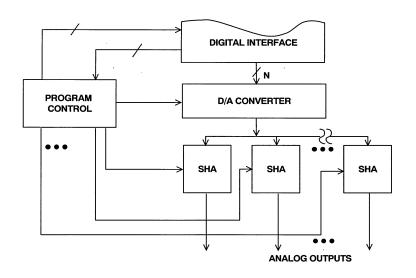

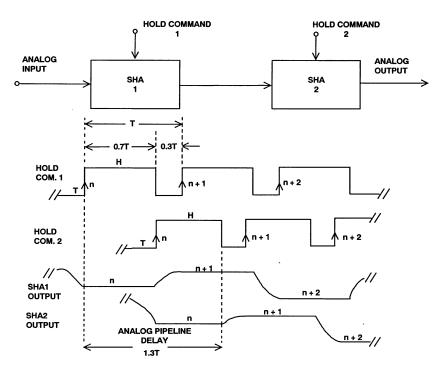

| 采样保持放大器309                  |

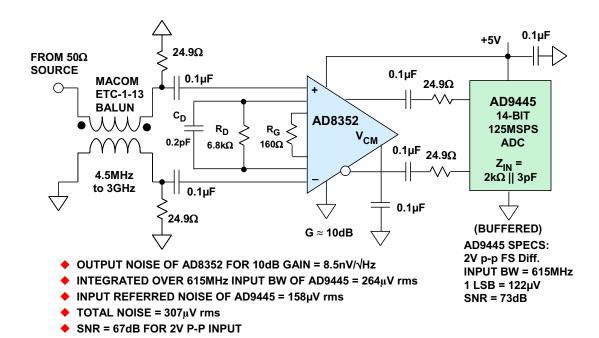

| 高速 ADC 用差分驱动器概述330          |

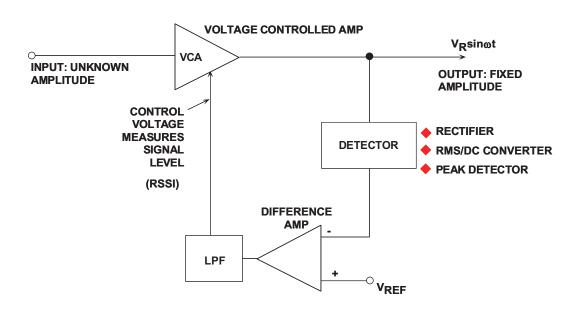

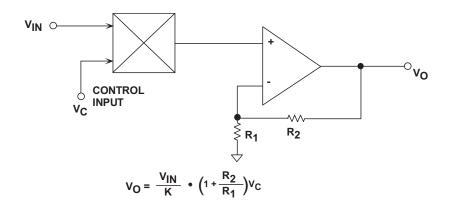

| 高速可变增益放大器 (VGA)339          |

| 高速电压反馈运算放大器348              |

| 高速电流反馈运算放大器358              |

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# Bainter陷波滤波器

作者: ADI公司 Hank Zumbahlen

#### 引言

Bainter运算放大器陷波滤波器是一种简单的陷波滤波器, 也是一系列小型指南中描述的多种分立式电路之一。

#### BAINTER陷波滤波器简介

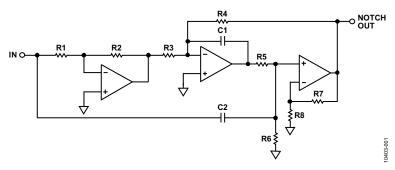

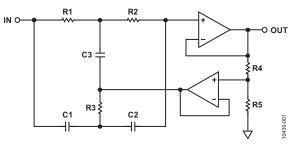

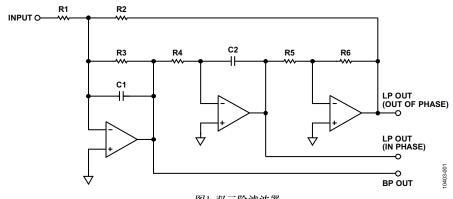

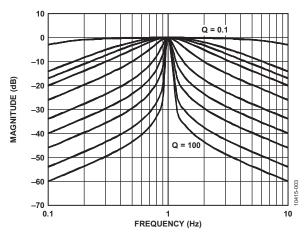

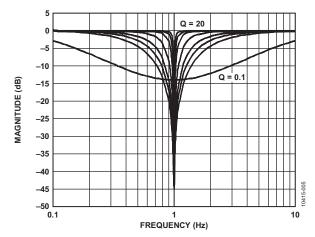

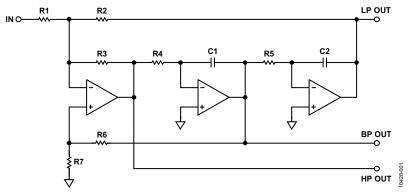

Bainter电路是一种简单的陷波滤波器(见参考文献部分), 它由简单的电路模块构成,带有两个反馈环路,如图1所 示。可以实现低通、高通和标准陷波响应。 图1中的电路有几种有趣的特性。陷波的Q并不像其他实现 方式一样是以元件匹配为基础的,而是只与放大器的增益 有关。因此,陷波深度不会随温度、老化和其他环境因素 而变化。虽然陷波频率可能变化,但陷波深度不会。另 外,元件灵敏度很低。

#### 滤波器原理图

放大器开环增益为 $10^4$ 时, $Q_z>200$ ,可以实现正交调谐,相互影响极小。R6调谐Q, $R1调谐\omega_z$ 。改变R3的值会设定  $\omega_0/\omega_z$ 比,结果产生低通陷波响应(R4>R3)、陷波响应(R4=R3)或高通陷波响应(R4<R3)。K1和K2的值分别设定陷波频率以上和以下的增益。一般初始值为1。

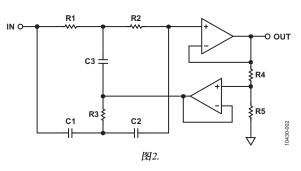

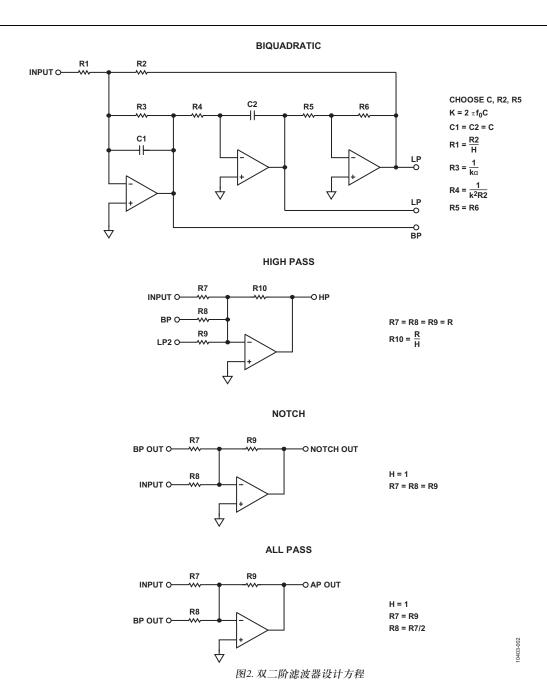

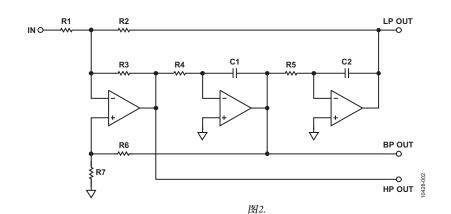

有关Bainter电路的设计方程式如图2所示。

图1. Bainter陷波滤波器

#### 设计方程

图2. Bainter陷波滤波器设计方程式

#### 参考文献

Bainter, J. R. "Active Filter Has Stable Notch and Response Can Be Regulated," *Electronics*, Oct. 2, 1975, pages 115 to 117. Zumbahlen, Hank. *Linear Circuit Design Handbook*. Elsevier. 2008. ISBN: 978-7506-8703-4.

#### 修订历史

2012年4月—修订版0: 初始版

# 三运算放大器仪表放大器基本结构

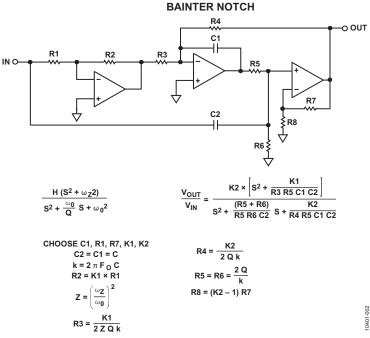

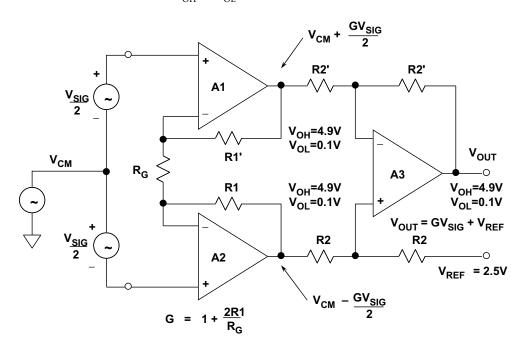

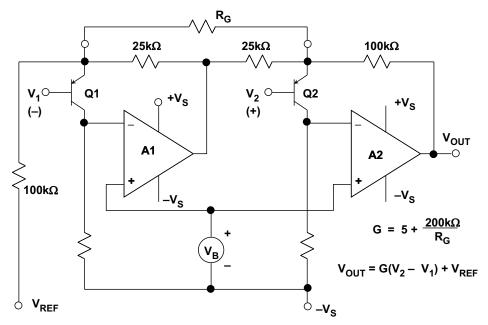

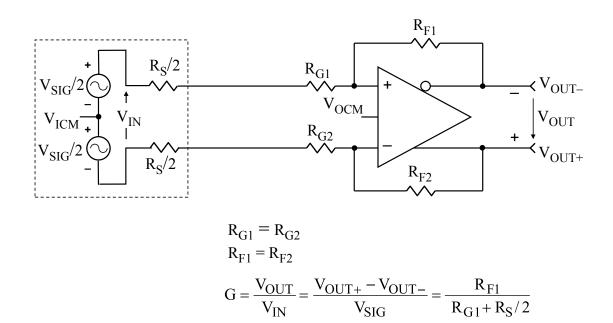

第二种常见的仪表放大器架构基于三运算放大器,显示于以下图1中。此电路通常称为三运算放大器仪表放大器。

图1: 三运算放大器仪表放大器

电阻R<sub>G</sub>设置此放大器的总增益。该电阻可以是内部、外部或(软件或引脚绑定)可编程电阻,视仪表放大器而定。在此配置下,CMR取决于R3/R2与R3'/R2'的比率匹配。另外,共模信号的放大因子为1,不受增益影响,(R<sub>G</sub>中不会出现共模电压,即是说其中不会流过共模电流,因为运行正常的运算放大器的输入引脚之间不存在显著的电位差)。

由于A1-A2中的差分对CM增益比率较高,该仪表放大器的CMR理论上与增益呈比例变化。大共模信号(A1-A2运算放大器余量限制以内)可在所有增益下处理。最后,鉴于这种配置的对称性,输入放大器中的共模误差(若采样)常常被减法器输出级消除。这些特性使得该三运算放大器仪表放大器配置能够提供最高性能,也是其大受欢迎的原因所在。

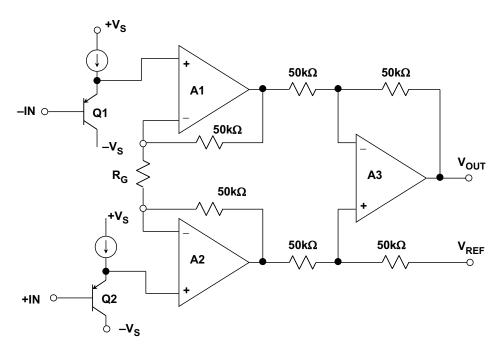

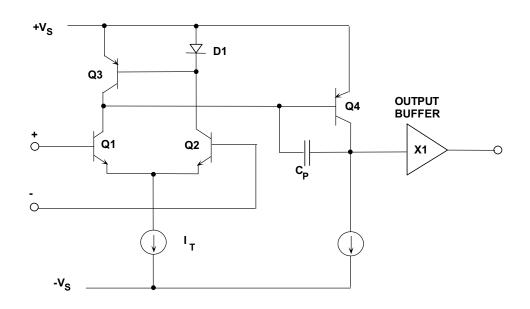

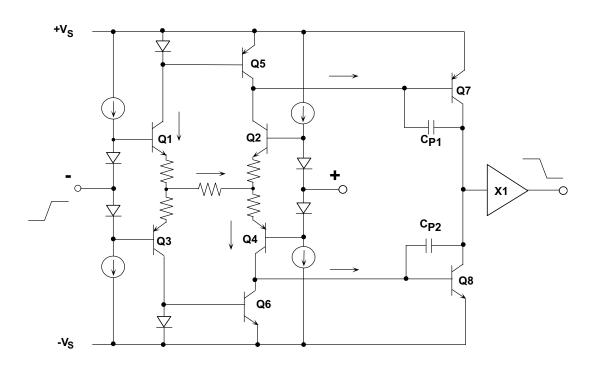

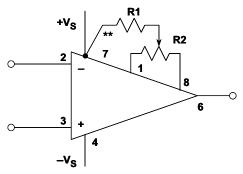

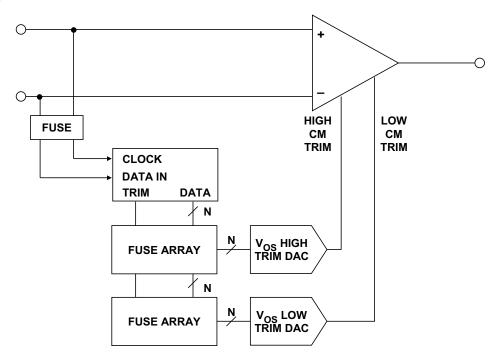

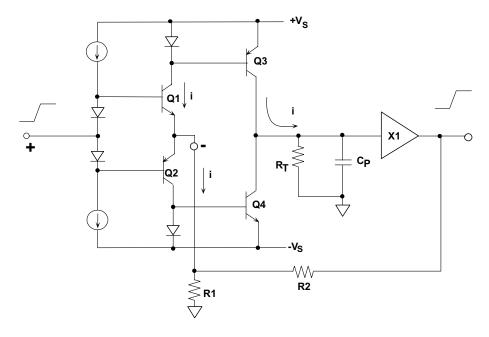

经典三运算放大器结构已经用于多种单芯片IC仪表放大器,包括业界标准AD620。除了三个内部运算放大器之间的出色匹配,薄膜激光调整电阻还具有极佳的比率匹配和增益精度,而且成本远远低于使用分立式精密运算放大器和电阻网络。AD620是单芯片IC仪表放大器技术的很好范例。以下图2给出了简化器件原理图。

图2: AD620 仪表放大器简化原理图

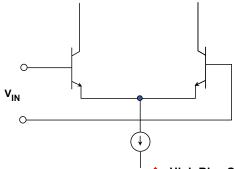

AD620是一款颇受欢迎的仪表放大器,额定电源电压范围为±2.3 V至±18 V。输入电压噪声在1 kHz下仅为9 nV/√Hz。由于Q1-Q2使用了Superbeta晶体管,最大输入偏置电流仅为1 nA。

内部400 Ω薄膜限流电阻与二极管(从Q1和Q2的发射极连接至基极)配合使用,从而提供过压保护功能。增益G由单一外部R<sub>c</sub>电阻设置,如以下公式1所示。

$$G = (49.4k\Omega/R_G) + 1$$

公式1

结合该公式和图2可以看出,AD620内部电阻经过调整,使得标准1%或0.1%电阻可用于将增益设置为常用值。

与双运算放大器仪表放大器配置一样,三运算放大器仪表放大器的单电源供电需要清楚内部节点电压。以下图3显示了采用+5 V单电源供电的仪表放大器的一般框图。各运算放大器的最大和最小容许输出电压分别指定为 $V_{OH}$ (最高输出)和 $V_{OL}$ (最低输出)。

请注意,从共模电压到A1和A2输出端的增益为单位增益。可以说,这些输出上的共模电压和信号电压之和必须在放大器输出电压范围内。

Page 2 of 5

4

显然该配置无法处理0 V或+5 V的输入共模电压,因为A1和A2已经饱和。与双运算放大器 仪表放大器一样,输出基准位于V<sub>OH</sub>和V<sub>OL</sub>中间,以提供双极性差分输入信号。

图3: 三运算放大器仪表放大器+5 V单电源限制

虽然有许多优秀的单电源仪表放大器,最高性能的器件仍然是那些采用传统双电源供电的器件,例如上述AD620,还有最近推出的AD8221和AD8222。在特定应用中,即使像AD620这样专为双电源供电而设计的器件,也可在单电源系统上发挥完整精度。

#### AD623单电源仪表放大器

与前述对应的双运算放大器仪表放大器一样,三运算放大器仪表放大器需要仔细设计,以实现单电源上的宽共模范围输入。以下图4所示的AD623单电源仪表放大器配置提供了很有吸引力的解决方案。该器件中,PNP发射极跟随器电平转换器Q1和Q2使输入信号可低于负电源150 mV,同时保持在正电源的1.5 V范围内。AD623的额定电源电压为+3 V至+12 V(单电源)或±2.5 V至±6 V(双电源)。

Page 3 of 5

图4: AD623单电源仪表放大器架构

AD623数据手册包含容许输入/输出电压范围的详细说明及数据,此范围与增益和电源电压成函数关系。此外,ADI网站提供交互式设计工具,可为许多仪表放大器执行关于这些参数的增益和范围计算,包括AD623。图5总结了AD623的主要规格特性。

- Wide Supply Range: +3V to ±6V

- ♦ Input Voltage Range: -V<sub>S</sub> 0.15V to +V<sub>S</sub> 1.5V

- ♦ 575µA Maximum Supply Current

- ♦ Gain Range: 1 to 1000

- ◆ 100µV Maximum Input Offset Voltage (AD623B)

- ♦ 1µV/°C Maximum Offset Voltage TC (AD623B)

- 50ppm Gain Nonlinearity

- ♦ 105dB CMR @ 60Hz, 1k $\Omega$  Source Imbalance, G ≥ 100

- ◆ 3µV p-p 0.1Hz to 10Hz Input Voltage Noise (G = 1)

#### 图5: AD623仪表放大器主要规格特性

AD8223是一款集成式单电源仪表放大器,采用单电源(+3.0 V至+25 V)供电时提供轨到轨输出摆幅。输入共模电压包括负供电轨。AD8223可以通过单一增益设置电阻进行编程,并遵照8引脚工业标准引脚排列配置,赋予用户出众的灵活性。不接外部电阻时,AD8223配置为G = 5;连接外部电阻时,AD8223可通过编程实现最高增益1000。AD8223利用了本教程介绍的三运算放大器架构。

#### 参考文献

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 5 of 5 7

## 二阶系统的运算放大器总输出噪声计算

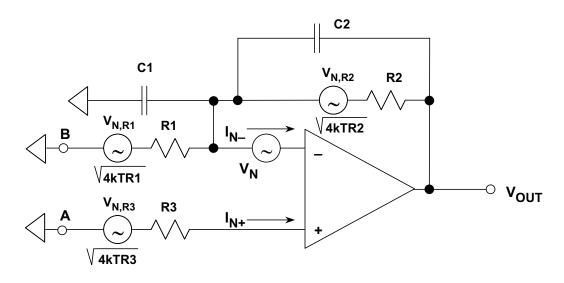

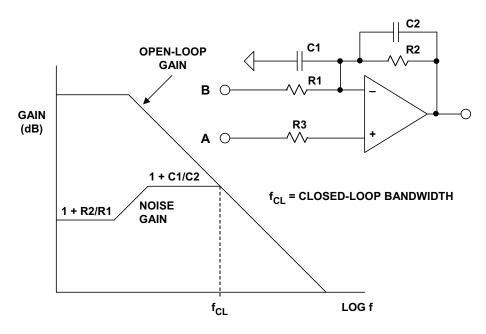

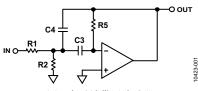

"<u>指南MT-049</u>"中分析了单极点系统的总输出噪声。下面图1所示的电路表示一个二阶系统,其中电容C1表示源电容、反相输入的杂散电容、运算放大器的输入电容或这些电容的任意组合。C1会导致噪声增益出现断点,C2则是为取得稳定性而必须添加的电容。

图1:带电抗元件的运算放大器噪声模型(二阶系统)

由于存在C1和C2,噪声增益是频率的函数,并在较高频率下有峰化现象(假定选择C2,使该二阶系统处于临界阻尼状况)。只要使R1×C1 = R2×C2,就可以实现平坦的噪声增益。

不过,对于电流电压转换器,R1通常为高阻抗,因此该方法不起作用。在这些情况下,要使信号带宽最大有点复杂,详见"指南MT-059"。

向输入端A施加直流信号(B接地)时,增益(即低频噪声增益)为1 + R2/R1。在较高频率下, 从输入端A到输出端的增益变为1 + C1/C2(高频噪声增益)。

请注意,闭环带宽f<sub>c</sub>是噪声增益与开环增益相交点的频率。向B施加直流信号(A接地)时,增益为-R2/R1,其中高频截止点由R2-C2决定。从B到输出端的带宽为1/2πR2C2。

同相输入端的电流噪声 $I_{N+}$ 流过R3会引起 $I_{N+}$ R3的噪声电压,与运算放大器噪声电压 $V_N$ 和R3的约翰逊噪声 $\sqrt{(4kTR3)}$ 一样,该噪声电压会被与频率相关的噪声增益放大。R1的约翰逊噪声会在 $1/2\pi$ R2C2带宽范围内放大-R2/R1,R2的约翰逊噪声则根本不会放大,而是在 $1/2\pi$ R2C2带宽范围内直接连接到输出。反相输入端的电流噪声 $I_{N-}$ 仅会流过R2,进而在 $1/2\pi$ R2C2带宽范围内导致放大器输出端出现大小为 $I_N$ R2的电压。

如果我们考虑这六种噪声贡献,则会发现如果R1、R2和R3很小,那么电流噪声和约翰逊噪声的影响将降至最低,主要噪声将是运算放大器的电压噪声。随着我们增加电阻,约翰逊噪声和噪声电流产生的电压噪声将升高。

如果噪声电流很小,那么约翰逊噪声将取代电压噪声而成为主要的噪声贡献。不过,约翰逊噪声随着电阻平方根增加而升高,电流噪声电压则随着电阻增加而呈线性升高,因此最终随着电阻继续增加,噪声电流引起的电压将成为主要因素。

无论输入端是连接到节点A还是节点B(另一个则接地或连接到其它低阻抗电压源),上文分析到的这些噪声贡献都不受影响,这也是为何出现在运算放大器电压噪声 $V_N$ 上的同相增益(1 + Z2/Z1)会被称为"噪声增益"的原因所在。

要计算二阶运算放大器系统的总输出rms噪声,需要将这六个噪声电压分别乘以相应的增益,然后在相应的频率上进行积分,如图2所示(下图)。

| NOISE SOURCE EXPRESSED<br>AS A VOLTAGE                                    | MULTIPLY BY THIS FACTOR<br>TO REFER TO OUTPUT | INTEGRATION<br>BANDWIDTH |

|---------------------------------------------------------------------------|-----------------------------------------------|--------------------------|

| Johnson noise in R3:<br>√(4kTR3)                                          | Noise Gain as a function of frequency         | Closed-Loop BW           |

| Non-inverting input current<br>noise flowing in R3:<br>I <sub>N+</sub> R3 | Noise Gain as a function of frequency         | Closed-Loop BW           |

| Input voltage noise:<br>V <sub>N</sub>                                    | Noise Gain as a function of frequency         | Closed-Loop BW           |

| Johnson noise in R1:<br>√(4kTR1)                                          | –R2/R1 (Gain from B to output)                | 1/2πR2C2                 |

| Johnson noise in R2:<br>√(4kTR2)                                          | 1                                             | 1/2πR2C2                 |

| Inverting input current noise<br>flowing in R2:<br>I <sub>N</sub> _R2     | 1                                             | 1/2πR2C2                 |

图2: 二阶系统折合到输出端的噪声源

Page 2 of 3 9

然后,所有输出贡献因素的和方根即代表总rms输出噪声。幸运的是,多数情况下,适当假设并识别主要噪声贡献因素,可以极大简化这个复杂繁琐的过程。

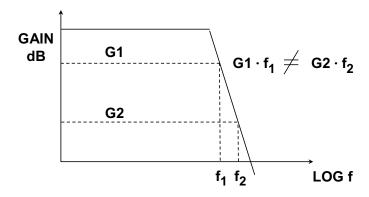

典型二阶系统的噪声增益如下面的图3所示。虽然两步内即可很容易地完成电压噪声积分,但请注意,由于存在峰化现象,因此输入电压噪声引起的输出噪声主要由噪声增益为1+C1/C2的高频部分决定。这是二阶系统的典型响应类型。反相输入电流噪声、R1和R2引起的噪声仅在1/2πR2C2带宽上积分。

图3: 典型二阶系统的噪声增益

# 参考文献

- Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 1.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 1.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

10

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# 从低通到带通滤波器的转换

作者: Hank Zumbahlen, Analog Devices, Inc.

#### 引言

有一种转换算法可将低通极点转换成等效带通极点。 这是一系列介绍分立式运算放大器电路的小型指南 之一。

#### 简介

根据极点的距离,可将带通滤波器分成宽带或窄带两种。如果带通滤波器的转折频率分离的较远(超过2个倍频程),则滤波器为宽带,由独立的低通和高通部分构成,并呈级联关系。本小型指南将主要介绍窄带滤波器。

这里的假设是对于分离较远的极点,它们之间的相互作用 很小。这种情况并不适用于窄带带通滤波器,因为这种情况下,转折频率相差不到2个倍频程。

滤波器一般用低通原型进行描述,因为低通是标准配置。要把该滤波器转换成带通,先从低通原型的复数极点对α和β开始。已知该极点对为复数共轭极点对。这意味着在直流周围(0 Hz.)是对称的。转换成带通的过程是将低通原型直流周围的响应镜像到新中心频率F<sub>0</sub>左右的相同响应的过程。

显然,这意味着当完成带通转换时,极点和零的数量将翻一番。与低通一样,实数轴以下的极点和零忽略不计。因此,一个n阶低通原型转换成了一个n阶带通,即使滤波器的阶数为2n。n阶带通滤波器由n部分构成,与其对比低通原型则由n/2部分构成。方便起见,不妨把响应设想成n个上极点和n个下极点。

通过以下方式确定Qgp的值

$$Q_{BP} = \frac{F_0}{BW} \tag{1}$$

其中, BW 为某电平下的带宽, 一般为-3 dB。

#### 一种转换算法

Geffe定义了一种转换算法(见参考文献部分),用以将低通 极点转换成等效带通极点。

若已知低通原型的极点位置

$$-\alpha \pm j\beta$$

(2)

以及 $F_0$ 和 $Q_{BP}$ 的值,则以下计算将得到两组Q值和频率 $F_H$ 和 $F_I$ ,结果定义了一对带通滤波器部分。

$$C = \alpha^2 + \beta^2 \tag{3}$$

$$D = \frac{2\alpha}{Q^{BP}} \tag{4}$$

$$E = \frac{C}{O_{RP}^2} + 4 \tag{5}$$

$$G = \sqrt{E^2 - 4D^2} \tag{6}$$

$$Q = \sqrt{\frac{E+G}{2D^2}} \tag{7}$$

注意,各部分的Q相同。

极点频率取决于

$$M = \frac{\alpha Q}{Q_{RP}} \tag{8}$$

$$W = M + \sqrt{M^2 - 1} \tag{9}$$

$$F_{BP1} = \frac{F_0}{W} \tag{10}$$

$$F_{BP2} = W F_0 \tag{11}$$

每个极点对转换同时也将导致2个位于原点的零点。

将幅度为 $\alpha_0$ 的归一化低通实数极点转换成一个带通部分, 其中,

$$Q = \frac{Q_{BP}}{\alpha_0} \tag{12}$$

频率为F。。

每次极点转换也会在原点产生一个零点。

# MT-215

椭圆函数低通原型同时含有零和极点。在转换滤波器时,必须同时转换这些零点。若低通零点为 $\pm$  j $\omega_z$ ,则带通零点如下:

$$M = \frac{\alpha Q}{Q_{RP}} \tag{13}$$

$$W = M + \sqrt{M^2 - 1} \tag{14}$$

$$F_{BP1} = \frac{F_0}{W} \tag{15}$$

$$F_{BP2} = W F_0 \tag{16}$$

由于带通滤波器的增益在F<sub>BP</sub>而非F<sub>0</sub>时出现峰值,因此需要 对幅度函数作出调整,用以归一化合并后的滤波器的响 应。各滤波器部分的增益如下:

$$A_R = A_0 \sqrt{1 + Q^2 \left(\frac{F_0}{F_{BP}} - \frac{F_{BP}}{F_0}\right)^2}$$

(17)

其中:

A。= 滤波器中心频率下的增益

A<sub>R</sub> = 谐振时的滤波器部分增益

F。= 滤波器中心频率

F<sub>RP</sub> = 滤波器部分谐振频率

现在,低通原型被转换成了带通滤波器。以上的一系列等式是用来转换使用的。原型滤波器的每个极点都转换成一个极点对。因此,转换完成时,3极点原型将拥有6个极点(3个极点对)。此外,原点处将有6个零点。

#### 极点位置

LP原型的极点位置来自设计表(见MT-206)。表1对其进行了总结。

#### 表1.

| 级 | α      | β      | F <sub>0</sub> | α      |

|---|--------|--------|----------------|--------|

| 1 | 0.2683 | 0.8753 | 1.0688         | 0.5861 |

| 2 | 0.5366 |        | 0.6265         |        |

第一级为极点对,第二级为单极点。请注意,用α表示两个完全不同的参数的做法是不可取的。左侧的α和β为复平面上的极点位置。这些是转换算法中使用的值。右侧的α为1/Q,这正是物理滤波器设计等式所希望看到的。

转换过程的部分工作是指定可合成的滤波器的3 dB带宽。 在这种情况下,该带宽将被设为500 Hz。转换结果如下表 所示:

#### 表2.

| 级 | F <sub>o</sub> | Q    | $A_0$ |

|---|----------------|------|-------|

| 1 | 804.5          | 7.63 | 3.49  |

| 2 | 1243           | 7.63 | 3.49  |

| 3 | 1000           | 3.73 | 1     |

前两级存在增益要求的原因在于,相对于总滤波器中心频率,它们的中心频率将会衰减。由于结果得到的Q适中(小于20),因而将选用多级反馈拓扑结构(见MT-218)。

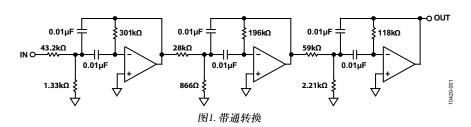

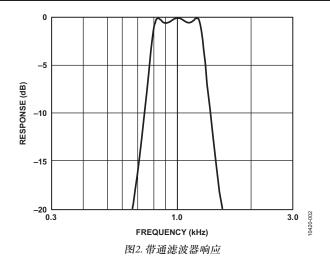

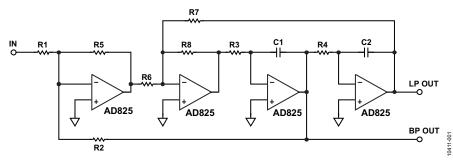

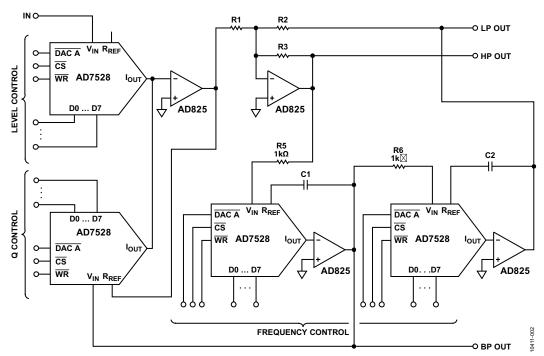

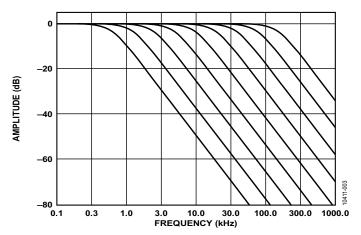

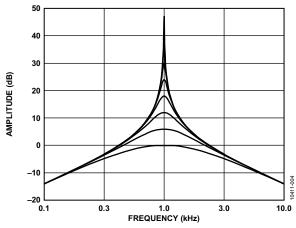

图1为该滤波器的示意图,图2所示为频率响应。

请注意,中心频率周围还是存在对称性。另外,500 Hz的带宽并不表示中心频率两端各250 Hz(算术对称)。相反,对称是几何性的,意思是说幅度相等的任意两个频率(F,和F,)都具有以下关系

$$F_0 = \sqrt{F_1 \times F2} \tag{18}$$

## 参考文献

Geffe, P. R. "Designer's Guide to Active Band-Pass Filters," EDN, Apr. 5 1974, pp. 46-52.

Zumbahlen, Hank. Linear Circuit Design Handbook. Elsevier. 2008. ISBN: 978-7506-8703-4.

#### 修订历史

2012年3月—修订版0:初始版

# 小型指南 MT-216

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# 从低通到带阻(陷波) 滤波器的转换

作者: Hank Zumbahlen, Analog Devices, Inc.

#### 引言

有一种转换算法可将低通极点转换成等效带阻极点。 这是一系列介绍分立式运算放大器电路的小型指南 之一。

#### 简介

就如带通滤波器一样,根据极点的距离,可将带阻滤波器 分成宽带或窄带两种。为避免混淆,可采用一种惯例。如 果滤波器为宽带,则称为带阻滤波器。窄带滤波器被称为 陷波滤波器。

在某些情况下,如从低电平传感器测量值中消除电力线频率(嗡嗡声),可以设计一种针对具体频率的陷波滤波器。

就如带通是由低通原型直接转换的一样(其中,直流被转换成 $F_0$ ),陷波滤波器可以先转换成高通滤波器,然后再将直流(现在为零)转换为 $F_0$ 。

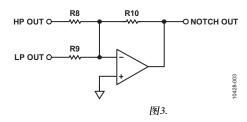

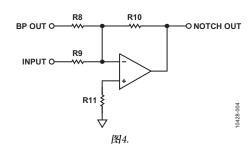

构建陷波滤波器的一种方法是将其当作带通滤波器构建, 并从输入中减去输出(1-BP)。另一种方法是采用级联低通 和高通部分,尤其是在带阻(宽带)的情况下。在这种情况 下,各部分相并行,差异体现在输出上。

一种更通行的做法是直接转换极点。陷波转换会给每一个 低通极点对带来两对复数极点和一对二阶虚数零点。

通过以下方式确定Qgp的值

$$Q_{BR} = \frac{F_0}{BW} \tag{1}$$

其中, BW 为某电平下的带宽, 一般为-3 dB。

#### 一种转换算法

若已知低通原型的极点位置

$$-\alpha \pm j\beta \tag{2}$$

以及 $F_0$ 和 $Q_{BR}$ 的值,则以下计算将得到两组Q值和频率 $F_H$ 和 $F_I$ ,结果定义了一对陷波滤波器部分。

$$C = \alpha^2 + \beta^2 \tag{3}$$

$$D = \frac{\alpha}{Q_{RR}C} \tag{4}$$

$$E = \frac{\beta}{O_{RR}C} \tag{5}$$

$$F = E^2 - D^2 + 4 (6)$$

$$G = \sqrt{\frac{F}{2} + \sqrt{\frac{F2}{4}} + D^2 E^2} \tag{7}$$

$$H = \frac{DE}{G} \tag{8}$$

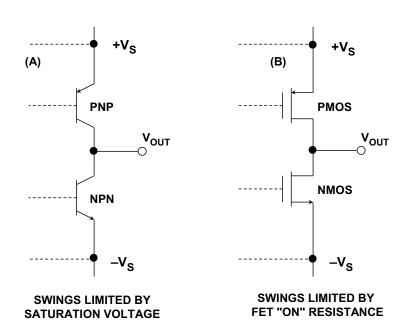

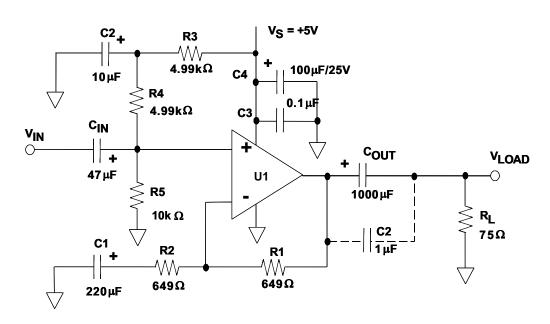

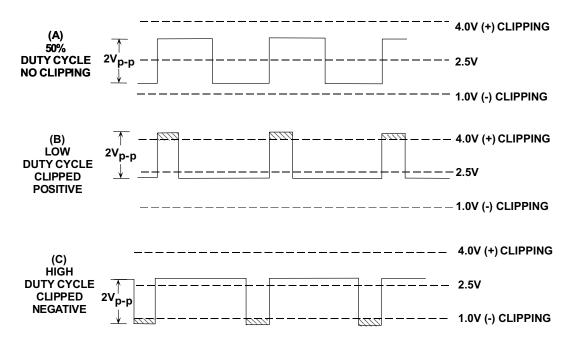

$$K = \frac{1}{2}\sqrt{(D+H)^2 + (E+G)^2}$$

(9)

$$Q = \frac{K}{D + H} \tag{10}$$

极点频率取决于

$$F_{BR1} = \frac{F_0}{K} \tag{11}$$

$$F_{RR2} = K F_0 \tag{12}$$

$$F_7 = F_0 \tag{13}$$

$$F_0 = \sqrt{F_{BR1} \times F_{BR2}} \tag{14}$$

其中,F<sub>0</sub>为陷波频率以及F<sub>BR1</sub>和F<sub>BR2</sub>的几何均值。

一个简单的实数极点α<sub>0</sub>转换成一个部分,其Q值用下式算出:

$$Q = Q_{BP} \alpha_0 \tag{15}$$

其中,频率 $F_{RR} = F_0$ 。在 $F_0$ 处还有转换零点。

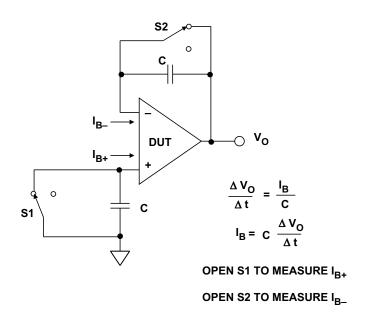

假设在B的带宽下需要A dB的衰减,则单频陷波需要的Q取决于

$$Q = \frac{\omega_0}{B\sqrt{10^{0.1A} - 1}} \tag{16}$$

原型被转换成一种带阻滤波器。对此,再次使用了以上一系列等式。原型滤波器的每个极点都转换成一个极点对。 因此,转换完成时,3极点原型将拥有6个极点(3个极点 对)。

就如带通一样,转换过程的部分工作是指定合并后的滤波器的3 dB带宽。

# **MT-216**

同样,在这种情况下,该带宽被设为500 Hz。LP原型的极点位置来自设计表(见MT-206)。

#### 极点位置

低通原型的极点位置来自设计表(见MT-206)。

表1.

| 级 | α      | β      | F <sub>0</sub> | α      |

|---|--------|--------|----------------|--------|

| 1 | 0.2683 | 0.8753 | 1.0688         | 0.5861 |

| 2 | 0.5366 |        | 0.6265         |        |

第一级为极点对,第二级为单极点。请注意,用α表示两个完全不同的参数的做法是不可取的。左侧的α和β为复平面上的极点位置。这些是转换算法中使用的值。右侧的α为1/Q,这正是物理滤波器设计等式所希望看到的。

转换结果将产生如表2所示结果。

#### 表2.

| 级 | F <sub>o</sub> | Q    | F <sub>oz</sub> |

|---|----------------|------|-----------------|

| 1 | 763.7          | 6.54 | 1000            |

| 2 | 1309           | 6.54 | 1000            |

| 3 | 1000           | 1.07 | 1000            |

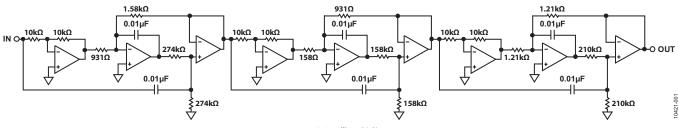

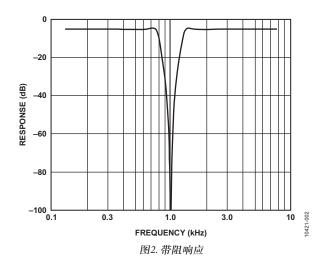

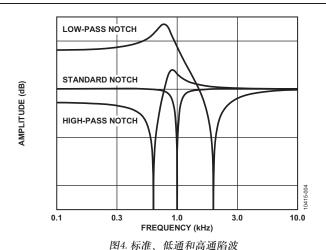

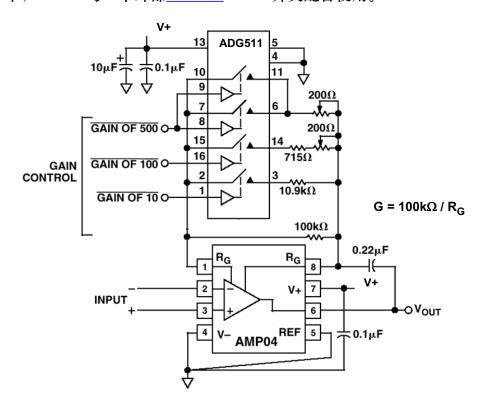

请注意,所需陷波滤波器有三种情况。即标准陷波 $(f_0=f_z)$ ,第3部分),低通陷波 $(F_0<F_z)$ ,第1部分),以及高通陷波 $(F_0>F_z)$ ,第2部分)。由于需要全部三类陷波,因而用Bainter陷波来构建滤波器。

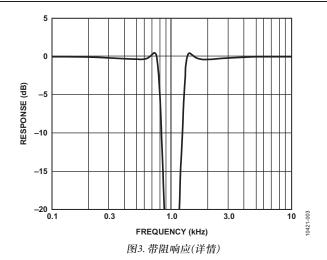

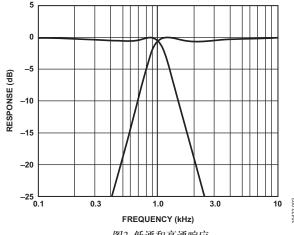

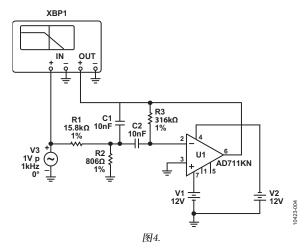

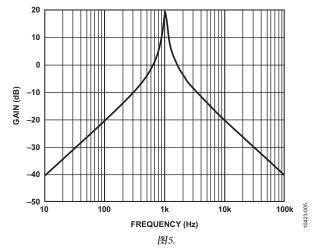

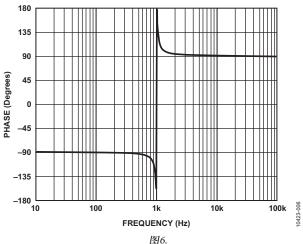

图1为滤波器的示意图。滤波器的响应如图2所示,图3为 其详细情况。同时注意,中心频率周围存在对称性,而且 这些频率拥有的是几何对称性。

图1. 带阻转换

修订历史 2012年2月—修订版0:初始版

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

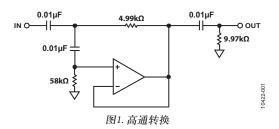

# 从低通到高通滤波器的转换

作者: ADI公司 Hank Zumbahlen

#### 引言

有一种转换算法可将低通极点转换成高通极点。这是 一系列介绍分立式运算放大器电路的小型指南之一。

#### 简介

滤波器一般用低通原型进行描述,因为低通是标准配置。 高通滤波器可以视为侧面接通的低通滤波器。

受原点零值的影响,其直流响应并不平坦,而是n×(20 dB/十倍频程)的上升响应,其中n为极点数。在转折频率条件下,受极点影响,上述上升响应会增加n×(-20 dB/十倍频程)的响应。结果是,在转折频率以外,会呈现平坦的响应。

以1/s缩放传递函数,可将低通原型转换成高通滤波器。实际上,这通常相当于将电容变成值为1/C的电感,而对于无源设计,则相当于将电感变成值为1/L的电容。对于有源设计,电阻变成值为1/R的电容,而电容则变成值为1/C的电阻。这仅适用于频率设置电阻,不适用于增益设置电阻(即并非适用于电路中的每个电阻或电容)。

#### 一种转换算法

考察转换的另一种方式是研究s平面的转换。低通原型的 复数极点对由一个实部α和一个虚部β构成。归一化高通极 点通过以下公式算出

$$\alpha_{HP} = \frac{\alpha}{+\beta^2} \tag{1}$$

以及

$$\beta_{HP} = \frac{\beta}{+\beta^2} \tag{2}$$

这样,一个简单的极点α。转换成

$$\alpha_{\omega,HP} = \frac{1}{\alpha_0} \tag{3}$$

低通零点(ωσιρ)通过以下公式转换

$$\omega_{Z,HP} = \frac{1}{\omega_{Z,LP}} \tag{4}$$

此外, 原点处将增加与极点数量相等的零点。

在将归一化低通原型极点和零点转换成高通之后,接着以与低通相同的方式(即以频率和阻抗)进行反向归一化处理。

作为例子,此处转换的是一个1 kHz、3极点、0.5 dB切比雪夫滤波器。选择切比雪夫滤波器的原因在于,如果响应不正确,它可以更清楚地显示出来;这种情况下,巴特沃兹则可能过于宽松。选择3极点滤波器是为了分别转换一个极点对和单个极点。

#### 极点位置

低通原型的极点位置来自设计表(见MT-206)。

表1.

| 级 | α      | β      | F <sub>o</sub> | α      |

|---|--------|--------|----------------|--------|

| 1 | 0.2683 | 0.8753 | 1.0688         | 0.5861 |

| 2 | 0.5366 |        | 0.6265         |        |

第一级为极点对,第二级为单极点。请注意,用α表示两个完全不同的参数的做法是不可取的。左侧的α和β为复平面上的极点位置。这些是转换算法中使用的值。右侧的α为1/Q,这正是物理滤波器设计等式所希望看到的。

转换结果将产生如表2所示结果。

#### 表2.

| 级 | α      | β      | F <sub>o</sub> | α      |

|---|--------|--------|----------------|--------|

| 1 | 0.3201 | 1.0443 | 0.9356         | 0.5861 |

| 2 | 1.8636 |        | 1.596          |        |

这里需要提醒一下。由于描述切比雪夫滤波器的一种习惯做法(即此处所用做法)是引用误差带的末端而非3 dB频率, 因此, F<sub>0</sub>必须除以(高通)纹波带与3 dB带宽的比值。

# **MT-217**

用Sallen-Key高通拓扑结构来构建滤波器(见MT-222)。原理 图见图1。

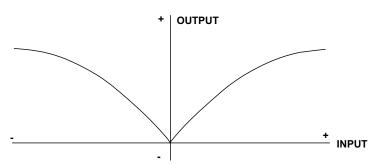

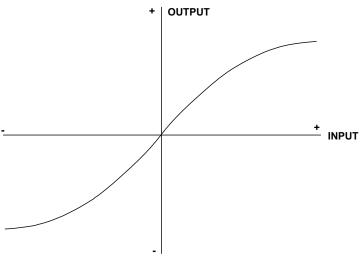

图2. 低通和高通响应

图2所示为低通原型和高通转换的响应。请注意,它们在 1 kHz截止频率左右是对称的。还应注意, 0.5 dB误差带位 于1 kHz, 而不是-3 dB点, 这是切比雪夫滤波器的一个特 征。响应的对称性验证了转换的精度。

修订历史 2012年3月—修订版0: 初始版

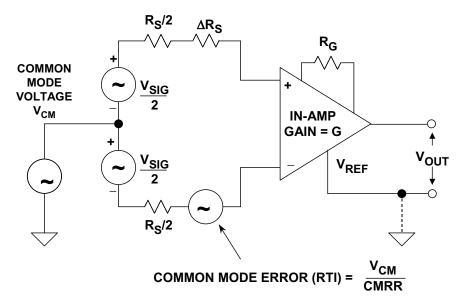

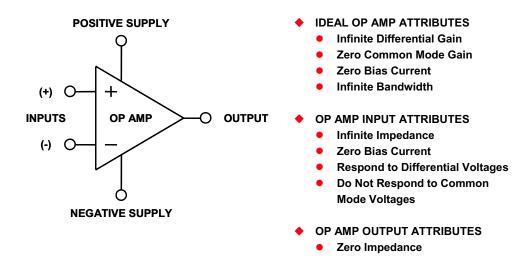

# 仪表放大器基础

在所有专用放大器中,可能最常用的就是仪表放大器。仪表放大器广泛运用于许多工业和测量领域,这些应用要求在高噪声环境下保持直流精度和增益精度,而且其中存在大共模信号(通常为交流电力线频率)。

#### 运算放大器/仪表放大器功能差异

仪表放大器在许多重要的方面都不同于运算放大器。运算放大器是一个通用增益模块,用户可采用R、C、和L(有时)这些外部反馈器件,对运放进行各种设置,最终配置和电路功能实际上取决于用户。

相比之下,仪表放大器的功能和允许的工作增益范围受到较多的限制。许多情况下,仪表放大器比运算放大器更适合完成其工作——尽管仪表放大器可能实际上是由一些运算放大器组成的!人们也常常会因功能而混淆仪表放大器,称其为"运算放大器"。但是相反的情况则几乎不成立。应该认识到,仪表放大器不只是一种特殊类型的运算放大器,这两种器件的功能实际上根本不同。

有一种方法或许能较好地区分这两种器件,就是记住:运算放大器凭借灵活的反馈,可以通过编程来实现几乎所有功能。相比之下,仪表放大器则不能通过编程实现所有功能。只能在规定范围内对增益进行编程设置。运算放大器通过大量外部器件进行配置,而仪表放大器则通过一个电阻或特定的引脚来配置其工作增益。

## 仪表放大器定义

仪表放大器是一个精密闭环增益模块,它有一对差分输入端和一个相对于参考端或共用端工作的单端输出,如下图1所示。其输入阻抗平衡并且阻值很高,典型值 $\geq$ 10° $\Omega$ 。仪表放大器采用内部反馈电阻网络,以及(通常)一个增益设置电阻 $R_G$ ,这一点也不同于运算放大器。另外,仪表放大器的内部电阻网络和 $R_G$ 与信号输入端隔离。仪表放大器增益还可以通过引脚选择的内部 $R_G$ 进行预设(也与信号输入端隔离)。仪表放大器增益范围通常为1至1000。

图1: 通用仪表放大器

仪表放大器产生以某个引脚为参考的输出电压,该引脚通常称为参考引脚或V<sub>REF</sub>。在许多应用中,该引脚连接至电路的接地端,但也可连接至其他电压端,只要其处于额定允许的电压范围即可。该特性在单电源应用中特别有用,此时输出电压通常以中间电源(即+5 V电源时为+2.5 V)为参考。

为了实现高效运作,仪表放大器需能够放大微伏电平信号,同时抑制其输入端的共模 (CM)信号电压。这要求仪表放大器必须具备极高的共模抑制(CMR)性能。仪表放大器的共模抑制典型值为70至100 dB以上,通常增益较高时共模抑制性能较佳。

必须注意,在大多数实际应用中,仅有直流输入的共模抑制规格是不够的。工业应用中最常见的外部干扰源是50/60 Hz的交流电源相关噪声(包括谐波)。进行差分测量时,这种干扰往往会对两个仪表放大器输入端产生相同的感应,因而干扰表现为共模输入信号。因此,确定频率范围内的共模抑制与确定其直流值同样重要。注意,两个源阻抗之间的不平衡会降低某些仪表放大器的共模抑制。ADI公司明确规定了仪表放大器50/60 Hz时的共模抑制,其中源阻抗不平衡为1 kΩ。

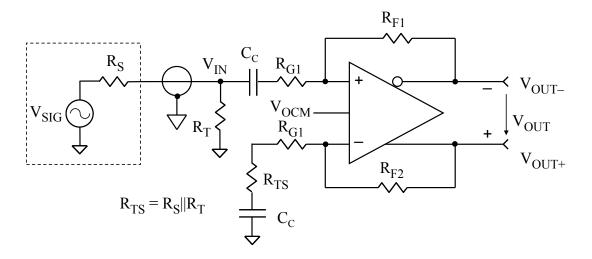

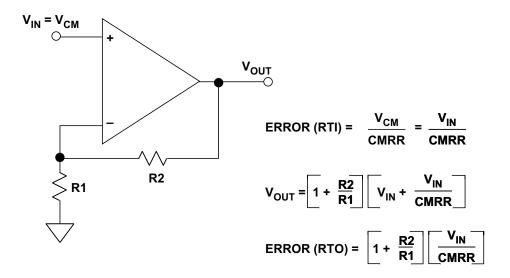

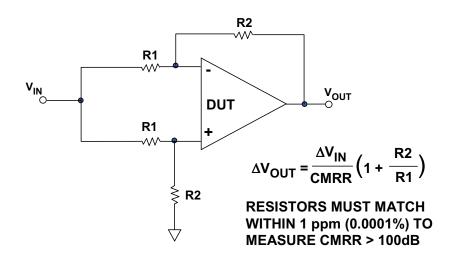

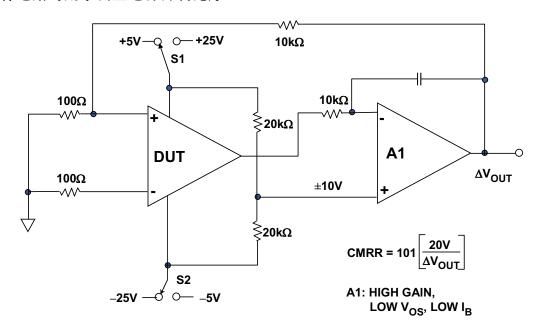

#### 减法器或差动放大器

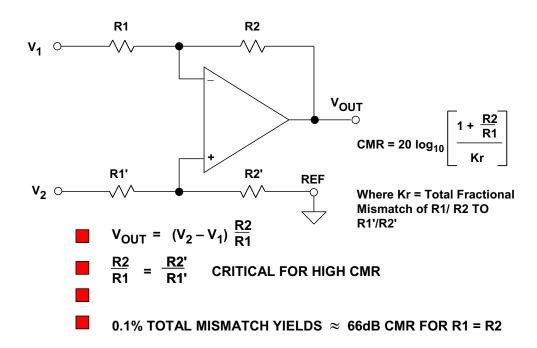

了解仪表放大器与减法器和或差动放大器之间的差别很重要。简单的减法器或差动放大器可由四个电阻和一个运算放大器组成,如下图2所示。必须注意,这不是一个真正的仪表放大器(根据之前讨论过的标准),但常用于一些需要简单的差分转单端转换的应用中。正因为使用广泛,所以需仔细研究该电路,目的是在讨论真正的仪表放大器结构之前,理解它的基本限制。

20

图2:运算放大器减法器或差动放大器

这个简单电路存在几个基本问题。首先,从 $V_1$ 和 $V_2$ 看到的输入阻抗不平衡。从 $V_1$ 看到的输入阻抗为R1,从 $V_2$ 看到的输入阻抗则为R1'+R2'。这个结构在共模抑制方面也相当有问题,因为即使是很小的源阻抗不平衡也会降低可用的共模抑制。采用和每个输入串联的匹配良好的开环缓冲器可以解决该问题(例如,采用精密双通道运算放大器)。但是,这会增加简单电路的复杂性,还可能会导致失调漂移和非线性。

该电路的第二个问题是共模抑制主要由电阻比匹配决定,而非运算放大器。电阻比R1/R2和R1/R2'必须匹配得非常好以此来抑制共模噪声,至少与典型运算放大器的共模抑制相当(≥100 dB)。还应注意,电阻绝对值相对而言不太重要。

从一批电阻中选择四个1%的电阻可能会产生0.1%的净电阻比匹配,使共模抑制达到66 dB(假设R1 = R2)。但是如果其中一个电阻和其它电阻相差1%,共模抑制可能会下降至仅46 dB。显然,在电路中采用普通分离电阻所获得的性能非常有限(不采用手动匹配)。因为最好标准的现成RNC/RNR型电阻的容差约为0.1%。

一般而言,这种电路最差情况下的共模抑制可通过下式计算:

$$CMR(dB) = 20 \log \left[ \frac{1 + R2 / R1}{4Kr} \right],$$

公式1

Page 3 of 5 21

其中Kr是小数形式的单电阻容差,此时采用4个分立电阻。上式显示,对于一个由4个没有经过挑选的相同标称值1%电阻组成的容差,最差情况下的共模抑制不会优于34 dB。

该电路可能会采用净匹配容差为Kr的单电阻网络,此时表达式如图所示,即:

$$CMR(dB) = 20 \log \left[ \frac{1 + R2 / R1}{Kr} \right]$$

公式2

用公式2计算,假定R1=R2,电阻比的净匹配容差为0.1%时,可得出最差情况的直流共模抑制为66 dB。注意,两种情况均假定较高的放大器共模抑制(即>100 dB)。显然,对高共模抑制而言,此类电路需要四个具有极高绝对值及温度系数匹配的单衬底电阻。此类网络采用厚/薄膜技术,Caddock和Vishay公司均可提供,其比率匹配0.01%或更佳。

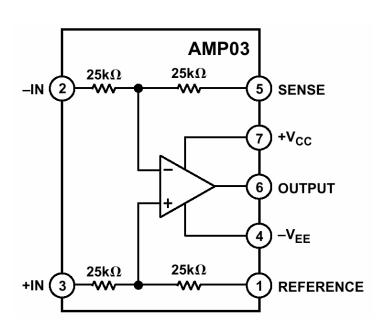

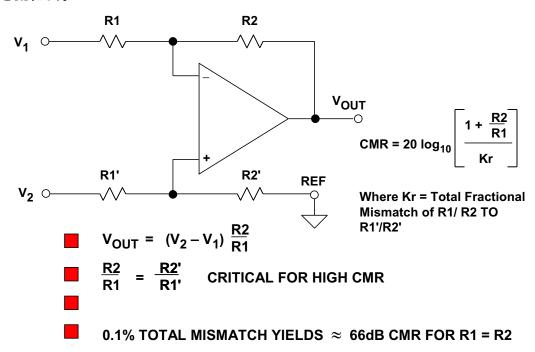

采用简单差动放大器时,与其招致高成本以及精密运算放大器和分离电阻网络带来的PCB面积限制,不如找出完整的单芯片解决方案。AMP03就是这样一款精密差动放大器,其中包括片内激光修调精密薄膜电阻网络。如下图3所示。AMP03F典型的共模抑制为100 dB,小信号带宽为3 MHz。

图3: AMP03精密差动放大器

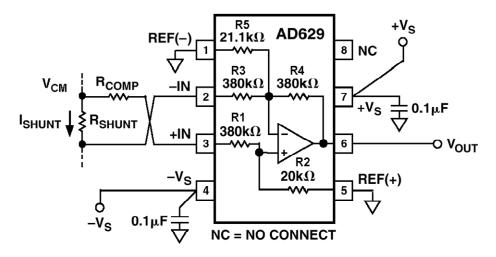

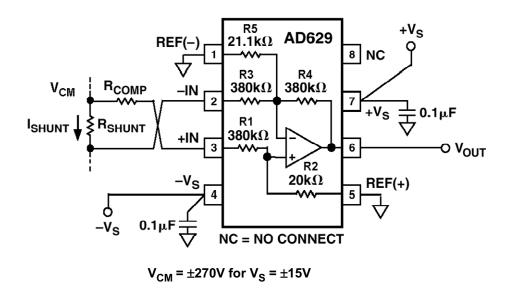

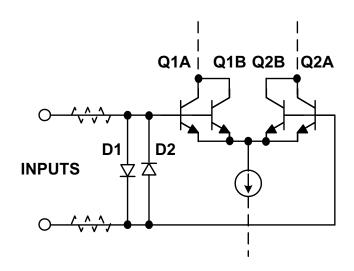

在AD629差动放大器中发现了一点关于简单差动放大器的有趣变化,这款放大器针对高共模输入电压进行了优化,典型的电流检测应用如下图4所示。AD629是一款单位增益差分转单端放大器,在电源电压为±15 V,小信号带宽为500 kHz情况下,可以处理±270 V的共模电压。

22

$V_{CM} = \pm 270V$  for  $V_S = \pm 15V$

图4:采用 AD629差动放大器的高共模电流检测

采用R1-R2分压器网络将同相输入(引脚3)衰减20倍,可以获得高共模电压范围。对于反相输入则选用电阻R5,使R5||R3等于电阻R2。电路的噪声增益等于20 [1 + R4/(R3||R5)],从而为差分输入电压提供单位增益。通过对R1-R5薄膜电阻进行激光晶圆修调,可使AD629B的最小共模抑制达到86 dB@500 Hz。在应用中,最好的做法是使两个输入的源阻抗保持平衡,因此选用虚拟电阻RCOMP,其阻值等于分流检测电阻RSHUNT的阻值。

#### 参考文献

- Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 5 of 5 23

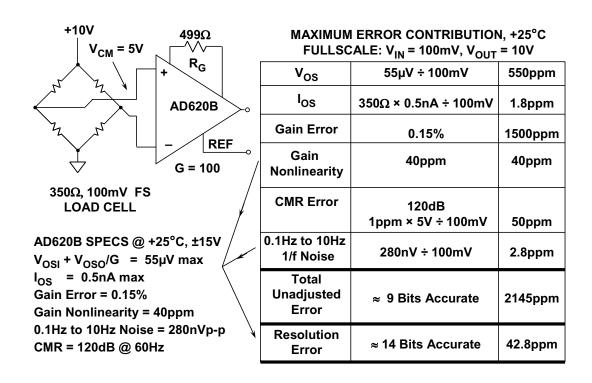

# 仪表放大器桥接电路误差预算分析

在典型应用中,有必要了解仪表放大器的误差源。下图1所示为一个350 Ω的称重传感器,当用10 V源激励时,其满量程输出为100 mV。用外部499 Ω增益设置电阻,将AD620的增益设为100。表中列出了每种误差源对2145 ppm的总非调整误差的贡献。但需要注意的是,增益、失调和CMR误差都可以通过系统校准消除。其余误差——增益非线性度和0.1 Hz至10 Hz噪声——无法通过校准消除,最终使系统分辨率限制为42.8 ppm(大约相当于14位精度)。当然,本例只是用于说明,但对于解决增益非线性度、LF噪声等性能限制性误差问题具有重要意义。

图1: AD620B 桥接放大器直流误差预算

ADI网站上提供了一种通用型放大器(包括仪表放大器)<u>误差预算分析</u>工具和<u>Analog</u> <u>Bridge Wizard™</u> 以协助桥接电路的设计。

## 参考文献

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN:0-915550-28-1. 另见*Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10:0750687037, ISBN-13:978-0750687034。Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, 另见*Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5.Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> Edition, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 2 of 2 25

# 仪表放大器直流误差源

仪表放大器的直流和噪声规格与常规运算放大器略有不同,因此需要进行讨论以全面了解 各种误差源。

#### 增益设置电阻误差

仪表放大器的增益通常通过单个电阻进行设置。如果电阻位于仪表放大器外部,则其值要 么根据公式计算,要么从数据手册中的表格中选择,具体取决于所需的增益。采用外部增 益设置电阻的仪表放大器有<u>AD620</u>、<u>AD623</u>、<u>AD627</u>、<u>AD8220</u>(JFET输入、轨到轨输出)、 <u>AD8221</u>、<u>AD8222</u>、<u>AD8223</u>和<u>AD8224</u>。

绝对值激光晶圆调整技术允许用户通过这一个电阻对增益进行精确编程。该电阻的绝对精度和温度系数直接影响着仪表放大器的增益精度和漂移。由于外部电阻不可能精确匹配内部薄膜电阻的温度系数,因此,应选择一个低温度系数TC (< 25 ppm/°C)金属薄膜电阻,其精度最好为0.1%或以上。

许多仪表放大器的额定增益范围一般为1至1000或者1至10000,因此,在较高增益下也能正常工作,但制造商并不保证能在这些高增益下实现特定性能水平。实践中,随着增益设置电阻变小,因金属走线和焊线电阻导致的误差将变大。这些误差再加上噪声和漂移的增加,结果可能使较高单级增益失去实用价值。另外,当反映到高增益输出时,输入失调电压可能变得很大。例如,对于增益为10000的输出,0.5 mV的输入失调电压将变成5 V。对于高增益,最佳做法是用一个仪表放大器作为前置放大器,然后用一个后置放大器进一步放大。

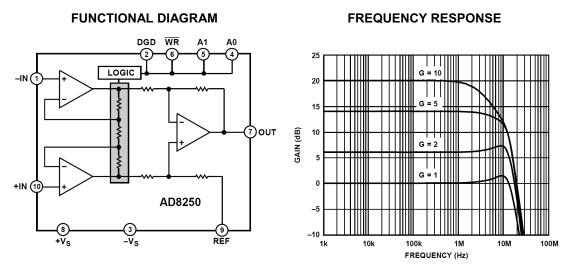

在引脚可编程增益仪表放大器(如AD621、AD624)中,增益设置电阻是内置的,而且匹配良好,并且器件增益精度和增益漂移规格包括了其效应。在其他方面,AD621与外部增益编程AD620相似。

AD8250、AD8251和AD8253同时具有引脚可编程增益和软件可编程增益,采用ADI公司  $iCMOS^{\circ}$ 工艺设计而成,工作电压为 $\pm 5$  V至 $\pm 15$  V。这些器件的输入阻抗处于 $G\Omega$ 范围之内。

#### 增益误差和增益非线性度

增益误差规格为与增益方程的最大偏差。单片仪表放大器(如AD8221(BR级))具有极低的工厂调整增益误差,该高品质仪表放大器的最大误差为0.02%(G=1)和0.15%(G=1000)。

注意,增益误差随着增益的增加而加大。尽管外部连接的增益网络允许用户精确设置增益,但外部电阻的温度系数以及网络中各电阻之间的温差都会加大整体增益误差。如果数据最终进行数字化处理并呈现给数字处理器,则可通过测量已知基准电压并乘以一个常数,来更正增益误差。

根据定义,增益非线性度指相对于输出与输入关系坐标图中一条直线的最大偏差。直线画在实际传递函数的终点之间。高品质仪表放大器的增益非线性度一般为0.01% (100 ppm)或以下,而且对推荐增益范围内的增益相对不太敏感。

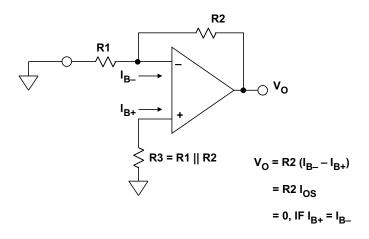

#### 输入失调电压与偏置电流误差

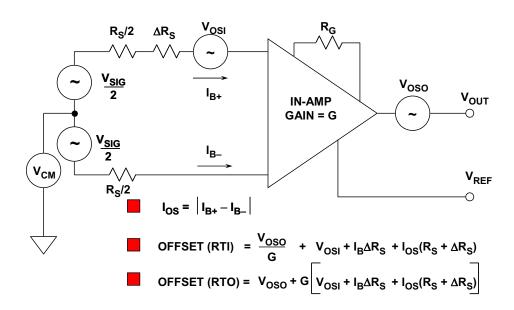

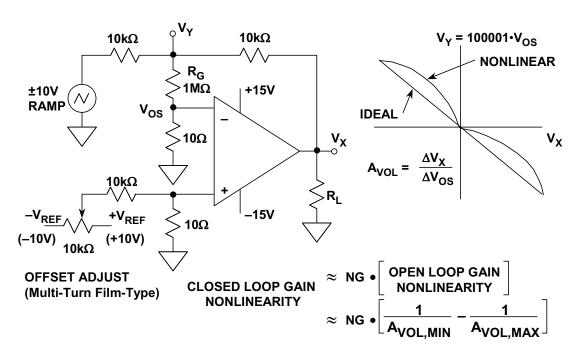

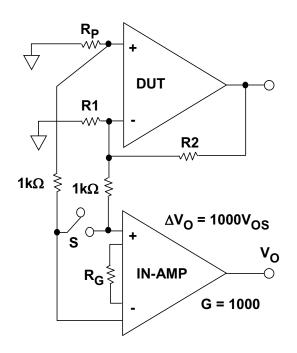

仪表放大器的总输入失调电压由两部分组成(见下图1)。输入失调电压V<sub>osi</sub>是由增益G反映到仪表放大器输出端的输入失调组分。输出失调电压V<sub>oso</sub>则是独立于增益的。

图1: 仪表放大器失调电压模型

在低增益情况下,输出失调电压占据主导地位,在高增益下,输入失调电压较为显著。输出失调电压漂移通常在G = 1时测得(此时,输入效应并不显著),输入失调电压漂移则是在高增益下测得的漂移规格(此时,输出失调效应可忽略不计)。

折合到输入端(RTI)的总输出失调误差等于 $V_{oso}$ / $F_{oso}$ / $F_$

Page 2 of 5 27

输入偏置电流也可能在仪表放大器电路中产生失调误差(同样参见图1)。如果源电阻 $R_s$ 的不平衡量为 $\Delta R_s$ (桥接电路通常如此),则偏置电流会导致额外的输入失调电压误差,等于 $I_B\Delta R_s$ (设 $I_B+\approx I_B-=I_B$ )。该误差被反映到输出端,分频系数为增益G。

输入失调电流 $I_{os}$ 会在源电阻 $R_s$ + $\Delta R_s$ 上产生输入失调电压误差,等于 $I_{os}(R_s$ + $\Delta R_s)$ ,同样由增益G反映到输出端。

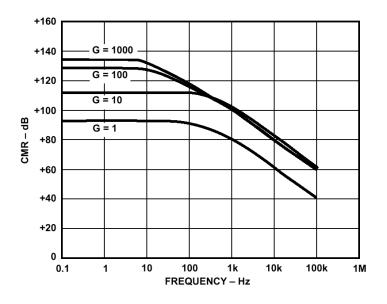

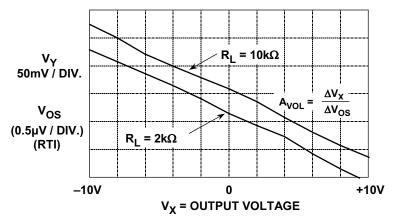

#### 共模抑制与电源抑制误差

仪表放大器共模误差同时为增益和频率的函数。ADI针对仪表放大器规定的共模抑制是在  $1 \, k\Omega$ 源阻抗不平衡、 $60 \, Hz$ 频率条件下测得的。RTI共模误差通过将共模电压 $V_{CM}$ 除以共模抑制比CMRR而得到。

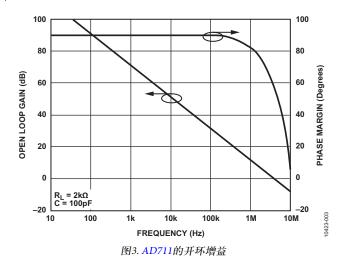

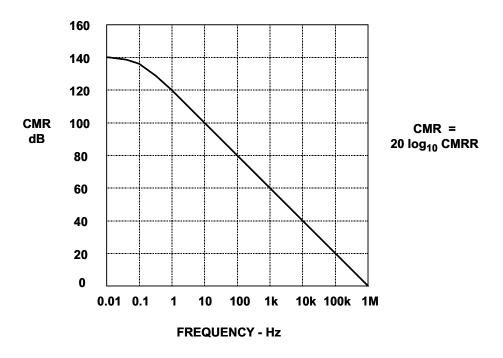

下面的图2展示的是AD620仪表放大器的共模抑制,为频率的函数,其源阻抗不平衡为 $1 \text{ k}\Omega$ 。

图2: AD620仪表放大器共模抑制(CMR)与 频率的关系(源不平衡为1 kΩ)

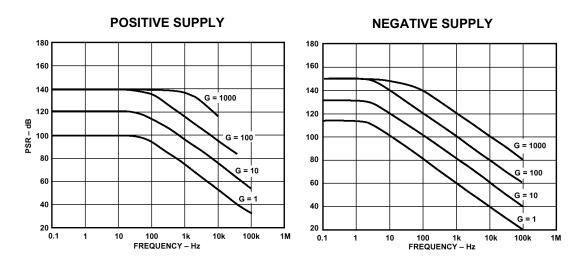

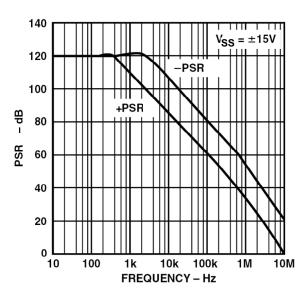

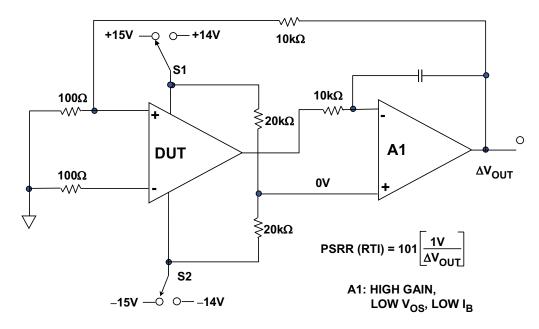

电源抑制(PSR)同样为增益和频率的函数。对于仪表放大器来说,一般是分别规定各个电源的灵敏度,如针对AD620的下图3所示。RTI电源抑制误差通过将电源的标称偏差除以电源抑制比PSRR获得。

28 Page 3 of 5

图3: AD620仪表放大器电源抑制(PSR)与频率的关系

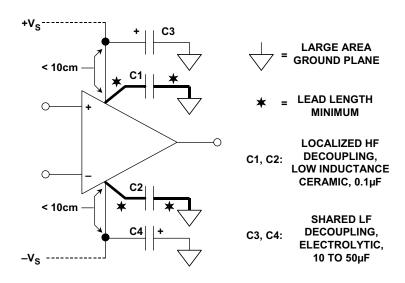

由于高频下的PSR性能较差,因此,仪表放大器的两个电源引脚都需要去耦电容。低电感陶瓷电容(0.01至0.1 μF)对于高频非常适用。低ESR电解电容也应位于PC板上的几个点,以实现低频去耦。

#### 仪表放大器直流误差总预算

以上处理了所有直流误差源,现在,我们可以将所有源反映到仪表放大器输入端,从而算 出最差情况下的直流误差预算,如下面图4中的表所示。

| RTI VALUE                      |

|--------------------------------|

| Gain Accuracy × FS Input       |

| Gain Nonlinearity × FS Input   |

| V <sub>OSI</sub>               |

| V <sub>OSO</sub> ÷ G           |

| I <sub>B</sub> ∆R <sub>S</sub> |

| $I_{OS}(R_S + \Delta R_S)$     |

| V <sub>CM</sub> ÷ CMRR         |

| ∆V <sub>S</sub> ÷ PSRR         |

|                                |

图4: 折合到输入端(RTI)的仪表放大器直流误差

需要注意,只需将RTI误差乘以仪表放大器增益,即可将直流误差折合到仪表放大器输出端(RTO)。

Page 4 of 5 29

# 参考文献

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN:0-915550-28-1. 另见*Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10:0750687037, ISBN-13:978-0750687034。Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, 另见*Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5.Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> Edition, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

30 Page 5 of 5

# 仪表放大器输入RFI保护

#### 保护仪表放大器不受RFI影响

在实际应用中,必须处理日益增多的射频干扰(RFI),对于信号传输线路较长且信号强度 较低的情况尤其如此,这是仪表放大器的典型应用,因为其本身具有共模抑制能力,所以 该器件能从较强共模噪声和干扰中提取较弱的差分信号。但有个潜在问题却往往被忽视, 即仪表放大器中存在的射频整流问题。当存在强射频干扰时,集成电路的内部结点可能对 干扰进行整流,然后以直流输出失调误差表现出来。

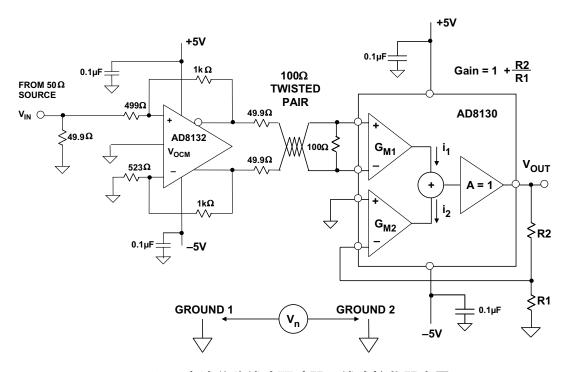

仪表放大器输入端的共模信号通常被其共模抑制的性能衰减了。但遗憾的是,射频整流仍然会发生,因为即使最好的仪表放大器在信号频率高于20 kHz时,实际上也不能抑制共模噪声。放大器的输入级可能对强射频信号进行整流,然后以直流失调误差表现出来。一旦经过整流后,在仪表放大器输出端的低通滤波器将无法消除这种误差。如果射频干扰为间歇性,那么它会导致测量误差,但无法被觉察到。

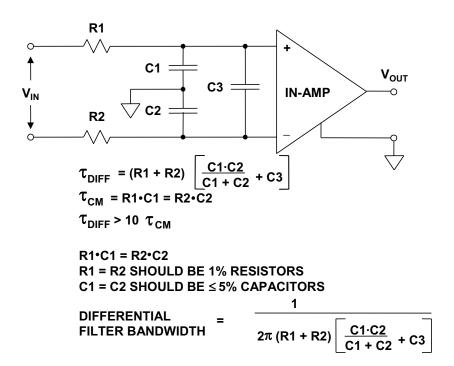

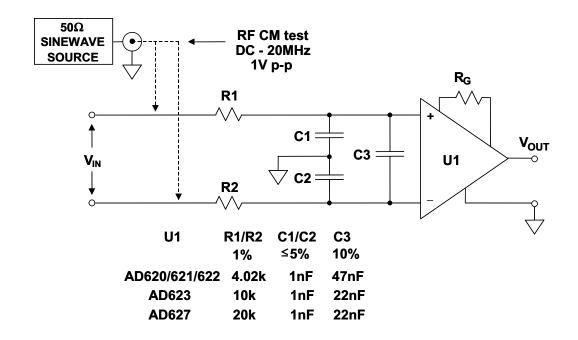

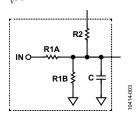

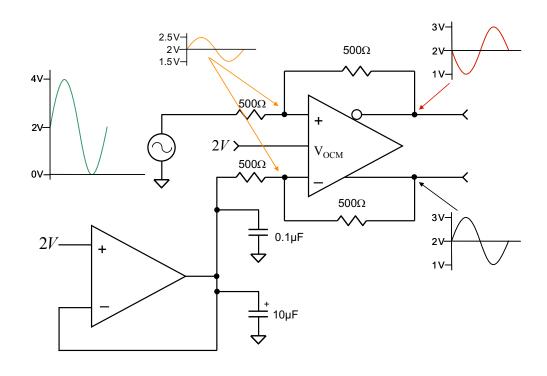

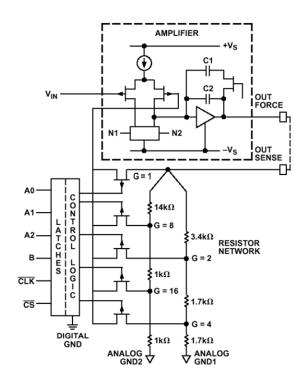

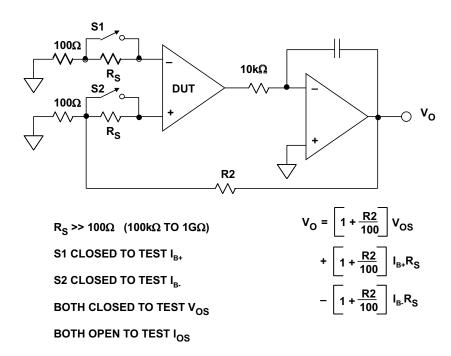

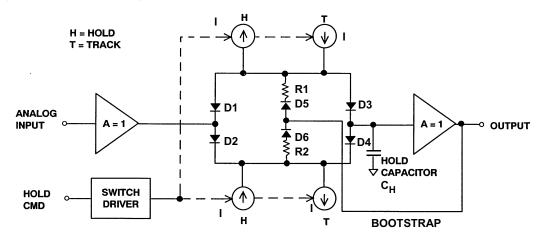

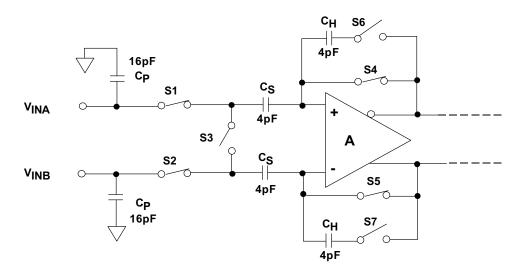

#### 共模(CM)和差模(DM) RC输入滤波器

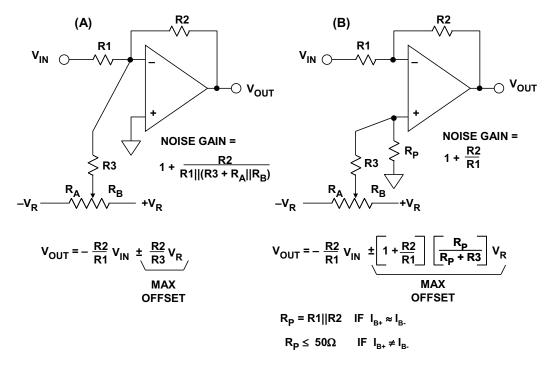

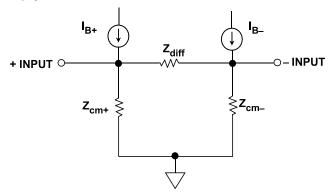

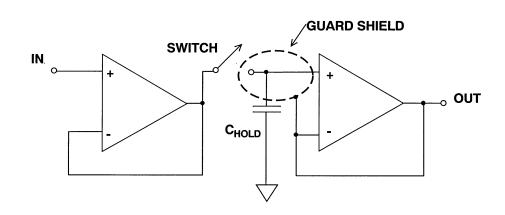

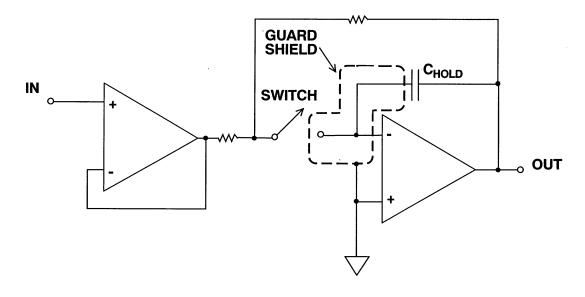

对于仪表放大器的器件级应用需进行适当的滤波,通用方法如图1所示。在此电路中,仪 表放大器可以是数种器件之一。仪表放大器前相对复杂的平衡RC滤波器负责执行所有高 频滤波。仪表放大器则通过其增益设置电阻(图中未显示)设置为应用所需的增益。

注意,该滤波器针对CM(R1-C1和R2-C2)以及差模(DM)信号(R1+R2和C3与串联的C1-C2并联)提供完全平衡的滤波。如果R1-R2和C1-C2匹配不佳, $V_{\rm IN}$ 处的某些输入共模信号将转换为仪表放大器输入端的差模信号。因此,C1和C2的匹配精度至少应达到5%。此外,R1和R2应该采用1%金属薄膜电阻,以便帮助实现这一匹配精度。

此处假设 $V_{IN}$ 引脚处的源阻抗小于R1-R2,并且相互匹配。在此类滤波器中,所选的C3应该至少比C1或C2 (C3  $\geq$  10C1, 10C2)大10倍,以抑制因R1-C1和R2-C2时间常数不匹配所引起的CM-DM转换而导致的杂散差分信号。

图1: 代码跃迁噪声(折合到输入端噪声)及其对ADC传递函数的影响

假设C3>>C1,由此得到CM滤波器带宽为1/2πR1·C1,而DM滤波器带宽则大约为1/4πR1·C3。

总体DM滤波器带宽应至少为输入信号带宽的100倍。滤波器元件应对称安装在具有较大面积接地层的电路板上,并且应该靠近仪表放大器的输入端,以便获得最佳性能。

图2显示了一系列适合各种不同仪表放大器的此类滤波器。RC元件应根据不同仪表放大器进行定制,具体如表中所示。选择这些滤波器元件是为了实现低EMI/RFI灵敏度和低噪声增长的合理平衡(与无滤波器的相应仪表放大器相比)。

要测试配置的EMI/RFI灵敏度,可以向输入电阻施加1 V p-p CM信号,如上所述。当 AD620等常用仪表放大器在增益为1000下工作时,20 MHz范围内观测到的最大RTI输入失调电压漂移为1.5 μV。在AD620滤波器示例中,差分带宽约为400 Hz。

32 Page 2 of 6

图2: 灵活的共模和差模RC EMI/RFI滤波器对 AD620系列、AD623、AD627及其它仪表放大器有效

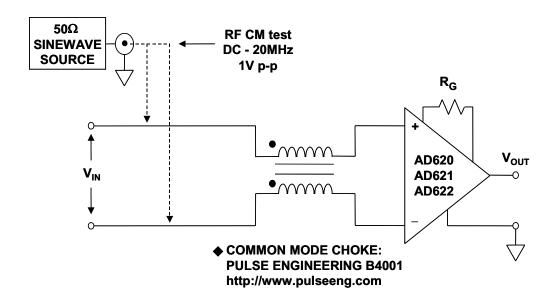

图3: 针对简单和最低噪声EMI/RFI滤波器操作, 共模扼流圈对AD620系列仪表放大器有效

Page 3 of 6 33

除了元件数较少之外,去除电阻后,基于扼流圈的滤波器还具有低噪声特性。不过,关键是要选择合适的共模扼流圈。上文图3所示电路中使用的扼流圈是Pulse Engineering B4001。 G = 1000时,DC至20 MHz范围内测得的最大RTI失调漂移为4.5 μV。针对该滤波器,用户既可以采用B4001等现成扼流圈,也可以自行构建扼流圈。线圈的平衡非常重要,因此建议使用双线。当然,磁芯材料必须能在预期频带内工作。注意,与图1中的RC系列滤波器不同,单纯的扼流圈滤波器不提供差分滤波。可以选择添加差模滤波功能,即在扼流圈之后的第二级添加图1中的R1-C3-R2连接。

#### 采用X2Y®电容的共模滤波器

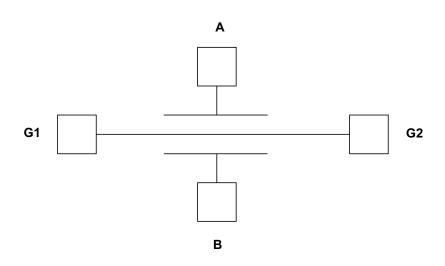

图4显示X2Y电容的连接图。这类器件尺寸非常小,配有三个引脚并具有四个外部连接——A、B、G1和G2。

See www.x2y.com for manufactures of x2y capacitors

图4: X2Y®电容静电模型

G1和G2引脚在器件内部相连。X2Y电容的内部板结构形成一种集成电路,具有一些有趣的特性。从静电角度来看,三个电节点构成两个电容,这两个电容共享G1和G2引脚。制造工艺会自动严格匹配这两个电容。此外,X2Y结构包含有效的自动变压器/共模扼流圈。因此,当共模滤波器使用这类器件时,与类似RC滤波器相比,高于滤波器转折频率的共模信号衰减幅度更大。因此,通常无需电容C3,进而节省了成本和电路板空间。

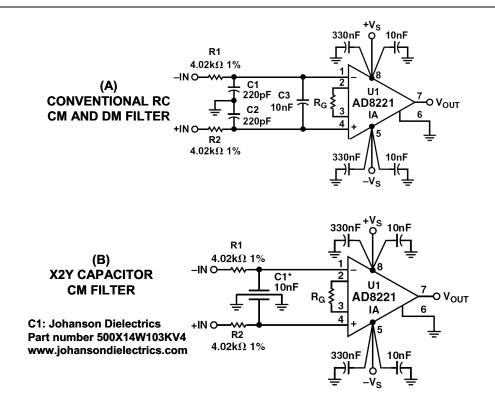

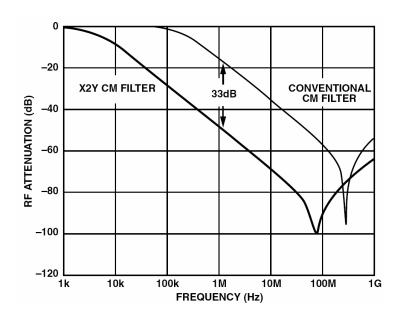

图5A所示为传统的RC共模滤波器,而图5B所示为采用X2Y器件的共模滤波器电路。图6比较了这两种滤波器的RF衰减性能。

34 Page 4 of 6

图5: 传统RC滤波器和X2Y CM滤波器

图6: X2Y共模滤波器与传统RC共模滤波器的RF衰减性能比较

Page 5 of 6 35

### 参考文献

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

36 Page 6 of 6

## 仪表放大器输入过压保护

### 保护仪表放大器不受过压影响

当仪表放大器的输入来自远程传感器时,则可能会受到过压影响。如果在电源开启时将连接线断开并重新连接,可能会产生较大的瞬态电压。感性耦合是导致电缆上产生无用电压的另一种因素,结果可能损害仪表放大器的输入级。

从保护角度来看,仪表放大器在许多方面与运算放大器相似。像运算放大器一样,共模 (CM)和差模(DM)输入电压必须遵循其绝对最大额定值。本指南重点讨论与仪表放大器相关的问题,而指南MT-036更适用于运算放大器。

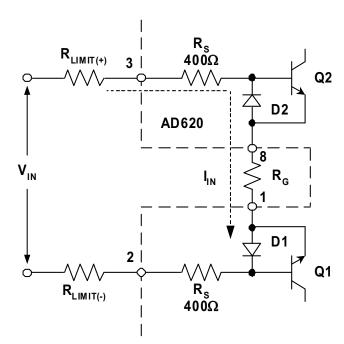

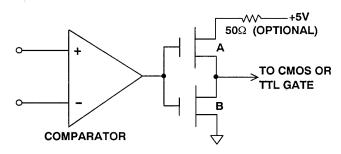

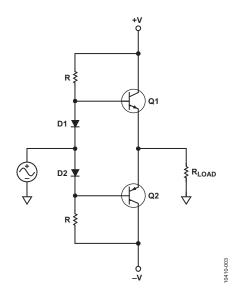

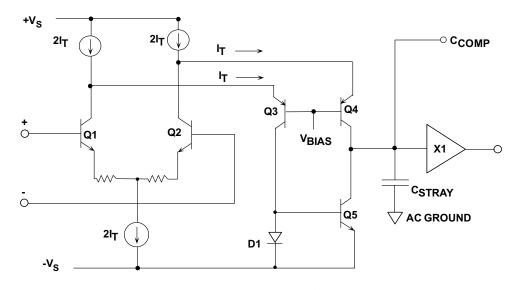

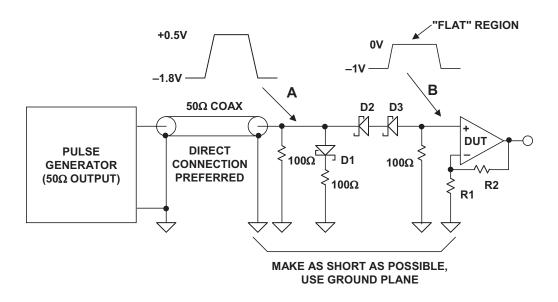

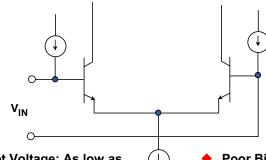

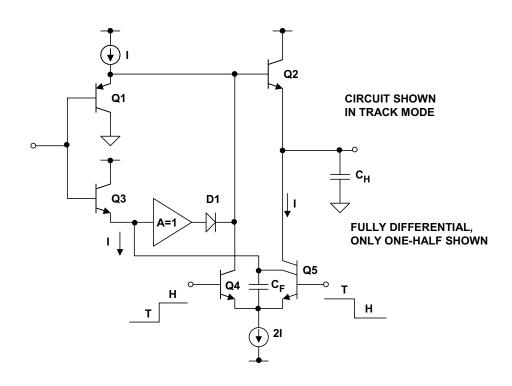

一些仪表放大器内置有串联电阻形式的过载保护电路。图1所示为AD620仪表放大器输入端的原理示意图,图中显示了输入差分晶体管及其相关保护器件。

图1: <u>AD620</u>仪表放大器内部采用D1-D2和串联电阻R<sub>s</sub>来提供保护 (可通过外部方式增加额外保护功能)

由于400 Ω内部R<sub>s</sub>保护电阻为薄膜型电阻,因此它们不会表现出类似于二极管的IC基板导通现象(如果是扩散电阻则会如此)。这意味着,这些电阻的输入端(引脚3和2)可能高于或低于电源电压。差分故障电流将通过内部电阻R<sub>s</sub>的两倍加上外部增益电阻R<sub>g</sub>之和进行限制。施加过量共模电压时,其对应电流会受到R<sub>s</sub>的限制。

输入晶体管Q1和Q2在其基极-发射极结点处有保护二极管D1和D2,以防止出现反向击穿电压。对于差分电压,分析显示,故障电流 $I_{\text{IN}}$ 流过外部 $R_{\text{LIMIT}}$ 电阻(若有)、内部 $R_{\text{S}}$ 电阻、增益设置电阻 $R_{\text{G}}$ 和两个二极管压降(Q2、D1)。对于AD620拓扑结构, $R_{\text{G}}$ 与增益成反比,在1000最大增益下,当 $R_{\text{G}}$ 为49.9  $\Omega$ 时,将出现最差情况(最低电阻)。因而,最低内部路径总串联电阻约为850  $\Omega$ 。

对于AD620,共模和差分输入电压的任意组合都应限制在一定的水平之内,以使输入故障电流限制在20 mA(最大值)之内。对于最低电阻情况,17 V的纯差分电压将产生这一电流水平。对于可能超过任一供电轨的共模电压,则应通过一个内部ESD保护二极管(图1中未显示)来导电,实际上相当于将被驱输入箝位于+ $V_s$ 或- $V_s$ 。对于这种过压共模条件, $R_s$ 的值 (400  $\Omega$ )以及超过供电轨的过量电压决定着电流水平。例如,如果 $V_{\rm IN}$ 为23 V,+ $V_s$ 为15 V,则 $R_s$ 上将出现8 V的电压,结果达到20 mA的额定电流。对于更高的故障电压,可以通过添加外部 $R_{\rm LIMIT}$ 电阻来处理,以使故障电流维持在20 mA或以下。然而,如果 $R_{\rm LIMIT}$ 电阻产生的约翰逊噪声(对于1000  $\Omega$ 电阻,25°C时该噪声为4 nV/ $\sqrt{}$ Hz)过大,则可能限制系统的性能。

最大容许输入故障电流由仪表放大器数据手册规定,可能因器件而异。另外,数据手册一般会讨论输入电路和推荐的保护方法。

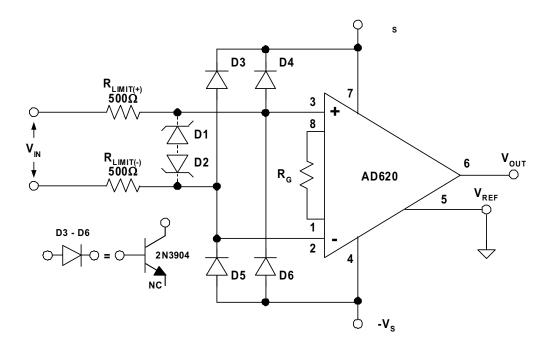

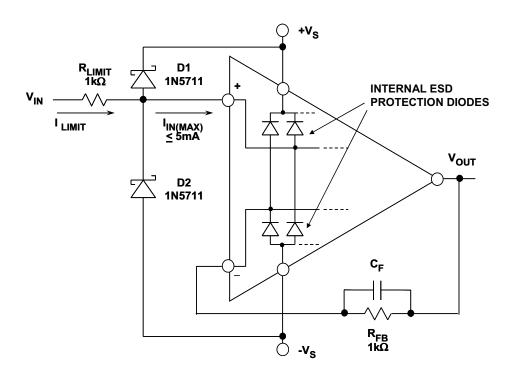

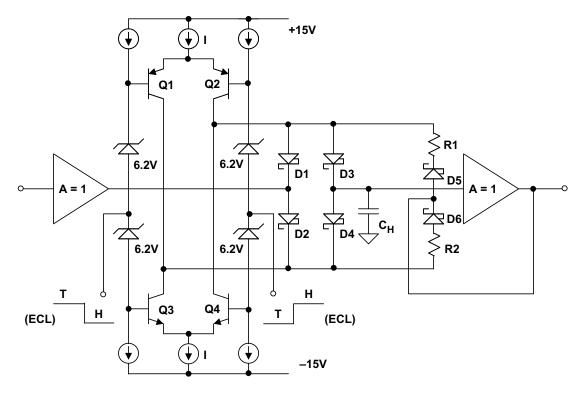

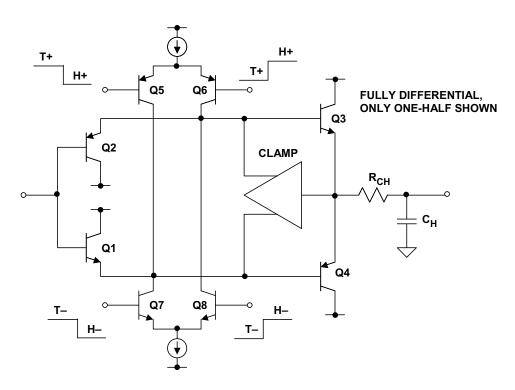

如果需要额外保护(不仅仅是像上文所述那样添加R<sub>LIMIT</sub>电阻),图2给出了AD620一类仪表放大器的通用外部电压保护电路。

图2: <u>AD620</u>以及其它仪表放大器的通用二极管保护电路 采用D3-D6来实现共模箝位,并采用串联电阻R<sub>IMIT</sub>来提供保护

在该电路中,低泄漏二极管D3-D6用作共模箝位。由于仪表放大器偏置电流可能只有1 nA 左右(对于AD620),因此必须使用低泄漏二极管,尤其是高源阻抗的情况。一种很好的方法是检查二极管的规格,以确保二极管在仪表放大器内部ESD保护二极管开始吸电流之前就导通。尽管标准肖特基二极管具有出色的输入保护能力,但其漏电流可能高达数mA。然而,快速肖特基二极管(如International Rectifier的SD101系列)的最大漏电流为200 nA,典型功耗为400 mW。

需要注意的是,二极管不仅基本上必须具有低泄露,而且还必须在最高预期温度下保持低泄漏。这表明需要使用FET型二极管或所示的晶体管集电极-基极型二极管。选择R<sub>LIMIT</sub>电阻是为了限制故障条件下的最大二极管电流。如果使用额外的差分保护,则可使用背对背齐纳或Transzorb箝位,以D1-D2表示。如果这样做,则应仔细考虑这些二极管的泄漏情况。

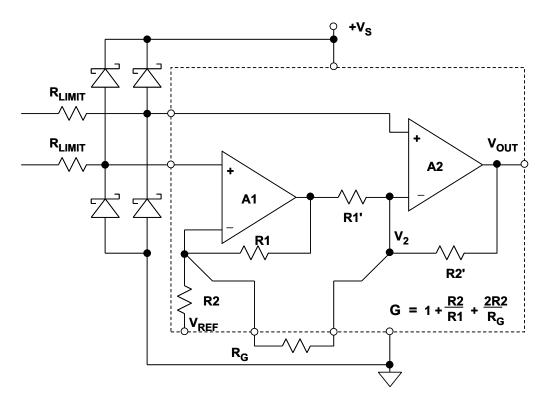

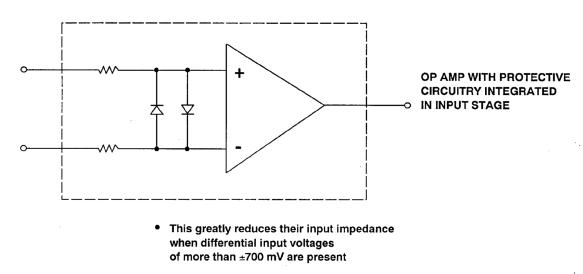

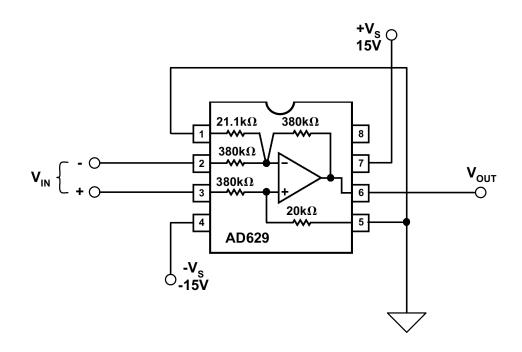

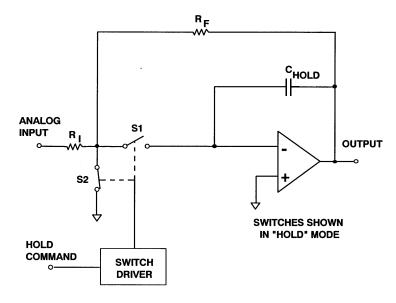

许多单电源仪表放大器的拓扑结构与图3虚线框中的双放大器仪表放大器电路类似。

图3: 单电源仪表放大器可能要求、也可能不要求具有电阻和 箝位二极管形式的外部保护

就外部保护元件的必要性而言,给定仪表放大器可能需要、也可能不需要使用它们。每种情况都需要单独考虑。例如,一些仪表放大器采用了图中所示的箝位二极管,不过是内置的而已。AD623就是这样一种器件,但它缺少串联电阻,必要时可以在外部添加。请注意,这种方法允许优化R<sub>LIMIT</sub>值以提供保护,对于不需要保护的应用,其对噪声的影响可以忽略不计。

Page 3 of 5 39

另外,一些仪表放大器同时具有内部保护电阻和箝位二极管,AD627即是这样一个例子。 在该器件中,内部保护足以耐受最高超过电源40 V的瞬态电压(内部电阻中存在20 mA故障 电流)。对于高于该值的过压水平,可以增加外部R<sub>LMIT</sub>电阻。

按图中所示在两个输入端放置肖特基二极管就是一种仪表放大器保护选项,不过前提是源阻抗很小,以致二极管漏电流产生的误差处于可接受水平。如果内部未专门提供箝位,则可使用肖特基二极管。请注意,在许多情况下,由于现代仪表放大器内置保护网络,因而不需要这些二极管。但同样,对此并无硬性规定,因而始终都应该查阅数据手册,然后再敲定应用设计。

总而言之,图4总结了本节讨论的仪表放大器的主要在线过压问题。

- INPUT VOLTAGES MUST NOT EXCEED ABSOLUTE MAXIMUM RATINGS (Usually Specified With Respect to Supply Voltages)

- Requires V<sub>IN(CM)</sub> Stay Within a Range Extending to ≤0.3V Beyond Rails (-V<sub>S</sub> - 0.3V ≥ V<sub>IN</sub> ≤ +V<sub>S</sub> + 0.3V)

- ◆ IC Input Stage Fault Currents Must Be Limited

(≤ 5mA Unless Otherwise Specified)

- Avoid Reverse-Bias Breakdown in Input Stage Junctions!

- Differential and Common Mode Ratings Often Differ

- Some ICs Contain Internal Input Protection

- Diode Voltage Clamps, Current Limiting Resistors (or both)

- Absolute Maximum Ratings Must Still Be Observed

- ♦ No Two Amplifiers are Exactly the Same

- Always consult the in-amp data sheet for overvoltage protection recommendations

#### 图4:仪表放大器过压问题小结

这些针对运算放大器和仪表放大器的过压防范措施看起来非常复杂吧,确实很复杂!只要运算放大器(或仪表放大器)输入(和输出)超出设备边界条件,就可能发生危险情况或器件损毁。显然,为了实现最高可靠性,必须防患于未然。

40 Page 4 of 5

幸运的是,许多应用都是完全内置于设备中,通常看到的是采用同一电源系统的其它IC的输入和输出。因此,这种情况下一般不需要箝位和保护方案。

### 参考文献:

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as *Linear Circuit Design Handbook*, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 5 of 5 41

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## 全波整流器

作者: ADI公司 Hank Zumbahlen

#### 引言

全波整流器通常用于从交流输入获得直流电平。该整流器是一系列小型指南描述的、内置运算放大器的多种分立式电路之一。

全波整流器通常用于从交流输入获得直流电平。这通常用于测量交流信号的幅度。全波整流器是一种均值检波器。 需要与均方根检波器或峰值检波器区分开来。

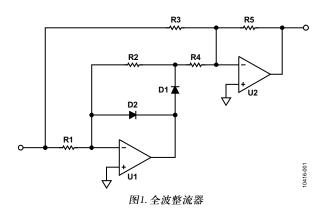

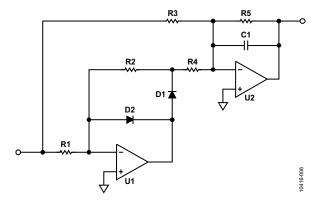

全波整流器是半波整流器(见MT-212)的增强型电路。图2 所示全波整流器为半波整流器与输入的求和电路。

图2. 作为半波整流器增强型器件的全波整流器

为了理解全波整流器的工作原理,我们不妨假定运算放大器和二极管在理论上无正向电压。对于负输入电压,U1的输出会尽量变为正,结果将接通D1而断开D2。假设D1短路(这种情况下为接通),结果将使输出保持于地电位,因为运算放大器(U1)的行为迫使运算放大器的输入电压保持相同电平。

对于正输入电压,输出将变为负,D2接通,D1断开。此时,U1的输出端充当一个反相放大器(见MT-213),其增益由R2/R1设定。通常,该增益设为1,即R2=R1。

结果,U1的输出在输入(反相)负半周期之后,正半周期的输出为0 V。然后,该输出成为第二级(U2)的输入之一,与输入波形求和(见MT-214)。

第一级(为半波整流器(见MT-212))的增益相对于输入为2。 这意味着,R3 = 2R4。因此,对于负半周期,输入波与参 考电位(地电位)求和。U2输出端的结果为负半周期的正增 益。对于正半周期,半波整流器的反相波与输入求和,其 中半波整流器的增益为2。因此,U2的输出端得到正半 波。所得到的就是全波整流器。

半波整流器部分的增益通常设为1 (R1 = R2)。R3和R4的比率匹配应非常接近(电阻值的绝对值相对而言不太重要),使半波整流器输出与输入正确求和。通过更改R5的值,可以非常方便地调整电路的增益。

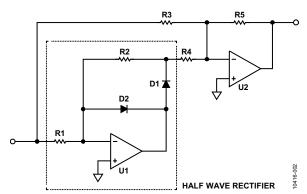

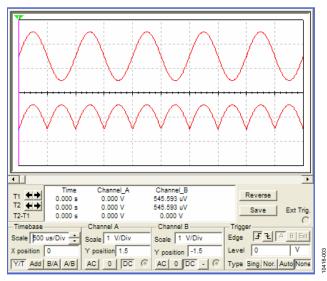

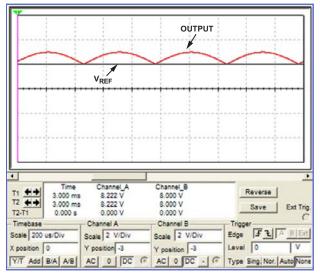

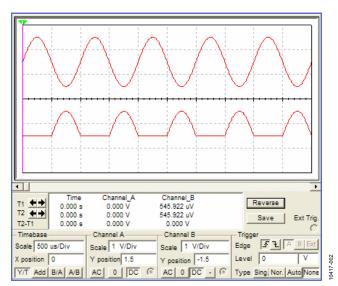

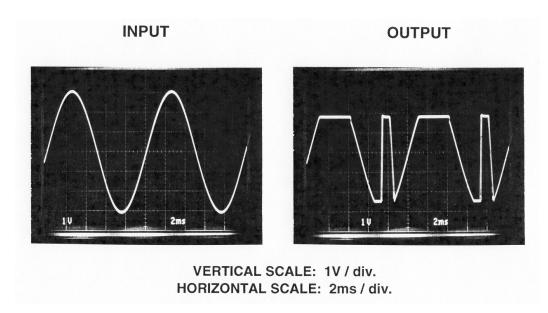

图3所示为全波整流器的波形。顶部曲线为输入,底部曲线则为U2处的电路输出。

图3. 全波整流器波形

图4显示的是U1的输出和半波整流器的输出。请注意,在实际电路中,U1的输出实际采用开环模式,直到达到D2的正向电压为止。图中所示为从顶部往下的第三条曲线(通道C)。半波整流器的输出在图中表示为底部曲线(通道D)。图4中所有曲线的增益都是相同的。

图4. 全波整流器波形与半波整流器输出

全波整流器的输出端之后往往是一个滤波器,用于形成直流电平。该滤波器的转折频率应置于足够低的水平,以限制输出上的交流纹波,同时还必须足够高,以免对电路的瞬态响应速率造成严重影响。

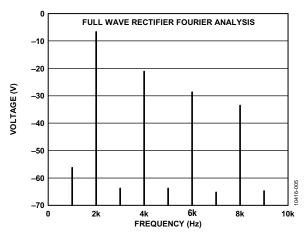

输出频谱如图5所示。全波整流器相对于半波整流器的一个优势是,其输出的频谱以系数2倍乘,这是因为整流器行为导致输出谱瓣增加了一倍。

图5. 全波整流器输出频谱

通过在反馈网络中添加一个电容,可以将全波整流器的加法器部分转换成一个简单的滤波器。该滤波器的转折频率由电容和R5的值设定( $F_0 = 1/(2\pi R5C1)$ ),如图6所示。另外,该电路之后可以放置一个有源滤波器。

图6. 在反馈环路中添加一个电容可将 全波整流器的输出转变成直流电平

通过同时反转两个二极管,可以将输出的极性转换为负。

全波整流器的误差项与反相放大器相同(见MT-213)。最重要的是失调项。该电路的频率响应主要由运算放大器的开环增益设定。二极管的等效并联电容和二极管导通/关断时间也会影响频率响应,但其影响一般比运算放大器的频率响应要小得多。

采用单电源电压供电时,同相输入偏置到基准电压,通常为电源电压的½。此时,零输入信号输出为基准电压。图7 所示单电源半波整流器的基准电压(运算放大器同相输入端的电压)为+4 V。在示意图中,地位于底部。

输入仍然以地为参考,因此,输入端必须用串联电容进行交流耦合。频率的低端取决于输入耦合电容和输入电阻R1的RC时间常数。对于双极性电源,电路响应可以达到直流。另外,如果上述电路以相同的基准电压为参考,则输入可能为直流耦合。如果采用电路增益,则需要格外小心,因为基准电平和信号都放大了。

运算放大器上的频率响应要求取决于最大信号输入频率。 必须有足够的开环增益,二极管才可偏置。另外,求和操 作会引起频率倍增。因此,根据经验,运算放大器的带宽 至少应为20 dB,在输入信号最大频率的两倍处。

图7. 单电源半波整流器波形

修订历史 2012年4月—修订版0:初始版

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## 全通滤波器

作者: ADI公司 Hank Zumbahlen

#### 引言

全通滤波器(包括一阶全通滤波器和二阶全通滤波器) 只需要一个运算放大器。全通滤波器是一系列小型指 南中描述的多种分立式电路之一。

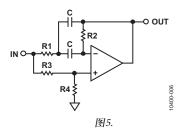

#### 全通滤波器简介

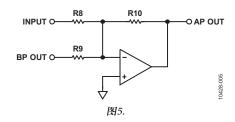

在多数情况下,滤波器的幅度响应是首要考虑因素。不影响信号幅度但会导致相移的另一类滤波器称为全通滤波器。

该滤波器的目的是给电路的响应增加相移(延迟)。全通滤波器的幅度在所有频率下一致。然而,在频率从0扫频至无穷大时,相位响应会从0°变化至360°(双极点滤波器)。全通滤波器的一种用途是提供相位均衡,一般用在脉冲电路中。同时也可用在单边带、抑制载波(SSB-SC)调制电路中。

全通滤波器的传递函数为:

$$H(s) = \frac{s^2 - \left(\frac{\omega_0}{Q}\right)s + {\omega_0}^2}{s^2 + \left(\frac{\omega_0}{Q}\right)s + {\omega_0}^2}$$

(1)

请注意,全通传递函数可以合成为

$$H_{AP} = H_{LP} - H_{BP} + H_{HP} = 1 - 2H_{BP}$$

(2)

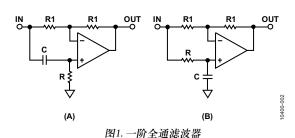

#### 一阶全通

一阶全通滤波器的一般形态如图1所示。如果其功能为简单的RC高通(图1A),则电路的相移范围为 $-180^{\circ}(0~Hz)$ 至0° (高频)。当 $\omega=1/RC$ 时,为 $-90^{\circ}$ 。可将电阻设为可变,以便在具体频率下进行延迟调节。

如果将功能改成低通功能(图1B),则滤波器仍然为一阶全通,延迟等式仍然有效,但信号会反相,变化范围为0°(直流)至-180°(高频)。

#### 二阶全通

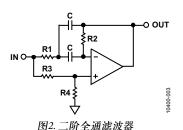

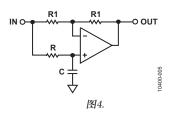

放大器。

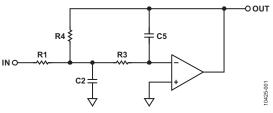

图2所示二阶全通电路首次由Delyiannis描述(见参考文献部分)。这种电路的最大魅力在于只需要一个运算放大器。同时记住,全通滤波器也可实现为1-2BP。

我们可以利用本小型指南系列中讨论的带通实现方式来构建该滤波器,但一定要知道,BP是否会使相位反转。另外需要记住BP部分的增益必须为2。为此,双放大器带通滤波器(DABP)结构十分有用,因为其增益固定为2。在选择运算放大器时,我们主要考虑带宽问题。根据经验,放大器在谐振频率下的开环增益不得低于20 dB。同时,由于反馈网络中有一个电容,所以,可能不大适合使用电流反馈

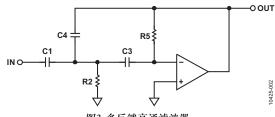

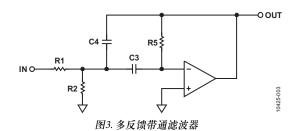

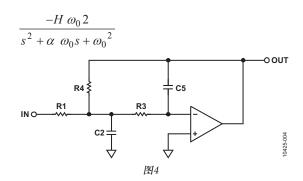

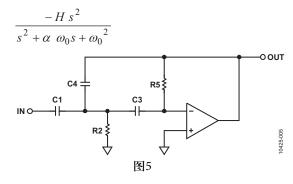

图3和图4总结了多种有源滤波器实现方式的设计方程式。 在所有情况下,H、 $\omega_{o}$ 、Q和 $\alpha$ 都是已知的,取自设计表。

### 一阶全通设计方程式

$$\frac{V_O}{V_{IN}} = \frac{s - \frac{1}{RC}}{s + \frac{1}{RC}}$$

$$IN \circ \qquad R1 \qquad R1 \qquad O \circ OUT$$

$$Phase Shift \left(\phi\right) = -2 \ Tan^{-1} \left(\frac{RC}{2\pi F}\right)$$

$$Group\ Delay = \frac{2\ RC}{\left(2\ \pi\ FRC\right)^2 + 1}$$

直流下延迟 = 2 RC 若频率 = F时,相移为φ

$$RC = 2\pi F TAN\left(-\frac{\phi}{2}\right)$$

图4中的设计与图3相同,只是相位的符号变了。

#### 二阶全通设计方程式

$$\frac{s^2 - s\left(\frac{\omega_0}{Q}\right) + {\omega_0}^2}{s^2 + s\left(\frac{\omega_0}{Q}\right) + {\omega_0}^2}$$

$$\frac{V_O}{V_{IN}} = \frac{s^2 - s\left(\frac{2}{R2C}\right) + \frac{1}{R1 \ R2 \ C^2}}{s^2 + s\left(\frac{2}{R2C}\right) + \frac{1}{R1 \ R2 \ C^2}}$$

要设计该滤波器,请选择C。

$$k=2\pi F_{o}C$$

$$R2 = \frac{2Q}{k}$$

$$R1 = \frac{1}{2 k Q}$$

$$R3 = R1$$

$$R4 = \frac{Q}{2}$$

### 参考文献

Delyiannis, T. High-Q Factor Circuit with Reduced Sensitivity, Electronic Letters, Volume 4, December 1968. p. 577.

Zumbahlen, Hank. Linear Circuit Design Handbook. Elsevier. 2008. ISBN: 978-7506-8703-4.

#### 修订历史

2012年4月—修订版0: 初始版

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# 切比雪夫响应

作者: ADI公司 Hank Zumbahlen

## 引言

切比雪夫滤波器是一款内置精密运算放大器的电路, 也是一系列小型指南中描述的分立式电路之一。

### 目录

| 切比雪夫响应简介     |           | 2 |

|--------------|-----------|---|

| 频率响应、群延迟、    | 脉冲响应和阶跃响应 | 3 |

| 0.01 dB切比雪夫啊 | <b>向应</b> | 3 |

| 0.1 dB切比雪夫响  | 应         | 4 |

| 0.25 dB切比雪夫啊 | 拘应        | 5 |

| 0.5 dB切比雪夫响  | <u> </u>  | 6 |

| 1 dB切比雪夫响应   | į         | 7 |

| 极点位置表         | 8  |

|---------------|----|

| 0.01 dB切比雪夫设计 | 8  |

| 0.1 dB切比雪夫设计  | 9  |

| 0.25 dB切比雪夫设计 | 10 |

| 0.5 dB切比雪夫设计  | 11 |

| 1 dB切比雪丰设计    | 12 |

#### 修订历史

2012年1月—修订版0: 初始版

## 切比雪夫响应简介

与相同阶数的巴特沃兹滤波器相比,切比雪夫(Chebyshev) 滤波器的过渡带较窄,但通带中存在波纹,而且瞬态响应 略有下降。这种滤波器的得名是因为切比雪夫滤波器最小 化了最大纹波的权重,这就是切比雪夫准则。

切比雪夫滤波器直流相对衰减为0 dB。奇阶滤波器的衰减带从0 dB延伸至波纹值。偶阶滤波器的增益与通带波纹相等。通带中的波纹周期数等于滤波器阶数。

把巴特沃兹滤波器的极点移至右边(向轴靠近),形成一个椭圆形,这样即可确定切比雪夫滤波器的极点。其方法是用k<sub>,</sub>乘以极点的实部,用k<sub>,</sub>乘以极点的虚部。k<sub>,</sub>和k<sub>,</sub>两个值可通过以下方程算出

$$K_{\rm r} = \sinh A$$

(1)

$$K_{\rm I} = \cosh A$$

(2)

其中:

$$A = \frac{1}{n} \sinh^{-1} \frac{1}{\varepsilon} \tag{3}$$

其中, n为滤波器的阶数, 并且

$$\varepsilon = \sqrt{10^R - 1} \tag{4}$$

$$R = \frac{R_{dB}}{10} \tag{5}$$

其中:

$$R_{dR}$$

= 以dB表示的通带纹波 (6)

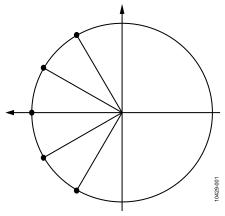

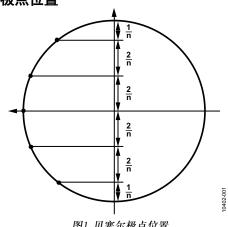

图1展示的是一个5极点1 dB切比雪夫滤波器的极点位置。

图1.1 dB切比雪夫滤波器的极点位置

切比雪夫滤波器一般经过归一化处理,以使波纹带边缘为 $\omega o = 1$ 。

3 dB带宽通过以下方程计算

$$A_{3dB} = \frac{1}{n} \cosh^{-1} \left( \frac{1}{\varepsilon} \right) \tag{7}$$

详见表1。

表1.3 dB带宽与纹波带宽的关系

| 阶数 | 0.01 dB | 0.1 dB  | 0.25 dB | 0.5 dB  | 1 dB    |

|----|---------|---------|---------|---------|---------|

| 2  | 3.30362 | 1.93432 | 1.59814 | 1.38974 | 1.21763 |

| 3  | 1.87718 | 1.38899 | 1.25289 | 1.16749 | 1.09487 |

| 4  | 1.46690 | 1.21310 | 1.13977 | 1.09310 | 1.05300 |

| 5  | 1.29122 | 1.13472 | 1.08872 | 1.05926 | 1.03381 |

| 6  | 1.19941 | 1.09293 | 1.06134 | 1.04103 | 1.02344 |

| 7  | 1.14527 | 1.06800 | 1.04495 | 1.03009 | 1.01721 |

| 8  | 1.11061 | 1.05193 | 1.03435 | 1.02301 | 1.01316 |

| 9  | 1.08706 | 1.04095 | 1.02711 | 1.01817 | 1.01040 |

| 10 | 1.07033 | 1.03313 | 1.02194 | 1.01471 | 1.00842 |

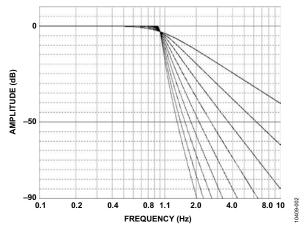

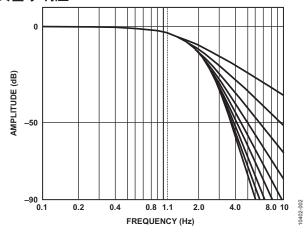

# 频率响应、群延迟、脉冲响应和阶跃响应

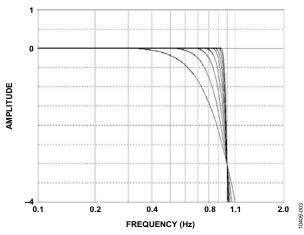

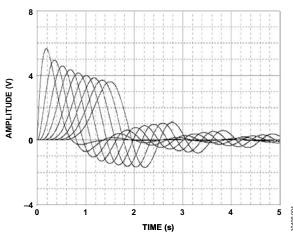

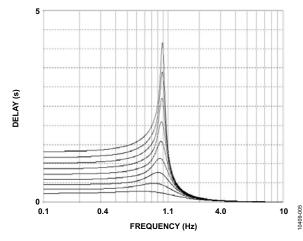

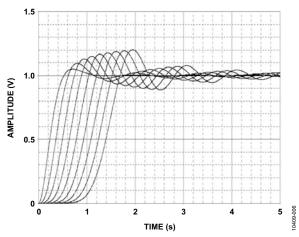

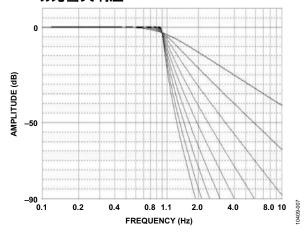

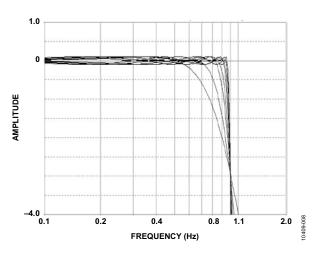

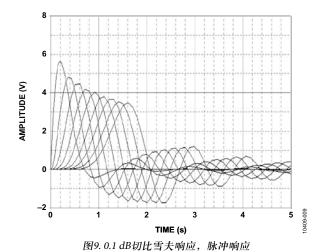

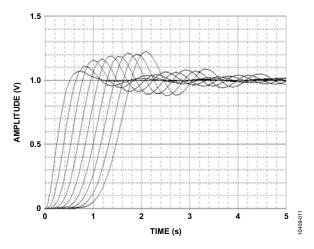

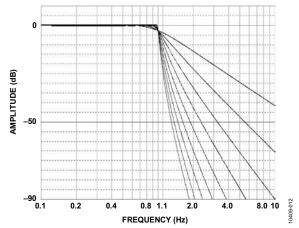

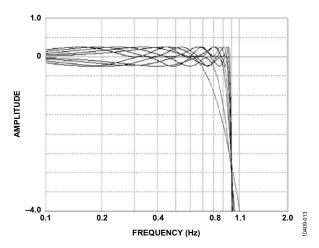

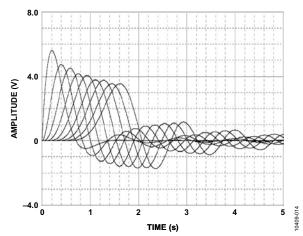

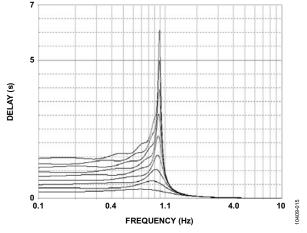

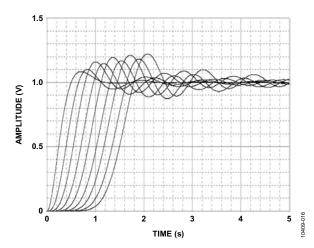

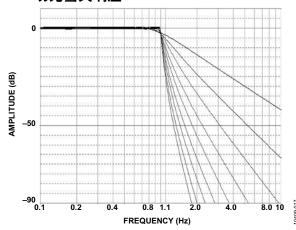

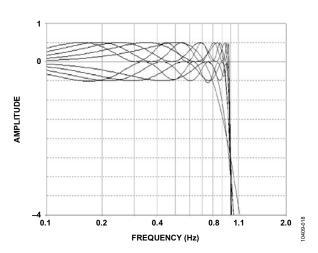

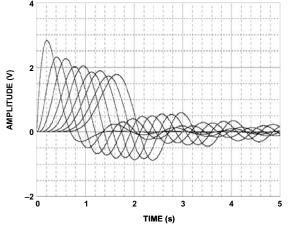

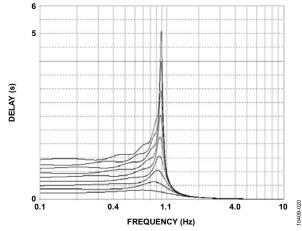

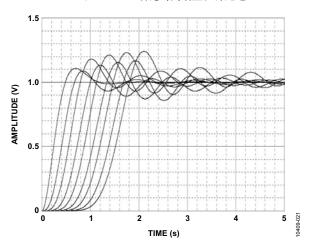

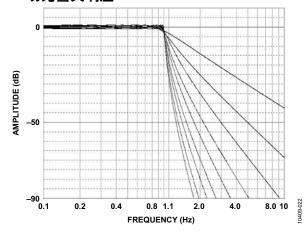

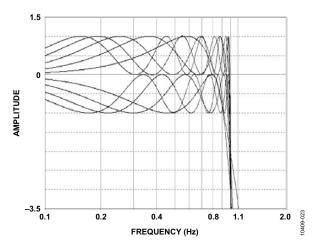

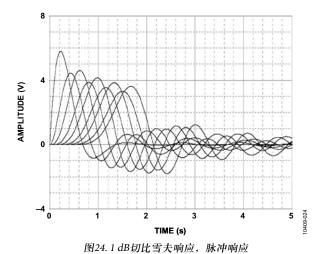

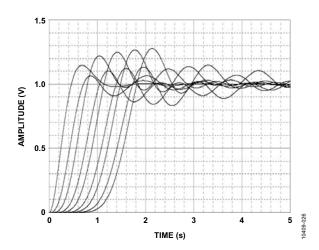

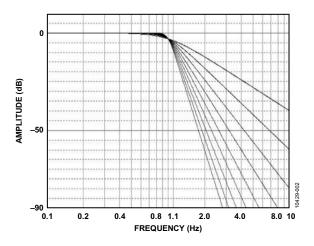

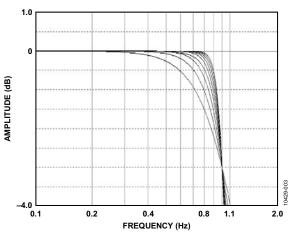

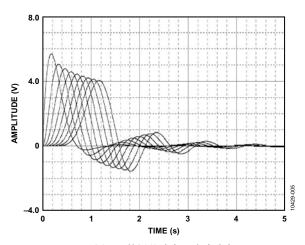

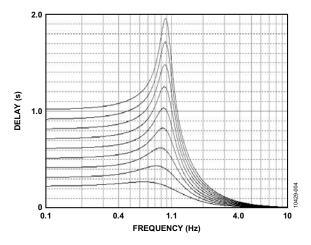

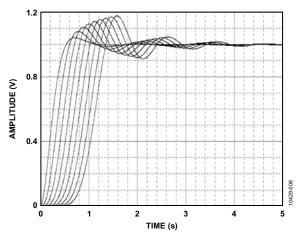

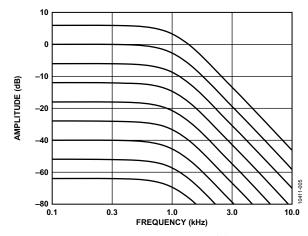

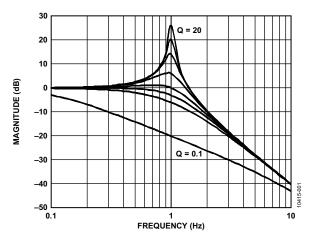

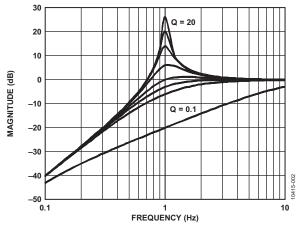

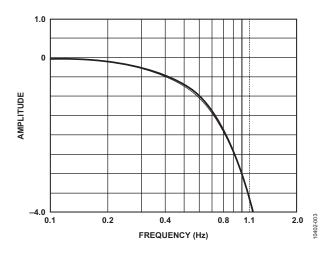

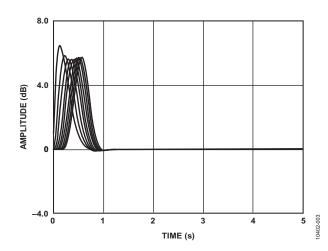

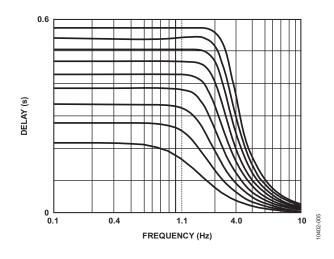

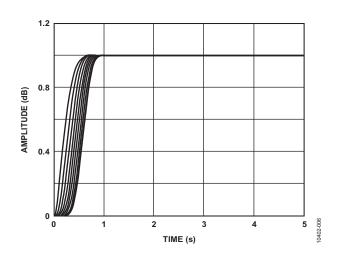

针对各种通带纹波值(0.01~dB、0.1~dB、0.25~dB、0.5~dB和1~dB)的频率响应、群延迟、脉冲响应、阶跃响应和幅度如图2至图26所示。

### 0.01 DB切比雪夫响应

图2.0.01 dB切比雪夫响应,幅度

图3.0.01 dB切比雪夫响应,幅度(详)

图4.0.01 dB切比雪夫响应,脉冲响应

图5.0.01 dB切比雪夫响应, 群响应

图6.0.01 dB切比雪夫响应, 阶跃响应

# MT-206

## 0.1 DB切比雪夫响应

图7.0.1 dB切比雪夫响应,幅度

图8.0.1 dB切比雪夫响应,幅度(详)

00.1 0.4 1.1 4.0 10 FREQUENCY (Hz)

图10.0.1 dB切比雪夫响应, 群延迟

图11.0.1 dB切比雪夫响应, 阶跃响应

## 0.25 DB切比雪夫响应

图12.0.25 dB切比雪夫响应,幅度

图13.0.25 dB切比雪夫响应,幅度(详)

图14.0.25 dB切比雪夫响应,脉冲响应

图15.0.25 dB切比雪夫响应, 群延迟

图16.0.25 dB切比雪夫响应, 阶跃响应

# **MT-206**

## 0.5 DB切比雪夫响应

图17.0.5 dB切比雪夫响应,幅度

图18.0.5 dB切比雪夫响应,幅度(详)

图19.0.5 dB切比雪夫响应,脉冲响应

图20.0.5 dB切比雪夫响应, 群延迟

图21.0.5 dB切比雪夫响应, 阶跃响应

## 1 DB切比雪夫响应

图22.1 dB切比雪夫响应,幅度

图23.1 dB切比雪夫响应,幅度(详)

DELAY (s)

FREQUENCY (Hz)

图25.1 dB切比雪夫响应,群延迟

1.1

图26.1 dB切比雪夫响应,阶跃响应

# **MT-206**

# 极点位置表

针对这些纹波值的极点位置和对应的ω。和α项如表2至表6所示。

## 0.01 DB切比雪夫设计

表2.

| 阶数 | 部分 | 实部     | 虚部     | F <sub>o</sub> | α      | Q      | –3 db<br>频率 | 峰值<br>频率 | 峰值<br>电平 |

|----|----|--------|--------|----------------|--------|--------|-------------|----------|----------|

| 2  | 1  | 0.6743 | 0.7075 | 0.9774         | 1.3798 | 0.7247 |             | 0.2142   | 0.0100   |

| 3  | 1  | 0.4233 | 0.8663 | 0.9642         | 0.8780 | 1.1389 |             | 0.7558   | 2.0595   |

| 3  | 2  | 0.4233 | 0.8003 | 0.9042         | 0.0760 | 1.1309 | 0.8467      | 0.7338   | 2.0393   |

|    |    | 0.0407 |        | 0.0407         |        |        | 0.0407      |          |          |

| 4  | 1  | 0.6762 | 0.3828 | 0.7770         | 1.7405 | 0.5746 | 0.6069      |          |          |

|    | 2  | 0.2801 | 0.9241 | 0.9656         | 0.5801 | 1.7237 |             | 0.8806   | 5.1110   |

| 5  | 1  | 0.5120 | 0.5879 | 0.7796         | 1.3135 | 0.7613 |             | 0.2889   | 0.0827   |

|    | 2  | 0.1956 | 0.9512 | 0.9711         | 0.4028 | 2.4824 |             | 0.9309   | 8.0772   |

|    | 3  | 0.6328 |        | 0.6328         |        |        | 0.6328      |          |          |

| 6  | 1  | 0.5335 | 0.2588 | 0.5930         | 1.7995 | 0.5557 | 0.4425      |          |          |

|    | 2  | 0.3906 | 0.7072 | 0.8079         | 0.9670 | 1.0342 |             | 0.5895   | 1.4482   |

|    | 3  | 0.1430 | 0.9660 | 0.9765         | 0.2929 | 3.4144 |             | 0.9554   | 10.7605  |

| 7  | 1  | 0.4393 | 0.4339 | 0.6175         | 1.4229 | 0.7028 | 0.6136      |          |          |

|    | 2  | 0.3040 | 0.7819 | 0.8389         | 0.7247 | 1.3798 |             | 0.7204   | 3.4077   |

|    | 3  | 0.1085 | 0.9750 | 0.9810         | 0.2212 | 4.5208 |             | 0.9689   | 13.1578  |

|    | 4  | 0.4876 |        | 0.4876         |        |        | 0.4876      |          |          |

| 8  | 1  | 0.4268 | 0.1951 | 0.4693         | 1.8190 | 0.5498 | 0.3451      |          |          |

|    | 2  | 0.3168 | 0.5556 | 0.6396         | 0.9907 | 1.0094 |             | 0.4564   | 1.3041   |

|    | 3  | 0.2418 | 0.8315 | 0.8659         | 0.5585 | 1.7906 |             | 0.7956   | 5.4126   |

|    | 4  | 0.0849 | 0.9808 | 0.9845         | 0.1725 | 5.7978 |             | 0.9771   | 15.2977  |

| 9  | 1  | 0.3686 | 0.3420 | 0.5028         | 1.4661 | 0.6821 | 0.4844      |          |          |

|    | 2  | 0.3005 | 0.6428 | 0.7096         | 0.8470 | 1.1807 |             | 0.5682   | 2.3008   |

|    | 3  | 0.1961 | 0.8661 | 0.8880         | 0.4417 | 2.2642 |             | 0.8436   | 7.3155   |

|    | 4  | 0.0681 | 0.9848 | 0.9872         | 0.1380 | 7.2478 |             | 0.9824   | 17.2249  |

|    | 5  | 0.3923 |        | 0.3923         |        |        | 0.3923      |          |          |

| 10 | 1  | 0.3522 | 0.1564 | 0.3854         | 1.8279 | 0.5471 | 0.2814      |          |          |

|    | 2  | 0.3178 | 0.454  | 0.5542         | 1.1469 | 0.8719 |             | 0.3242   | 0.5412   |

|    | 3  | 0.2522 | 0.7071 | 0.7507         | 0.6719 | 1.4884 |             | 0.6606   | 3.9742   |

|    | 4  | 0.1619 | 0.891  | 0.9056         | 0.3576 | 2.7968 |             | 0.8762   | 9.0742   |

|    | 5  | 0.0558 | 0.9877 | 0.9893         | 0.1128 | 8.8645 |             | 0.9861   | 18.9669  |

## 0.1 DB切比雪夫设计

### 表3.

| 阶数 | 部分 | 实部     | 虚部     | F <sub>o</sub> | α      | Q       | -3 db<br>频率 | 峰值<br>频率 | 峰值<br>电平 |

|----|----|--------|--------|----------------|--------|---------|-------------|----------|----------|

| 2  | 1  | 0.6104 | 0.7106 | 0.9368         | 1.3032 | 0.7673  |             | 0.3638   | 0.0999   |

| 3  | 1  | 0.3490 | 0.8684 | 0.9359         | 0.7458 | 1.3408  |             | 0.7952   | 3.1978   |

|    | 2  | 0.6970 |        | 0.6970         |        |         | 0.6970      |          |          |

| 4  | 1  | 0.2177 | 0.9254 | 0.9507         | 0.4580 | 2.1834  |             | 0.8994   | 7.0167   |

|    | 2  | 0.5257 | 0.3833 | 0.6506         | 1.6160 | 0.6188  | 0.5596      |          |          |

| 5  | 1  | 0.3842 | 0.5884 | 0.7027         | 1.0935 | 0.9145  |             | 0.4457   | 0.7662   |

|    | 2  | 0.1468 | 0.9521 | 0.9634         | 0.3048 | 3.2812  |             | 0.9407   | 10.4226  |

|    | 3  | 0.4749 |        | 0.4749         |        |         | 0.4749      |          |          |

| 6  | 1  | 0.3916 | 0.2590 | 0.4695         | 1.6682 | 0.5995  | 0.3879      |          |          |

|    | 2  | 0.2867 | 0.7077 | 0.7636         | 0.7509 | 1.3316  |             | 0.6470   | 3.1478   |

|    | 3  | 0.1049 | 0.9667 | 0.9724         | 0.2158 | 4.6348  |             | 0.9610   | 13.3714  |

| 7  | 1  | 0.3178 | 0.4341 | 0.5380         | 1.1814 | 0.8464  |             | 0.2957   | 0.4157   |

|    | 2  | 0.2200 | 0.7823 | 0.8126         | 0.5414 | 1.8469  |             | 0.7507   | 5.6595   |

|    | 3  | 0.0785 | 0.9755 | 0.9787         | 0.1604 | 6.2335  |             | 0.9723   | 15.9226  |

|    | 4  | 0.3528 |        | 0.3528         |        |         | 0.3528      |          |          |

| 8  | 1  | 0.3058 | 0.1952 | 0.3628         | 1.6858 | 0.5932  | 0.2956      |          |          |

|    | 2  | 0.2529 | 0.5558 | 0.6106         | 0.8283 | 1.2073  |             | 0.4949   | 2.4532   |

|    | 3  | 0.1732 | 0.8319 | 0.8497         | 0.4077 | 2.4531  |             | 0.8137   | 7.9784   |

|    | 4  | 0.0608 | 0.9812 | 0.9831         | 0.1237 | 8.0819  |             | 0.9793   | 18.1669  |

| 9  | 1  | 0.2622 | 0.3421 | 0.4310         | 1.2166 | 0.8219  |             | 0.2197   | 0.3037   |

|    | 2  | 0.2137 | 0.6430 | 0.6776         | 0.6308 | 1.5854  |             | 0.6064   | 4.4576   |

|    | 3  | 0.1395 | 0.8663 | 0.8775         | 0.3180 | 3.1450  |             | 0.8550   | 10.0636  |

|    | 4  | 0.0485 | 0.9852 | 0.9864         | 0.0982 | 10.1795 |             | 0.9840   | 20.1650  |

|    | 5  | 0.2790 |        | 0.2790         |        |         | 0.2790      |          |          |

| 10 | 1  | 0.2493 | 0.1564 | 0.2943         | 1.6942 | 0.5902  | 0.2382      |          |          |

|    | 2  | 0.2249 | 0.4541 | 0.5067         | 0.8876 | 1.1266  |             | 0.3945   | 1.9880   |

|    | 3  | 0.1785 | 0.7073 | 0.7295         | 0.4894 | 2.0434  |             | 0.6844   | 6.4750   |

|    | 4  | 0.1146 | 0.8913 | 0.8986         | 0.2551 | 3.9208  |             | 0.8839   | 11.9386  |

|    | 5  | 0.0395 | 0.9880 | 0.9888         | 0.0799 | 12.5163 |             | 0.9872   | 21.9565  |

# **MT-206**

## 0.25 DB切比雪夫设计

表4.

| 阶数 | 部分 | 实部     | 虚部     | F <sub>o</sub> | α      | Q       | -3 db<br>频率 | 峰值<br>频率 | 峰值<br>电平 |

|----|----|--------|--------|----------------|--------|---------|-------------|----------|----------|

| 2  | 1  | 0.5621 | 0.7154 | 0.9098         | 1.2356 | 0.8093  |             | 0.4425   | 0.2502   |

| 3  | 1  | 0.3062 | 0.8712 | 0.9234         | 0.6632 | 1.5079  |             | 0.8156   | 4. 0734  |

|    | 2  | 0.6124 |        | 0.6124         |        |         | 0.6124      |          |          |

| 4  | 1  | 0.4501 | 0.3840 | 0.5916         | 1.5215 | 0.6572  | 0.5470      |          |          |

|    | 2  | 0.1865 | 0.9272 | 0.9458         | 0.3944 | 2.5356  |             | 0.9082   | 8.2538   |

| 5  | 1  | 0.3247 | 0.5892 | 0.6727         | 0.9653 | 1.0359  |             | 0.4917   | 1.4585   |

|    | 2  | 0.1240 | 0.9533 | 0.9613         | 0.2580 | 3.8763  |             | 0.9452   | 11.8413  |

|    | 3  | 0.4013 |        | 0.4013         |        |         | 0.4013      |          |          |

| 6  | 1  | 0.3284 | 0.2593 | 0.4184         | 1.5697 | 0.6371  | 0.3730      |          |          |

|    | 2  | 0.2404 | 0.7083 | 0.7480         | 0.6428 | 1.5557  |             | 0.6663   | 4.3121   |

|    | 3  | 0.0880 | 0.9675 | 0.9715         | 0.1811 | 5.5205  |             | 0.9635   | 14.8753  |

| 7  | 1  | 0.2652 | 0.4344 | 0.5090         | 1.0421 | 0.9596  |             | 0.3441   | 1. 0173  |

| ,  | 2  | 0.1835 | 0.7828 | 0.8040         | 0.4565 | 2.1908  |             | 0.7610   | 7. 0443  |

|    | 3  | 0.0655 | 0.9761 | 0.9783         | 0.1339 | 7.4679  |             | 0.9739   | 17.4835  |

|    | 4  | 0.2944 | 0.3701 | 0.2944         | 0.1333 | 7.1075  | 0.2944      | 0.57.55  | 17.1655  |

| 8  | 1  | 0.2543 | 0.1953 | 0.3206         | 1.5862 | 0.6304  | 0.2822      |          |          |

| 0  | 2  | 0.2343 | 0.1953 | 0.5266         | 0.7230 | 1.3832  | 0.2022      | 0.5126   | 3.4258   |

|    | 3  | 0.1441 | 0.8323 | 0.8447         | 0.7230 | 2.9309  |             | 0.8197   | 9.4683   |

|    | 4  | 0.0506 | 0.9817 | 0.9830         | 0.1029 | 9.7173  |             | 0.9804   | 19.7624  |

| 9  | 1  | 0.2176 | 0.3423 | 0.4056         | 1.0730 | 0.9320  |             | 0.2642   | 0.8624   |

| ,  | 2  | 0.1774 | 0.6433 | 0.4650         | 0.5317 | 1.8808  |             | 0.6184   | 5.8052   |

|    | 3  | 0.1158 | 0.8667 | 0.8744         | 0.2649 | 3.7755  |             | 0.8589   | 11.6163  |

|    | 4  | 0.0402 | 0.9856 | 0.9864         | 0.0815 | 12.2659 |             | 0.9848   | 21.7812  |

|    | 5  | 0.2315 | 0.5050 | 0.2315         | 0.0015 | 12.2033 | 0.2315      | 0.5010   | 21.7012  |

| 10 | 1  | 0.2065 | 0.1565 | 0.2591         | 1.5940 | 0.6274  | 0.2267      |          |          |

| 10 | 2  | 0.2003 | 0.1363 | 0.4910         | 0.7588 | 1.3178  | 0.2207      | 0.4143   | 3. 0721  |

|    | 3  | 0.1803 | 0.7075 | 0.7228         | 0.4090 | 2.4451  |             | 0.6919   | 7.9515   |

|    | 4  | 0.1478 | 0.7073 | 0.7228         | 0.4090 | 4.7236  |             | 0.8864   | 13.5344  |

|    | 5  | 0.0327 | 0.9883 | 0.9888         | 0.0661 | 15.1199 |             | 0.9878   | 23.5957  |

## 0.5 DB切比雪夫设计

表5.

| 阶数 | 部分  | 实部               | 虚部     | F <sub>o</sub>   | α      | Q       | -3 db<br>频率 | 峰值<br>频率 | 峰值<br>电平 |

|----|-----|------------------|--------|------------------|--------|---------|-------------|----------|----------|

| 2  | 1   | 0.5129           | 0.7225 | 1.2314           | 1.1577 | 0.8638  |             | 0.7072   | 0.5002   |

| 2  | 1   | 0.2602           | 0.0752 | 1.0600           | 0.5061 | 1 7061  |             | 0.0727   | F 0201   |

| 3  | 1 2 | 0.2683<br>0.5366 | 0.8753 | 1.0688<br>0.6265 | 0.5861 | 1.7061  | 0.6265      | 0.9727   | 5.0301   |

|    |     | 0.5500           |        | 0.0203           |        |         | 0.0203      |          |          |

| 4  | 1   | 0.3872           | 0.3850 | 0.5969           | 1.4182 | 0.7051  | 0.5951      |          |          |

|    | 2   | 0.1605           | 0.9297 | 1.0313           | 0.3402 | 2.9391  |             | 1.0010   | 9.4918   |

| 5  | 1   | 0.2767           | 0.5902 | 0.6905           | 0.8490 | 1.1779  |             | 0.5522   | 2.2849   |

| 3  | 2   | 0.1057           | 0.9550 | 1.0178           | 0.2200 | 4.5451  |             | 1.0054   | 13.2037  |

|    | 3   | 0.3420           |        | 0.3623           |        |         | 0.3623      |          | 1012001  |

|    |     |                  |        |                  |        |         |             |          |          |

| 6  | 1   | 0.2784           | 0.2596 | 0.3963           | 1.4627 | 0.6836  | 0.3827      |          |          |

|    | 2   | 0.2037           | 0.7091 | 0.7680           | 0.5522 | 1.8109  |             | 0.7071   | 5.5025   |

|    | 3   | 0.0746           | 0.9687 | 1.0114           | 0.1536 | 6.5119  |             | 1.0055   | 16.2998  |

| 7  | 1   | 0.2241           | 0.4349 | 0.5040           | 0.9161 | 1. 0916 |             | 0.3839   | 1.7838   |

|    | 2   | 0.1550           | 0.7836 | 0.8228           | 0.3881 | 2.5767  |             | 0.7912   | 8.3880   |

|    | 3   | 0.0553           | 0.9771 | 1.0081           | 0.1130 | 8.8487  |             | 1.0049   | 18.9515  |

|    | 4   | 0.2487           |        | 0.2562           |        |         | 0.2562      |          |          |

| 8  | 1   | 0.2144           | 0.1955 | 0.2968           | 1.4779 | 0.6767  | 0.2835      |          |          |

|    | 2   | 0.1817           | 0.5565 | 0.5989           | 0.6208 | 1.6109  |             | 0.5381   | 4.5815   |

|    | 3   | 0.1214           | 0.8328 | 0.8610           | 0.2885 | 3.4662  |             | 0.8429   | 10.8885  |

|    | 4   | 0.0426           | 0.9824 | 1.0060           | 0.0867 | 11.5305 |             | 1.0041   | 21.2452  |

| 9  | 1   | 0.1831           | 0.3425 | 0.3954           | 0.9429 | 1.0605  |             | 0.2947   | 1.6023   |

|    | 2   | 0.1493           | 0.6436 | 0.6727           | 0.4520 | 2.2126  |             | 0.6374   | 7.1258   |

|    | 3   | 0.0974           | 0.8671 | 0.8884           | 0.2233 | 4.4779  |             | 0.8773   | 13.0759  |

|    | 4   | 0.0338           | 0.9861 | 1.0046           | 0.0686 | 14.5829 |             | 1.0034   | 23.2820  |

|    | 5   | 0.1949           |        | 0.1984           |        |         | 0.1984      |          |          |

| 10 | 1   | 0.1736           | 0.1566 | 0.2338           | 1.4851 | 0.6734  | 0.2221      |          |          |

|    | 2   | 0.1566           | 0.4545 | 0.4807           | 0.6515 | 1.5349  |             | 0.4267   | 4.2087   |

|    | 3   | 0.1243           | 0.7078 | 0.7186           | 0.3459 | 2.8907  |             | 0.6968   | 9.3520   |

|    | 4   | 0.0798           | 0.8919 | 0.8955           | 0.1782 | 5.6107  |             | 0.8883   | 15.0149  |

|    | 5   | 0.0275           | 0.9887 | 0.9891           | 0.0556 | 17.9833 |             | 0.9883   | 25.1008  |

# **MT-206**

## 1 DB切比雪夫设计

表6.

| 阶数 | 部分 | 实部     | 虚部     | F <sub>o</sub> | α      | Q       | -3 db<br>频率 | 峰值<br>频率 | 峰值<br>电平 |

|----|----|--------|--------|----------------|--------|---------|-------------|----------|----------|

| 2  | 1  | 0.4508 | 0.7351 | 0.8623         | 1.0456 | 0.9564  |             | 0.5806   | 0.9995   |

| 3  | 1  | 0.2257 | 0.8822 | 0.9106         | 0.4957 | 2.0173  |             | 0.8528   | 6.3708   |

|    | 2  | 0.4513 |        | 0.4513         |        |         | 0.4513      |          |          |

| 4  | 1  | 0.3199 | 0.3868 | 0.5019         | 1.2746 | 0.7845  |             | 0.2174   | 0.1557   |

|    | 2  | 0.1325 | 0.9339 | 0.9433         | 0.2809 | 3.5594  |             | 0.9245   | 11.1142  |

| 5  | 1  | 0.2265 | 0.5918 | 0.6337         | 0.7149 | 1.3988  |             | 0.5467   | 3.5089   |

|    | 2  | 0.0865 | 0.9575 | 0.9614         | 0.1800 | 5.5559  |             | 0.9536   | 14.9305  |

|    | 3  | 0.2800 |        | 0.2800         |        |         | 0.2800      |          |          |

| 6  | 1  | 0.2268 | 0.2601 | 0.3451         | 1.3144 | 0.7608  |             | 0.1273   | 0.0813   |

|    | 2  | 0.1550 | 0.7106 | 0.7273         | 0.4262 | 2.3462  |             | 0.6935   | 7.6090   |

|    | 3  | 0.0608 | 0.9707 | 0.9726         | 0.1249 | 8.0036  |             | 0.9688   | 18.0827  |

| 7  | 1  | 0.1819 | 0.4354 | 0.4719         | 0.7710 | 1.2971  |             | 0.3956   | 2.9579   |

|    | 2  | 0.1259 | 0.7846 | 0.7946         | 0.3169 | 3.1558  |             | 0.7744   | 10.0927  |

|    | 3  | 0.0449 | 0.9785 | 0.9795         | 0.0918 | 10.8982 |             | 0.9775   | 20.7563  |

|    | 4  | 0.2019 |        | 0.2019         |        |         | 0.2019      |          |          |

| 8  | 1  | 0.1737 | 0.1956 | 0.2616         | 1.3280 | 0.7530  |             | 0.0899   | 0.0611   |

|    | 2  | 0.1473 | 0.5571 | 0.5762         | 0.5112 | 1.9560  |             | 0.5373   | 6.1210   |

|    | 3  | 0.0984 | 0.8337 | 0.8395         | 0.2344 | 4.2657  |             | 0.8279   | 12.6599  |

|    | 4  | 0.0346 | 0.9836 | 0.9842         | 0.0702 | 14.2391 |             | 0.9830   | 23.0750  |

| 9  | 1  | 0.1482 | 0.3427 | 0.3734         | 0.7938 | 1.2597  |             | 0.3090   | 2.7498   |

|    | 2  | 0.1208 | 0.6442 | 0.6554         | 0.3686 | 2.7129  |             | 0.6328   | 8.8187   |

|    | 3  | 0.0788 | 0.8679 | 0.8715         | 0.1809 | 5.5268  |             | 0.8643   | 14.8852  |

|    | 4  | 0.0274 | 0.9869 | 0.9873         | 0.0555 | 18.0226 |             | 0.9865   | 25.1197  |

|    | 5  | 0.1577 |        | 0.1577         |        |         | 0.1577      |          |          |

| 10 | 1  | 0.1403 | 0.1567 | 0.2103         | 1.3341 | 0.7496  |             | 0.0698   | 0.0530   |

|    | 2  | 0.1266 | 0.4548 | 0.4721         | 0.5363 | 1.8645  |             | 0.4368   | 5.7354   |

|    | 3  | 0.1005 | 0.7084 | 0.7155         | 0.2809 | 3.5597  |             | 0.7012   | 11.1147  |

|    | 4  | 0.0645 | 0.8926 | 0.8949         | 0.1441 | 6.9374  |             | 0.8903   | 16.8466  |

|    | 5  | 0.0222 | 0.9895 | 0.9897         | 0.0449 | 22.2916 |             | 0.9893   | 26.9650  |

## 参考文献

$Zumbahlen, Hank.\ \textit{Linear Circuit Design Handbook}.\ Elsevier.\ 2008.\ ISBN:\ 978-7506-8703-4.$

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

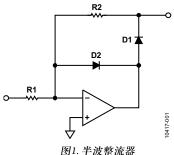

## 半波整流器

作者: ADI公司 Hank Zumbahlen

### 引言

半波整流器通常用于从交流输入获得直流电平。该整 流器是一系列小型指南描述的、内置运算放大器的多 种分立式电路之一。

半波整流器通常用于从交流输入获得直流电平。这点通常 用于测量交流信号的幅度。

为了理解半波整流器的工作原理,我们不妨假定运算放大 器和二极管在理论上无正向电压。

对于正输入电压,输出会尽量变为负。这使D2接通, D1 断开。假设D2短路,结果将使输出保持于地电位,因为运 算放大器的行为迫使运算放大器的输入电压保持相同电 平。

对于负输入电压,输出将变为正,D1接通,D2断开。此 时,输出端充当一个反相放大器(见MT-213),其增益由 R2/R1设定。其结果是,输出在输入(反相)负半周期之后, 正半周期的输出为0 V。

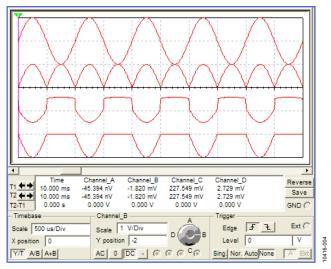

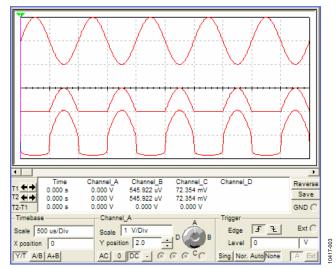

图2. 半波整流器波形

图2所示为半波整流器的波形。顶部曲线为输入,底部曲 线则为输出。

图3所示为运算放大器的输出。请注意,在实际电路中, 运算放大器的输出实际采用开环模式,直到达到D2的正向 电压为止。图中所示为底部曲线(通道C)。

图3. 半波整流器波形与运算放大器输出

## MT-212

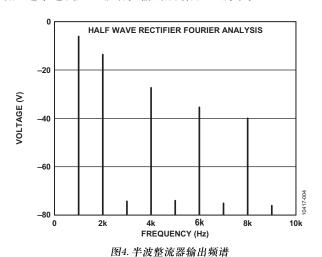

半波整流器的输出端之后为一个滤波器,用于形成直流电平。该滤波器的转折频率应置于足够低的水平,以限制输出上的交流纹波,同时还必须足够高,以免对电路的瞬态响应速率造成严重影响。输出频谱如图4所示。

通过同时反转两个二极管,可以将输出的极性转换为负。

误差项与反相放大器相同(见MT-213)。最重要的是失调项。该电路的频率响应主要由运算放大器的开环增益设定。二极管的等效并联电容和二极管导通/关断时间也会影响到频率响应,但其影响一般比运算放大器要小得多。

半波整流器的一个缺陷是,仅在输入的半周期内工作。对于中线周围的对称输入(如正弦波),这不一定会构成真正的问题。为抵消此限制,人们对该电路进行了改进,这就是全波整流器。(见MT-211)。

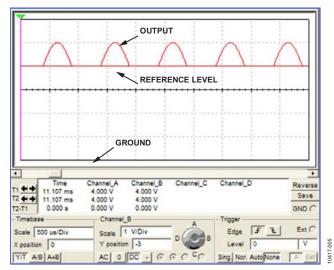

采用单电源电压供电时,同相输入偏置到基准电压,通常 为电源电压的½。此时,零输入信号输出为基准电压。 图5所示单电源半波整流器的基准电压(运算放大器同相输入端的电压)为+4 V。在示意图中,地位于底部。

图5. 单电源半波整流器波形

输入仍然以地为参考,因此,输入端必须用串联电容进行交流耦合。频率的低端取决于输入耦合电容和输入电阻R1的RC时间常数。对于双极性电源,电路响应可以到达直流。另外,如果上述电路以相同的基准电压为参考,则输入可能为直流耦合。如果采用电路增益,则需要格外小心。运算放大器上的频率响应要求取决于最大信号输入频率。必须有足够的开环增益,二极管才可偏置。因此,根据经验,运算放大器的带宽至少应为20 dB,在输入信号的最大频率处。

修订历史 2012年4月—修订版0:初始版

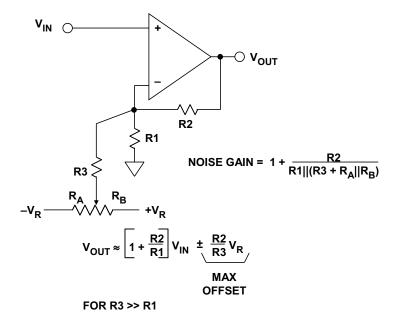

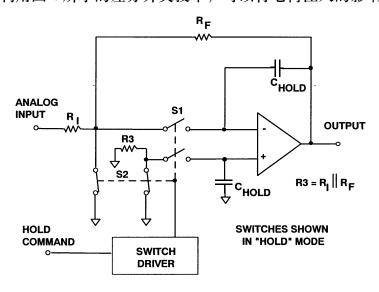

## 单极点系统的运算放大器总输出噪声计算

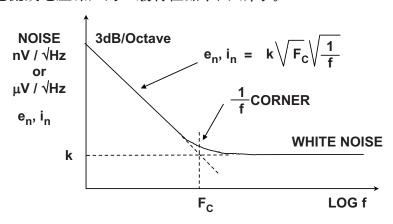

我们已经指出,噪声比一些较大噪声源少三分之一至五分之一的任何噪声源都可以忽略,几乎不会有误差。此时,两个噪声电压必须在电路内的同一点测量。要分析运算放大器电路的噪声性能,必须评估电路每一部分的噪声贡献,并确定以哪些噪声为主。为了简化后续计算,可以用噪声频谱密度来代替实际电压,从而带宽不会出现在计算公式中(噪声频谱密度一般用nV/√Hz表示,相当于1 Hz带宽中的噪声)。

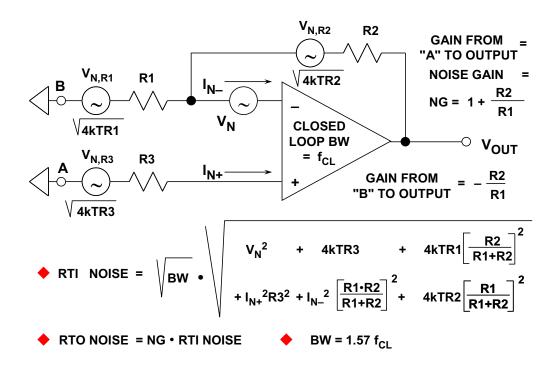

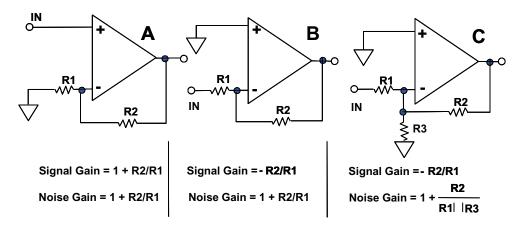

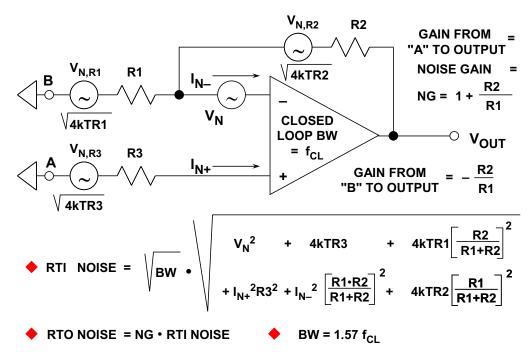

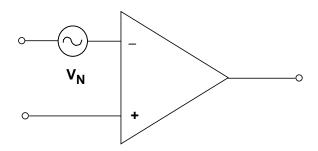

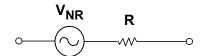

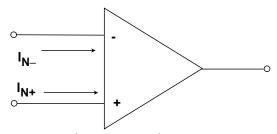

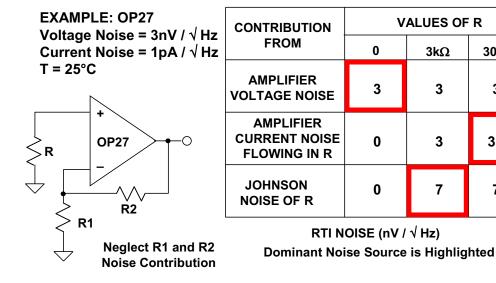

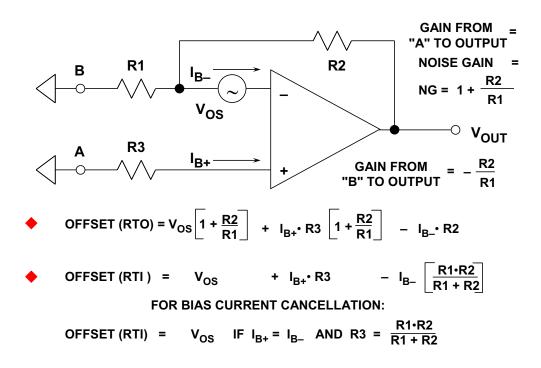

如果考虑下图1中的电路——由一个运算放大器和三个电阻组成的放大器(R3代表节点A处的源阻抗),可以发现六个独立噪声源:三个电阻的约翰逊噪声、运算放大器电压噪声和运算放大器各输入端的电流噪声。每个噪声源都会贡献一定的放大器输出端噪声。噪声一般用RTI来规定,或折合到输入端,但计算折合到输出端(RTO)噪声往往更容易,然后将其除以放大器的噪声增益(非信号增益)便得到RTI噪声。

图1: 单极点系统的运算放大器噪声模型

下图2详细分析了图1中的各噪声源是如何反映到运算放大器输出端的。有关反相输入端的电流噪声效应,还需要进一步讨论。此电流 $I_{N-}$ 不会按预期流入R1——放大器周围的负反馈可使得反相输入端的电位保持不变,因此从该引脚流出的电流在负反馈强制作用下仅能流入R2,从而产生 $I_{N-}$  R2输出端电压。也可以考虑 $I_{N-}$ 流入R1和R2并联组合产生的电压,然后通过放大器的噪声增益放大,但结果是一样的,计算反而更复杂。

| NOISE SOURCE EXPRESSED AS A VOLTAGE                                       | MULTIPLY BY THIS FACTOR TO REFER TO THE OP AMP OUTPUT |

|---------------------------------------------------------------------------|-------------------------------------------------------|

| Johnson noise in R3:<br>√(4kTR3)                                          | Noise Gain = 1 + R2/R1                                |

| Non-inverting input current<br>noise flowing in R3:<br>I <sub>N+</sub> R3 | Noise Gain = 1 + R2/R1                                |

| Input voltage noise:<br>V <sub>N</sub>                                    | Noise Gain = 1 + R2/R1                                |

| Johnson noise in R1:<br>√(4kTR1)                                          | –R2/R1 (Gain from input of R1<br>to output)           |

| Johnson noise in R2:<br>√(4kTR2)                                          | 1                                                     |

| Inverting input current noise<br>flowing in R2:<br>I <sub>N</sub> _R2     | 1                                                     |

图2: 折合到输出端的噪声源(RTO)

请注意,与三个电阻相关的约翰逊噪声电压已包括在图2的表达式中。所有电阻的约翰逊噪声为 $\sqrt{(4kTBR)}$ ,其中k是玻尔兹曼常数 $(1.38\times10^{-23}\ J/K)$ ,T是绝对温度,B是带宽(单位为Hz),R是电阻(单位为 $\Omega$ )。一个很容易记住的简单关系是:1000  $\Omega$ 电阻在25°C时产生的约翰逊噪声为 $4\,nV/\sqrt{Hz}$ 。

以上分析假设是单极点系统,其中反馈网络为纯阻性,且噪声增益与频率关系曲线平坦。此情况适用于大多数应用,但如果反馈网络包含电抗元件(通常为电容),则噪声增益在目标带宽内不恒定,必须使用更复杂的技术来计算总噪声。有关二阶系统噪声的考虑,请参见指南MT-050。

62 Page 2 of 3

### 参考文献

- 1. Hank Zumbahlen, *Basic Linear Design*, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 1.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 1.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 3 of 3 63

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## 双T陷波滤波器

作者: ADI公司 Hank Zumbahlen

### 引言

本小型指南讨论一种双T陷波滤波器设计示例,是一系列介绍精密运算放大器分立式电路的小型指南之一。

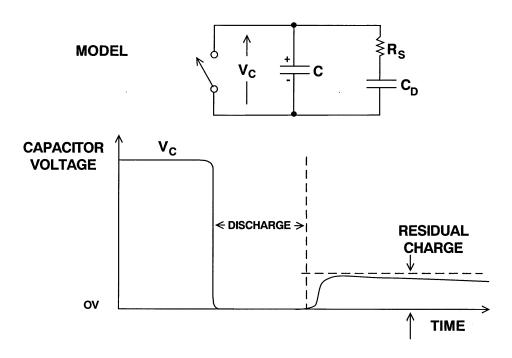

双T设计广泛用作一种通用型陷波电路,如图1所示。双T的无源实现方式(即无反馈)存在一个大缺陷: 其Q固定为0.25。该问题可以通过向参考节点应用正反馈来进行整流纠正。信号反馈量(由R4/R5之比设置)决定电路的Q值,而Q值又决定陷波深度。要使陷波深度达到最大,可以取消电阻R4和R5以及相应的运算放大器。这种情况下,C3和R3的结点将直接连接至输出端。

图1. 双T陷波滤波器

调整并非易事,因为需要对元件(R1和R2、C1和C2)进行跟踪。使用标准的1%元件时,最多可以获得60 dB的陷波,而更典型的值则为40-50 dB。

双T陷波滤波器的设计公式见"双T陷波设计公式"部分。

#### 双T陷波设计公式

$$\frac{s^2 + \omega_0 2}{s^2 + 4\omega_0 (1 - K)s + {\omega_0}^2}$$

$$\frac{V_O}{V_{IN}} = \frac{s^2 \frac{1}{RC}}{s^2 + \frac{1}{RC} 4 \left(1 - \frac{R5}{R4 + R5}\right) s + \frac{1}{RC}}$$

要设计该滤波器,请选择C、K和R'。.

#### 那么

$$k = 2 \pi F_0 C$$

$$R4 = (1 - K)R'$$

$$R = \frac{1}{k}$$

$$R5 = KR'$$

$$R = R1 = R2 = 2 R3$$

$$C = C1 = C2 = \frac{C3}{2}$$

$$K = 1 - \frac{1}{4Q}$$

$$F_0 = \frac{1}{2\pi RC}$$

对于K=1, 取消R4和R5(即R4→0, R5, Q→∞)。

#### 参考文献

Zumbahlen, Hank, editor, 2008. *Linear Circuit Design Handbook*, Newnes, ISBN 978-0-7506-8703-4.

#### 修订历史

2012年3月—修订版0: 初始版

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

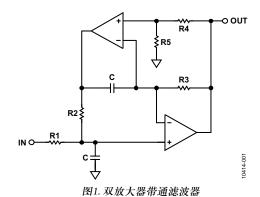

## 双放大器带通(DABP)滤波器

作者: ADI公司 Hank Zumbahlen

#### 引言

贝塞尔滤波器是关注相位响应的运算放大器的理想双放大器带通滤波器用于高Q和高频设计中。该滤波器是一系列小型指南描述的、内置运算放大器的多种分立式电路之一。

双放大器带通滤波器结构对于要求高Q和高频的设计十分 有用。其元件灵敏度较低,元件扩散度低。这种电路的一 个有用特性是,其Q和谐振频率可在一定程度上独立调 节。

如图1所示,谐振频率可以按R2调节。在此基础上,则可针对Q调节R1。在这种拓扑结构中,对使用双运算放大器非常有用。两个运算放大器的匹配可以降低Q对放大器参数的灵敏度。

请注意,DABP谐振时的增益为2。如果需要更低的增益,则可对电阻R1分路,以形成一个分压器。这反映在DABP设计等式的附加项上(见图2)。

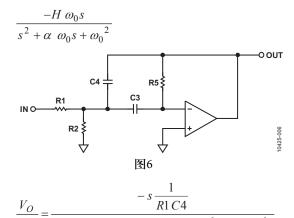

$$\frac{+H\omega_0^S}{s^2 + \alpha\omega_0 s + \omega_0^2}$$

图2. 双放大器带通滤波器的设计等式

$$\frac{V_O}{V_{IN}} = \frac{s\left(\frac{2}{R1C}\right)}{s^2 + s\left(\frac{1}{R1C}\right) + \frac{1}{R2 R3 C^2}}$$

选择C, R4。

$$R = \frac{1}{2\pi F_0 C}$$

$$R1 = QR$$

$$R2 = R3 = R$$

若增益<2(增益= A,):

$$R1A = \frac{2R1}{A_V}$$

$$R1B = \frac{R1A A_V}{2 - A_V}$$

# MT-209

### 参考文献

$Zumbahlen, Hank.\ \textit{Linear Circuit Design Handbook}.\ Elsevier.\ 2008.\ ISBN:\ 978-7506-8703-4.$

## 修订历史

2012年3月—修订版0: 初始版

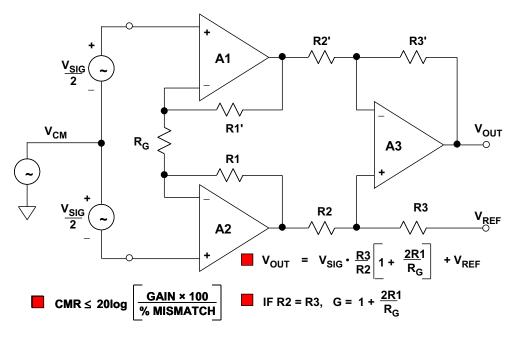

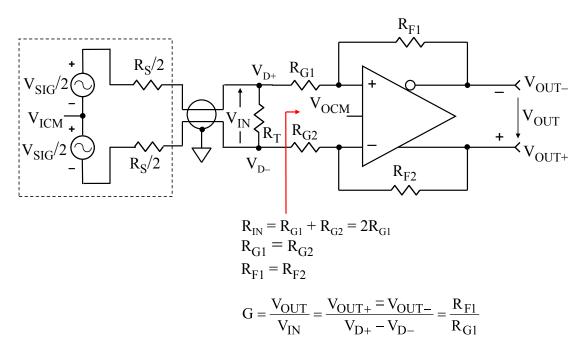

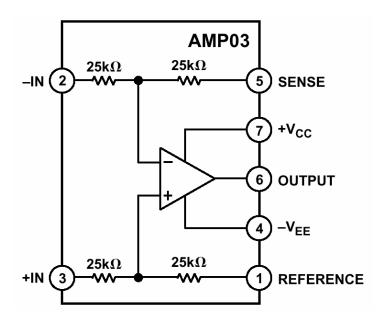

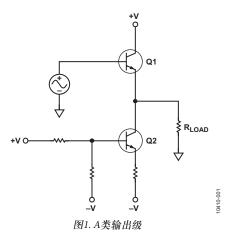

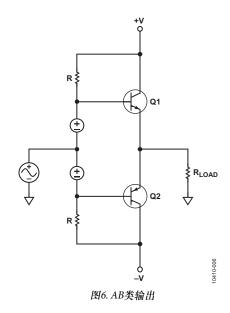

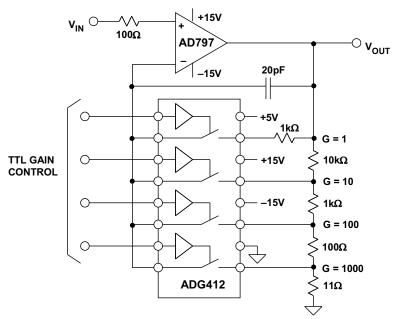

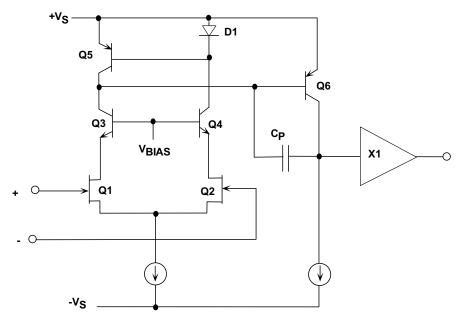

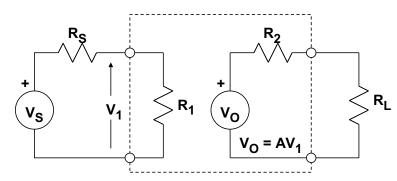

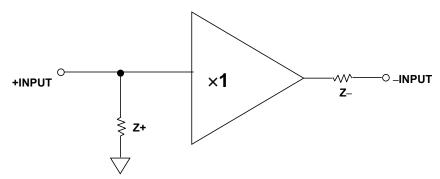

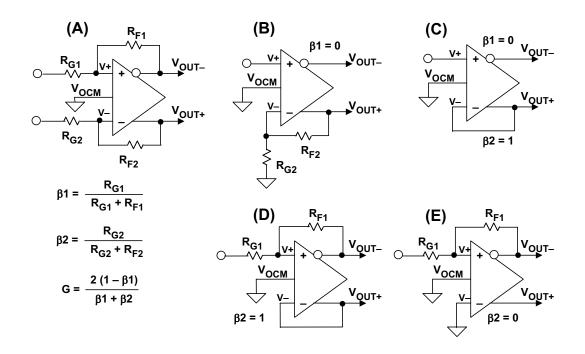

### 双运放仪表放大器基本配置

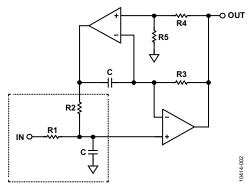

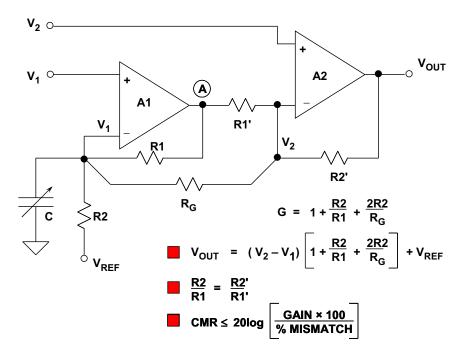

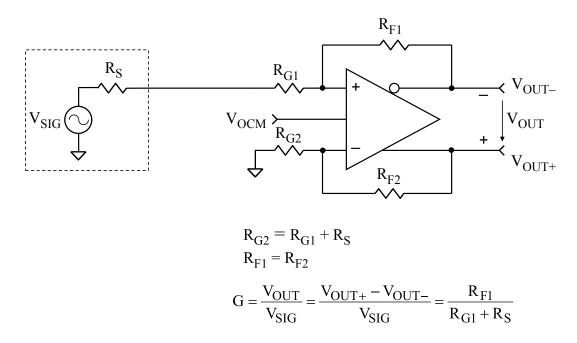

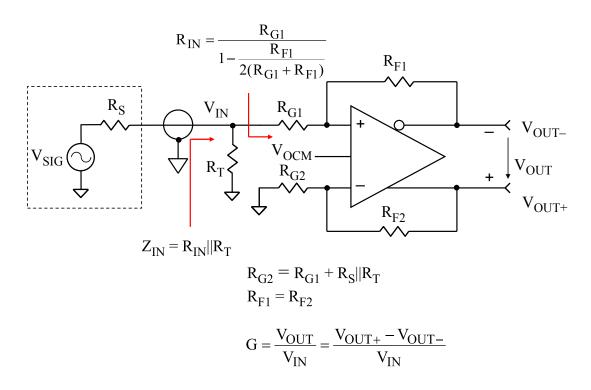

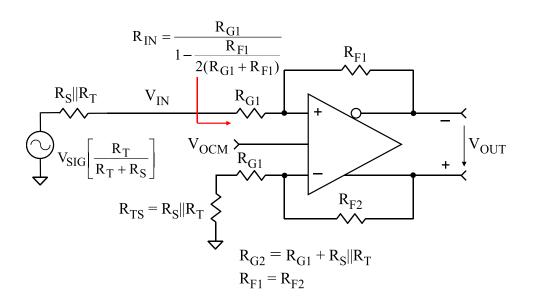

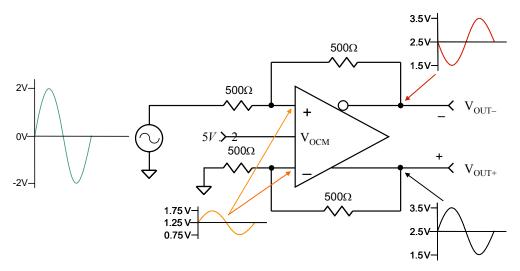

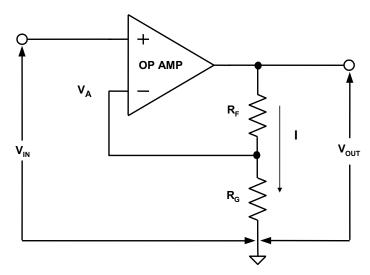

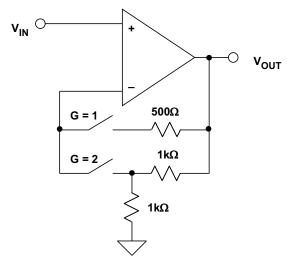

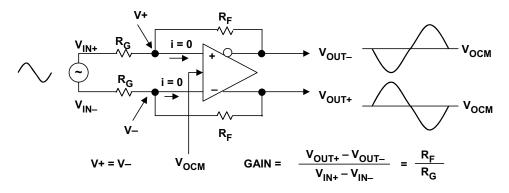

仪表放大器是基于运算放大器的,有两种基本配置极为常见。第一种基于双运算放大器,第二种则基于三运算放大器。图1所示电路称为双运放仪表放大器。双通道精密IC运算放大器在大多数情况下拥有良好匹配,例如OP297或OP284。电阻通常是同一芯片上的薄膜激光调整阵列。仪表放大器增益可利用外部电阻R<sub>G</sub>轻松设置。无R<sub>G</sub>时,增益是1+R2/R1。实际应用中,R2/R1比值依据所需的最小仪表放大器增益来选择。

图1: 双运放仪表放大器

双运放仪表放大器的输入阻抗本身较高,使得信号源阻抗可能较高且失衡。直流共模抑制性能受R1/R2与R1'/R2'的匹配限制。如果四个电阻中有任何一个存在不匹配,直流共模抑制比限于下值:

$$CMR \le 20 \log \left[ \frac{GAIN \times 100}{\%MISMATCH} \right].$$

公式1

请注意,电路净CMR随着仪表放大器工作增益增大而成比例提高,从而有效提升较高增益下的性能。

IC仪表放大器特别适合同时满足增益设置电阻的比率匹配和温度跟踪需求。虽然在硅片上制造的薄膜电阻最高具有±20%的初始容差,生产过程中的激光调整可将电阻间比率误差减小至0.01% (100 ppm)。另外,薄膜电阻温度系数之间的跟踪本身较低,通常小于3 ppm/℃ (0.0003%/℃)。

使用双电源时, $V_{REF}$ 一般直接接地。在单电源应用中, $V_{REF}$ 通常连接至等于电源电压一半的低阻抗电压源。从 $V_{REF}$ 到节点"A"的增益为R1/R2,从节点"A"到输出的增益为R2'/R1'。假定比率匹配是理想的,则从 $V_{REF}$ 到输出的增益等于单位增益。请注意, $V_{REF}$ 的源阻抗必须较低,否则CMR会降低。

双运放仪表放大器的一个主要缺点是共模电压输入范围必须相对于增益进行取舍。放大器 A1必须将 $V_1$ 下的信号放大1+R1/R2倍。如果R1>>R2(图1中的低增益示例),一旦 $V_1$ 共模信号过高A1将发生饱和,结果消耗掉用于放大目标差分信号的A1"余量"。对于高增益(R1<<R2),节点"A"则有更多的余量,可提供更大的共模输入电压。

此配置的交流共模抑制性能一般较差,因为从 $V_1$ 到 $V_{OUT}$ 的信号路径具有额外的A1相移。此外,两个放大器在不同闭环增益下(对应于不同带宽)工作。图1所示的小调整电容"C"可稍微改善交流CMR。

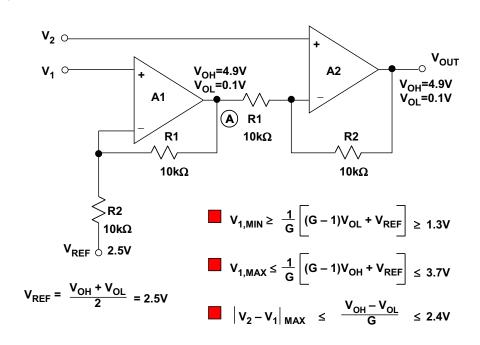

不使用R。时,低增益(G=2)单电源双运放仪表放大器配置结果如以上图2所示。

图2:  $V_s = +5V$ 、G = 2时的双运放仪表放大器单电源限制

输入共模和差分信号值必须限制,以防止A1或A2发生饱和。本例中,运算放大器在供电轨的0.1 V内保持线性,输出上限和下限分别指定为V<sub>OH</sub>和V<sub>OL</sub>。这些饱和电压限值是单电源、轨到轨输出运算放大器(例如AD822)的典型值。

使用图2的公式, $V_1$ 的电压必须介于1.3 V至2.4 V之间,以防止A1发生饱和。请注意, $V_{REF}$  连接到 $V_{OH}$ 和 $V_{OL}$ 的平均值(2.5 V)。这是为了提供双极性差分输入信号和以+2.5 V为参考的  $V_{OUT}$ 。

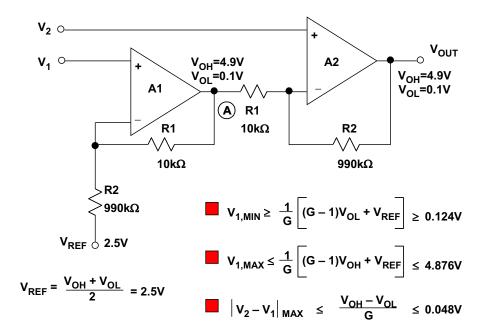

以下图3显示高增益(G=100)单电源双运放仪表放大器配置。请注意,使用相同公式, $V_{\text{RFF}}$  的电压现在可在0.124 V至4.876 V间摆动。 $V_{\text{RFF}}$  仍为2.5 V,以提供双极性输入和输出信号。

图3:  $V_s = +5V$ 、G = 100时的双运放仪表放大器单电源限制

所有这些分析都显示,采用单电源供电时,传统的双运放仪表放大器架构存在较大限制。 一方面,该架构对给定增益下的容许输入CM范围造成限制。另一方面,它对给定CM输入 电压下的容许增益范围造成限制。

不过,还有许多情况下,增益和CM电压的组合无法用图1至3的基本双运算放大器结构来支持,即使放大器是理想的(即两个供电轨均有零输出饱和电压)。

总而言之,无论增益如何,常见的双运放仪表放大器基本结构在采用单电源供电时无法提供0V的CM输入电压。消除这些单电源供电限制的唯一途径是修改仪表放大器架构。

Page 3 of 5 69

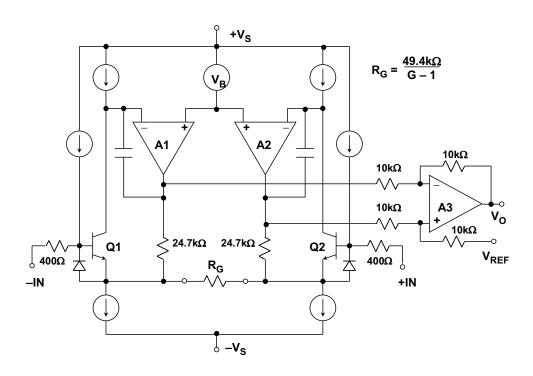

### AD627单电源双运放仪表放大器

通过对基本双运放仪表放大器架构做一些关键修改,可以克服上述CM限制。以下图4为AD627仪表放大器架构,其中显示了这些在电路中实施的修改。

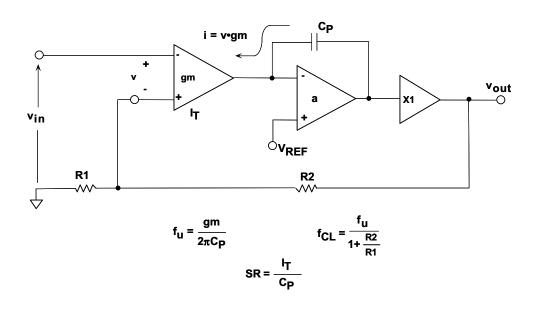

图4: AD627仪表放大器架构

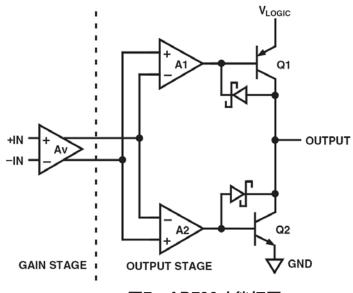

在此电路中,两个运算放大器均由一个PNP共发射极输入级和一个增益级构成,分别指定为Q1/A1和Q2/A2。PNP晶体管不仅提供增益,还可对输入信号进行电平转换,将其提高约0.5 V,因此共模输入电压可到达负供电轨以下0.1 V。容许的最大正输入电压比正供电轨低1 V。

AD627仪表放大器提供轨到轨输出摆幅,且具有宽电源电压范围(+2.7 V至±18 V)。无外部增益设置电阻 $R_G$ 时,仪表放大器增益最小值为5。通过添加外部电阻,增益最高可达1000。使用1 kΩ非均衡信号源、+3 V单电源且G = 5时,AD627B在60 Hz下的共模抑制比为85 dB。

虽然AD627是双运放仪表放大器,仍需注意,它没有图1所示基本电路的CM频率响应限制。由于使用专利电路,AD627 CMR的平坦频率远远高于传统分立式双运放仪表放大器可实现的水平。

70 Page 4 of 5

AD627数据手册详细说明了容许输入/输出电压范围,其与增益和电源电压成函数关系。 交互式<u>仪表放大器共模范围/增益计算器设计工具</u>可以帮助用户计算仪表放大器的基本共模范围和增益。

AD627的主要规格特性如以下图5所示。尽管是低功耗、单电源器件, AD627却能够采用传统的较高电压电源, 例如±15 V, 而且性能出色。

- Wide Supply Range: +2.7V to ±18V

- ♦ Input Voltage Range: -V<sub>S</sub> 0.1V to +V<sub>S</sub> 1V

- ♦ 85µA Supply Current

- ♦ Gain Range: 5 to 1000

- ♦ 75µV Maximum Input Offset Volage (AD627B)

- 10ppm/°C Maximum Offset Voltage TC (AD627B)

- 10ppm Gain Nonlinearity

- 85dB CMR @ 60Hz, 1kΩ Source Imbalance (G = 5)

- ◆ 3µV p-p 0.1Hz to 10Hz Input Voltage Noise (G = 5)

# 图5: AD627仪表放大器主要规格特性

# 参考文献

- Hank Zumbahlen, Basic Linear Design, Analog Devices, 2006, ISBN: 0-915550-28-1. Also available as <u>Linear Circuit Design Handbook</u>, Elsevier-Newnes, 2008, ISBN-10: 0750687037, ISBN-13: 978-0750687034. Chapter 2.

- 2. Walter G. Jung, *Op Amp Applications*, Analog Devices, 2002, ISBN 0-916550-26-5, Also available as *Op Amp Applications Handbook*, Elsevier/Newnes, 2005, ISBN 0-7506-7844-5. Chapter 2.

- 3. Charles Kitchin and Lew Counts, <u>A Designer's Guide to Instrumentation Amplifiers</u>, 3<sup>rd</sup> <u>Edition</u>, Analog Devices, 2006.

Copyright 2009, Analog Devices, Inc. All rights reserved. Analog Devices assumes no responsibility for customer product design or the use or application of customers' products or for any infringements of patents or rights of others which may result from Analog Devices assistance. All trademarks and logos are property of their respective holders. Information furnished by Analog Devices applications and development tools engineers is believed to be accurate and reliable, however no responsibility is assumed by Analog Devices regarding technical accuracy and topicality of the content provided in Analog Devices Tutorials.

Page 5 of 5 71

# 小型指南 MT-213

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

# 反相放大器

作者: Hank Zumbahlen, Analog Devices, Inc.

# 引言

作为一种基本的运算放大器电路,反相运算放大器是 系列小型指南中介绍的分立式电路之一。

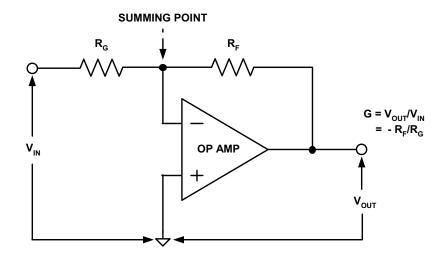

反相放大器是一种基本的运算放大器电路。

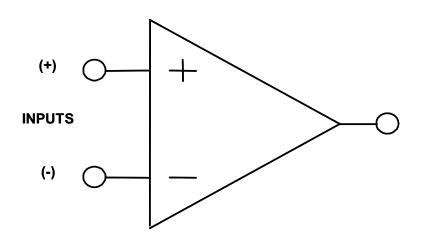

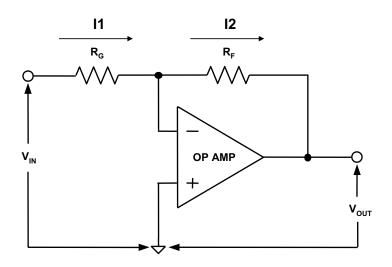

图1. 反相整流器

设运算放大器的输入阻抗无穷大,即是说无电流流入或流出运算放大器反相输入。由于运算放大器迫使两个输入端的电压相同,因此,反相输入(-)看起来也像是地。这一般称为虚拟地。另外,据基尔霍夫定律,流入节点的所有电流必须从节点流出。

输入电压决定电流

$$I_{I_N} = \frac{V_{IN}}{R_{IN}} \tag{\cup \text{\varphi}}$$

从求和节点流出的电流等于输入电流。

$$I_N = I_{OUT}$$

(等式2)

因而,流过反馈电阻(R<sub>p</sub>)的电压为:

$$-V_{OUT} = R_F \times I_{OUT} \tag{等式3}$$

该电压为负值(相对于输入电压),因为电流正从节点中流出。这也是该电路被称为反相放大器的原因所在。请注意,输入电压将按输入电阻的值来调整缩放。

在该电路中,主要的误差源是运算放大器的失调电压和偏置电流。失调电压会影响反相输入端的视在电压。该电压将不再是0 V。偏置电流会在对电流求和时导致误差,因为将有一个小电流流入或流出运算放大器的输入。

对于交流输入,会存在对运算放大器带宽的限制。

放大器电路的输入阻抗将为输入电阻的值。请记住,电阻的另一端为(虚拟)地。

以上讨论是以双极性电源为基础的。如果使用单电源,地 将由参考节点取代,后者的电压电平为 $V_{REF}$ , 一般相当于 电源电压的一半。在此基础上,输入和输出电压将以该电 压而非地为参考。

输入电流变成

$$I_{IN} = \frac{V_{IN} - V_{REF}}{R_{IN}} \tag{\xi \pi \pi}$$

输出变成

$$V_{REF} - V_{OUT} = \frac{R_F}{R_{IN}} \left( V_{IN} - V_{REF} \right) \tag{\$式5}$$

#### 修订历史

2012年2月—修订版0: 初始版

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

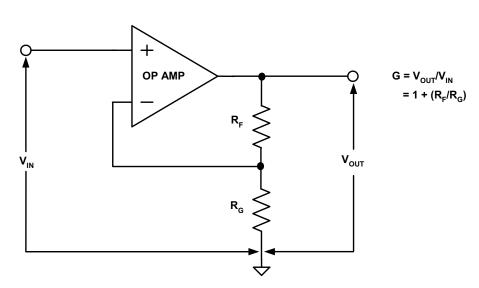

# 反相求和放大器

作者: ADI公司 Hank Zumbahlen

### 引言

作为基本反相运算放大器电路的扩展,反相求和放大器是一系列小型指南中描述的多种分立式电路之一。

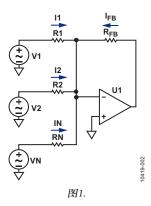

反相求和放大器是MT-213中所述反相放大器的一种扩展器件。然而,反相求和放大器有多路输入。

假设运算放大器的输入阻抗无穷大,因此电流不会流入或流出运算放大器的反相输入端。由于运算放大器迫使两个输入端的电压相同,因此,反相输入(-)看起来也像是地。这一般称为虚拟地。另外,据基尔霍夫定律,流入节点的所有电流必须从节点流出。

各输入电压决定电流

$$II = \frac{VI}{RI} \tag{1}$$

$$I2 = \frac{V2}{R2} \tag{2}$$

依此类推。

从求和节点流出的电流等于全部输入电流之和。因而,流过反馈电阻(Rfb)的电压为:

$$-V_{OUT} = Rfb \times (II + I2 + ... + IN)$$

(3)

或者

$$-V_{OUT} = \frac{Rfb}{R1}V1 + \frac{Rfb}{R2}V2 + ... + \frac{Rfb}{Rn}VN$$

(4)

该电压为负值(相对于输入电压),因为电流正从节点中流出。请注意,输入电压按输入电阻的值来调整缩放。

在该电路中,主要的误差源是运算放大器的失调电压和偏置电流。失调电压会影响反相输入端的可见电压。该电压将不再是0 V。偏置电流会在对电流求和时导致误差,因为将有一个小电流流入或流出运算放大器的输入端。

大量输入导致的一个潜在问题是电路中的噪声增益。有效 输入电阻为全部输入电阻的并联组合。对于大量输入,结 果可能使等效输入电阻变小,从而造成较大的噪声增益。

$$NG = 1 + \frac{Rfb}{R_{IN} \ eq} \tag{5}$$

$$R_{IN} eq = R1 || R2 || ... || RN$$

(6)

然而,出于稳定性考虑,大噪声增益有助于确保放大器的 稳定性。

由于稳定性取决于噪声增益与开环增益的相交位置,因此,较高的噪声增益会使该点远离次级极点,从而导致不稳定。

显然,噪声增益越高,噪声也越高。对于交流输入,会存 在对运算放大器带宽的限制。

以上讨论是以双极性电源为基础的。如果使用单电源,地 将由参考节点取代,后者的典型电压电平为V<sub>REF</sub>,一般相 当于电源电压的一半。在此基础上,输入和输出电压将以 该电压而非地为参考。

# MT-214

输入电流变成

$$IN = \frac{VN - V_{REF}}{RN} \tag{7}$$

其中, N为输入数。结果输出变成

$$V_{REF} - V_{OUT} = \frac{Rfb}{R1} \left( VI - V_{REF} \right) + \left( V2 - V_{REF} \right) + \ldots + \frac{Rfb}{RN} \left( VN - V_{REF} \right)$$

# 参考文献

Zumbahlen, Hank. Linear Circuit Design Handbook. Elsevier. 2008. ISBN: 978-7506-8703-4.

#### 修订历史

2012年4月—修订版0: 初始版

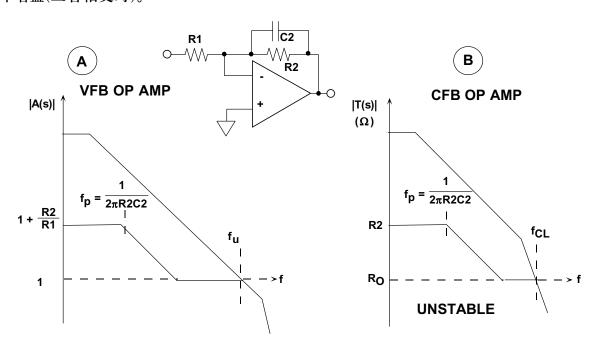

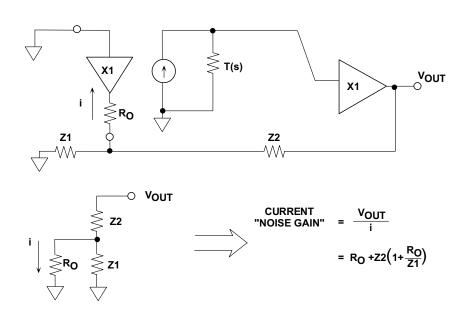

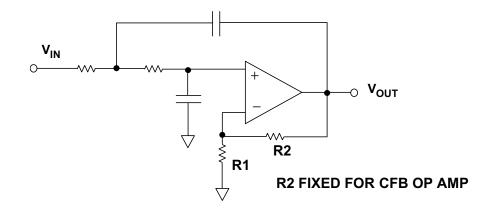

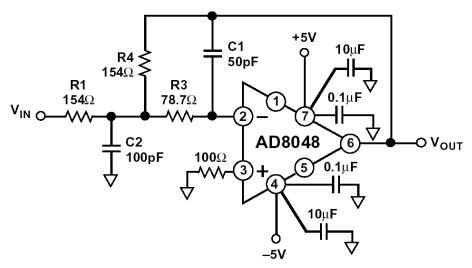

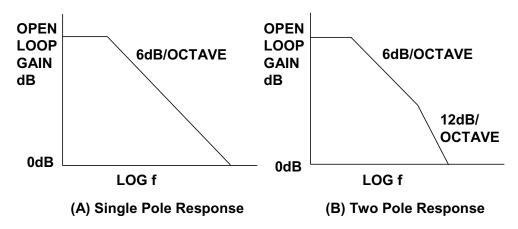

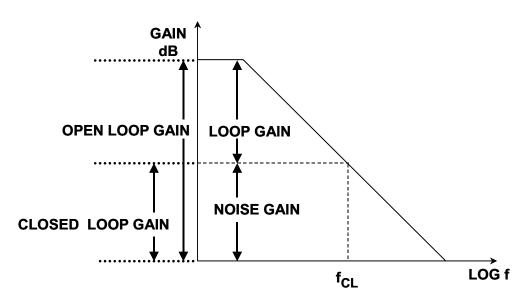

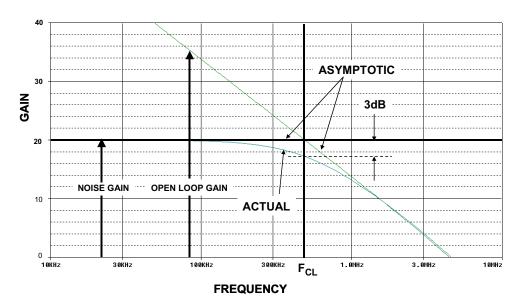

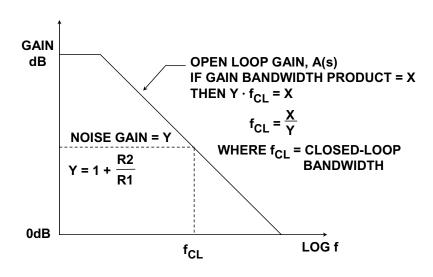

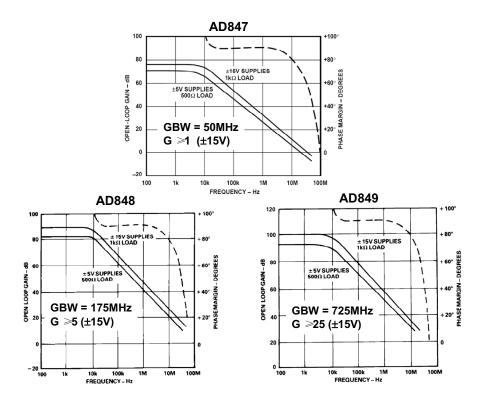

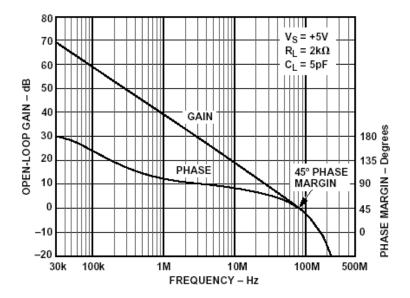

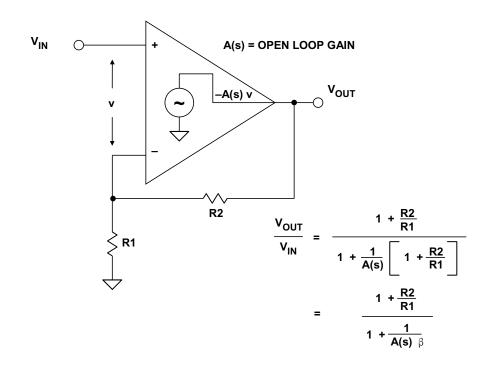

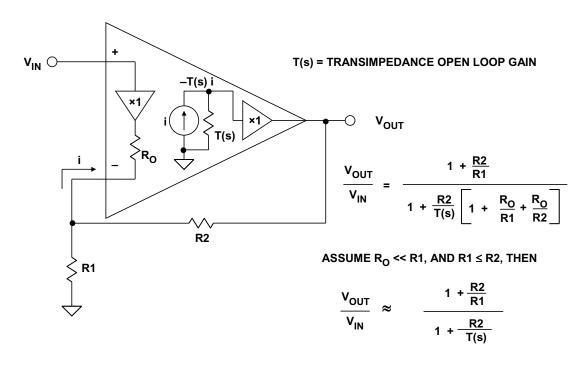

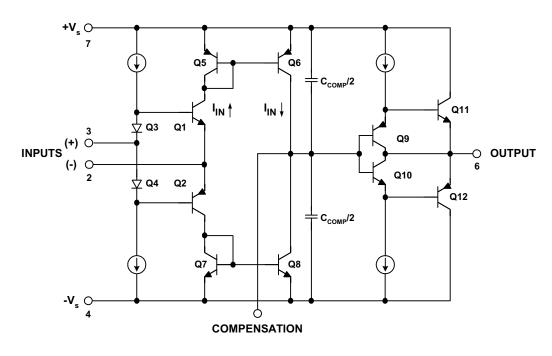

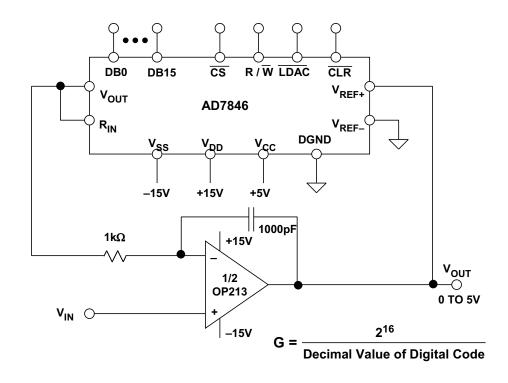

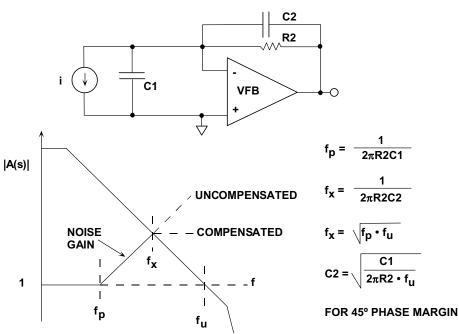

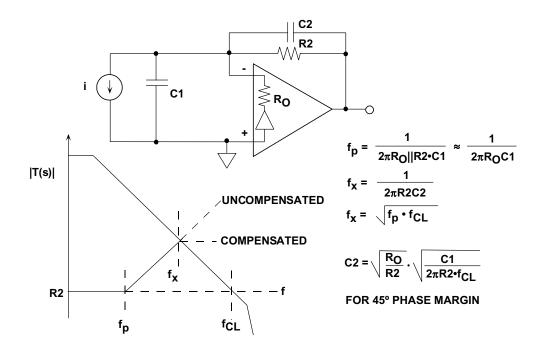

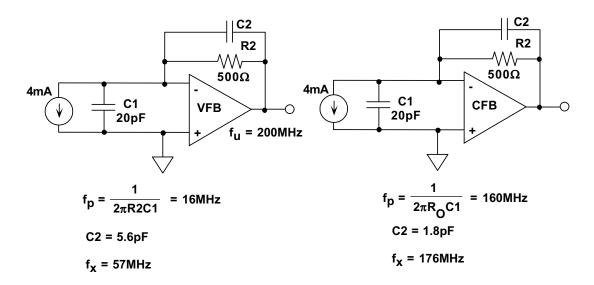

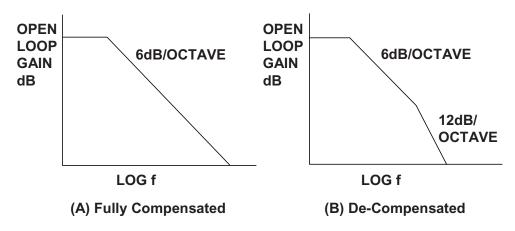

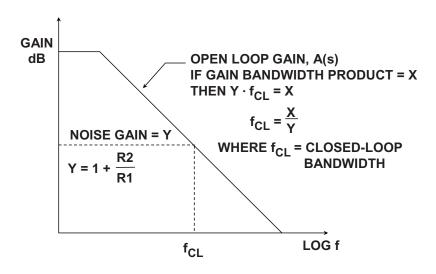

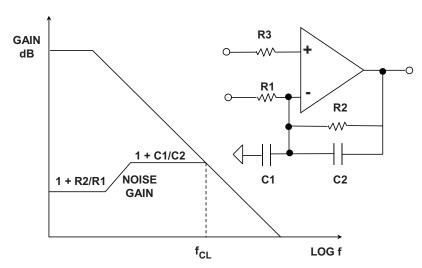

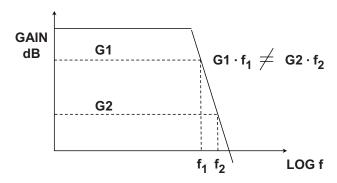

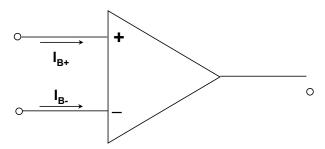

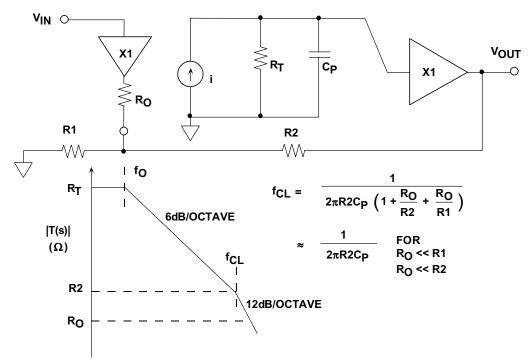

# 反馈电容对VFB和CFB运算放大器的影响

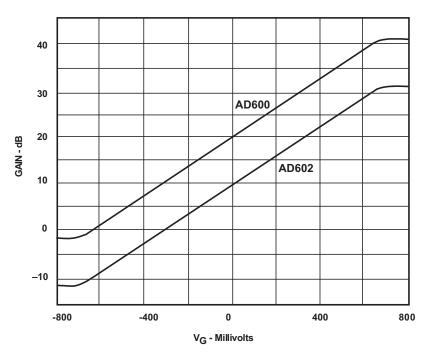

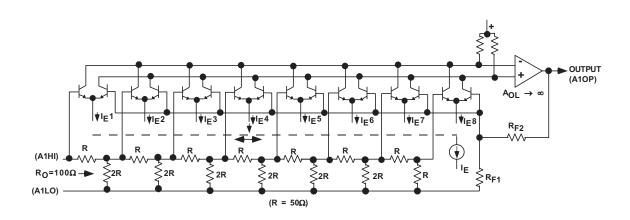

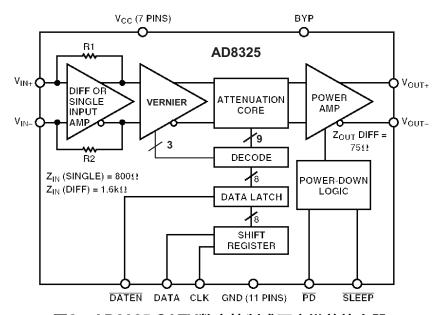

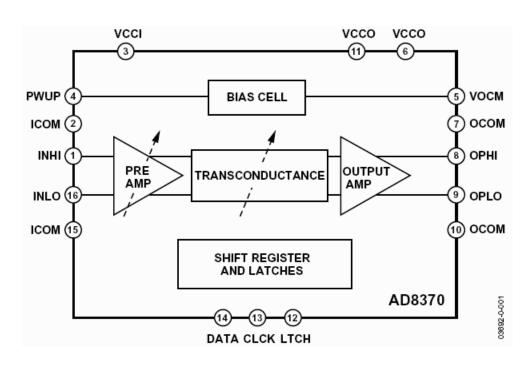

在VFB运算放大器的反馈环路中使用一个电容是非常常见的做法,其目的是影响频率响应,就如在简单的单极点低通滤波器中一样,如下面的图1所示。结果将噪声增益绘制成了一幅波特图,用于分析稳定性和相位裕量。系统的稳定性取决于噪声增益的净斜率以及开环增益(二者相交时)。