# MachXO2 sysCLOCK PLL Design and Usage Guide

May 2014

#### Technical Note TN1199

# Introduction

MachXO2<sup>™</sup> devices support a variety of I/O interfaces such as display interfaces (7:1 LVDS) and memory interfaces (LPDDR, DDR, DDR2). In order to support applications which use these interfaces, the MachXO2 device architecture has been designed to include advanced clocking features that are typically found in higher density FPGAs. These features provide designers the ability to synthesize clocks, minimize clock skew, improve performance and manage power consumption.

This technical note describes the clock resources available in the MachXO2 devices. Details are provided for primary clocks, edge clocks, clock dividers, sysCLOCK<sup>™</sup> PLLs, DCC elements, the secondary high fan-out nets, and the internal oscillator available in the MachXO2 device.

The number of PLLs, edge clocks, and clock dividers for each MachXO2 device are listed in Table 13-1.

| Parameter                   | Description                                 | XO2-<br>256 | XO2-<br>640 | XO2-<br>640U | XO2-<br>1200 | XO2-<br>1200U | XO2-<br>2000 | XO2-<br>2000U | XO2-<br>4000 | XO2-<br>7000 |

|-----------------------------|---------------------------------------------|-------------|-------------|--------------|--------------|---------------|--------------|---------------|--------------|--------------|

| Number of PLLs              | General purpose<br>PLLs                     | 0           | 0           | 1            | 1            | 1             | 1            | 2             | 2            | 2            |

| Number of<br>edge clocks    | Edge clocks for high-<br>speed applications | 0           | 0           | 4            | 4            | 4             | 4            | 4             | 4            | 4            |

| Number of<br>clock dividers | Clock dividers for<br>DDR applications      | 0           | 0           | 4            | 4            | 4             | 4            | 4             | 4            | 4            |

Table 13-1. Number of PLLs, Edge Clocks, and Clock Dividers

# **Clock/Control Distribution Network**

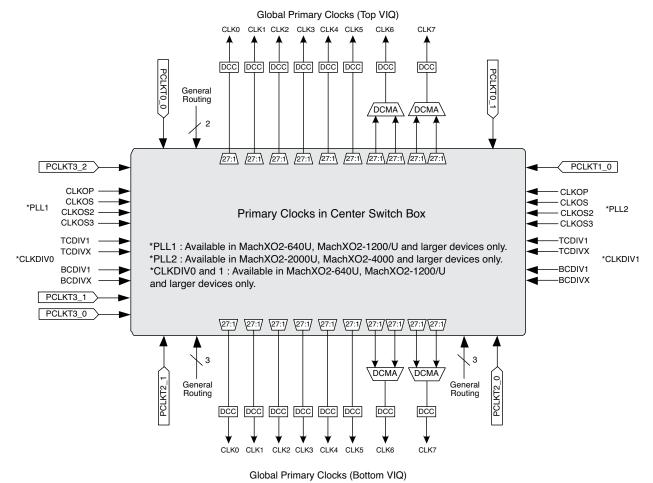

MachXO2 devices provide global clock distribution in the form of eight global primary clocks and eight secondary high fan-out nets. Two edge clocks are provided on the top and bottom sides of the MachXO2-640U, MachXO2-1200/U and higher density devices. Other clock sources include clock input pins, internal nodes, PLLs, clock dividers, and the internal oscillator.

# MachXO2 Top Level View

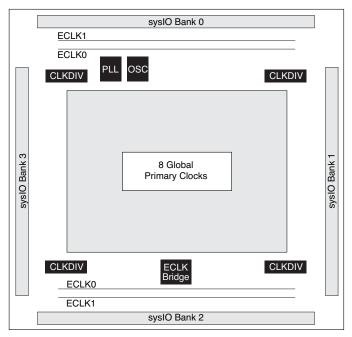

A top level view of the major clocking resources for the MachXO2-1200 device is shown in Figure 13-1.

<sup>© 2014</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

#### Figure 13-1. MachXO2 Clocking Structure (MachXO2-1200)

# **Primary Clocks**

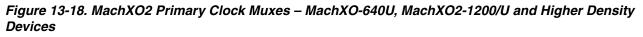

The MachXO2 device has eight global primary clocks. The primary clock networks provide a low skew clock distribution path across the chip for high fan-out signals. Two of the primary clocks are equipped with a Dynamic Clock Mux (DCMA) feature that provides the ability to switch between two different clock sources.

The sources of the primary clocks are:

- Dedicated clock pins

- PLL outputs

- CLKDIV outputs

- Internal nodes

# **Dynamic Clock Mux (DCMA)**

The MachXO2 devices have two Dynamic Clock Muxes (DCMA) that allow a design to dynamically switch between two independent primary clock signals. The output of the DCMA is to the primary clock distribution network. The inputs to the DCMA can be any of the clock sources available to the primary clock network.

The DCMA is a simple clock buffer with a multiplexer function. There is no synchronization of the clock signals when switching occurs so a glitch could occur.

# **DCMA Primitive Definition**

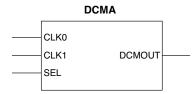

The DCMA primitive can be instantiated in the source code of a design as defined in this section. Figure 13-2 and Table 13-2 show the DCMA definitions.

### Figure 13-2. DCMA Primitive Symbol

#### Table 13-2. DCMA Primitive Port Definition

| Port Name | I/O | Description                                         |

|-----------|-----|-----------------------------------------------------|

| CLK0      | I   | Clock input port zero – this the default            |

| CLK1      | I   | Clock input port one                                |

| SEL       | I   | Select port<br>- SEL=0 for CLK0<br>- SEL=1 for CLK1 |

| DCMOUT    | 0   | Clock output port                                   |

#### DCMA Declaration in VHDL Source Code

#### Library Instantiation

library machxo2; use machxo2.all;

#### **Component Declaration**

```

component DCMA

port CLK0 : in std_logic;

CLK1 : in std_logic;

SEL : in std_logic;

DCMOUT : out std_logic);

end component;

```

#### **DCMA Instantiation**

I1: DCMA

port map (CLK0 => CLK0,

CLK1 => CLK1,

SEL => SEL,

DCMOUT => DCMOUT);

### DCMA Usage with Verilog Source Code

#### **Component Declaration**

module DCMA (CLK0, CLK1, SEL, DCMOUT); input CLK0; input CLK1; input SEL; output DCMOUT; endmodule

#### **DCMA Instantiation**

DCMA I1 (.CLK0 (CLK0), .CLK1 (CLK1), .SEL (SEL), .DCMOUT (DCMOUT));

# **Dynamic Clock Control (DCCA)**

The MachXO2 devices have a dynamic clock control feature that is available for each of the primary clock networks. The Dynamic Clock Control (DCCA) allows each primary clock to be disabled from core logic if desired. Doing so disables a clock and its associated logic in the design when is it not needed and thus saves power.

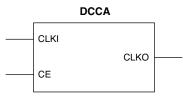

### **DCCA Primitive Definition**

The DCCA primitive can be instantiated in the source code of a design as defined in this section. Figure 13-3 and Table 13-3 show the DCMA definitions.

#### Figure 13-3. DCCA Primitive Symbol

Table 13-3. DCCA Primitive Port Definition

| Port Name | I/O | Description                                                    |

|-----------|-----|----------------------------------------------------------------|

| CLKI      | I   | Clock input port                                               |

| CE        | I   | Clock enable port<br>- CE = 0 – disabled<br>- CE = 1 – enabled |

| CLKO      | 0   | Clock output port                                              |

# DCCA Declaration in VHDL Source Code Library Instantiation

```

library machxo2;

use machxo2.all;

```

#### **Component Declaration**

component DCCA

port(CLKI : in std\_logic;

CE : in std\_logic;

CLKO : out std\_logic);

end component;

#### **DCCA** Instantiation

# DCCA Usage with Verilog Source Code

#### **Component Declaration**

module DCCA (CLKI, CE, CLKO); input CLKI; input CE;

output CLKO;

endmodule

#### **DCCA** Instantiation

DCCA I1 (.CLKI (CLKI), .CE (CE), .CLKO (CLKO));

# **Edge Clocks**

There are two edge clock resources on the top and bottom sides of the MachXO2-640U, MachXO2-1200/U and higher density devices. These clocks, which have low injection time and skew, are used to clock I/O registers. Edge clock resources are designed for high-speed I/O interfaces with high fan-out capability. Refer to Appendix B for detailed information on the ECLK locations and connectivity.

The sources of edge clocks are:

- Dedicated clock pins

- PLL outputs

- Internal nodes

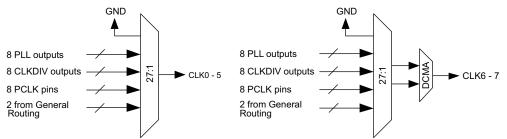

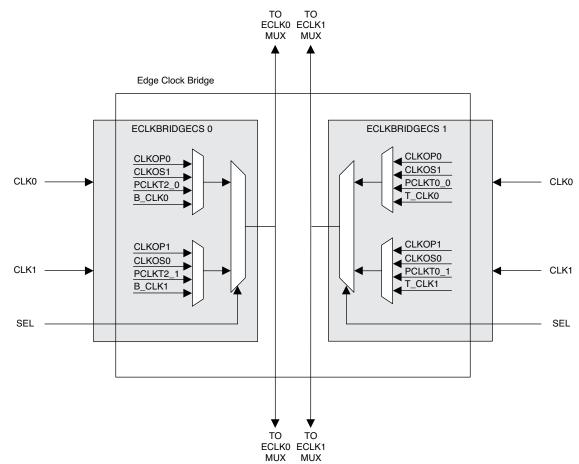

# Edge Clock Bridge

The MachXO2-640U, MachXO2-1200/U and higher density devices also have an edge clock bridge that is used to enhance communication of ECLKs across the device. The bridge allows an input on the bottom of the device to drive the edge clock on the top edge of the device with minimal skew. Edge clock sources can either go through the edge clock bridge to connect to the edge clock or can be directly connected using the shortest path.

The Edge Clock Bridge is primarily intended for use with high-speed data interfaces such as DDR or 7:1 LVDS Video. For more information on the use of the Edge Clock Bridge please see TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

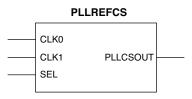

In the edge clock bridge there is a clock select mux that allows a design to switch between two different clock sources for each edge clock. This clock select mux is modeled using the ECLKBRIDGECS primitive. A block diagram of the edge clock bridge is shown in Appendix B.

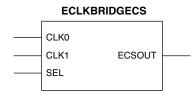

# **ECLKBRIDGECS** Primitive Definition

The ECLKBRIDGECS primitive can be instantiated in the source code of a design as defined in this section. A design can have up to two instantiations of ECLKBRIDGECS primitives if desired. Figure 13-4 and Table 13-4 show the ECLKBRIDGECS definitions.

#### Figure 13-4. ECLKBRIDGECS Primitive Symbol

#### Table 13-4. ECLKBRIDGECS Primitive Port Definition

| Port Name | I/O | Description                                           |

|-----------|-----|-------------------------------------------------------|

| CLK0      | I   | Clock Input port zero – this the default.             |

| CLK1      | I   | Clock Input port one                                  |

| SEL       | I   | Select port<br>- SEL = 0 for CLK0<br>- SEL=1 for CLK1 |

| ECSOUT    | 0   | Clock output port                                     |

### ECLKBRIDGECS Declaration in VHDL Source Code

#### **Library Instantiation**

library machxo2; use machxo2.all;

#### **Component Declaration**

component ECLKBRIDGECS

port ( CLK0 : in std\_logic;

CLK1 : in std\_logic;

SEL : in std\_logic;

ECSOUT : out std\_logic);

end component;

#### **ECLKBRIDGECS** Instantiation

### ECLKBRIDGECS Usage with Verilog Source Code

#### **Component Declaration**

```

module ECLKBRIDGECS (CLK0, CLK1, SEL, ECSOUT);

input CLK0;

```

input CLK1; input SEL; output ECSOUT;

endmodule

#### **ECLKBRIDGECS** Instantiation

| ECLKBRIDGECS | I1 | ( | .CLK0  | (CLK0),       |

|--------------|----|---|--------|---------------|

|              |    |   | .CLK1  | (CLK1),       |

|              |    |   | .SEL   | (SEL),        |

|              |    |   | .ECSOU | JT (ECSOUT)); |

# Edge Clock Synchronization (ECLKSYNCA)

MachXO2-640U, MachXO2-1200/U and higher density devices also have a dynamic edge clock synchronization control (ECLKSYNCA). This feature allows each edge clock to be disabled from core logic if desired. Designers can use this feature to synchronize the edge clock to an event or external signal if desired. Designers can also use this feature to design applications in which a clock and its associated logic can be dynamically disabled to save power. For the "R1" version of the MachXO2 devices ECLKSYNC may have a glitch in the output under certain conditions, leading to possible loss of synchronization. The "R1" versions of the MachXO2 devices have an "R1" suffix at the end of the part number (e.g., LCMXO2-1200ZE-1TG144CR1). For more details on the R1 to Standard migration refer to AN8086, Designing for Migration from MachXO2-1200-R1 to Standard (Non-R1) Devices.

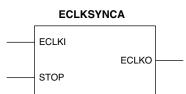

# **ECLKSYNCA** Primitive Definition

The ECLKSYNCA primitive can be instantiated in the source code of a design as defined in this section. Figure 13-5 and Table 13-3 show the ECLKSYNCA definitions.

#### Figure 13-5. ECLKSYNCA Primitive Symbol

Table 13-5. ECLKSYNCA Primitive Port Definition

| Port Name | I/O | Description                                                                            |

|-----------|-----|----------------------------------------------------------------------------------------|

| ECLKI     | I   | Clock input port                                                                       |

| STOP      | I   | Control signal to stop edge clock<br>- STOP=0 Clock is active<br>- STOP=1 Clock is off |

| ECLKO     | 0   | Clock output port                                                                      |

# ECLKSYNCA Declaration in VHDL Source Code

#### Library Instantiation

library machxo2; use machxo2.all;

#### **Component Declaration**

```

component ECLKSYNCA

port ( ECLKI :in std_logic;

STOP :in std_logic;

ECLKO :out std_logic);

end component;

```

#### **ECLKSYNCA** Instantiation

I1: ECLKSYNCA

port map ( ECLKI => ECLKI,

STOP => STOP,

ECLKO => ECLKO);

### ECLKSYNCA Usage with Verilog Source Code

#### **Component Declaration**

module ECLKSYNCA (ECLKI, STOP, ECLKO);

input ECLKI; input STOP; output ECLKO;

endmodule

#### **ECLKSYNCA** Instantiation

ECLKSYNCA I1 (.ECLKI (ECLKI), .STOP (STOP), .ECLKO (ECLKO));

# Secondary High Fan-out Nets

MachXO2 devices have eight secondary high fan-out nets that can be used for clock, control, or high fan-out data signals. These secondary nets are a flexible global clocking resource with low injection delay and lower skew than the general routing resources. The secondary nets are primarily for global high fan-out control signals such as Clock Enables (CE), Local Set/Reset (LSR), and Reset (RST) applications. The eight secondary nets can have four independent control or clock inputs and four independent data inputs.

The sources of the secondary nets are:

- Dedicated clock pins

- Internal nodes

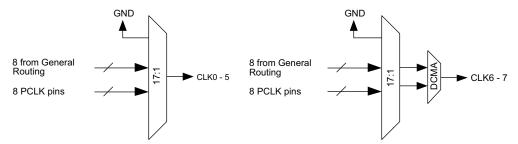

# Clock Dividers (CLKDIVC)

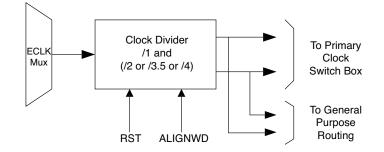

There are four clock dividers available in the MachXO2-640U, MachXO2-1200/U and higher density devices. The MachXO2-256 and MachXO2-640 devices do not have clock dividers. The clock divider provides two outputs. One is the same frequency as the input clock and the other is the input clock divided by either 2, 3.5, or 4. Both of the outputs have matched input-to-output delay. The input to the clock divider is the output from the edge clock mux. The outputs of the clock divider drive the primary clock network and are also available for general purpose routing or secondary clocks.

A block diagram of the clock divider is shown in Figure 13-6.

#### Figure 13-6. MachXO2 Clock Divider

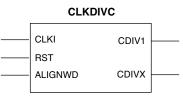

# **CLKDIVC** Primitive Definition

The CLKDIVC primitive can be instantiated in the source code of a design as defined in this section. Figure 13-7 and Tables 13-6 and 13-7 show the CLKDIVC definitions.

Figure 13-7. CLKDIVC Primitive Symbol

Table 13-6. CLKDIVC Primitive Port Definition

| Port Name | I/O | Description                                                                                                                                                       |

|-----------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI      | I   | Clock input                                                                                                                                                       |

| RST       | I   | Reset input - asynchronously forces all outputs low<br>- RST = 0 Clock output outputs are active<br>- RST = 1 Clock output outputs are OFF                        |

| ALIGNWD   | I   | Signal is used for word alignment.<br>- ALIGNWD = 0 when not used<br>See TN1203, Implementing High-Speed Interfaces with MachXO2<br>Devices for more information. |

| CDIV1     | 0   | Divide by 1 output port. When RST = 1 CDIV1 output does not tog-<br>gle and stays either L or H                                                                   |

| CDIVX     | 0   | Divide by 2, 3.5 or 4 output port                                                                                                                                 |

Table 13-7. CLKDIVC Primitive Attribute Definition

| Name | Description | Value             | Default  |

|------|-------------|-------------------|----------|

| GSR  | GSR Enable  | ENABLED, DISABLED | DISABLED |

| DIV  | CLK Divider | 2.0, 3.5 or 4.0   | 2.0      |

The ALIGNWD input is intended for use with high-speed data interfaces such as DDR or 7:1 LVDS video. For more information on the use of ALIGNWD please see TN1203, Implementing High-Speed Interfaces with MachXO2 Devices.

### **CLKDIVC Declaration in VHDL Source Code**

#### Library Instantiation

```

library machxo2;

use machxo2.all;

```

#### **Component and Attribute Declaration**

```

component CLKDIVC

generic (DIV : string;

GSR : string);

port (RST : in std_logic;

CLKI : in std_logic;

ALIGNWD : in std_logic;

CDIV1 : out std_logic;

CDIVX : out std_logic);

end component;

```

#### **CLKDIVC** Instantiation

### **CLKDIVC Usage with Verilog Source Code**

### **Component and Attribute Declaration**

```

module CLKDIVC (RST, CLKI, ALIGNWD, CDIV1, CDIVX);

parameter DIV = "2.0"; // "2.0", "3.5", "4.0"

parameter GSR = "DISABLED"; // "ENABLED", "DISABLED"

input RST;

input CLKI;

input ALIGNWD;

output CDIV1;

output CDIVX;

```

endmodule

### **CLKDIVC Instantiation**

```

defparam I1.DIV = "2.0";

defparam I1.GSR = "DISABLED";

CLKDIVC I1 ( .RST (RST),

.CLKI(CLKI),

.ALIGNWD (ALIGNWD),

.CDIV1 (CDIV1),

.CDIVX (CDIVX));

```

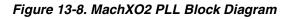

# sysCLOCK PLL

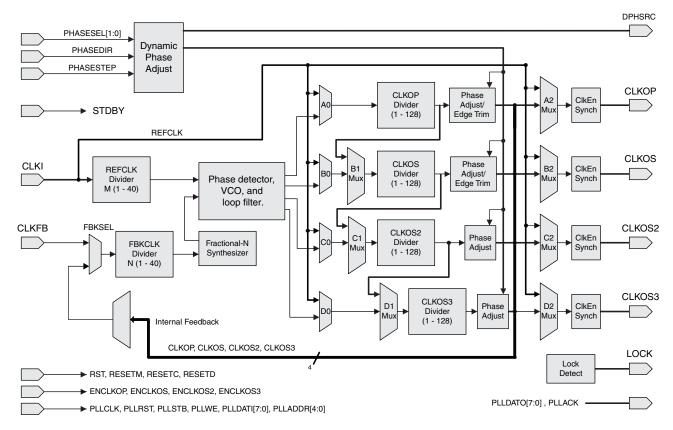

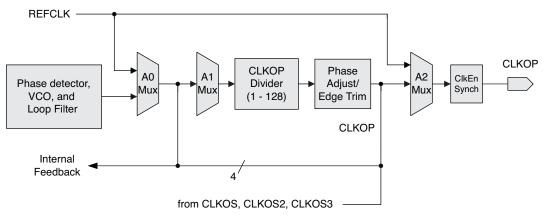

The MachXO2 PLL provides features such as clock injection delay removal, frequency synthesis, and phase adjustment. The MachXO2-640U, MachXO2-1200/U devices have one PLL, the larger devices MachXO2-2000U, MachXO2-4000 and MachXO2-7000 have two PLLs. Please note that for devices that have two PLLs, if using background FLASH configuration care must be taken for the use of the Right side PLL. Please see TN1204, MachXO2 Programming and Configuration Usage Guide for detailed description. Figure 13-8 shows a block diagram of the MachXO2 PLL.

# **Functional Description**

### PLL Divider Blocks

**Input Clock (CLKI) Divider**: The CLKI divider is used to control the input clock frequency into the PLL block. The divider setting directly corresponds to the divisor of the output clock. The input must be within the input frequency range specified in the MachXO2 Family Data Sheet. The output of the input divider must also be within the phase detector frequency range specified in the data sheet.

**Feedback Loop (CLKFB) Divider**: The CLKFB divider is used to divide the feedback signal. Effectively, this multiplies the output clock because the divided feedback must speed up to match the input frequency into the PLL block. The PLL block increases the output frequency until the divided feedback frequency equals the input frequency. The output of the feedback divider must be within the phase detector frequency range specified in the MachXO2 Family Data Sheet.

**Output Clock Dividers (CLKOP, CLKOS, CLKOS2, CLKOS3)**: The output clock dividers allow the VCO frequency to be scaled up to the 400-800 MHz range which minimizes jitter. Each of the output dividers is independent of the other dividers and each uses the VCO as the source by default. Each of the output dividers can be set to a value of 1 to 128. The CLKOS, CLKOS2 and CLKOS3 dividers can be cascaded together to produce a lower frequency output if desired.

**Phase Adjustment (Static Mode)**: The CLKOP, CLKOS, CLKOS2, and CLKOS3 outputs can be phase adjusted relative to the input clock. The phase adjustments can be done in 45° steps. The clock output selected as the feedback cannot use the static phase adjustment feature.

**Phase Adjustment (Dynamic Mode)**: The phase adjustments can also be controlled in a dynamic mode using the PHASESEL, PHASEDIR, and PHASESTEP ports. The clock output selected as the feedback cannot use the dynamic phase adjustment feature. Please see the Dynamic Phase Adjustment section of this document for more details.

Edge Trim Adjustment (Static Mode): The CLKOP and CLKOS ports can be finely tuned with an edge trim adjustment feature.

# **PLL Features**

#### Standby Mode

The MachXO2 PLL contains a Standby mode that allows the PLL to be placed into a standby state to save power when not needed in the design. The PLL can be powered down completely or just partially depending on the needs of the design.

#### Fractional-N synthesis

The MachXO2 PLL contains a fractional-N synthesis feature which allows the user to generate an output clock which is a non-integer multiple of the input frequency. The user is allowed to enter a value between 0 and 65535 for the fractional-N divider. This value is then divided by 65536 and the result is added to the feedback divider. A MASH Delta-Sigma modulation technique is used such that the average effective feedback divide value is equal to this value. Fractional-N synthesis can be used to create a closer PPM match to the target frequency.

#### **WISHBONE** Ports

The MachXO2 PLL contains a WISHBONE port feature which allows the PLL settings to be dynamically changed from the user logic. When using this feature the EFB block must also be instantiated in the design to allow access to the WISHBONE ports. The WISHBONE ports of the PLL must be connected to the WISHBONE ports of the EFB block for proper simulation and operation. The use of the WISHBONE ports is described in detail in Appendix D.

### PLL Inputs and Outputs

#### CLKI Input

The CLKI signal is the reference clock for the PLL. It must conform to the specifications in the data sheet in order for the PLL to operate correctly. The CLKI signal can come from a dedicated dual-purpose I/O pin, from any I/O pin, or from routing. The dedicated dual-purpose I/O pin provides a low skew input path and is the recommended source for the PLL. The reference clock will be divided by the input (M) divider to create one input to the phase detector of the PLL. The dedicated GPLL pins and PCLK pins located on the top and bottom sides provide direct connection to the PLL input. The PCLK pins located on the left and right sides use primary clock routing to connect to the PLL input pin.

#### **CLKFB** Input

The CLKFB signal is the feedback signal to the PLL. The feedback signal is used by the PLL to determine if the output clock needs adjustment to maintain the correct frequency, phase, or other characteristic. The CLKFB signal can come from the primary clock net, from a dedicated dual-purpose I/O pin, directly from an output clock divider, or from routing. By using external feedback designers can compensate for board-level clock alignment. The feedback clock signal will be divided by the feedback (N) divider to create an input to the phase detector of the PLL. A bypassed PLL output cannot be used as the feedback signal.

#### **RST Input**

The PLL reset occurs under two conditions. At power-up an internal power-up reset signal from the configuration block resets the PLL. The user-controlled PLL reset signal RST can be provided as a part of the PLL module. The RST signal can be driven by an internally-generated reset function or by an I/O pin. This RST signal resets the PLL core (VCO, phase detector, and charge pump) and the output dividers which causes the outputs to be grounded, even in bypass mode.

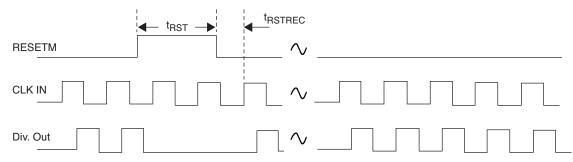

After the RST signal is de-asserted the PLL will start the lock-in process and will take t<sub>LOCK</sub> time to complete the PLL LOCK. Figure 13-9 shows the timing diagram of the RST input. The RST signal is active high. The RST signal is optional.

The RST input does NOT reset the input divider (M-divider). The reason for not resetting the M-divider is that there may be a clock used externally that is a synchronized to the reference clock. In this case there is a state relationship between the external clock and the M-divided clock (which the PLL is synchronized to). This relationship needs to be preserved by the user when resetting the PLL. In this condition, RST will be used to reset the PLL without resetting the M-divider.

#### **RESETM Input**

The user-controlled PLL reset signal RESETM can be provided as a part of the PLL module. The RESETM signal can be driven by an internally-generated reset function or by an I/O pin. The RESETM signal resets the PLL core (similar to RST) and the all the dividers, including the M-divider. This causes the outputs to be grounded, including when the PLL is in bypass mode.

After the RESETM signal is de-asserted the PLL will start the lock-in process and will take t<sub>LOCK</sub> time to complete the PLL LOCK. Figure 13-9 shows the timing diagram of the RESETM input. The RESETM signal is active high. The RESETM signal is optional.

If the user wishes to synchronize the PLL output to an external clock source the RESETM signal can be used to reset the PLL.

#### Figure 13-9. RST and RESETM Timing Diagram

#### **RESETC Input**

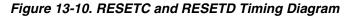

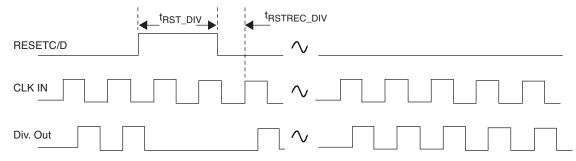

The user-controlled PLL reset signal RESETC can be provided as a part of the PLL module. The RESETC signal can be driven by an internally-generated reset function or by an I/O pin. This RESETC signal resets only the CLKOS2 output divider. This causes the CLKOS2 output to be grounded unless the output is in the bypass mode. If this output is in bypass mode as a clock divider it will be reset by the RESETC signal. The RESETC signal can be used to synchronize the CLKOS2 output to an external clock signal.

After the RESETC signal is de-asserted there is a time delay of t<sub>RSTREC\_DIV</sub> time before the next clock edge will toggle the CLKOS2 output divider. Figure 13-10 shows the timing diagram of the RESETC input. The RESETC signal will not affect the PLL loop unless the CLKOS2 output is used in the feedback path. If the CLKOS2 output is used in the feedback path it is recommended to use the RST or RESETM signal to reset the PLL rather than RESETC. The RESETC signal is active high. The RESETC signal is optional.

#### **RESETD** Input

The user-controlled PLL reset signal RESETD can be provided as a part of the PLL module. The RESETD signal can be driven by an internally-generated reset function or by an I/O pin. This RESETD signal resets only the CLKOS3 output divider. This causes the CLKOS3 output to be grounded unless the output is in the bypass mode. If this output is in bypass mode as a clock divider it will be reset by the RESETD signal. The RESETD signal can be used to synchronize the CLKOS3 output to an external clock signal.

After the RESETD signal is de-asserted there is a time delay of t<sub>RSTREC\_DIV</sub> time before the next clock edge will toggle the CLKOS3 output divider. Figure 13-10 shows the timing diagram of the RESETD input. The RESETD signal will not affect the PLL loop unless the CLKOS3 output is used in the feedback path. If the CLKOS3 output is used in the feedback path it is recommended to use the RST or RESETM signal to reset the PLL rather than RESETD. The RESETD signal is active high. The RESETD signal is optional.

#### ENCLKOP Input

The ENCLKOP signal is used to enable and disable the CLKOP output from a user signal. This enables designers to save power by stopping the CLKOP output when it is not used. Additionally this signal also allows the designer to synchronize CLKOP with another signal in the design. The ENCLKOP signal is optional and will only be available if the user has selected the clock enable ports option in IPexpress<sup>™</sup>. If the ENCLKOP signal is not requested the CLKOP output will be active at all times (when the PLL is instantiated) unless the PLL is placed into the standby mode. The ENCLKOP signal is active high.

#### ENCLKOS Input

The ENCLKOS signal is used to enable and disable the CLKOS output from a user signal. This enables designers to save power by stopping the CLKOS output when it is not used. Additionally this signal also allows the designer to synchronize CLKOS with another signal in the design. The ENCLKOS signal is optional and will only be available when the PLL is configured with the CLKOS output and the Clock Enable ports options in IPexpress. If the PLL is configured with the CLKOS output enabled and the ENCLKOS signal is not requested the CLKOS output will always be active unless the PLL is placed into the standby mode. The ENCLKOS signal is active high.

#### ENCLKOS2 Input

The ENCLKOS2 signal is used to enable and disable the CLKOS2 output from a user signal. This enables designers to save power by stopping the CLKOS2 output when it is not used. Additionally this signal also allows the designer to synchronize CLKOS2 with another signal in the design. The ENCLKOS2 signal is optional and will only be available when the PLL is configured with the CLKOS2 output and the Clock Enable ports options in IPexpress. If the PLL is configured with the CLKOS2 output enabled and the ENCLKOS2 signal is not requested the CLKOS2 output will always be active unless the PLL is placed into the standby mode. The ENCLKOS2 signal is active high.

#### ENCLKOS3 Input

The ENCLKOS3 signal is used to enable and disable the CLKOS2 output from a user signal. This enables designers to save power by stopping the CLKOS3 output when it is not used. Additionally this signal also allows the designer to synchronize CLKOS3 with another signal in the design. The ENCLKOS3 signal is optional and will only be available when the PLL is configured with the CLKOS3 output and the Clock Enable ports options in IPexpress. If the ENCLKOS3 signal is not requested the CLKOS3 output will always be active unless the PLL is placed into the standby mode. The ENCLKOS3 signal is active high.

#### STDBY Input

The STDBY signal is used to put the PLL into a low power standby mode when it is not required. The STDBY port can be connected to the power controller so that the PLL will enter the low power state when device is driven to the Standby mode. Alternatively the STDBY port can be driven by user logic independent of the standby mode. The STDBY signal is optional and will only be available if the user has selected the Standby ports option in IPexpress. The STDBY signal is active high.

#### PHASESEL Input

The PHASESEL[1:0] input is used to specify which PLL output port will be affected by the dynamic phase adjustment ports. The settings available are shown in the Dynamic Phase Adjustment section of this document. The PHASESEL signal must be stable before the PHASESTEP signal is toggled. The PHASESEL signal is optional and will only be available if the user has selected the Dynamic Phase ports option in IPexpress.

#### PHASEDIR Input

The PHASEDIR input is used to specify which direction the dynamic phase shift will occur, advanced (leading) or delayed (lagging). When PHASEDIR = 0 then the phase shift will be delayed from the current clock by one step. When PHASEDIR = 1 then the phase shift will be advanced from the current clock by one step. The PHASEDIR signal must be stable before the PHASESTEP signal is toggled.

The PHASEDIR signal is optional and will only be available if the user has selected the Dynamic Phase ports option in IPexpress.

#### PHASESTEP Input

The PHASESTEP signal is used to initiate the dynamic phase adjustment for the clock output port and in the direction specified by the PHASESEL and PHASEDIR inputs respectively. The PHASESTEP signal is optional and will only be available if the user has selected the Dynamic Phase ports option in IPexpress.

#### **CLKOP** Output

CLKOP is the main clock output of the sysCLOCK PLL. This signal is always available by default and can be routed to the primary clock network of the chip. The CLKOP output can also be routed to top/bottom edge clocks. The CLKOP output can be phase-shifted either statically or dynamically and can also be used with the duty trim adjustment feature. The CLKOP signal output can either come from the CLKOP output divider or can bypass the PLL. When CLKOP is in the bypass mode the output divider can either be bypassed or used in the circuit.

#### CLKOS Output

The secondary clock output of the sysCLOCK PLL is the CLKOS signal. This signal is available when selected by the user and can be routed to the primary clock network of the device. The CLKOS output can also be routed to top and bottom edge clocks. The CLKOS output can be phase-shifted either statically or dynamically and can also be used with the duty trim adjustment feature. The CLKOS signal output can either come from the CLKOS output divider or can bypass the PLL. When CLKOS is in the bypass mode the output divider can either be bypassed or used in the circuit. The CLKOS signal is optional.

The CLKOS output also supports lower frequency outputs that require an output divider value greater than 128. This is accomplished by cascading the CLKOP and CLKOS output dividers. When used in this application, the CLKOP output cannot be used as an independent clock output. A cascaded clock output cannot be used for the feedback signal of the PLL.

#### CLKOS2 Output

The CLKOS2 signal is another secondary clock output that is available in the sysCLOCK PLL. This signal is available when selected by the user and can be routed to the primary clock network of the chip. The CLKOS2 output cannot be routed to top and bottom edge clocks. The CLKOS2 output can be phase-shifted either statically or dynamically but does not have the duty trim adjustment feature. The CLKOS2 signal output can either come from the CLKOS2 output divider or can bypass the PLL. When CLKOS2 is in the bypass mode the output divider can either be bypassed or used in the circuit. The CLKOS2 signal is optional.

The CLKOS2 output also supports lower frequency outputs that require an output divider value greater than 128. This is accomplished by cascading the CLKOS and CLKOS2 output dividers. When used in this application, the CLKOS output cannot be used as an independent clock output. A cascaded clock output cannot be used for the feedback signal of the PLL.

#### CLKOS3 Output

The CLKOS3 signal is another secondary clock output that is available in the sysCLOCK PLL. This signal is available when selected by the user and can be routed to the primary clock network of the chip. The CLKOS3 output cannot be routed to top/bottom edge clocks. The CLKOS3 output can be phase-shifted either statically or dynamically but does not have the duty trim adjustment feature. The CLKOS3 signal output can either come from the CLKOS3 output divider or can bypass the PLL. When CLKOS3 is in the bypass mode the output divider can either be bypassed or used in the circuit. The CLKOS3 signal is optional.

The CLKOS3 output also supports lower frequency outputs that require an output divider value larger than 128. This is accomplished by cascading the CLKOS2 and CLKOS3 output dividers. When used in this application the CLKOS2 output cannot be used as an independent clock output. A cascaded clock output cannot be used for the feedback signal of the PLL.

#### DPHSRC Output

The DPHSRC output is used to indicate whether the dynamic phase ports or the WISHBONE registers are being used for control of the dynamic phase adjustment feature. The dynamic phase ports are the PHASESEL, PHASE-DIR, and PHASESTEP ports. The DPHSRC signal is optional and will be available if the user has selected the Dynamic Phase ports option in IPexpress. If the user has not selected the Dynamic Phase ports option the WISH-BONE registers will be used to set the dynamic phase adjustment feature by default.

#### LOCK Output

The LOCK output provides information about the status of the PLL. After the device is powered up and the input clock is valid, the PLL will achieve lock within the specified lock time. Once lock is achieved, the PLL LOCK signal will be asserted. The LOCK can either be in the Normal Lock mode or the Sticky Lock mode. In the Normal Lock mode, the LOCK signal is asserted when the PLL determines it has achieved lock and de-asserted if a loss of lock is detected. In Sticky Lock mode, once the LOCK signal is asserted or until the PLL is powered down. It is recommended to assert PLL RST to re-synchronize the PLL to the reference clock when the PLL loses lock. The LOCK signal is available to the FPGA routing to implement the generation of the RST signal if requested by the designer. The LOCK signal is optional and will be available if the user has selected the Provide PLL Lock signal option in IPexpress.

For the "R1" version of the MachXO2 devices, the PLL Lock signal will glitch high when coming out of standby. This glitch lasts for about 10µsec before returning low. The "R1" versions of the MachXO2 devices have an "R1" suffix at the end of the part number (e.g., LCMXO2-1200ZE-1TG144CR1). For more details on the R1 to Standard migration, refer to AN8086, Designing for Migration from MachXO2-1200-R1 to Standard (Non-R1) Devices.

#### WISHBONE Ports

The WISHBONE parts are listed in Appendix D along with the description of how to use them. The WISHBONE ports are optional.

# **PLL Attributes**

The PLL utilizes several attributes that allow the configuration of the PLL through source constraints and a preference file. The following section details these attributes and their usage.

### FIN

The input frequency can be any value within the specified frequency range based upon the divider settings.

#### CLKI\_DIV, CLKFB\_DIV, CLKOP\_DIV, CLKOS\_DIV, CLKOS2\_DIV, CLKOS3\_DIV

These dividers determine the output frequencies of each of the output clocks. The user is not allowed to input an invalid combination when using IPexpress. Valid combinations are determined by the input frequency, the dividers, and the PLL specifications.

The CLKOP\_DIV value is calculated to maximize the FVCO within the specified range based upon the FIN and CLKOP\_FREQ in conjunction with the CLKI\_DIV and CLKFB\_DIV values. This applies when the CLKOP output is used for the feedback signal. If another output is used for the feedback signal then the corresponding output divider shall be calculated in this manner.

The output signals that are not used for the feedback signal will use an output divider value based upon the VCO frequency and desired output frequency. The possible divider values for all these dividers are 1 to 128, though in some cases the full range is not allowed since it would violate the PLL specifications.

# FREQUENCY\_PIN\_CLKI, FREQUENCY\_PIN\_CLKOP, FREQUENCY\_PIN\_CLKOS, FREQUENCY PIN CLOS2, FREQUENCY PIN CLKOS3

These input and output clock frequencies determine the divider values.

#### Frequency Tolerance – CLKOP, CLKOS, CLKOS2, CLKOS3

When the desired output frequency is not achievable, users may enter the frequency tolerance of the clock output.

# MachXO2 PLL Primitive Definition

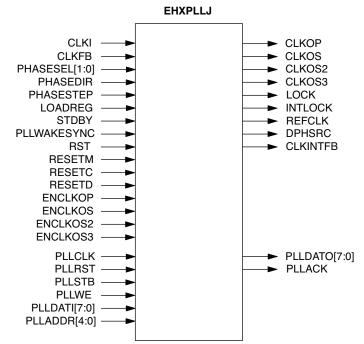

The PLL primitive can be instantiated in the source code of a design as defined in this section. Figure 13-11 and Table 13-8 show the EHXPLLJ definitions.

#### Figure 13-11. PLL Primitive Symbol

#### Table 13-8. PLL Primitive Port Definition

| Port Name     | I/O | Description                                                                                                       |

|---------------|-----|-------------------------------------------------------------------------------------------------------------------|

| CLKI          | I   | Input clock to PLL                                                                                                |

| CLKFB         | I   | Feedback clock                                                                                                    |

| PHASESEL[1:0] | I   | Select which output is affected by Dynamic Phase adjustment ports                                                 |

| PHASEDIR      | I   | Dynamic Phase adjustment direction.                                                                               |

| PHASESTEP     | I   | Dynamic Phase step – toggle shifts VCO phase adjust by one step                                                   |

| LOADREG       | I   | Dynamic Phase Load – toggle loads divider phase adjustment values into PLL                                        |

| CLKOP         | 0   | Primary PLL output clock (with phase shift adjustment)                                                            |

| CLKOS         | 0   | Secondary PLL output clock (with phase shift adjust)                                                              |

| CLKOS2        | 0   | Secondary PLL output clock2 (with phase shift adjust)                                                             |

| CLKOS3        | 0   | Secondary PLL output clock3 (with phase shift adjust)                                                             |

| LOCK          | 0   | PLL LOCK, asynchronous signal. Active high indicates PLL is locked to input and feedback signals.                 |

| INTLOCK       | 0   | PLL internal LOCK, asynchronous signal. Active high indicates PLL lock using internal feed-<br>back. <sup>1</sup> |

| REFCLK        | 0   | Output of reference clock mux                                                                                     |

| DPHSRC        | 0   | Dynamic phase source – ports or WISHBONE is active                                                                |

| STDBY         | I   | Standby signal to power down the PLL                                                                              |

| PLLWAKESYNC   | I   | PLL wake-up sync. Enable PLL to switch from internal to user feedback path when the PLL wakes up. <sup>1</sup>    |

| RST           | I   | PLL Reset without resetting the M-divider. Active high reset.                                                     |

| RESETM        | I   | PLL Reset - includes resetting the M-divider. Active high reset.                                                  |

| Port Name     | I/O | Description                                                                |

|---------------|-----|----------------------------------------------------------------------------|

| RESETC        | I   | Reset for CLKOS2 output divider only. Active high reset.                   |

| RESETD        | I   | Reset for CLKOS3 output divider only. Active high reset.                   |

| ENCLKOP       | I   | Clock Enable for CLKOP output                                              |

| ENCLKOS       | I   | Clock Enable for CLKOS output - only available if CLKOS port is active     |

| ENCLKOS2      | I   | Clock Enable for CLKOS2 output - only available if CLKOS2 port is active   |

| ENCLKOS3      | I   | Clock Enable for CLKOS3 output - only available if CLKOS3 port is active   |

| PLLCLK        | I   | PLL data bus clock input signal                                            |

| PLLRST        | I   | PLL data bus reset. This resets only the data bus not any register values. |

| PLLSTB        | I   | PLL data bus strobe signal                                                 |

| PLLWE         | I   | PLL data bus write enable signal                                           |

| PLLADDR [4:0] | I   | PLL data bus address                                                       |

| PLLDATI [7:0] | I   | PLL data bus data input                                                    |

| PLLDATO [7:0] | 0   | PLL data bus data output                                                   |

| PLLACK        | 0   | PLL data bus acknowledge signal                                            |

#### Table 13-8. PLL Primitive Port Definition (Continued)

1. The PLLWAKWSYNC and INTLOCK primitive ports are not brought out to the module level when IPexpress is used to generate the PLL. The ports are tied off in the module. Testing indicated that using these ports did not have a significant benefit.

# **Dynamic Phase Adjustment**

The MachXO2 PLL supports dynamic phase adjustments through either the dynamic phase adjust ports or the WISHBONE interface using the following method. The WISHBONE interface is covered in more detail in Appendix D.

To use the dynamic phase adjustment feature the PHASESEL[1:0], PHASEDIR, PHASESTEP ports/signals are used. The DPHSRC port is also available and can be used to confirm that the correct signal source, the primitive ports or WISHBONE signals, has been selected prior to implementing the phase adjustment. The default setting when the dynamic phase ports are selected is to use the primitive ports for dynamic phase adjustments. The source for the dynamic phase adjustments can also be changed from the WISHBONE interface if desired using the MC1\_DYN\_SOURCE WISHBONE register. If the user does not select the dynamic phase ports from the GUI interface then the WISHBONE signals will be used for dynamic phase adjustments.

All four output clocks, CLKOP, CLKOS, CLKOS2, and CLKOS3, have the dynamic phase adjustment feature but only one output clock can be adjusted at a time. Table 13-9 shows the output clock selection settings available using the PHASESEL[1:0] signal. The PHASESEL signal must be stable before the PHASESTEP signal is toggled.

| PHASESEL[1:0] | PLL Output Shifted |

|---------------|--------------------|

| 00            | CLKOS              |

| 01            | CLKOS2             |

| 10            | CLKOS3             |

| 11            | CLKOP              |

### Table 13-9. PHASESEL Signal Settings Definitions

The selected output clock phase will either be advanced or delayed depending upon the value of the PHASEDIR port or signal. Table 13-10 shows the PHASEDIR settings available. The PHASEDIR signal must be stable before the PHASESTEP signal is toggled.

#### Table 13-10. PHASEDIR Signal Settings Definitions

| PHASEDIR | Direction          |

|----------|--------------------|

| 00       | Delayed (lagging)  |

| 01       | Advanced (leading) |

Once the PHASESEL and PHASEDIR have been set the phase adjustment is made by toggling the PHASESTEP signal. Each pulse of the PHASESTEP signal will generate a phase shift of one step. The PHASESTEP signal pulse must be initiated from a logic zero value and the phase shift will be initiated on the negative edge of the PHASESTEP signal. The step size is specified in the equation below.

Step size =  $45^{\circ}$  / Output Divider

If the phase shift desired is larger that 1 step the PHASESTEP signal can be pulsed several times to generate the desired phase shift. One step size is the smallest phase shift that can be generated by the PLL. The dynamic phase adjustment results in a glitch-free adjustment when delaying the output clock but glitches may result when advancing the output clock.

# **Frequency Calculation**

The PLL can be used to synthesize a clock frequency that is needed in a design when the user's board does not have the necessary frequency source. The synthesized frequency can be calculated using the equations listed below.

| $f_{OUT} = f_{IN} * N/M$            | (1) |

|-------------------------------------|-----|

| $f_{VCO} = f_{OUT} * V$             | (2) |

| $f_{PFD} = f_{IN} / M = f_{FB} / N$ | (3) |

Where:

f<sub>OUT</sub> is the output frequency.

f<sub>IN</sub> is the input frequency.

f<sub>VCO</sub> is the VCO frequency.

f<sub>PFD</sub> is the PFD (Phase detector) Frequency.

f<sub>FB</sub> is the Feedback signal Frequency.

N is the feedback divider (integer value shown in the IPexpress GUI).

M is the input divider (integer value shown in the IPexpress GUI).

V is the output divider (integer value shown in the IPexpress GUI).

These equations hold true for the clock output signal that is used for the feedback source to the PLL. Once the VCO frequency has been calculated from these equations, it can be used to calculate the remaining output clock signals using equation (2) above.

The equations listed above are valid provided that the divider value used for the output and feedback paths are equivalent. If they are not then the equation (1) becomes more complex because the two dividers must be included.

# **Fractional-N Synthesis Operation**

The MachXO2 sysCLOCK PLLs support high resolution (16-bit) fractional-N synthesis. Fractional-N frequency synthesis allows the user to generate an output clock which is a non-integer multiple of the input frequency. The Fractional-N synthesis option is enabled in the IPexpress GUI by checking the Enable box under the Fractional-N Divider heading and then entering a number between 0 and 65535 into the adjacent box. The value which is entered in to the box will be divided by 65536 to form the fractional part of the feedback divider (also called the N divider) value. The effective feedback divider value is given by the equation:

$$Neff = N + (F/65536)$$

Where:

N is the integer Feedback divider (shown in the IPexpress GUI).

F is the value entered into the Fractional-N synthesis box described above.

The output frequency is given by the equation:

$f_{OUT} = (f_{IN}/M) * Neff$

Where:

f<sub>OUT</sub> is the output frequency.

f<sub>IN</sub> is the input frequency.

M is the input divider (shown in the IPexpress GUI).

The Fractional-N synthesis works by using a delta-sigma technique to approximate the fractional value that was entered by the user. Therefore, using the Fractional-N synthesis option will result in higher jitter of the PLL VCO and output clocks compared to using an integer value for the feedback divider. It is recommended that Fractional-N synthesis only be used if the N/M divider ratio is 4 or larger to prevent impacting the PLL jitter performance excessively. Fractional N jitter numbers can be found in the MachXO2 Family Data Sheet.

# **Low Power Features**

The MachXO2 PLL contains several features that enable designers to minimize the power consumption of a design. These include dynamic clock enable and support for the standby mode.

# **Dynamic Clock Enable**

The dynamic clock enable feature allows designers to turn off selected output clocks during periods when they are not used in the design. To support this feature, each output clock has an independent output enable signal that can be selected. The output enable signals are ENCLKOP, ENCLKOS, ENCLKOS2, and ENCLKOS3. When the Clock Enable Ports option is selected in the IPexpress GUI the output enable signal will be brought out to the top level ports of the PLL module for the CLKOP port and any other ports that are enabled in the IPexpress GUI.

If an output is not enabled in the IPexpress GUI, the ports for that selected output signal will not be present in the module and that output will be inactive.

# Standby Mode

In order to minimize power consumption, the PLL can be shut down when it is not required by the application. The PLL can then be restarted when it is needed again and, after a short delay to allow the PLL to lock to the feedback signal, the output clocks will be reactivated. To support this mode the Standby Ports option is selected in the IPexpress GUI. This will cause the STDBY signal to be brought out to the top level of the PLL module. Placing the PLL into the Standby mode powers down the PLL and will cause all the outputs to be disabled.

(5)

(4)

The PLL will enter the Standby mode when the STDBY signal is driven high and the outputs will be driven low. The STDBY port can be connected to the power controller so that the PLL will enter the low power state when device is driven to the Standby mode. Alternatively the STDBY port can be driven by user logic independent of the Standby mode.

The PLL will wake-up from the Standby mode when the STDBY signal is driven low. When waking up from Standby mode the PLL will automatically lock to the external feedback signal that was originally selected prior to entering Standby mode. The PLL will lock to the external feedback signal after a maximum time delay of  $t_{LOCK}$ . When the PLL achieves lock to the external feedback signal the LOCK signal will be asserted high to indicate that it has locked.

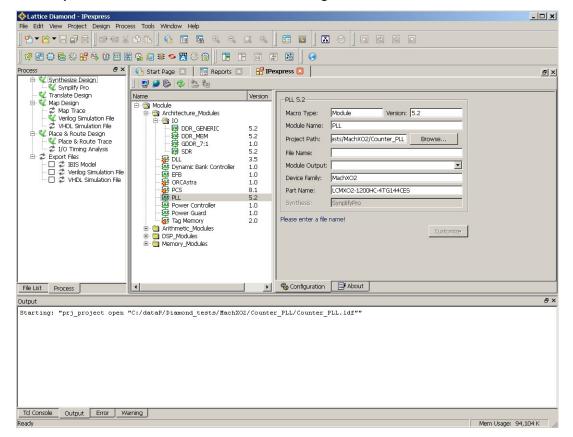

# **Configuring the PLL Using IPexpress**

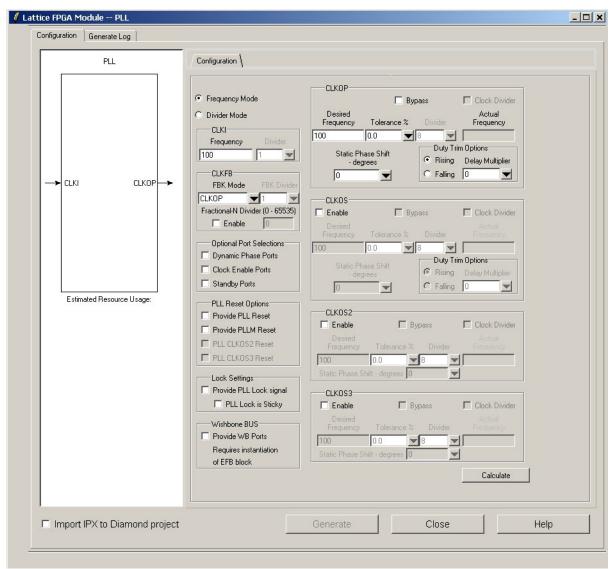

IPexpress is used to create and configure a PLL. Designers can select the parameters for the PLL using the graphical user interface. This process results in an HDL model that is used in the simulation and synthesis flow.

Figure 13-12 shows the main window when the PLL is selected in IPexpress from ispLEVER. For an example of the equivalent screen in Lattice Diamond<sup>®</sup>, see Figure 13-24 in Appendix E. When IPexpress is opened from within the ispLEVER Project Navigator or from Diamond, the project settings are automatically filled in for the you. The only entry required when using ispLEVER is the file name. When using Diamond, the file name and module output type (VHDL or Verilog) must be entered.

If IPexpress is opened as a stand-alone tool then it is necessary to supply the additional parameters shown on this screen. After entering the module name of choice, clicking on the **Customize** button will open the Configuration tab window as shown in Figure 13-13.

| File Tools Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 🗠 😓   🟝 📬   👔                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Name     Version       Module     Architecture_Modules       ID     3.5       ID     3.5       ID     ID       ID     3.5       ID     ID       ID     ID | To generate the module or IP, enter the information in the<br>enabled fields (such as Project Path, File Name, etc.) and click<br>on the Customize button. A dialog will open to allow<br>customization of the selected module or IP.<br>Macro Type: Module Version: 5.1<br>Module Name: PLL<br>Project Path: c:\data_machxo2\designs\test_pll<br>File Name:<br>Design Entry: Schematic/Verilog HDL<br>Device Family: MachX02<br>Part Name: LCMX02:1200HC-4TG100C |

| Local 💋 IP Server                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configuration About                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 13-12. IPexpress Main Window for PLL Module

# Configuration Tab

The configuration tab lists all user-accessible attributes with default values set. Upon completion, clicking on the **Generate** button will generate the source.

# **Configuration Modes**

There are two modes that can be used to configure the PLL in the Configuration Tab: Frequency Mode and Divider Mode.

• Frequency Mode: In this mode the user enters the input and output clock frequencies and IPexpress calculates the divider settings. After input and output frequencies are entered, clicking the **Calculate** button will display the divider values and actual frequencies.

If the output frequency entered is not achievable the nearest frequency will be displayed in the "Actual" text box and an error message will be displayed. The user can also enter a tolerance value in percent. When the Calculate button is pressed the calculation will be considered accurate if the result in within the entered tolerance range.

If an entered value is out of range it will be displayed in red and an error message will be displayed after the Calculate button is used.

• **Divider Mode**: In this mode the user sets the input frequency and the divider settings. Users will choose the CLKOP divider value to maximize the frequency of the VCO within the acceptable range as specified in the MachXO2 Family Data Sheet.

If the combination of entered values will result in an invalid PLL configuration the user will be prompted by a text box to change the value with a suggestion for the value that is out of range.

Figure 13-13. MachXO2 PLL Configuration Tab

### Table 13-11. User Parameters in the IPexpress GUI

| User Parameter         | Description                                             | Range                                                                              | Default |

|------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------|---------|

| Frequency Mode         | User enters desired CLKI and CLKOP frequency            | ON/OFF                                                                             | ON      |

| Divider Mode           | User enters desired CLKI frequency and divider settings | ON/OFF                                                                             | OFF     |

|                        | Frequency                                               | 10 to 400 MHz                                                                      | 100 MHz |

| CLKI                   | Divider                                                 | 1 to 40                                                                            | 1       |

| CLKFB                  | Feedback mode                                           | CLKOP, CLKOS, CLKOS2,<br>CLKOS3, INT_OP,<br>INT_OS, INT_OS2,<br>INT_OS3, UserClock | CLKOP   |

|                        | Fractional-N divider enable                             | ON / OFF                                                                           | OFF     |

|                        | Fractional-N divider                                    | 0 to 65535                                                                         | 0       |

|                        | Dynamic phase ports                                     | ON / OFF                                                                           | OFF     |

| Output Port Selections | Clock enable ports                                      | ON / OFF                                                                           | OFF     |

|                        | Standby ports                                           | ON / OFF                                                                           | OFF     |

|                        | Provide PLL reset                                       | ON / OFF                                                                           | OFF     |

| DLL Deset Ostions      | Provide PLLM reset                                      | ON / OFF                                                                           | OFF     |

| PLL Reset Options      | Provide CLKOS2 reset                                    | ON / OFF                                                                           | OFF     |

|                        | Provide CLKOS3 reset                                    | ON / OFF                                                                           | OFF     |

|                        | Provide PLL LOCK signal                                 | ON / OFF                                                                           | OFF     |

| Lock Settings          | PLL LOCK is "sticky"                                    | ON / OFF                                                                           | OFF     |

| WISHBONE Bus           | Provide WISHBONE ports                                  | ON / OFF                                                                           | OFF     |

|                        | Bypass                                                  | ON / OFF                                                                           | OFF     |

|                        | Clock Divider (in Bypass mode only)                     | ON / OFF                                                                           | OFF     |

|                        | Desired frequency                                       | 3.125 to 400 MHz                                                                   | 100 MHz |

|                        | Tolerance (%)                                           | 0.0, 0.1, 0.2, 0.5, 1.0, 2.0,<br>5.0, 10.0                                         | 0.0     |

|                        | Divider                                                 | 1-128                                                                              | 8       |

| CLKOP                  | Actual frequency (read only)                            | _                                                                                  | _       |

|                        | Static phase shift (degrees)                            | 0°, 45°, 90°, 135°, 180°,<br>225°, 270°, 315°                                      | 00      |

|                        | Rising edge trim                                        | ON / OFF                                                                           | OFF     |

|                        | Falling edge trim                                       | ON / OFF                                                                           | OFF     |

|                        | Delay multiplier                                        | 0, 1, 2, 4                                                                         | 0       |

|                        | Enable                                                  | ON / OFF                                                                           | OFF     |

|                        | Bypass                                                  | ON / OFF                                                                           | OFF     |

|                        | Clock divider (in Bypass mode only)                     | ON / OFF                                                                           | OFF     |

|                        | Desired frequency                                       | 0.024 – 400 MHz                                                                    | 100 MHz |

|                        | Tolerance (%)                                           | 0.0, 0.1, 0.2, 0.5, 1.0, 2.0,<br>5.0, 10.0                                         | 0.0     |

| CLKOS                  | Divider                                                 | 1-128                                                                              | 8       |

|                        | Actual frequency (read only)                            | _                                                                                  | -       |

|                        | Static phase shift (degrees)                            | 0°, 45°, 90°, 135°, 180°,<br>225°, 270°, 315°                                      | 00      |

|                        | Rising edge trim                                        | ON / OFF                                                                           | OFF     |

|                        | Falling edge trim                                       | ON / OFF                                                                           | OFF     |

|                        | Delay multiplier                                        | 0, 1, 2, 4                                                                         | 0       |

| User Parameter | Description                         | Range                                         | Default |

|----------------|-------------------------------------|-----------------------------------------------|---------|

| _              | Enable                              | ON / OFF                                      | OFF     |

|                | Bypass                              | ON / OFF                                      | OFF     |

| CLKOS2         | Clock divider (in Bypass mode only) | ON / OFF                                      | OFF     |

|                | Desired frequency                   | 0.024 to 400 MHz                              | 100 MHz |

|                | Tolerance (%)                       | 0.0, 0.1, 0.2, 0.5, 1.0, 2.0,<br>5.0, 10.0    | 0.0     |

|                | Divider                             | 1-128                                         | 8       |

|                | Actual frequency (read only)        | -                                             | -       |

|                | Static phase shift (degrees)        | 0°, 45°, 90°, 135°, 180°,<br>225°, 270°, 315° | 00      |

|                | Enable                              | ON / OFF                                      | OFF     |

|                | Bypass                              | ON / OFF                                      | OFF     |

|                | Clock divider (in Bypass mode only) | ON / OFF                                      | OFF     |

|                | Desired frequency                   | 0.024 – 400 MHz                               | 100 MHz |

| CLKOS3         | Tolerance (%)                       | 0.0, 0.1, 0.2, 0.5, 1.0, 2.0,<br>5.0, 10.0    | 0.0     |

|                | Divider                             | 1-128                                         | 8       |

|                | Actual frequency (read only)        | -                                             | -       |

|                | Static phase shift (degrees)        | 0°, 45°, 90°, 135°, 180°,<br>225°, 270°, 315° | 0°      |

#### Table 13-11. User Parameters in the IPexpress GUI (Continued)

# **IPexpress Output**

There are two IPexpress output files that are important for use in the design. The first is the <module\_name.[v|vhd] file. This is the user-named module that was generated by IPexpress. This file is meant to be used in both the synthesis and simulation flows. The second is a template file, <module\_name>\_tmpl.[v|vhd]. This file contains a sample instantiation file of the module. This file is provided for the user to copy/paste the instance and is not intended to be used in the synthesis or simulation flows directly.

IPexpress sets attributes in the HDL module for the PLL that are specific to the data rate selected. Although these attributes can be easily changed, they should only be modified by re-running the GUI so that the performance of the PLL is maintained. After the MAP stage in the tool flow, FREQUENCY preferences will be included in the preference file to automatically constrain the clocks produced by the PLL.

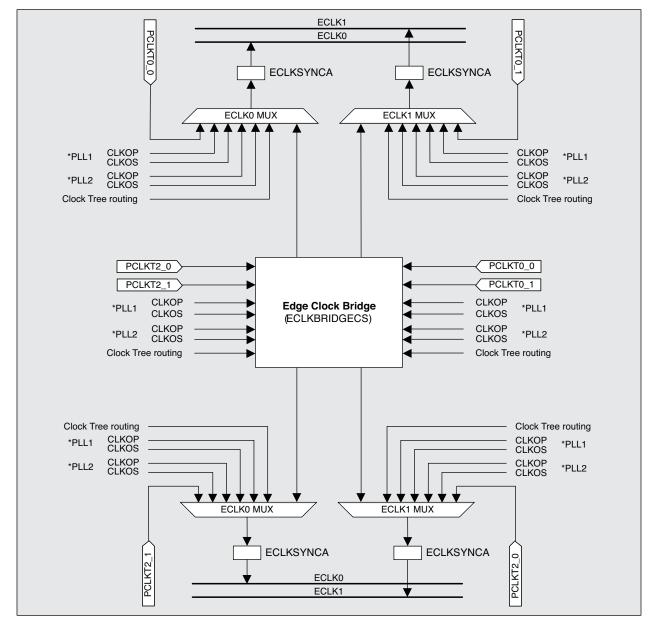

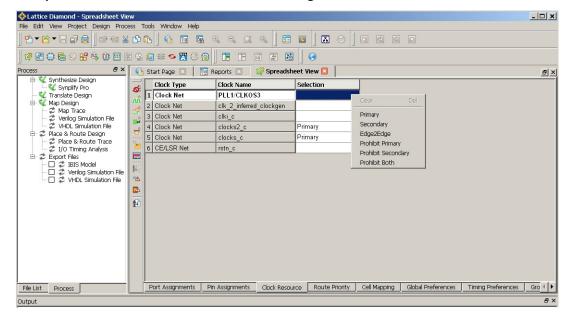

### Use of the Pre-MAP Preference Editor

Clock preferences can be set in the Pre-MAP Preference Editor. Figure 13-14 shows an example screen shot. The Quadrant and DCS/Pure columns are not applicable to the MachXO2 device. The Pre-MAP Preference Editor is a part of the ispLEVER<sup>®</sup> Design Planner tool. The equivalent function in Diamond is simply called the "Spreadsheet View".

Figure 13-14. Pre-MAP Preference Editor Example

| Main Less (pil)     Clock Type     Clock Name     Selection     Ouadrant     DCS/Pure       a - Minput Ports     1     Clock Net     PLL1/CLKOS     N/A     N/A       a - Minput Ports     2     Clock Net     PLL1/CLKOS2     N/A     N/A       a - Minput Ports     3     Clock Net     PLL1/CLKOS2     Clock Secondary       a - Minput Ports     4     Clock Net     clock     Primary       4     Clock Net     clock_c_c     Primary     Edge       5     Clock Net     clock_c_c     Primary     Edge       6     CE/LSR Net     rstn_c     Secondary     Prohibit Primary       Prohibit Both     Prohibit Both     Prohibit Both     Prohibit Both | ∣ቆ⊡. ≵ ≞ ∎ ∾ ∽   %  \$ | Ø, Block | © J Period/Frequency | er infort Clock | llicycle/MaxDelay | fel 🚄 🎫 z     | ≦ <u>A</u> 2↓ |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|----------------------|-----------------|-------------------|---------------|---------------|--|

| Product     Product     Product     Product                                                                                                                                                                                                 |                        |          | Clock Type           | Clock Name      | Selection         | Quadrant      | DCS/Pure      |  |

| Primary     Edge       6     CECLSR Net     rstr_c       6     CECLSR Net     rstr_c       7     Clock Net     clock_c_c       8     Clock Net     clock_c_c       9     Clock Net     clock_c_c       10     CECLSR Net     rstr_c       10     CECLSR Net     rstr_c       11     Secondary       12     Prohibt Primary                                                                                                                                                                                                                                                                                                                                  |                        | 1        | Clock Net            | PLL1/CLKOS      |                   | N/A           |               |  |

| B     Clock Net     PLL I/CLXOS3       B     Clock Net     Clock Net       Clock Net     Secondary       Edge/ZeGpe       Prohib Thimary       Prohib Thimary                                                                                         |                        | 2        | Clock Net            | PLL1/CLKOS2     |                   |               |               |  |

| 4     Clock Net     clia_c     Secondary       5     Clock Net     clock_c_c     Primary     Edge       6     CE/LSR Net     rstn_c     Secondary       Prohibit Primary       Prohibit Secondary                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                        | З        | Clock Net            | PLL1/CLKOS3     |                   |               | 100000        |  |

| 5     Clock Net     clock_c_c     Primary     Edge       6     CE/LSR Net     rstn_c     Secondary     Edge/2E/dge       Prohibit Primary     Prohibit Primary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | e ceis                 | 4        | Clock Net            | clki_c          |                   |               |               |  |

| Prohibit Primary<br>Prohibit Secondary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                        | 5        | Clock Net            | clock_c_c       | Primary           |               |               |  |

| Prohibit Secondary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        | 6        | CE/LSR Net           | rstn_c          | Secondary         | Edge2Edge     |               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                        |          |                      |                 |                   |               |               |  |