# Innovative Airflow Analysis, p. 60 • ARM Architecture: The Story From "Computer" to "MCU," p. 66 COMPUTER APPLICATIONS

#231 October 2009

# SIGNAL PROCESSING

Tackle Difficult Signal-Processing Problems123.6IR Signal Control Made Simple0.15%Power Grid Frequency MonitoringCapacitor ESR Measurement ExplainedDigitally Controlled Amp Design

# 59.96 Hz

$V_{avg}$

59.96 Nz

015% 0 74470 75349 0 \$5.95 U.S. (\$6.95 Canada)

Freq 59.96 Hz

123.6 v

avg

123.6 v

123.6

## A Low Cost Solution for Industrial Serial to Ethernet with Digital I/O and Analog to Digital Converters

## The all-new **NetBurner SBL2e** INDUSTRIAL SERIAL TO ETHERNET SOLUTION

## A NetBurner Complete Hardware & Software Solution

Board Part Number | SBL2e-200IR Information and Sales | sales@netburner.com Web | www.netburner.com Telephone | 1-800-695-6828

# Attention **USB** Developers! Class is now in Session

I will get free HID, Mass Storage, Hub, and Audio class decoding. I will get free HID, Mass Storage, Hub, and Audio class decoding.

I will get free HID, Mass Stor I will get free HID, Mass Stor

## **Debug USB Faster with Data Center Software**

|                                                        | 🖹 🖻 🔒            | 8 5 🖻           | •    | 669.4 | 10   | •                         |                                      |                                     |                               |                      |

|--------------------------------------------------------|------------------|-----------------|------|-------|------|---------------------------|--------------------------------------|-------------------------------------|-------------------------------|----------------------|

| Sø                                                     | Index            | m:s.ms.us       | Len  | Err   | Dev  | Ep                        | Record                               | Deta                                | Nevigetor                     |                      |

| 45                                                     | 1999             | 0.04.016.154    | 34.8 |       | 55   | 00                        | 🕷 🥶 Get String Descriptor            | Index+3 Langth+255                  | Mass Storage Transfer         |                      |

| 45                                                     | 2014             | 0.04.018.623    | 0.8  |       | 55   | 00                        | 🖮 🍼 Set Configuration                | Configuration+1                     | Il General                    |                      |

| HS.,                                                   | 2015             | 0.04.016.623    | 0.0  |       | 55   | 00                        | 🕷 👩 SETUP bin                        | 00 09 01 00 00 00 00 00             | Timestana                     | 0.09.051.571.715     |

| 45                                                     | 2019             | 0.04.018.621    | 0.8  |       | 55   | 00                        | H g Niten (2 POLL)                   |                                     | Duration                      | 2 000 950 mm         |

| 45                                                     | 2027             | 0.09.036.056    | 18   |       | 55   | 00                        | in 🔝 Get Max LUN                     | Max LUN = 0                         | Length                        | 11 Dutes             |

| 45                                                     | 2042             | 0.09.037.570    | 36.8 |       | 55   | 01                        | it 📓 trouty [2]                      | Passed                              |                               |                      |

| 15.                                                    | 2059             | 0:09.043.570    |      |       | 55   | 01                        | in 📳 Teel Unit Ready (0)             | Faled                               | E Command Block Wraps         |                      |

| 45                                                     | 2071             | 0.09.045.570    | 10.8 |       | 55   | 01                        | 🕾 📓 Request Seriae (0)               | Sense Key + Unit Attention (Passed) | dC8WSignature                 | Correct (0+43425355  |

| 45                                                     | 2072             | 0.05.045.570    | 21.8 |       | 55   | 01                        | # E Command Transport                |                                     | dCBWTag                       | Del .                |

| 45.                                                    | 2077             | 0.09.046.570    | 10.8 |       | 55   | 01                        | H 🗑 Dels Transport                   | 70 00 06 00 00 00 00 6A 00 00 00    | dCBI//DataTranaferLangth      | 182                  |

| 45                                                     | 2082             | 0:08.046.721    | 13.8 |       | - 55 | 01                        | 🕷 📓 Status Transport                 | Passed                              | bmCBV//Fixps.Drecton          | Data-In (0b1)        |

| 45                                                     | 2088             | 0.08.047.570    |      |       | 55   | 01                        | A 📓 Test Unit Ready (0)              | Passed                              | <b>BCBVILUN</b>               | 0                    |

| HS.                                                    | 2100             | 0.09.048.571    | 1.0  |       | - 55 | 01                        | # 🗑 Read Capacity (0)                | Passed                              | <b>SCBWCBLergth</b>           |                      |

| MS                                                     | 2117             | 8 09 051 571    | 11.8 |       | 55   | 81                        | # 🗐 Mode Sense (0)                   | Fashed                              | B SCS Command                 | -                    |

| 45                                                     | 2118             | 0.09.051.571    | 31.8 |       | 55   | 01                        | H 🗑 Command Transport                |                                     | Cocode                        | Node Sense (E) (Du1  |

| 45                                                     | 2119             | 0:09.051.571    | 31.8 |       | 55   | 01                        | 🕷 🎒 OUT two                          | 88 53 42 43 04 00 00 00 C0 00 00    |                               |                      |

| 45                                                     | 2123             | 0.09.052.571    | 11.0 |       | 55   | 01                        | 🗟 📓 Data Transport                   | CB 00 00 CB 00 00 00 00 00 02 C2    | Disable Block Descriptors     | Not Disabled (DDD)   |

| 15                                                     | 2124             | 0.09.052.571    | 11 0 |       | 55   | 01                        | iii 🥔 Nibet                          | 08 00 00 00 00 00 00 00 00 00 02    | Page Central                  | Current values (DbD) |

| 45                                                     | 2125             | 0:09.052.571    | 38   |       | 55   | 01                        | O Ripschef                           | 49 37 30                            | Page Code                     | 0x3f                 |

| 45                                                     | 2126             | 0.08.052.571    | 148  |       | 55   | 01                        | DATAD pecket                         | C8 08 00 00 08 00 00 00 00 00 00    | Subpege Code                  | 040                  |

| 45                                                     | 2127             | 8 09 052 572    | 18   |       | 55   | 01                        | <ul> <li>ACK packet</li> </ul>       | 03                                  | Altroation Length             | 192                  |

| 45                                                     | 2128             | 0.09.053.571    | 138  |       | 55   | 01                        | 🛪 🗑 Status Transport                 | Passed                              | Cantral                       | 960                  |

| 45                                                     | 2134             | 0.09.054.572    |      |       | 55   | 01                        | ik 📓 Test Unit Ready (0)             | Passed                              | Il Mode Sense (II) Data       | -                    |

| 45                                                     | 2146             | 0.09.056.571    |      |       | 55   | 01                        | A 📓 Prevent Adour Medium Removal (0) | Removal Prohibited (Falled)         | The block descriptor is missi |                      |

| 45                                                     | 2158             | 0:09.058.572    | 10.0 |       | 55   | 01                        | ik 📳 Request Sense (0)               | Sense Key + Begal Request (Passed)  | Node Data Length              | 11                   |

|                                                        |                  |                 |      |       |      |                           |                                      | 2                                   | Nedun Type                    | 0-0                  |

|                                                        |                  |                 |      |       |      | Device-Specific Parameter | 0+0                                  |                                     |                               |                      |

|                                                        |                  |                 | -    |       |      |                           |                                      |                                     |                               | 04                   |

| Filte                                                  | applied: matched | 15,422 of 5,893 |      |       |      |                           |                                      | Protocol Lens: USB 🛩 🍠              | Block Descriptor Length       |                      |

|                                                        |                  |                 |      |       |      |                           |                                      |                                     | Command Status Wrap           |                      |

| Command Line X Details X                               |                  |                 |      |       |      |                           | dCS//Signature                       | Correct (0x5342535)                 |                               |                      |

| * 0 144 1124-517138 1.90 1.91 938 C 012 3 4 5 6 7 ASCB |                  |                 |      |       |      |                           | oCSWTag                              | 048                                 |                               |                      |

|                                                        |                  |                 |      |       |      |                           | dC51/QataResidue                     | 0                                   |                               |                      |

| 2> connect(1124570138)                                 |                  |                 |      |       |      |                           | bCDI//Dtatue                         | Passed (0x0)                        |                               |                      |

|                                                        |                  |                 |      |       |      |                           | 00010                                |                                     |                               |                      |

| Des                                                    | ice settings     | updated.        |      |       |      |                           | 00018                                |                                     | -                             |                      |

|                                                        |                  |                 |      |       |      |                           | 00020<br>Date                        |                                     | C But Filer Infe              |                      |

Please visit our website for our complete line of USB, I2C, & SPI tools.

Real-time class-level decoding is now available in the Data Center Software for the Beagle USB 480 Protocol Analyzer.

Within a few clicks, class-level USB data is instantly decoded and displayed as it is being captured.

Debug USB with class. Get yours now.

# The Newest Semicond uctors

## New Products from:

TEXAS INSTRUMENTS Authorized Distributor TMS320C672x Digital Signal Processor www.mouser.com/tidsp/a

🗚 freescale

MC56F8006 / MC56F8002 Digital Signal Controller www.mouser.com/freescale/a

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 390 leading suppliers.

a til company

The Newest Products For Your Newest Designs

(800) 346-6873

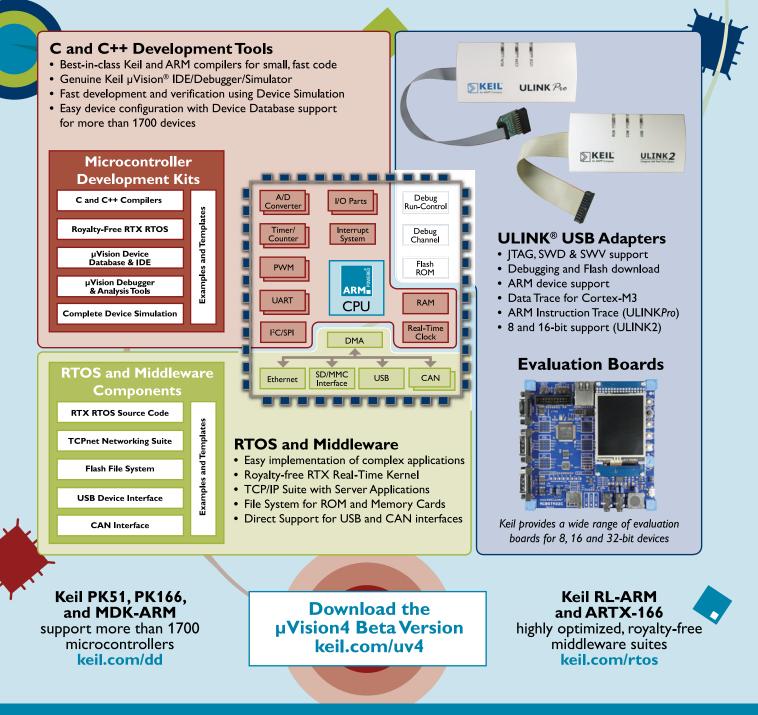

## Development Solutions

## for ARM<sup>®</sup>, 8051 & XE166 Microcontrollers

## keil.com 1-800-348-8051

## **Signal Significance**

Readers and writers know we typically run about one or two "theme-related" articles per issue. We do this because we have a wide readership with diverse interests. We try to please as many people as possible. And we've been doing that well since 1988. What's always interesting about the Signal Processing issue is that almost every article we run (as well as many of those considered for publication) has something to do with signal theory, processing, or control in one way or another. You don't need a PhD with a focus on signal processing to be an embedded design engineer. But you definitely need a good grounding in signal theory to be a successful one, whether your end goal is a marketable embedded wireless product or simply a handy design for your workbench.

This Signal Processing issue is true to form. As you'll see, the topics of signal processing and control figure prominently in most of the subjects covered.

In "IR Signal Control," Naubert Aparicio presents a design for offsite control of an electrical system (p. 12). He uses the IR signal controller design to remotely operate his home's AC system from his cell phone. You can use the techniques Naubert covers to customize an IR signal control project of your own.

Frequency monitoring is the topic presented in Arnold Stadlin's article, "Frequency Sensing Made Simple" (p. 22). In this article, he describes a microcontroller-based power frequency monitor design that can indicate the relative stability of a power grid. The design measures power grid frequency via a standard electrical outlet. The acquired data is transferred to a PC, which displays the information and relays it to a web server for real-time analysis.

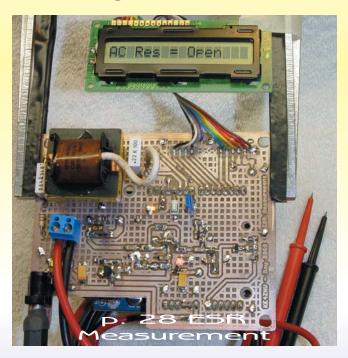

As you probably know, many instruments don't measure equivalent series resistance (ESR). Enter Ed Nisley. After studying the design of a classic pure-analog ESR meter, he built an analog front end for an MCU that measures ESR. In "Capacitor ESR Measurement," he covers the project's design and math (p. 28).

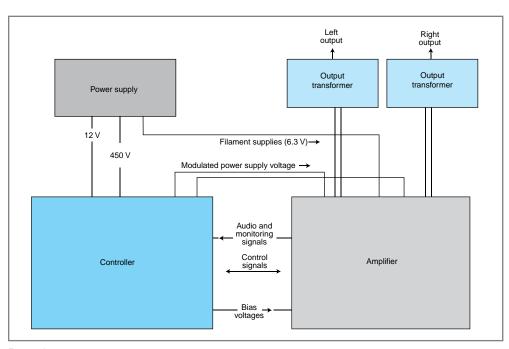

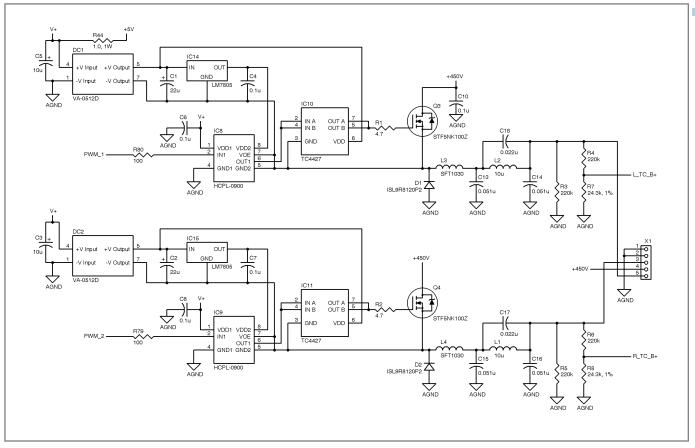

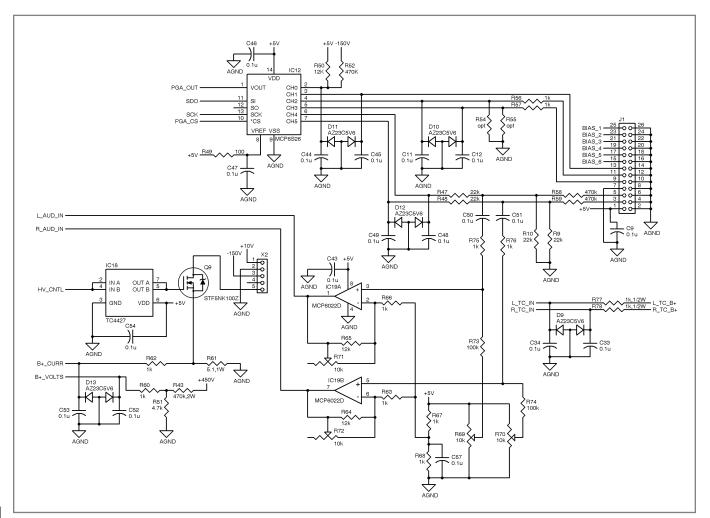

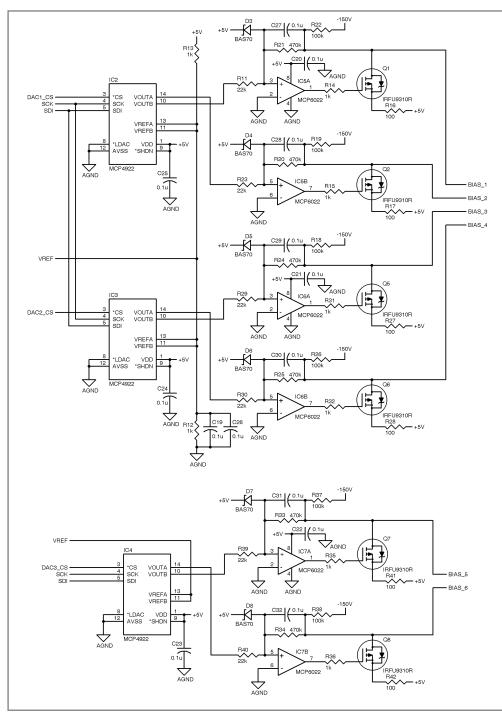

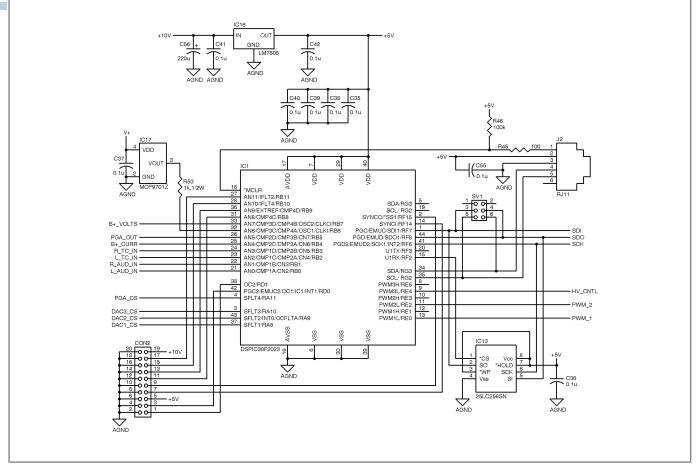

Starting on page 38, George Anderson presents a dsPIC30F2023-controlled, high-end vacuum tube stereo amplifier with distortion control, power output, and more. He describes unique circuitry and specialized processing software.

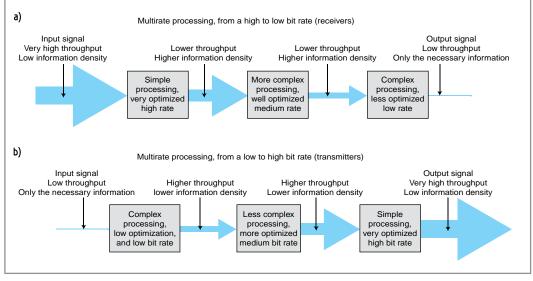

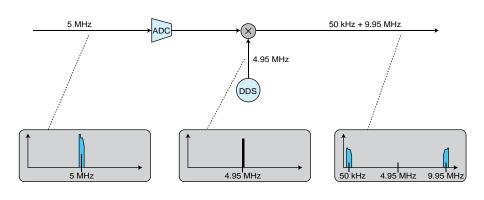

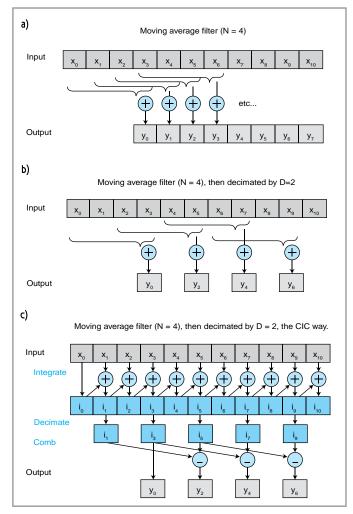

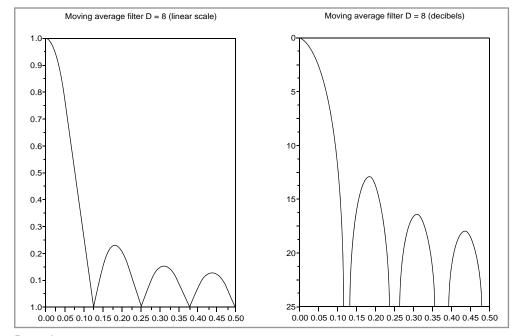

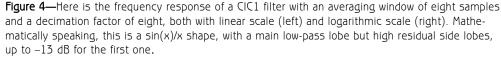

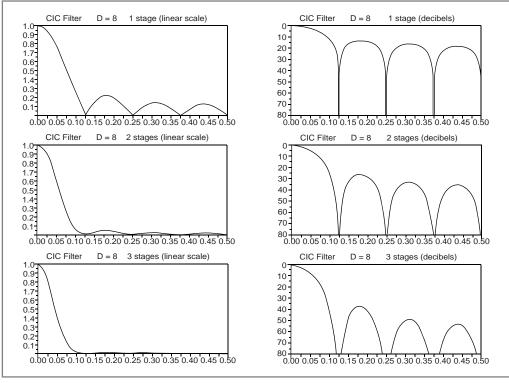

Turn to page 50 for information about multirate techniques and cascaded integrator-comb (CIC) filters. Robert Lacoste explains how you can use these moving average filters to tackle difficult signal-processing issues. When a FIR filter won't do the trick, this might be the perfect solution.

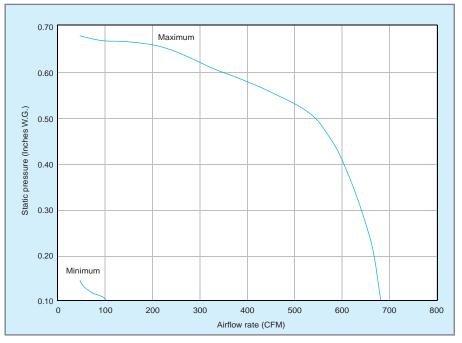

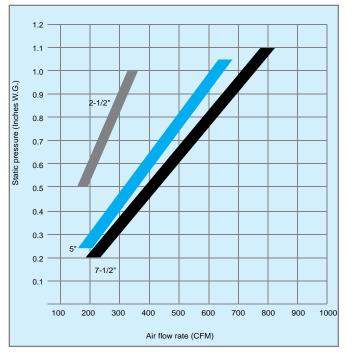

In "Airflow Analysis," Jeff Bachiochi describes an effective way to measure airflow in an air duct (p. 60). He explains how he took apart a small CPU fan, calculated RPMs, and implemented a circuit to output data to an LCD.

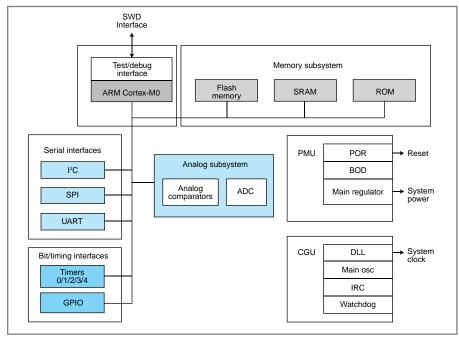

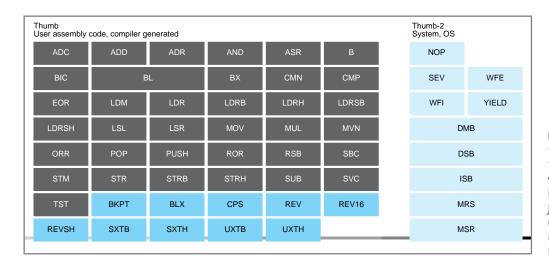

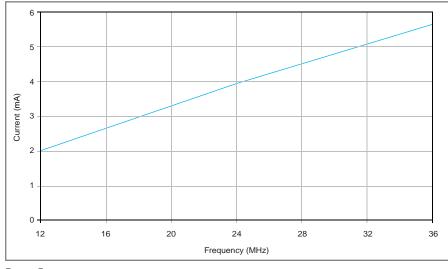

Remember when Acorn Computers introduced its RISC CPU? Tom Cantrell has been following the story for nearly two decades. In "Thumbs Up: The ARM Saga Continues," he brings you up to speed with a review of the ARM Cortex-M0 core (p. 66). The story continues.

cj@circuitcellar.com

C.Aprile

# CIRCUIT CELLAR®

#### FOUNDER/EDITORIAL DIRECTOR

Steve Ciarcia

MANAGING EDITOR

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Jeff Bachiochi Robert Lacoste George Martin

Ed Nisley

NEW PRODUCTS EDITOR

PROJECT EDITORS Gary Bodley Ken Davidson David Tweed CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> MEDIA CONSULTANT Dan Rodrigues

CUSTOMER SERVICE Debbie Lavoie

> CONTROLLER Jeff Yanco

ART DIRECTOR KC Prescott

GRAPHIC DESIGNERS Grace Chen Carey Penney

> STAFF ENGINEER John Gorsky

#### ADVERTISING

860.875.2199 • Fax: 860.871.0411 • www.circuitcellar.com/advertise

#### PUBLISHER Sean Donnelly

Direct: 860.872.3064, Cell: 860.930.4326, E-mail: sean@circuitcellar.com

ADVERTISING REPRESENTATIVE Shannon Barraclough Direct: 860.872.3064, E-mail: shannon@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster E-mail: val.luster@circuitcellar.com

> Cover photography by Chris Rakoczy—Rakoczy Photography www.rakoczyphoto.com

## PRINTED IN THE UNITED STATES

SUBSCRIPTIONS

Information: www.circuitcellar.com/subscribe, E-mail: subscribe@circuitcellar.com Subscribe: 800.269.6301, www.circuitcellar.com/subscribe, Circuit Cellar Subscriptions, P.O. Box 5650, Hanover. NH 03755-5650

Address Changes/Problems: E-mail: subscribe@circuitcellar.com

#### GENERAL INFORMATION

860.875.2199, Fax: 860.871.0411, E-mail: info@circuitcellar.com Editorial Office: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: editor@circuitcellar.com

New Products: New Products, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: newproducts@circuitcellar.com AUTHORIZED REPRINTS INFORMATION

860.875.2199. E-mail: reprints@circuitcellar.com

AUTHORS

Authors' e-mail addresses (when available) are included at the end of each article

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Vernon, CT 06066. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions 529.95, Canada/Mexico \$34.95, all other countries \$49.95. Two-year (24 issues) subscription rate USA and possessions \$49.95, Canada/Mexico \$59.95, all other countries \$45. All subscription orders payable in U.S. funds only via Visa, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-5650 or call 800.2665.0311.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755-5650.

Circuit Cellar® makes no warranties and assumes no responsibility or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of read er-assembled projects, Circuit Cellar® disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Cellar® makes no claims or warrants that readers have a right to build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader assumes any risk of infringement liability for constructing or operating such devices.

Entire contents copyright @ 2009 by Circuit Cellar, Incorporated. All rights reserved. Circuit Cellar is a registered trademark of Circuit Cellar, Inc Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

ojeon

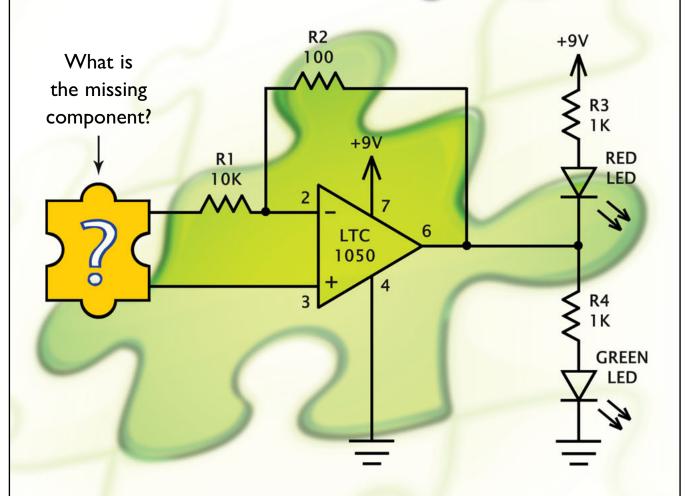

# Are you up for a challenge?

Industry guru Forrest M. Mims III has created a stumper. Video game designer Bob Wheels needed an inexpensive, counter-clockwise rotation detector for a radio-controlled car that could withstand the busy hands of a teenaged game player and endure lots of punishment. Can you figure out what's missing? Go to <u>www.Jameco.com/unravel</u> to see if you are correct and while you are there, sign-up for our free full color catalog.

# INSIDE ISSUE

Buddy Memory Manager

Arduino-based Temperature Display

p. 12 Signal Control

- ABOVE THE GROUND PLANE Capacitor ESR Measurement Ed Nisley

- **THE DARKER SIDE** Multirate Techniques and CIC Filters Robert Lacoste

- **FROM THE BENCH** Airflow Analysis Jeff Bachiochi

- **SILICON UPDATE** Thumbs Up The ARM Saga Continues *Tom Cantrell*

October 2009 • Signal Processing

IR Signal Control Naubert Aparicio

INTELLIGENT ENERGY SOLUTIONS Frequency Sensing Made Simple Power Grid Frequency Monitor Design Arnold Stadlin

$\mathbf{38}$

**Digitally Controlled Amplifier** Connect Vintage Analog to Modern Digital Tech George Anderson

- TASK MANAGERSignal SignificanceC. J. Abate

- NEW PRODUCT NEWSSedited by John Gorsky

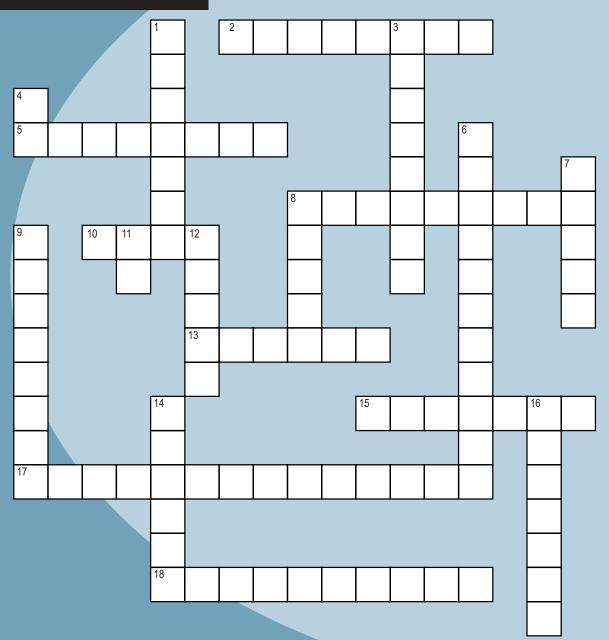

- CROSSWORD 74

- INDEX OF ADVERTISERS 79 November Preview

- PRIORITY INTERRUPTSOA Broadening ExperienceSteve Ciarcia

$\mathbf{28}$

## Hammer Down Your Power Consumption with picoPower™!

## **THE Performance Choice of Lowest-Power Microcontrollers**

Performance and power consumption have always been key elements in the development of AVR<sup>®</sup> microcontrollers. Today's increasing use of battery and signal line powered applications makes power consumption criteria more important than ever. To meet the tough requirements of modern microcontrollers, Atmel<sup>®</sup> has combined more than ten years of low power research and development into picoPower technology.

picoPower enables tinyAVR<sup>®</sup>, megaAVR<sup>®</sup> and XMEGA<sup>™</sup> microcontrollers to achieve the industry's lowest power consumption. Why be satisfied with microamps when you can have nanoamps? With Atmel MCUs today's embedded designers get systems using a mere 650 nA running a real-time clock (RTC) and only 100 nA in sleep mode. Combined with several other innovative techniques, picoPower microcontrollers help you reduce your applications power consumption without compromising system performance!

Visit our website to learn how picoPower can help you hammer down the power consumption of your next designs. PLUS, get a chance to apply for a free AVR design kit!

## http://www.atmel.com/picopower/

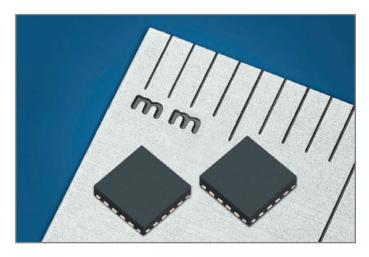

## FRONT END IC SIMPLIFIES BOARD DESIGN AND REDUCES COST

The UPG2253T65 Front End Integrated Circuit (FEIC) is a highly integrated device that combines a power amplifier, low-pass filter, and two single-pole, double-throw switches into a single chip. By integrating these components into one die, the FEIC reduces the component count, saves the total bill of materials cost, simplifies procurement, and decreases the PCB space required for many new embedded product designs. The FEIC eliminates the need for RF component matching, which greatly simplifies board design and further reduces component count.

The FEIC is superior to similar products on several fronts. Its smaller package size enables product designs with tiny footprints, while its better harmonic suppression eliminates the need for low-pass filters on most product designs. Few designs have the FEICs through/PA bypass feature, which enables the end product to switch to a high-power mode when greater range is needed, but automatically switches to a low-power mode when greater battery savings are optimal. Alternatively, the through/bypass path can be used as the receive path. Furthermore, the ability to integrate these functions on a single chip gives size reduction and performance advantages over companies using multi-chip modules.

The UPG2253T65 FEIC is shipping now. It costs \$1.10 in quantities of 100,000. Evaluation boards are available.

California Eastern Laboratories www.cel.com

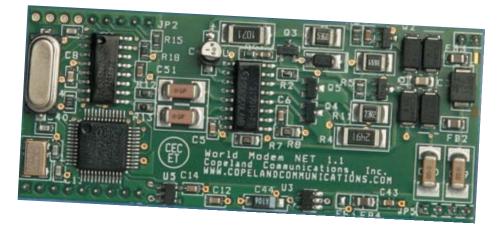

## EMBEDDED MODEM DEVICE SERVER

The World Modem NET is a compact 2400 to 56 K baud modem with embedded Internet link controller. The unit features a transformerless DAA meeting global telephone system requirements, no electromechanical components, and a flexible DSP data pump. The modem is user-configurable to meet virtually all global telecom requirements and conforms to the industry-standard World Modem mechanical and interface specifications. Because of its built-in features and flexibility, many applications and OEM products can be created using the device.

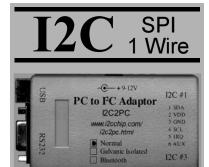

In addition, the modem mediates an Internet link via its embedded controller. This provides an extended AT command set for a simple, low-overhead interface to the Internet. The World Modem NET also provides interfaces to SPI, I<sup>2</sup>C, and general-purpose I/O signals. The base version includes support for IP, TCP, UDP, DNS, HTTP client, and PING. SMTP, FTP, and other features are available as options. The embedded controller automatically configures the modem interface and is controlled by an extension to the AT command set.

The World Modem NET comes with a transferable FCC Part 68 license, CE, and other certifications. The World Modem NET requires only 65-mA maximum at either 3.3 or 5 V, and provides 5 kV of isolation.

The World Modem NET prices start under \$43 in 1,000-piece quantities. RS-232 and USB models are also available upon request. The World Modem NET is available through Saelig Company or Copeland Communications.

Copeland Communications, Inc. www.copelandcommunications.com

## W PRODUCT N Edited by John Gorsky

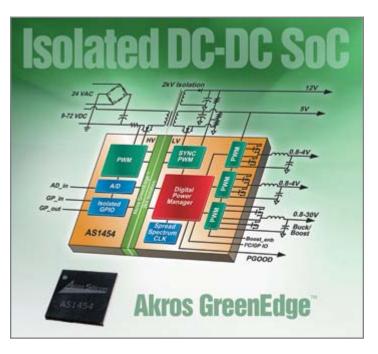

## TWO kV-ISOLATED, QUAD-OUTPUT POWER SoC

The **A51454** is an isolated quad-output digital power SoC that sets a new integration benchmark for isolated DC-DCs in a wide range of industrial and other distributed power applications. The A51454 eliminates the need for low-speed, bulky optocouplers and integrates the

for low-speed, bulky optocouplers and integrates the functionality of up to eight separate ICs used in current implementations. This leads to a substantial reduction in design footprint and bill-of-material costs. The A51454's built-in cross-isolation DC-DC timing management and digital power control delivers 92% DC-DC efficiency with excellent light-load efficiency management for energyefficient, green-power applications.

The A51454 integrates a wide input range (9- to 72-V) isolated primary converter, a 2-kV isolation barrier, a high-current-capable buck or boost PWM controller, and two 2-A buck regulators into a single device. Its wide-input voltage range allows it to be used in 12 VDC/24 VDC/24 VAC distributed power applications, as well as 48-V distributed power applications and equipment requiring a 36- to 72-V input voltage range. It offers selectable spread-spectrum clocking on all PWM to reduce power-supply spectral noise by more than 15 dB to lower the EMI signature of the switch-mode power supplies and ease system design for EMC compliance.

Device pricing is available upon request.

Akros Silicon, Inc. www.AkrosSilicon.com

**RF Specialists**

**RF** Modules

From Part 15 to Part 90 Compliant Narrow Band FM, UHF Multi-Channel GSM/GPRS

GSM/GPRS modules and modem series

M2M Solutions

## Data Loquers ndustrial Bluetooth OEM, Modules, Wireless Device Servers, RS-232 Stand Alone and Long range options, low cost Wireless Mesh Networking Logger LigBee Pro OEM Modules and USB ZigBee Sticks, OEM Modules and USB ZigBee Sticks, Mesh Networks Mesh Networks Wi-Fi S232 / 422 / 485 to Wi-Fi Adapter onnect Data Acquisition Equipment through Serial Port to Wi-Fi network ww.lemosint.com 866.345.3667 INTERNATIONAL sales@lemosint.com

## COMPACT HIGH-PERFORMANCE SBC

The **Eagle 50** and **50E** are single-board computers (SBCs) designed for cost-sensitive control applications that require realtime performance, networking, and extensive support of popular peripherals. Available in the compact 100 mm x 72 mm picoITX form factor, they deliver 32-bit performance and features at a cost equivalent to legacy 8- and 16-bit controllers. Powered by a TI ARM Cortex-M3 core capable of 60 MIPS, these SBCs can fulfill demanding requirements in monitoring, instrumentation, data acquisition, process control, factory automation, and many other applications. Configurations include up to 256-KB flash memory, 64-KB SRAM, 40 digital I/Os, eight analog inputs, four analog outputs, RS-232/485, one microSD card, and a battery-backed RTC. The Eagle 50E also supports 100-Mbps Ethernet, allowing remote access via web or command line interfaces for off-site monitoring. An optional USB port can be used for programming or data transfers.

IAR and GNU programming tools allow development of fast and efficient applications in C. An extensive collection of code examples is included to get started quickly. Ports of popular open-source Basic and LUA development tools are also available to reduce application development time. Demos of FreeRTOS and NuttX are included for applications requiring an RTOS. The Eagle SBCs provide system designers and integrators with high functionality, a

NPN

compact footprint, and a low cost.

In single quantities, the Eagle 50 starts at **\$44.95** and the Eagle 50E at **\$49.95**. Custom OEM versions can be designed for specific requirements.

#### Micromint USA www.micromint.com

## The Next Generation of In-Circuit Debugging

## The NEW MPLAB® ICD 3

The MPLAB ICD 3 In-Circuit Debugger is Microchip's most cost effective high-speed debugger for Microchip Flash PIC® Microcontrollers (MCU) and dsPIC® Digital Signal Controller devices. It debugs and programs PIC MCUs and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of MPLAB Integrated Development Environment (IDE).

- In-Circuit Debugging for PIC MCUs and dsPIC DSCs

- Full-speed, real-time emulation

- Source debugging, stopwatch, complex breakpoints and in-circuit programming

- MPLAB IDE compatible

- Firmware upgrade via MPLAB IDE

- Overvoltage and undervoltage protection

- High Speed USB 2.0 (480 Mbps)

- Target power, up to 100 MA

- Internal 1 MB memory buffer for increased download speed

## MPLAB® ICD 2 RECYCLE

Return your old MPLAB ICD 2 and receive 25% off the new MPLAB ICD 3, MPLAB REAL ICE or PICkit<sup>™</sup> 3 Debug Express. For more information on this offer, please visit:

www.microchip.com/ICD2recycle

The Microchip name and logo, the Microchip logo, MPLAB and PIC are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries. PICkit is a trademark of Microchip Technology Incorporated in the U.S.A. and other countries. © 2009, Microchip Technology Incorporated. All Rights Reserved.

www.microchip.com/ICD3

## **IR Signal Control**

Do you want offsite control of your electronic equipment? With this handy IR signal controller design, you can remotely operate the system of your choice right from your cell phone. In this project, the inno vative design is used to control an AC system.

live in Puerto Rico, which is a hot place, as you know. The temperature averages 82.4°F (30°C) throughout the year, but it can reach temperatures above 100°F. As a result, some of us are used to ar tificial climates—that is, air-conditioned environments—which cost money to maintain. Like many tropical islands, much of Puerto Rico's electricity is expensive because it comes from oil-based power plants.

Thus, electricity conservation is the best way to keep my monthly utility bill down. To do so, I power-up my AC units only when someone is home. But when I get home at 6 PM after a long day of working and sitting in traffic jams, I don't like it when walking through my door feels like entering an oven.

I used to use timers to control my AC system, but I eventually stopped because I wasn't arriving at home the same time every day. It was then that I decided to design a way to control my AC system remotely. I wanted to be able to turn on my AC early enough to cool my house before arrival. Figuring that I'd typically use such a design from my car, I decided to use my cell phone as the remote control device.

After a few days of planning, I

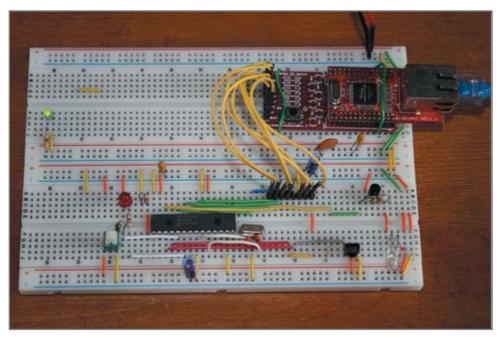

came up with my ACcontrol design (see Photo 1). It is a small stand-alone, Ethernet-enabled device that uses an infrared (IR) signal for controlling my AC system remotely. By connecting the device to my fixed Internet connection, I can continuously monitor a POP e-mail account for a specific e-mail subject. When it is found, the system sends an IR signal that enables AC control. I can use virtually any

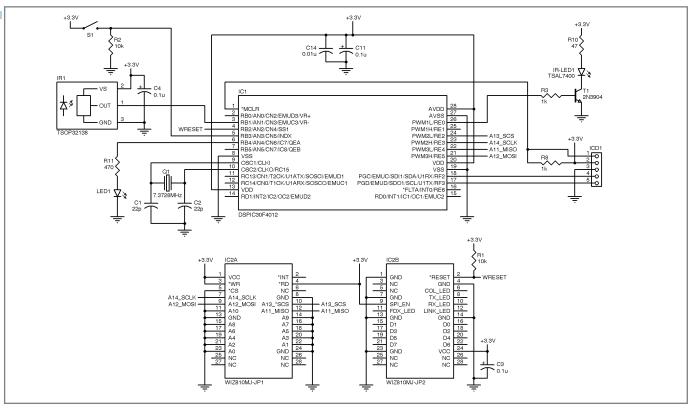

**Photo 1**—The ACcontrol features a WIZ810MJ module (top right) and a Microchip T echnology dsPIC30F4012 (center). A red LED mode indicator and a push button form a simple user interface. The IR sensor and the IR transmitter are on the lower right.

October 2009 - Issue 231

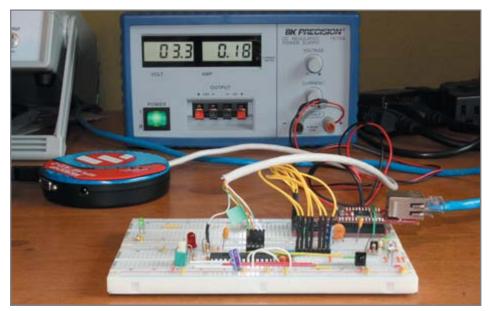

**Photo 2**—This is my development setup. I used a Microchip MPLAB ICE 2 to help with the debugging process. Being able to display the internal variables (e.g., the retrieved IP packets) through hardware breakpoints was important for accelerating the debugging process.

cell phone to send an e-mail (even with only SMS through an SMS-to-e-mail gateway). Upon receipt, the system sends a confirmation e-mail so I know the command was received.

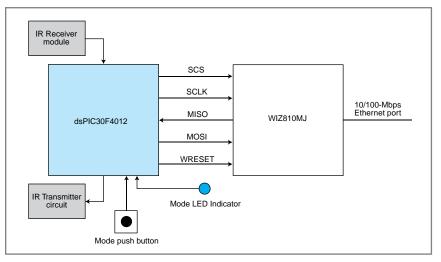

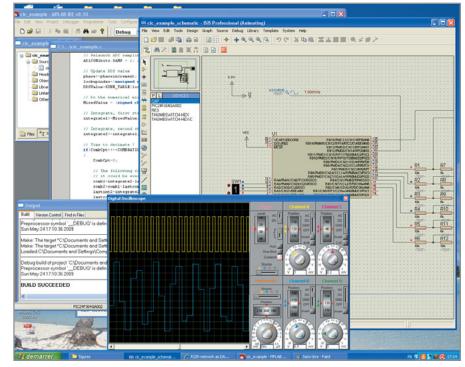

In this article, I'll describe how I designed the control system around a WIZnet WIZ810MJ module and a Microchip Technology dsPIC30F4012 microcontroller. The W5100 chip embedded in the WIZ810MJ module is a high-level hardwired TCP/IP implementation that ultimately makes projects like this simple, fast, and affordable. I programmed the project in C language with shor t assembler routines using Microchip Technology's MPLAB IDE version 7.52 and the C30 compiler. I ported the W5100 driver to the Microchip architecture and

adapted the WIZnet DNS routines to use the SPI. For simplicity, I extracted several utility routines from WIZnet application notes and adapted them to my code. I used a Microchip MPLAB ICE 2 programmer/debugger and an external power supply as my development setup (see Photo 2).

#### **USER INTERFACE**

I purposely tried to make everything associated with this project as simple as possible. For instance, I didn't want to complicate the project with difficult or costly interfaces. Thus, once the system is configured, it requires no further user interaction.

I designed a simple set-up procedure and incorporated only one button and an LED indicator. The design has the ability to learn an infrared command, set the

network configuration (IP, netmask, gateway, DNS IP), configure the POP account, set an access password, erase a forgotten password, and configure the specific e-mail subject to trigger the infrared signal. The network parameters are set from a local networked computer through a dedicated set-up program. Then, through a telnet interface, the rest of the configuration can be adjusted. You can develop a more elaborate graphical interface setup program in the future with this same design.

### SYSTEM SET-UP

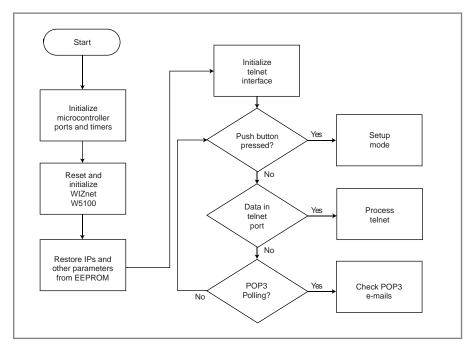

Setting up the ACcontrol system is simple (see Figure 1). First, the device is connected to the network and powered on. Pressing the button for 5 s activates the IP

set-up mode. In this mode, the system waits for a network-based configuration packet that's sent by the set-up program in a nearby networked PC. I developed a Linux command line program for this project, but it could be ported easily to any operating system that supports TCP. The set-up program sends a special UDP broadcast packet that contains the IP number, netmask, gateway address, and DNS to be set in the device. When the ACcontrol is in IP set-up mode and sees a configuration packet that matches its MAC address, it sets its network parameters from the packet data. After this, you can telnet to the assigned IP and set the rest of the parameters. All the parameters are saved into the Microchip EEPROM to preserve its values. You can change the telnet password

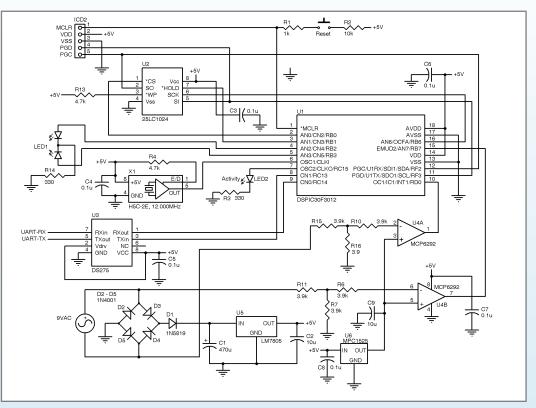

**Figure 1**—The WIZ810MJ module simplified this project. The only other major component is a dsPIC30F4012 that handles the higher-level TCP routines and IR logic. The WIZnet W5100 hardwired TCP/IP integrated circuit handles the lower-end TCP/IP stack. This resulted in cleaner code and reduced microcontroller har dware requirements.

**Figure 2**—I used a hardwired TCP/IP hardware module and a SPI. It seems as though the software in the dsPIC30F4012 handles everything. But in reality, most of the TCP/IP complexity is hidden from the programmer in the W5100 IC located inside the WIZ810MJ module. A single 3.3-V regulated power source rated at 350 mA is enough to power this project.

from the same telnet session. If you forget it, you can reset it by pressing the button for more than 5 s.

The IR command setup to powerup the AC is also simple. Pressing the Mode button once puts the ACcontrol in IR learning mode. The infrared command is then "learned" by pointing the original AC remote control to the IR-receiving sensor and pushing the Power button on the remote. The LED indicator remains on while learning mode is activated.

#### HARDWARE DESIGN

The WIZnet module simplified the design. In addition to the WIZ810MJ module and the dsPIC30F4012 microcontroller, I used a Vishay Intertechnology TSOP321 38-kHz IR receiver module and a TSAL7400 high-output IR emitting diode (see Figure 2). The WIZnet module comprises everything needed for the Ethernet interface, including the RJ-45 socket, the support circuit, and a SPI. I chose the dsPIC30F4012 for its RAM, EEPROM, flash memory, and timer resources. I needed it to implement the IR learning and sending routines, as well as to implement the code needed for the DNS, POP3, and SMTP software components. The dsPIC software handles the higher-level TCP protocols, all the communication with the W5100, the user interface, and the IR learn and

**Figure 3**—The segmented software makes it easy to develop and understand. The initialization process is straightforward. The rest of the code is an event loop, where an action is taken after a specific event is detected.

send functions. It controls the WIZ810MJ module through a four-pin SPI and a fifth pin for a RESET signal. I manually coded the SPI routines because the hardware SPI module shared the pins with the PIC debugging interface. The 38-kHz infrared module handles the IR code reception and sends a filtered signal to the dsPIC30F4012's CN3 input configured to generate an interrupt when the logic state changes. Finally, the dsPIC30F4012 is also connected through the REO pin to an IR LED through a 2N3904 amplifier. The REO is driven by the dsPIC PWM module set to generate the required IR frequency of 38 kHz. The only other two connections are for the push button and red LED as the user interface.

### SIMPLE SOFTWARE?

The hardware is simple, but is the software complex? No. If you're familiar with the TCP protocols (i.e., the POP3, DNS and SMTP protocols), the only complexity that remains is related to the W5100 interface and IR-handling routines. Let's review each software segment and see how they work, so that you can form your own conclusions about this project's complexity. I encourage you to download the source code from the *Circuit Cellar* FTP site so you can follow the subsequent explanations.

Figure 3 depicts the software flow. You can see the standard hardware initialization that covers the dsPIC resources and the W5100 chip. It is followed by the parameter initialization in the EEPROMs and the initialization of the telnet interface. The software then enters in a loop to look for the push button or data in the telnet port or data in the POP3 account. Each of these functions is handled in a separate code segment. This flow is shown as the main() routine (see Listing 1).

The first four routines initialize the system. The init() routine initializes the dsPIC30F4012 by configuring the I/O pins, programming the PWM module to the output IR frequency, sending and holding the RESET signal to the WIZnet module, and programming the systick timer used for the delay routines. The next initialization routine is for the IR system, IR\_init(). This initializes the IR input port interrupt and the Timer3 module (TMR3) to count every 8.7-µs resolution used to measure the IR pulses. When I cover the IR routines later in this article, you'll see that these can easily cope with most of the IR protocols.

After setting up the IR hardware, the next thing to do is to prepare the

W5100 hardware TCP/IP chip. This is done with the reset\_w5100 and sysinit calls. The former just resets the W5100. It is held in reset by the init() call, so in this second call it just frees it after the required hardware reset delay of more than 10 ms. A software reset command is then sent to the chip itself. Then comes the sysinit call, part of the W5100 driver, which configures the transmit and receive buffer sizes. The W5100 has four channels, each for

different TCP/IP connections. Also, the W5100 has 8 KB of internal memory. The amount of memory you assign to each channel depends on the simultaneously open sockets or connections in your software, which will determine the volume of traffic the system can handle. More memory assigned to a channel means that the software may be slower when attending the connection as the buffer is bigger and data will not be lost.

I used three channels, so I configured the W5100 in the only possible configuration: 1 KB for each transmit and receive buffer for four channels (8 KB in total). Thus, packets can't exceed the 1 KB size, which is not a problem for my configuration. In my software, channel 0 is assigned as an administration RAW port for IP address configuration, channel 1 is shared for the DNS and e-mail protocols, and channel 2 is for the telnet TCP interface. Channel 3 is reserved as a UDP socket for broadcasting the message to other receiving modules for future expansion.

Once the hardware is ready, the main code restores the IP parameters from the EEPROM, sets the fixed hardware MAC address, and initializes the IP values in the W5100 chip. It is important to note that the W5100 chips don't come with MAC addresses. You can purchase them separately at www.ieee.org, as noted on WIZnet's FAQ page. I created one **Listing 1**—After initialization, a simple loop is used to check for three dif ferent events: a push button press, data in the telnet port, or a POP3 e-mail trigger .

```

// ----- main program -----

int main()

{

// initialize microcontroller

init();

// initialize IR system

IR_init();

// reset w5100

reset_w5100();

// initialize w5100

sysinit(0x00, 0x00);

// initialize MAC/IP layer with default values

// restore parameters from EEPROM

restore_parameters();

setSHAR(my_mac);

// set MAC address

// init IP values

init_ip();

// initialize telnet port

init_telnet();

// process cycle

systick = 0;

for (;;) {

// check if setup mode is requested

if (PUSH_BUTTON == 1)

setup_mode();

// check if telnet session

if (getSn_SR(SOCKET_TELNET) == SOCK_ESTABLISHED)

process_telnet();

if (email_hostname[0] && systick >= email_freq)

email process();

return 0;

}

```

for this demo, but please note that you need to obtain legal MAC addresses to be able to commercialize products with these chips. For the demonstration's sake, I just had to be sure that the selected MAC address didn't match any other MAC address in my lab.

```

nas@nvs:~/development/accontrol$ ls

makefile popchk popchk.c setip setip.c setip.c.old

nas@nvs:~/development/accontrol$ setip 172.16.2.255 000800ABCDEF 172.16.2.210 25

5.255.255.0 172.16.2.1 172.16.2.1

Sending message to broadcast IP: 172.16.2.255

MAC: 00:08:00:ab:cd:ef

IP: 172.016.002.210

NM: 255.255.255.000

GWY: 172.016.002.001

DNS: 172.016.002.001

message sent!

nas@nvs:~/development/accontrol$ ping 172.16.2.210

PING 172.16.2.210 (172.16.2.210) 56(84) bytes of data.

64 bytes from 172.16.2.210: icmp_seq=1 ttl=128 time=2.22 ms

64 bytes from 172.16.2.210: icmp_seq=2 ttl=128 time=0.095 ms

--- 172.16.2.210 ping statistics ---

2 packets transmitted, 2 received, 0% packet loss, time 1002ms

rtt min/avg/max/mdev = 0.095/1.161/2.227/1.066 ms

nas@nvs:~/development/accontrol$

```

**Photo 3**—The sample Linux set-up utility receives the following: the broadcast address of the PC and the MAC address of the device, the desired IP, the netmask, the gateway, and the DNS addresses. A UDP packet is broadcast addressed to port 9000, and it's captured by the ACcontrol's Raw mode, even if its IP doesn't belong to the current network.

The W5100's IP setup procedure is very simple, as you can see in the init\_ip routine. I first set the IP address by calling the W5100 driver setSIPR routine. The netmask is set with the setSUBR call and the gateway address configuration requires a call to the setGAR routine. Each IP address and netm ask is represented as a 4-byte array. The DNS address is saved in a local variable in the format required by the DNS search routines.

Finally, the initialization segment is completed by a call to the Telnet initialization routine, init\_telnet(). It opens a TCP socket in the W5100's preassigned SOCKET\_TEL-NET channel and sets it to listen mode. Please note that these calls are non-blocking. They just set the socket to listen. The actual packet "listening" is performed in the process\_telnet segment code where the socket is tested for data. If you are familiar with the sock et interface, you will realize that the WIZnet driver interface is similar to other operating systems like Unix. Some differences exist. In the current implementation, the programmer has to first check that there is data in a socket before calling the socket read routine (i.e., there is no select call and the read routines are non-blocking). This is needed because you don't want to stop the CPU waiting for a packet to arrive. You check for data, and if there is no data just continue to check other things. This technique is used a lot in embedded processing and avoids the need for a multitasking RTOS.

#### PROCESSING LOOP & SETUP

Refer to the main routine (see Listing 1). After initialization, the code is a simple loop that checks for a button press, a new connection to the telnet socket, or a received trigger e-mail. Each event produces a call to a corresponding routine. A button press event puts the device in set-up mode via the setup\_mode routine. A new telnet connection executes the process\_telnet code, which implements the telnet interface. Finally, if a new e-mail is detected, the email\_process routine activates the IR signal and sends you a reply e-mail.

Pressing the Set-Up mode push button activates the set-up routine. This makes the ACcontrol listen to a special UDP packet sent from a PC program that's designed to send the device IP configuration. In Set-Up mode, you execute a simple program to request the IP address, netmask, default gateway, and DNS IP and then send it to the network. But how can the ACcontrol, with no defined IP configuration, receive an IP packet?

Other devices on the market generally use DHCP or a fixed IP address for the initial contact. DHCP was undesirable for this case because it would be difficult for you or the set-up program to know the IP address required for the rest of the configuration. A fixed IP would force you to change the PC's IP to be able to communicate with the newly reset device. Thus, I decided to use another

-91

WaveSurfer<sup>®</sup>

200 MHz - 1 GHz

## 60 MHz - 1 GHz Starting from \$1,000

Experience the New LeCroy Oscilloscopes\*

WaveJet<sup>®</sup>

100 MHz - 500 MHz

Debug, verify, characterize, troubleshoot, analyze oscilloscopes do it all, but LeCroy's breakthrough oscilloscopes do more. More measurements, more math, and more time-saving tools to easily make measurements in even the most challenging situations.

WaveAce™

60 MHz - 300 MHz

\*To learn more about LeCroy's full line of oscilloscopes, including the 30 GHz WaveMaster 8 Zi, the world's fastest real-time oscilloscope, visit www.lecroy.com or call 1-800-5-LeCroy approach and experiment with the W5100 chip's Raw Socket mode.

Set-Up mode opens a socket in Raw mode. If you are unfamiliar with Raw Socket mode, think of it as a "promiscuous" (as it is called in some circles) Ethernet interface that captures every packet, even if it isn't directed to the device. In this mode, I checked for a specific UDP packet sent from the PC with the required IP configuration. When the ACcontrol sees it, it takes the information from the UDP packet body and sets itself accordingly. The previous IP configuration doesn't matter because this method always works (see Photo 3). The setup\_mode routine implements this as well as the IR learning and password reset functions.

For the IP configuration, there is a do-while loop in the code that checks for a packet arrival. It checks that it is an IP packet (0800 hex at the Ethernet-type field). Then it checks if it is a UDP packet directed to por t 9000 and if the packet is a special packet sensed by a magic number in

**Listing 2**—The IR\_send routine just replays the sampled transitions from the IR learning routine. The ir\_array contains the elapsed time between changes of the learned signal. If a signal must be modulated at 38 kHz for the duration of the transition, the most significant bit of the word is set to one.

```

// send the learned IR command

void IR send(void)

{

uint8 i, logic;

uint16 t;

for (i = 0; i < ir transitions; ++i) {

t = ir_times[i];

// get time

logic = (t & 0 \times 8000)?1:0:

// get logic

IRpulse(logic, (t&0x7FFF));

// send pulse

of the corresponding logic

}

// wait lead time

IRpulse(0, 2298);

}

```

its first data position. If everything is fine, the configuration is extracted from the packet, applied to the system, and the Set-Up mode is exited.

## INFRARED COMMANDS

Most of the IR commands for remote control consist of a pulse-

modulated 30- to 60-kHz signal. (Note that 38 kHz is the most common.) Although different protocols exist for embedding a command in the signal, what I wanted was just to learn a single command—the power On/Off signal—and then be able to replay it when needed. The system

Website: http://www.machinepier.com

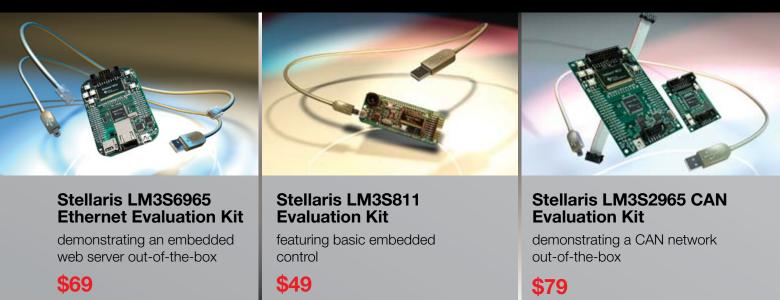

# Stellaris®

## **Connected. Versatile. Cost-effective.**

Stellaris LM3S9B90 **Ethernet Evaluation Kit**

featuring USB, Ethernet and CAN

## **\$99**

Stellaris LM3S8962 **Evaluation Kit** featuring integrated Ethernet and CAN

**\$89**

Stellaris LM3S3748 **Evaluation Kit** featuring USB Host/Device

## \$109

## Deterministic ARM<sup>®</sup> Cortex<sup>™</sup>-M3 cores **Stellaris® Means:**

- Real-time multi-tasking MCUs

- Advanced interrupt-driven software with Stellarisware<sup>®</sup> software

doesn't need to understand the data in the signal (i.e., decoding isn't needed), so it's simple to sample the signal and record the time lapses between signal changes. This will accommodate any protocol.

Replaying the "learned" IR signal is also easy. Just perform the modulation at the previously recorded time. As I already mentioned, I used a 38-kHz IR module that filters th e signal and converts it to a logic 1, where a 0 is when modulation is present and a 1 other wise. This signal is connected to the dsPIC30F4012's CN3 pin.

IR routines are included at the end of the ACcontrol.c source code file available on the Circuit Cellar FTP site. The IR\_capture routine starts the interrupt at CN3 and resets the internal counters and variables that record the signal. The time between interrupts are saved into the ir\_times variable. IR\_stop stops the recording. Actual sampling and recording occur at the CN3 state change interrupt-handler routine called \_CNInterrupt. In each logic state, the change of the CN3 input pin is recorded together with the time from the last interrupt. The signal recording stops when the array storage is filled or if no signal is received in 20 ms, as set in the IR\_init routine. The fifteenth bit in each value in the ir\_times array records the state at the capture: one if there was modulation, zero if there wasn't.

The IR\_send routine is much simpler (see Listing 2). An iteration covers all the words in the ir\_times array, checking the fifteenth bit or the modulation state and sending an IR signal for the recorded time. This is for all the learned transitions, thus replaying the signal exactly as it was sampled. The IRpulse function sends the required 38-kHz signal to the dsPIC30F4012's output pin using the previously configured PWM module.

#### TELNET INTERFACE

The telnet interface is one of the most complex components of the ACcontrol project. Interactivity complicates things. Processing starts nas@nvs:-/development/accontrol\$ telnet 172.16.2.210 9000 Trying 172.16.2.210... Connected to 172.16.2.210. Escape character is '^]'. ACcontrol v1.0 system password: Logged! POP3 hostname: pop. .net POP3 username: naubert POP3 password: notification email address: naubert.aparicio@usa.net SMTP server: mail. .net activation string: AC:ON quit connection now or enter parameters: hostname:

**Photo 4**—Once the device IP is set through the PC set-up program, you can connect via telnet to the 9000 port in the device to set the rest of the parameters: the POP3 account, the username, the password, the e-mail address that will receive the activation reply e-mail, the SMTP server where e-mails are to be sent, and the subject that will activate the infrared signal. You can also change the telnet password from the default "password" string.

when a connection is received at port 9000. The main program calls the process\_telnet routine, which first checks that the connection is established and monitors it in case you or the connection fails during the telnet session (closing the socket in that case). When the connection and password prompt is sent, the telnet command IAC WILL ECHO is also sent, causing the telnet client to turn off its local echo so that the password isn't visible on the screen.

The telnet routine then waits until the getSn\_RX\_RSR function returns notification that data is available at the receiving buffer. Text processing filters the telnet protocol control characters and buffers a complete line before analyzing it. A finite state machine performs the interface actions in order. First, it gets the password and then asks for the POP parameters, enabling a subject string and a new password. Photo 4 shows the interaction. Using a finite state machine and moving from state to state simplified the coding because the software was not implemented in an RTOS. You can interrupt the telnet session at any time. Only the changed parameters are saved in the EEPROM.

### **E-MAIL COMMUNICATIONS**

The email\_process routine is the main ACcontrol function. The main

code calls it periodically. It just checks if there is an activation email from the POP3 account. If there is, it activates the IR signal and sends a reply e-mail confirming the command. To check the POP3 account, it calls the check\_email routine. This routine establishes a new TCP connection to the POP3 standard port at the server specified in the telnet configuration session. Once connected, it logs into the POP3 account sending the POP3 commands USER and PASS. If the log-on is successful, the routine requests the number of e-mails with the STAT command and then loops through the e-mails scanning the subjects to check for the activation substring. If a subject contains it, the scan email routine sends the DELE command to delete that single mail and it signals the calling program that the IR command must be sent. This is received by the email\_process routine, which then calls the IR send command, turning on or off the air conditioning equipment. It also calls the send email routine to send you a reply e-mail. This last routine uses SMTP commands to send a reply address to the registered address through the telnet configuration session. Like the check email routine, it establishes a new TCP connection to the SMTP port at the registered

mail server, authenticates it by sending the HELO command, and sends the e-mail using the MAIL FROM, RCPT TO, and DATA commands via the network connection. This implementation requires that the SMTP accepts an anonymous session.

#### DESIGN SUCCESS

This project took just 20 days, as you can see in the log included with the source code posted on *Circuit Cellar* FTP site. The WIZnet module and its W5100 hardwired TCP/IP chip really simplified the programming process. They provided a highlevel socket interface with raw socket processing to a lower-end microcontroller.

I now have a working design for controlling my air conditioner with my cell phone. Plus, I can say I have a great networked embedded hardware design project under my belt. Now it's your turn to design a similar project of your own.

Naubert Aparicio (naubert.aparicio@usa. net) is a computer science engineer with a degree from the Simon Bolivar University in Venezuela. As the technology director for Quantum Business Engineering in Puerto Rico, he manages design-critical Unix system architectures. In his free time, Naubert enjoys researching topics such as robotics, advanced digital design, and embedded systems.

## PROJECT FILES

To download the code and a list of useful resources, go to ftp://ftp. circuitcellar.com/pub/Circuit\_ Cellar/2009/231.

## Resources

——, "TSOP321: IR Receive Modules for Remote Control Systems," 82229, 2007.

Microchip Technology, Inc., "dsPIC30F4011/4012 Data Sheet: High-Performance 16-bit Digital Signal Controllers," DS70135D, 2007. WIZnet, "WIZ810MJ Datasheet," Version 1.0. 2007, www.circuitcellar.com /Wiznet/WIZ810MJ%20Datasheet\_V\_1.0.pdf.

## OURCES

dsPIC30F4012 DSC Microchip Technology, Inc. | www.microchip.com

#### Ethernet WIZ810MJ module

WIZnet, Inc. | www.wiznet.co.kr/en/

**TSAL7400 Infrared-emitting diode and TSOP321 modules** Vishay Intertechnology, Inc. | www.vishay.com

## It takes more than a top program to win the **Product of the Year Award**<sup>\*</sup>

#### five times running

- For instance, reasonable prices without hidden costs.

- A fair update policy without mandatory maintenance fees or costly add-on contracts.

- A competent hotline available free of charge for every customer.

- A program development and optimization process based on an open discussion with the users.

In other words: EAGLE is one of the world's highest rated schematic capture and PCB-board layout packages because for the last twenty years we have been treating our customers the way we would like to be treated ourselves.

An example:

In the course of product development we implemented a

#### Follow-me Router

which saves an enormous amount of time during the manual routing process. This new function is available free of charge to every customer as are all new features within a main EAGLE release. In this particular case you need to have the autorouter module of version 5.

## Pick the level that is right for you — pay only the difference for upgrades!

|                                                         | Light      | Standard   | Professional |

|---------------------------------------------------------|------------|------------|--------------|

| Max. number of schematic sheets                         | 1          | 99         | 999          |

| Max. board size                                         | 4x3.2 inch | 6.4x4 inch | 64x64 inch   |

| Max. # of signal layers                                 | 2          | 4          | 16           |

| Layout or<br>Schematic Editor                           |            | \$249      | \$498        |

| Layout and<br>Schematic Editor                          |            | \$498      | \$996        |

| Layout Editor and<br>Autorouter                         |            | \$498      | \$996        |

| Layout Editor and<br>Schematic Editor<br>and Autorouter | \$49       | \$747      | \$1494       |

CadSoft Computer, Inc., 19620 Pines Blvd., Suite 217, Pembroke Pines, FL 33029 Hotline (954) 237 0932, Fax (954) 237 0968, E-Mail: info@cadsoftusa.com Windows / Linux / Mac are registered trademarks of Microsoft Corp. / Linus Torvalds / Apple Computer, Inc.

Version 5 Schematic - Layout - Autorouter for Windows<sup>®</sup> Linux<sup>®</sup> Mac<sup>®</sup>

Annual award of the leading German electronics magazine. The winners of eleven categories are determined by the reader's votes.

Standard and Light Editions have full functionality except for the limitations mentioned in the table.

You can use EAGLE Light for evaluation and non-commercial applications without charge. Download it from our web site.

www.cadsoftusa.com 800-858-8355

## INTELLIGENT ENERGY SOLUTIONS

## Frequency Sensing Made Simple Power Grid Frequency Monitor Design

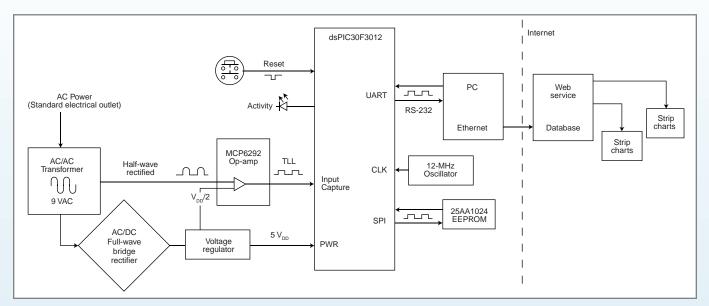

This power frequency monitor indicates the relative stability of a power grid. Built around a microcontroller, a precision crystal oscillator, an op-amp, and various passive components, the design measures power grid frequency via a standard electrical outlet. It then sends the data to a PC, displays the information, and relays it to a web server for real-time monitoring.

## by Arnold Stadlin

n indicator of a power grid's health is its ability and agility to respond to changes in the supply and demand of electricity. Measuring the stability of a power grid's frequency is an easy method for monitoring its health. Although there are other measurable grid characteristics, frequency is ubiquitous across the grid and less affected by local disturbances than other attributes like voltage and current.

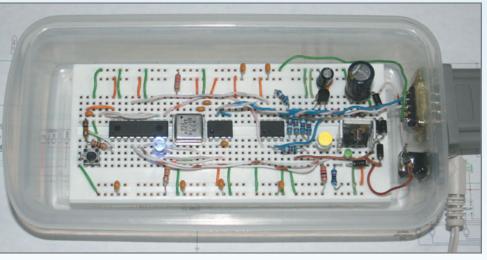

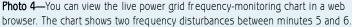

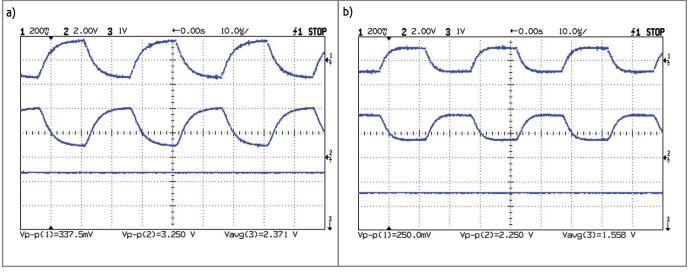

"PHzMonitor" is a short name I affectionately use to refer to this project and its frequency sensor (see Photo 1). The PHzMonitor frequency sensor consists of a Microchip Technology dsPIC30F3012 microcontroller, a precision crystal oscillator, an op-amp, and various passive components (see Figure 1). The sensor measures the power grid frequency from a typical electrical outlet scaled down to less than 12 V b y an AC/AC transformer (see Photo 2). A PC communicates with the PHzMonitor via its RS-232 serial port. Software on the computer displays the frequency measurements and optionally relays the data to a web ser ver for live public viewing. You can save the data to disk via the PC software or download it from the web ser ver for offline analysis.

## FREQUENCY MEASUREMENT

Let's review how the PHzMonitor measures power grid frequency. There are five steps in the process.

Step one: Use an AC-to-AC transformer to scale the stan-

dard electrical outlet voltage down to a safe level for your components. You need the AC voltage to be between 9 to 12 VAC. Step 2: Rectify the AC waveform to a half wave using diodes. Step three: Scale the AC half waveform to a safe level for op-amp input using voltage divider resistors. Step four: Create a square waveform from the half wave using a DC reference voltage and an op-amp in a railto-rail configuration. The opamp outputs the amplified difference between the AC voltage and the DC reference voltage as 0 to 5 VDC. Step five: Use a crystal oscillator-driven microcontroller to measure the periodic cycle

Photo 1—The PHzMonitor project is a useful, scalable system. Networked sensors along with the Internet enable you to monitor frequency conditions in a power grid. You can also compare the performance of different grids.

Figure 1—The PHzMonitor project includes a sensor input, microcontroller, computer, and web server components.

timespan by counting the number of oscillator cycles between the leading edges of the square wave.

#### **DESIGN & CONSTRUCTION**

I'll be honest. I jumped into the design and construction of the PHzMonitor sensor *before* doing my homework! The sensor design concept is simple: convert alternating current to a square wave and then use a microcontroller to count timer ticks between leading edges of the digital signal. The concept for measuring the frequency of a square wave is similar to measuring the motion velocity of a quadrature encoder signal. The design concept is heavily biased toward this method because I was involved in a robotics project at the time.

What makes the PHzMonitor sensor unique is that it measures frequency at an arbitrary 2.5-VDC reference voltage level instead of measuring at the zero crossings. I used a reference voltage for two fundamental reasons. One, it's easier (for me, at least) to measure a voltage reliably than it is to measure no voltage reliably. Two, the cyclic nature of the power signal being measured enables me to set a voltage reference between logic level voltages

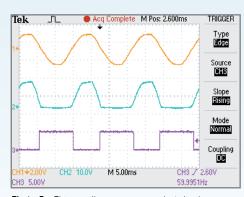

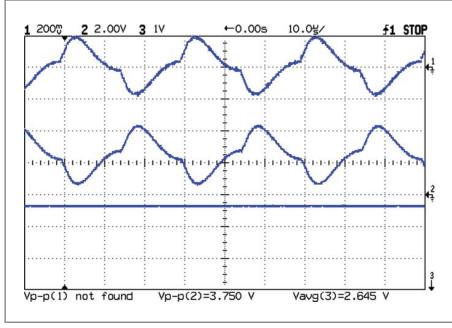

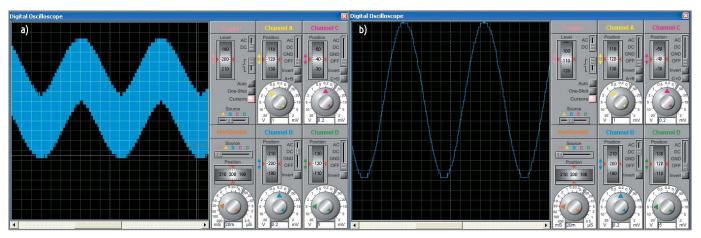

**Photo 2**—This oscilloscope screenshot displays (from top to bottom) the input AC sine wave, the rectified half wave, and the amplified 5-V square wave prepared for measurement.

and amplify the comparative results with acceptable accuracy.

The design uses a 9-VAC transformer for power and sensor input. The 5-VDC power supply for the integrated circuit components is tapped from the AC power input using a standard full-wave bridge rectifier, a linear voltage regulator, and an electrolytic capacitor. The half-wave signal samples are simply the resultant, complimentary, half-wave forms from the rectifier's inputs. The current design uses a dual-channel op-amp. If you really want to measure frequency at the zero crossings, the complementary half-wave forms can be used for calculating the zero-crossing point between two reference voltage comparisons. Both half-waves are positive, and both use the same reference voltage, so the zero-crossing time is one-half the time between the leading edges. Did I not mention that it is more difficult for me to measure no voltage?

I used a Microchip Technology MCP6292 op-amp in the sensor. I chose it for two reasons: it is designed to operate in 0- to 5-V rail-to-rail mode, and it has a high speed of 10 MHz. The 16-bit dsPIC30F3012 microcontroller has a built-in input capture peripheral, which is ideal for measuring the timespan of a periodic digital signal. This device has a generous 24 K B of program memory, 2 KB of RAM, and 1 KB of flash EEPROM. The dsPIC30F3012 is available in an 18-pin parallel dual inline packaging as well as surface-mount packaging.

A Fox H5C-2E 12-MHz crystal oscillator drives the microcontroller. The 12-MHz oscillator frequency was selected because it can be evenly divided by both 60 Hz and 50 Hz frequency values. A Maxim Integrated Products DS275 RS-232 transceiver is used for communications with a PC. A National Semiconductor LM340T5 (7805) linear voltage regulator is used to provide the integrated circuit component power. A Microchip Technology MCP1525 provides the 2.5-V reference. Other components include resistors, capacitors, silicon diodes, LEDs, and a push button for reset. The project is assembled on a 2" × 4" prototype board packaged in a plastic container.

#### PROGRAMMING

The PHzMonitor's dsPIC30F3012 microcontroller is programmed with the Microchip C30 compiler. The programmed firmware configures an input capture timer to accumulate clock ticks in a 16-bit register. A high-priority ISR executes when an INPUT pin detects the leading edge of the square wave. This routine copies the input capture timer's register value to a RAM variable for program loop processing and clears the register. A normal priority ISR receives an RS-232 command byte and copies it to a RAM variable for program loop processing. The main program loop polls the RAM for command bytes recorded by the RS-232 routine. When a command is found, the main loop processes the command's procedure and repeats the loop.

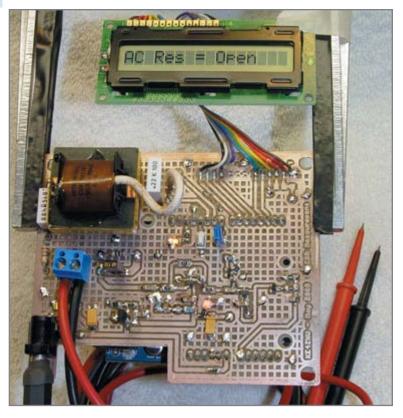

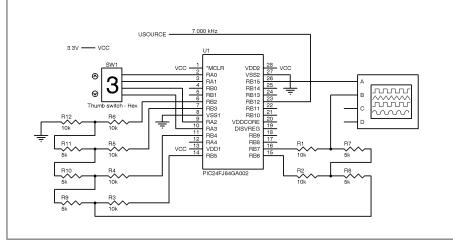

Figure 2—A dsPIC30F3012 sits at the heart of the PHzMonitor design. I used a Fox H5C-2E 12-MHz crystal oscillator to drive the microcontroller.

The PHzMonitor is

programmed to respond to single byte command constants. There are only three commands. PING transmits the device's unique identification number and firmware version. TRANSMIT sends a data packet containing a start byte, 16-bit packet identifier, 16-bit last measurement, 16-bit average of the last 10 measurements, and a stop byte. DIAGNOSTIC transmits a continuous bitstream for RS-232 timing measurements.

The computer sends the PING command to verify that it is connected to the device and to get the device's unique identification number. When the computer is ready to receive data, it sends the TRANSMIT command. The device responds to the TRANSMIT command by sending a data packet. The computer software is programmed to transmit the commands in a separate thread from receiving and processing the data packets. This asynchronous flow permits the computer to perform various tasks like charting the data and responding to user input at the same time it is obtaining data from the device.

The computer's clock needs to be synchronized with a National Institute of Standards and Technology Internet time server (http://tf.nist.gov/service/its.htm). When the data packet is received, the computer software assigns it a timestamp before charting the data, saving it to disk, or relaying it to the webserver. This places the timestamp close to the data collection time. Using a command-driven protocol improves the communications because the requests for data can be transmitted by the computer when it is ready to respond to receiving the data. The

computer can record the timestamp when it receives the data packet with minimal variance in latency between the actual time the sample is recorded and when the timestamp is applied to the data. The data is always the very last sample taken and the data packets are a fixed number of bytes transmitted at a fixed data rate.

### **CYCLE PERIOD & FREQUENCY**

The dsPIC30F3012 microcontroller oscillator configuration settings enable you to tune the instruction timing by setting a phase-locked loop (PLL) frequency multiplier. The resulting processor frequency, used by the programmable timers, can be prescaled to reduce the timer ticks frequency. To improve the precision of measurement, you need to select a processor frequency that enables you to measure frequency comfortably for both 60 and 50 Hz using a 16-bit unsigned integer value (0 to 65535).

A timer tick's length is four oscillator cycles. If you use a PLL multiplier of four to drive the microcontroller at 48 MHz , the following two equations provide the timer tick counts for 60 and 50 measurements using a timer prescale divider of eight.

$$\frac{\left(\frac{1 \text{ s}}{60}\right) \times 12,000,000 \text{ ticks/s}}{8} = 25,000 \text{ ticks for a 60 period}$$

$$\frac{\left(\frac{1 \text{ s}}{50}\right) \times 12,000,000 \text{ ticks/s}}{8} = 30,000 \text{ ticks for a 50 period}$$

The following formula converts the clock tick count to

# Pick a Chip. Any Chip.

Find a Solution to your next Embedded Challenge. Do the Research you should, but never had time for.

Embedded Developer's intuitive research engine helps you speed your chip evaluation time. You don't have to know the manufacturer, chip family or part number--just select the features you want and let us do the rest.

| Processors - All    | -        | Any AD       | <b>N</b> | EEPROM              | Any Core Architecture |

|---------------------|----------|--------------|----------|---------------------|-----------------------|

| Any Manufacturer    | ~        | Any I2C      | <b>~</b> | D/A                 | Any Part Family       |

| Any Instruction Set | ~        | Any CAN      | <b>~</b> | Encryption          | Any Tool Type 😽 😽     |

| Any Frequency       | <b>v</b> | Any Ethernet |          | Internal Oscillator | Any Tool Provider 🛛 🗸 |

| Any Flash/ROM       | ~        | Any USB      | <b>•</b> | LCD Controller      | Reset Search          |

| Reset               |          | Any PCI      | ×        |                     | 2 3872-65870118       |

|                     |          | Any DDR      | ~        | Search              |                       |

| Part Number    | AT91SAM7X | MCF5208     | LPC2923   |  |

|----------------|-----------|-------------|-----------|--|

| Manufacturer   |           | Freescale   | NP        |  |

| Core Variant   | ARM7TDMI  | ColdFire V2 | ARM968E-S |  |

| Flash          | 262144    | 0           | 262144    |  |

| RAM            | 65536     | 16384       | 16384     |  |

| Max. Freq.     | 55        | 166         | 125       |  |

| Dhrystone MIPS | 50        | 159         | 156       |  |

| Timer Bits     | 16        | 32          | 32        |  |

We help you research your best option. Nowhere else can you compare your best options side-by-side from different manufacturers. Click on the device you want, and a product page lets you select Distributor Buy/Quote options, send RFQs, download datasheets, and more. Plus--Hearst stock check gives you up-to-date inventory on every device.

frequency in hertz.

$$\frac{\text{counted ticks} \times 60}{25,000 \text{ ticks}} = \text{calculated}$$

You're also able to compare power grids with both 60- and 50-Hz nominal frequencies. You can normalize the data to a percentage deviation from the nominal frequency using the following calculation.

$$\frac{100\% \times \text{[measured frequency - nominal frequency]}}{\text{nominal frequency}} = \text{deviation \%}$$

Using this calculation, you can compare power grid frequency data. For example, you can compare New Zealand's 50 frequency (www.systemoperator.co.nz/power-system-overview) to the 60 frequency measured in the United States.

### **ASSEMBLY & TESTING**

Working with prototype boards is fun. But getting the prototypes to actually work can be a challenge. When building a prototype board assembly, it's good to keep the wiring short, neat, and color-coded. I like using category 5 solid conductor cable wire that gives me eight colors to work with. The convention I follow is to use the solid colors for power and voltage wires: green for ground, orange for 5 VDC, brown for rectified AC, and blue for the 2.5-V DC reference voltage. I use the white/color wires for wires carrying signals like RS-232 and LEDs. When trimming leads on resistors, capacitors, and other components, it is good to cut them to consistent lengths. Component leads of 0.5" work well for this project.

The PHzMonitor's complete circuitry is shown in Figure 2. After the circuit is assembled and double-checked, the AC transformer is connected and the prototype is ready for programming and testing.

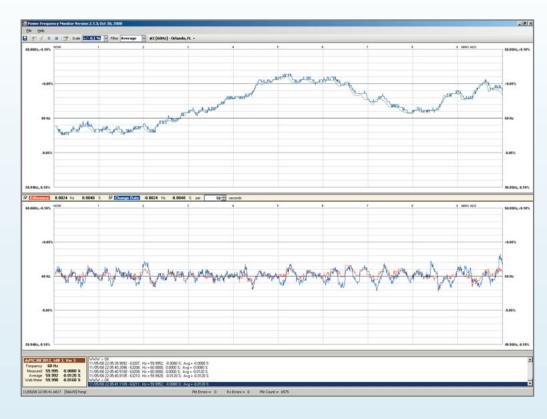

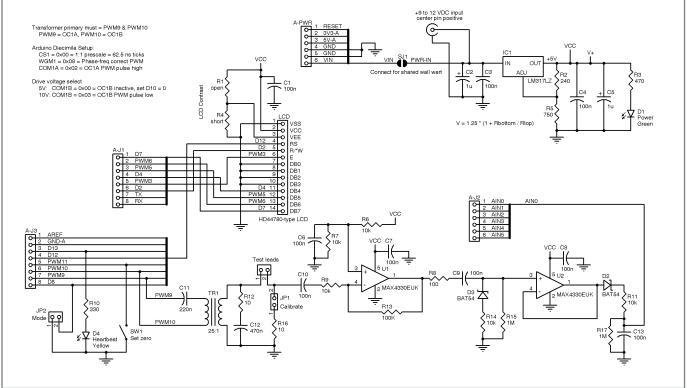

**Photo 3**—Frequencies are displayed in the top chart. Frequency change and differences are plotted in the lower chart. The bottom of the screen displays a running activity log and various operational indicators.

The firmware source code is posted on the Circuit Cellar FTP site. After the firmware is programmed, the PHzMonitor produces a 60-Hz pulse-width-modulated, 50% duty cycle, square wave output on pin 10. This 60-Hz signal can be connected to the op-amp input and used for calibrating the system if no other known frequency calibration signal source is available. Two LEDs should be active. The Power LED is on when the device has power. A large

red/green activity indicator LED is toggled between on and off with each program loop pass. If the measured frequency is within  $\pm 1$ % of the programmed nominal frequency, the red/green activity indicator pulses green. If the frequency is outside of the  $\pm 1$ % tolerance, the activity indicator pulses red. The process loop performance can be measured from the activity indicator signal pulses using an oscilloscope.

## **COMPUTER SOFTWARE**

After ensuring the device is functional, the next step is to connect it to the computer's RS-232 port and then load and run the computer software. The computer software for this project was developed using the Microsoft C# programming language, the readily available Visual Studio Express 2008, and .NET Framework development tools. The Microsoft Visual Studio Express editions are free download versions of the Visual Studio development tools. The source code for this project is available on the *Circuit Cellar* FTP site.

Photo 3 is a screenshot of the computer software with local sensor measurement frequency. A selected remote frequency is displayed in the top chart. The difference and rate of change between the two frequencies are plotted in the lower chart. The bottom of the screen displays a r unning activity log and various operational indicators.

### MONITOR VIA THE 'NET

There are currently multiple sources for grid frequency information. I created a new source! When the frequency sensor and computer are connected to the Internet, the data can be relayed to a web server where people from around the world can view the data live and download it for off-line analysis. The implementation details for setting up the web server for this project are beyond the scope of this ar ticle.

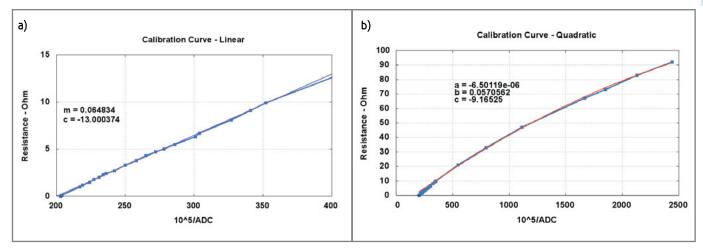

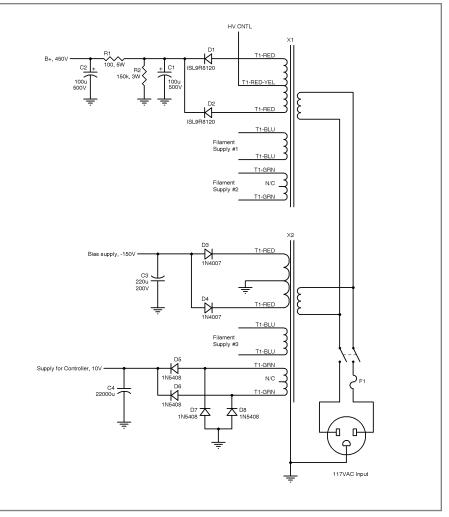

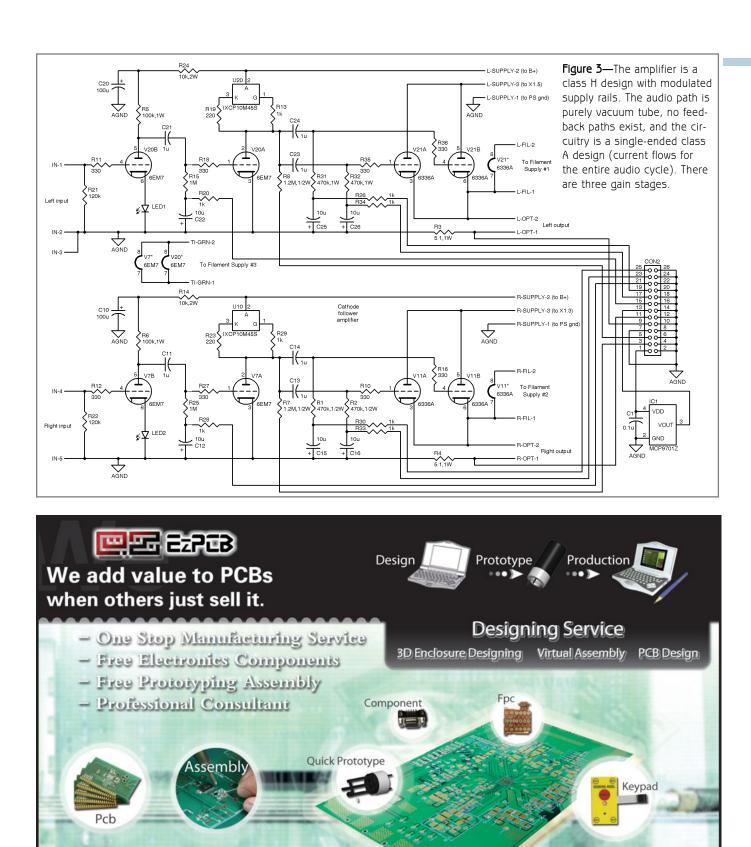

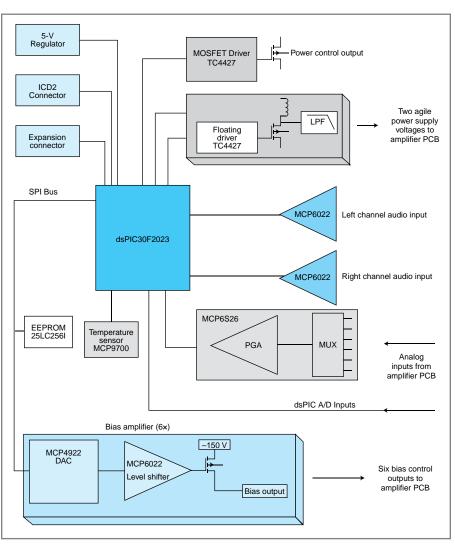

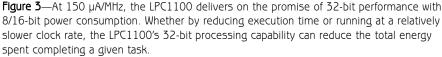

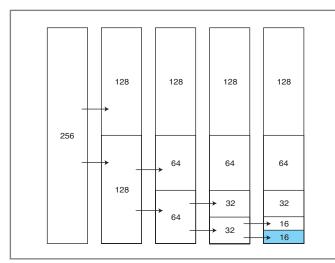

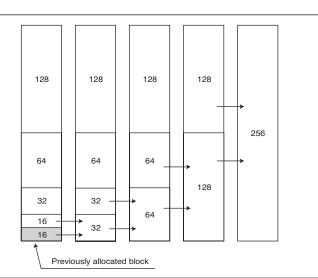

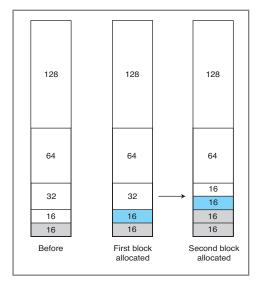

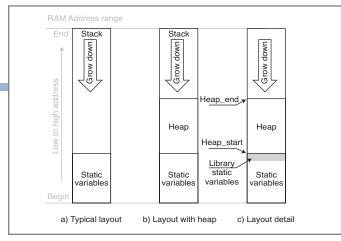

However, the source code and database schema are available in the PHzMon\_Web.zip file on the *Circuit Cellar* FTP site.