USB JTAG Module p. 24 • DOS in the 21<sup>st</sup> Century p. 36 • Bridge the Gap Between NTSC and VGA p. 52 COMPUTER APPLICATIONS

#226 May 2009

dB

BATT

# **MEASUREMENT & SENSORS**

MCU-Based SLA Battery Measurement

Modern DSP Technology

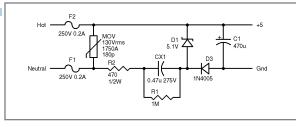

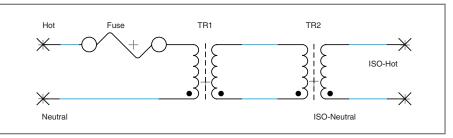

Transformerless Power Supply

C Code for a FAT File System

# **SECURE SERIAL-TO-ETHERNET SOLUTION**

# Low-cost

# 32-bit Performance

# SSH/SSL Secured

#### Need a custom solution?

Customize with the NetBurner SB70LC Development Kit for only \$99.

Customize any aspect of operation including web pages, data filtering, or custom network applications.

Kit includes: platform hardware, ANSI C/C++ compiler, TCP/IP stack, web server, e-mail protocols, RTOS, flash file system, Eclipse IDE, debugger, cables and power supply

Kit enables communication with peripherals that use: SD/MMC Flash Card (including SDHC), SPI, I<sup>2</sup>C, or the general purpose digital I/O interface

The NetBurner Security Suite Option includes: SSH v1, v2 and SSL support

# The complete, secure hardware and software solution

- Simple Ethernet connectivity for serial devices

- Works out of the box no programming is required

- Enable data encryption to prevent unauthorized monitoring

- Customize to suit any application with development kit

#### Features:

- 10/100 Mbps Ethernet

- SSH/SSL/TCP/UDP modes

- DHCP/ Static IP support

- Web-based configuration

- Two TTL serial ports

etBurner Networking in One Day!

Board Part Number | SB70LC-100CR Development Kit Part Number | NNDK-SB70LC-KIT Information and Sales | sales@netburner.com Web | www.netburner.com Telephone | 1-800-695-6828

# **5** Competitive Advantages

#### Overseas Manufacturing

Imagineering, Inc. enjoys the reputation of being one of the most experienced & successful offshore PCB suppliers.

#### CAM USA

Our Illinois based DFM office has eight fully staffed CAD / CAM stations. Within hours of receipt of new Gerber files, our highly experienced DFM engineers conduct thorough and precise analyses.

#### **Quick-Turn Production**

Imagineering offers small volume production in 5-6 days and medium to large volume production in 2-3 weeks.

#### Overseas Manufacturing

#### **Shipping Logistics**

With Imagineering there is no need to deal with multiple suppliers, language barriers, customs headaches, and shipping logistics. We do it all for you ..and deliver door-to-door

Significant Price Saving

Our global buying power combined with the capabilities of our overseas manufacturers translate into tremendous savings to our customers. Quick-Turn Production

## CAM USA

Door to Door Delivery

#### Significant Price Saving

For details please visit our website or call us Up to 30 Layers Blind Buried Vias Di-Electric Thickness Impedance Control (TDR Tested) Plated Edge Holes Up to 6oz Copper 6 mil Laser Drill 3 mil line width/spacing Conductive Epoxy Filled Vias Aluminum Metal Core Boards ...and many others

Capabilities

ITAR, ISO 9001 : 2008

Over the past 5 years, 70,000 prototypes have been successfully delivered from overseas to over 5000 customers

eering inc. 847-806-0003

www.PCBnet.com

email: sales@PCBnet.com

## 24 YEARS IN BUSINESS ... AND STILL GOING STRONG

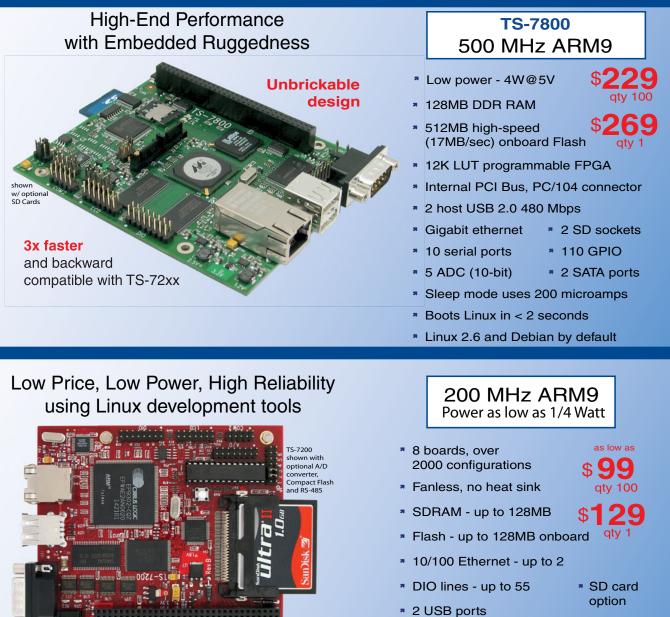

# **Embedded Single Board Computers**

options include: onboard temperature sensor, A/D Converter 8 channel 12 bit, Extended Temperature, Battery Backed Real Time Clock, USB Flash, USB WiFi

- Over 20 years in business

- Open Source Vision

- Never discontinued a product

- Engineers on Tech Support

- Custom configurations and designs w/ excellent pricing and turn-around time

- Most products stocked and available for next day shipping

Design your solution with one of our engineers (480) 837-5200

- VGA video COM ports- up to 10

- LCD ready Programmable FPGAs

- Linux, Real Time extension, Debian

# Featured Products and PC/104 Peripherals

**Technologic**

We use our stuff. Visit our TS-7800 powered website at

www.embeddedARM.com

8x oversampling 500m/1000m 1 ms timing 100mph

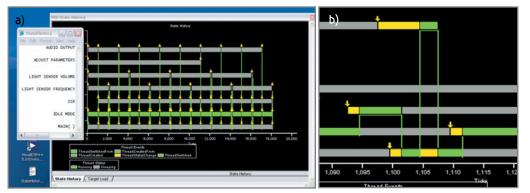

60hz update Sensor calibration **Bonus Video Portal:** Circuit Cellar recurring author Chris Coulston presents the first installment of the DIY guide to building a Goldsprints racing system.

*Circuit Cellar video from the* 16<sup>th</sup> annual Trinity College Fire Fighting Home Robot Contest 2009.

## Sponsor Events – click to see video

**Upcoming Microchip MASTERS 2009**

#### Old Tech, New App

t first glance, this issue looks more like one you would've read in the mid-'90s rather than in mid-2009. The topics of DOS, sealed lead-acid (SLA) batteries, NTSC, C code, digital signal processing, DIY power supplies, and JTAG don't really scream "cutting-edge technology!" But when presented by *Circuit Cellar* authors who spend their days and nights dreaming up innovative embedded apps, they don't scream "old school ideas" either. Yes, we're up to something here.

Basically, we've assembled a group of articles about new ways of developing and tweaking proven older technologies to meet modern design goals. For instance, on page 16, Dale Wheat describes an MCU-based meter he built for SLA battery charge testing. DJ Delorie finishes his USB GPIO pod series with information about downloading a JTAG programming application to program a CPLD circuit (p. 24). In "DOS in the 21st Century," Andrew Mitz and Jon Daley explain how they use DOS as an operating system for embedded applications (p. 36). Turn to Tom Struzik's article on page 44 to learn how he saved money by using a transformerless power supply, rather than expensive transformers or converters, in a recent light switch design project. On page 52, Jeff Bachiochi describes how he uses a Propeller to live in a world without NTSC. After saying farewell to NTSC, check out George Martin's article about C code for the FAT file system (p. 60). Tom Cantrell ends the issue with an article about new ways for tackling DSP apps (p. 65). The part he presents "isn't your father's DSP."

Just so I don't feel left out, let me describe a new twist on an old technology. It is called *Circuit Cellar Digital Plus*, which is the newest version of *Circuit Cellar*'s ever-evolving electronic edition. I encourage all *Circuit Cellar* readers to give *Digital Plus* a try! Here's a short intro to *Digital Plus*:

1. *Digital Plus* is a replica of the print magazine in digital form, "plus" it includes digital-only extras like bonus articles, tutorials, videos, photos, advertisements, interviews, and more.

2. You can easily view *Digital Plus* in two ways. One, view it through an online flip book reader, which does not require special software downloads. Click on the "?" icon to get instructions about using the flip reader. Two, download each issue as an easy-to-print PDF. Simply click on the "Adobe Acrobat" icon to download the PDF.

3. An e-mail will notify *Digital Plus* subscribers when a new issue is available. New issues (and some old) are posted at www.circuitcellar.com/DP/.

If you want to subscribe to *Digital Plus*, renew a subscription, or update your information, feel free to visit www.circuitcellar.com/DP at any time. Enjoy!

cj@circuitcellar.com

C.Abita

# CIRCUIT CELLAR®

FOUNDER/EDITORIAL DIRECTOR Steve Ciarcia

MANAGING EDITOR C. J. Abate

WEST COAST EDITOR Tom Cantrell

CONTRIBUTING EDITORS Jeff Bachiochi Ingo Cyliax

Ingo Cyliax Robert Lacoste George Martin Ed Nisley

NEW PRODUCTS EDITOR John Gorsky

PROJECT EDITORS Gary Bodley Ken Davidson David Tweed CHIEF FINANCIAL OFFICER Jeannette Ciarcia

> MEDIA CONSULTANT Dan Rodrigues

CUSTOMER SERVICE Debbie Lavoie

> CONTROLLER Jeff Yanco

ART DIRECTOR KC Prescott

GRAPHIC DESIGNERS Grace Chen Carey Penney

> STAFF ENGINEER John Gorsky

ADVERTISING

860.875.2199 • Fax: 860.871.0411 • www.circuitcellar.com/advertise

PUBLISHER Sean Donnelly

Direct: 860.872.3064, Cell: 860.930.4326, E-mail: sean@circuitcellar.com

ADVERTISING REPRESENTATIVE Shannon Barraclough Direct: 860.872.3064, E-mail: shannon@circuitcellar.com

ADVERTISING COORDINATOR Valerie Luster E-mail: val.luster@circuitcellar.com

Cover photography by Chris Rakoczy—Rakoczy Photography www.rakoczyphoto.com PRINTED IN THE UNITED STATES

CONTACTS

SUBSCRIPTIONS Information: www.circuitcellar.com/subscribe, E-mail: subscribe@circuitcellar.com Subscribe: 800.269.6301, www.circuitcellar.com/subscribe, Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-5650 Address Changes/Problems: E-mail: subscribe@circuitcellar.com GENERAL INFORMATION 860.875.2199, Fax: 860.871.0411, E-mail: info@circuitcellar.com

Editorial Office: Editor, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: editor@circuitcellar.com New Products: New Products, Circuit Cellar, 4 Park St., Vernon, CT 06066, E-mail: newproducts@circuitcellar.com AUTHORIZED REPRINTS INFORMATION

- 860.875.2199, E-mail: reprints@circuitcellar.com AUTHORS

- Authors' e-mail addresses (when available) are included at the end of each article.

CIRCUIT CELLAR®, THE MAGAZINE FOR COMPUTER APPLICATIONS (ISSN 1528-0608) is published monthly by Circuit Cellar Incorporated, 4 Park Street, Vernon, CT 06066. Periodical rates paid at Vernon, CT and additional offices. One-year (12 issues) subscription rate USA and possessions \$23.95, Canada/Mexico \$34.95, all other countries \$49.95. Two-year (24 issues) scription rate USA and possessions \$43.95, Canada/Mexico \$36, \$31 other countries \$49.95. Two-year (24 issues) U.S. funds only via Visa, MasterCard, international postal money order, or check drawn on U.S. bank. Direct subscription orders and subscription-related questions to Circuit Cellar Subscriptions, P.O. Box 5650, Hanover, NH 03755-5650 or call 800.2696.501.

Postmaster: Send address changes to Circuit Cellar, Circulation Dept., P.O. Box 5650, Hanover, NH 03755 5650.

Circuit Celiar® makes no warranties and assumes no respons billy or liability of any kind for errors in these programs or schematics or for the consequences of any such errors. Furthermore, because of possible variation in the quality and condition of materials and workmanship of read erassembled projects. (Cruit Celar® disclaims any responsibility for the safe and proper function of reader-assembled projects to assore disclaims any responsibility for the safe and proper function of reader-assembled projects based upon or from plans, descriptions, or information published by Circuit Cellar®.

The information provided by Circuit Cellar® is for educational purposes. Circuit Ce lar® makes no claims or warrants that readers have a right to build things based upon these ideas under patent or other relevant intellectual property law in their jurisdiction, or that readers have a right to construct or operate any of the devices described herein under the relevant patent or other intellectual property law of the reader's jurisdiction. The reader assumes any risk of infringement lability for constructing or operating such devices.

Entire contents copyright © 2009 by Circuit Cellar, Incorporated. All rights reserved. Circuit Cellar is a registered trademark of Circuit Ce Iar, Inc. Reproduction of this publication in whole or in part without written consent from Circuit Cellar Inc. is prohibited.

With compilers that cut power consumption

# Your MCU can go green!

featuring Omniscient Code Generation<sup>™</sup> (OCG)

OCG is a new whole-program compilation technology that cuts power consumption by reducing interrupt latency and increasing speed while simultaneously reducing code size. It's a win-win for your project and the environment.

HI-TECH C PRO compilers for Microchip PIC10/12/16/18/32 MCUs and other microcontrollers.

Denser code, better performance: www.htsoft.com/ocg

www.htsoft.com • sales@htsoft.com • +61 7 3722 7777 All trademarks are the property of their respective owners.

# INS SUE

May 2009 • Measurement & Sensors

Smart Lead-Acid Battery Meter An MCU-Based "Gauge" for SLA Batteries Dale Wheat

44

16

Construct a USB GPIO Pod (Part 2) USB JTAG Module DJ Delorie

36 DOS in the 21<sup>st</sup> Century A USB FLash Drive Reader for MCUs Works for DOS Andrew Mitz & Jon Daley

Transformerless Power Supply Tom Struzik

#### 52 FROM THE BENCH

A World Without NTSC Bridge the Gap Between NTSC and VGA Jeff Bachiochi

#### 65 SILICON UPDATE Whistle While You Work A Look at a Modern DSP

Tom Cantrell

TASK MANAGER Old Tech, New App C. J. Abate

- **NEW PRODUCT NEWS** 8 edited by John Gorsky

- **TEST YOUR EQ** 15

4

- CROSSWORD 74

- **INDEX OF ADVERTISERS** 79 June Preview

PRIORITY INTERRUPT 80 It's All About the Content, Stupid! Steve Ciarcia

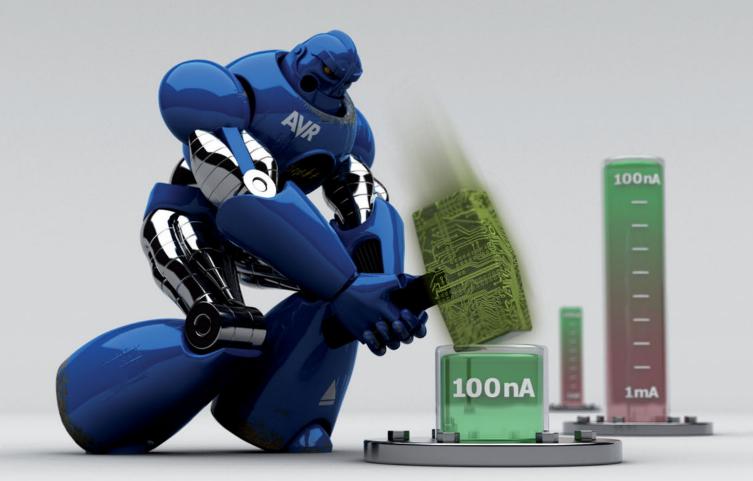

# Hammer Down Your Power Consumption with picoPower™!

# **THE Performance Choice of Lowest-Power Microcontrollers**

Performance and power consumption have always been key elements in the development of AVR<sup>®</sup> microcontrollers. Today's increasing use of battery and signal line powered applications makes power consumption criteria more important than ever. To meet the tough requirements of modern microcontrollers, Atmel<sup>®</sup> has combined more than ten years of low power research and development into picoPower technology.

picoPower enables tinyAVR<sup>®</sup>, megaAVR<sup>®</sup> and XMEGA<sup>™</sup> microcontrollers to achieve the industry's lowest power consumption. Why be satisfied with microamps when you can have nanoamps? With Atmel MCUs today's embedded designers get systems using a mere 650 nA running a real-time clock (RTC) and only 100 nA in sleep mode. Combined with several other innovative techniques, picoPower microcontrollers help you reduce your applications power consumption without compromising system performance!

Visit our website to learn how picoPower can help you hammer down the power consumption of your next designs. PLUS, get a chance to apply for a free AVR design kit!

#### http://www.atmel.com/picopower/

### **NEW SEALED LIMIT SWITCHES**

Many limit switches must function in harsh conditions or outdoors environments which may damage switches and lead to frequent change outs. Even limit switches that are IP67 sealed often require wiring replacements. This could mean changing several meters of cable on outdoor equipment.

In order to facilitate faster maintenance, the newly introduced models **MP730** through **MP760** sealed limit switches with the ability to connect through an M12x1 connector— which maintains IP67 protection on the switch—are now available. The connector can be mounted on the side, but a bottom-mount option is also available.

The MP700 series limit switches are available with a metal housing and a five-pin connector or with a plastic housing and a four-pin connector. Mounting holes can be placed either 20 mm or 25 mm apart for installation flexibility. The switches are additionally supplied with a large variety of actuator options and conform to IEC 947-5-1 and EN 60 947-5-1.

Pricing for the switches starts at around \$40.

Microprecision Electronics www.microprecision.us

### NEW OSCILLOSCOPES FOR DEBUGGING

The **WaveAce** series of digital oscilloscopes is a line of portable, affordable, easy-to-use oscilloscopes in the 60- to 300-MHz range. The WaveAce improves troubleshooting and shortens debug time by providing unique features such as long memory, a color display, extensive measurement capabilities, and advanced triggering. A streamlined, time-saving user interface provides quick access to all important controls. With its USB host and device ports, the WaveAce easily connects to a memory stick, PC, or printer. The variety of standard acquisition modes and advanced triggers simplifies capturing even the most complex waveforms, making the WaveAce a valuable tool for design, debug, and troubleshooting.

The new WaveAce is available in two-channel models with bandwidths of 60, 100, 200, and 300 MHz. All models have color displays. With a maximum sample rate of 2 G5/s and up to 8 kpts/ch memory, the WaveAce is a performance leader in this class of portable oscilloscopes. The long memory enables users to capture full sample rate acquisitions that are two to three times longer than the competition.

Improving how a user can understand and analyze waveforms, the WaveAce has 32 built-in automated parameters, including advanced timing parameters for skew, phase, and edge-to-edge measurements between channels. Additional features—such as Pass/Fail testing, user-definable digital filters, and a waveform sequence recorder—all simplify and shorten debug time.

Prices for the WaveAce series start at approximately **\$1,200**.

LeCroy Corp. www.lecroy.com

NEW PRODUCT NEWS

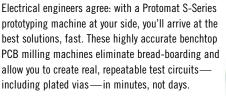

#### LOW-POWER COMPUTER CAPTURES & TRANSMITS REMOTE DATA

The **DataMover** offers an economical solution to remote data capture and transmission. By integrating an optional GP5 receiver, GPR5 cell modem, and Sleep mode power controller in a die cast aluminum enclosure, the DataMover is capable of logging and transmitting data from remote or inaccessible locations. With power consumption of less than 1 W during operation and less than 3 mW in Sleep mode, the DataMover can be battery- or solar-powered with minimal expense.

The DataMover single board computer comes standard with R5-232/R5-485 serial ports, conditioned analog-to-digital converter inputs, driver outputs, optically isolated inputs, and simple TTL I/O. The software supplied includes drivers and a read/write file system.

The DataMover controller is **\$142** in 100piece quantities. Development kits are available for **\$229**.

JK microsystems www.jkmicro.com

# HALL-EFFECT MAGNETIC POSITION SENSORS

The **55361RT** and **55461R** are bipolar latch, Hall-effect magnetic position sensors with enhanced sensitivity, which enables the use of less expensive magnets in some applications. The 55361RT sensor's small footprint takes up less space on the printed circuit board, typically allowing for a reduction in costs. Additionally, the 55361RT sensor is supplied on tape and reel, allowing for automated, high-volume, lower-cost pick-and-place assembly.

The 55361RT and 55461R sensors are designed for potential use in industrial applications (e.g., speed and RPM sensing, tachometer, flow-rate sensing, valve/damper position, brushless dc motors, variable speed drives, motor and fan control, and robotics control), medical applications (e.g., motor assemblies and medication dispense control), and transportation motion control applications (e.g., RPM sensing, tachometer, motor and fan control, electric window lifts, convertible roof positioning, and transmission positioning).

The SS361RT and SS461R sensors feature a 3-V supply voltage capability for low-voltage applications. The sensors are available in two package styles, providing application flexibility. The SS361RT's miniature SOT-23 surface-mount package utilizes a tape and reel format. The SS461R's flat TO-92 style is available in bulk (1,000 units per bag). Please contact your Honeywell distributor for pricing.

Honeywell International www.honeywell.com

### PROGRAMMABLE SMART CARD

The BasicCard ZC3.12 is the first programmable smart card with 2 KB of EEPROM for a price less than \$1.30. This microprocessor-based smart card is programmable in Basic. Applications like E-Purse, Identification Card, Medical Card, Gift and Lovalty Card, and so on, can be developed in BASIC and are fully compatible to the ISO 7816 standard. Encryption technology like AES, DES, or ECC is included.

Programming is accomplished through a bidirectional I/O contact. Communication takes place at 9,600 bps or more, according to the T=0 and T=1 protocols defined in ISO/IEC standards 7816-3 and 7816-4. (The latest cards also implement the con-

tactless ISO14443 protocol.) This is completely invisible to the Basic programmer. All you have to do is define a command in the card and program it like an ordinary Basic procedure. Then you can call this command from a ZC-Basic program running on the PC. Again, the command is called as if it was an ordinary procedure.

The BasicCard operating system takes care of all the communications for you. It will even encrypt and decrypt the commands and responds if you ask it to. All you have to do is specify a different two-byte ID for each command that you define

A development kit for the BasicCard ZC3.12 is available for about \$78. The BasicCard ZC3.12 is priced at \$1.30 in quantities of 10 or more.

ZeitControl cardsystems GmbH www.basiccard.com

### NEW 8-, 16-, AND 32-BIT INDUSTRIAL MCUs

Three new series microcontrollers with embedded flash technology for industrial applications are now available. All are designed to meet the performance and reliability requirements of a wide range of drive applications across a variety of industries.

The new XC864 series is designed for cost-sensitive motor control applications. The XC864 series combines in a small footprint TS5OP-20 package a standard 8051 core with on-chip flash memory of up to 4 KB and powerful on-chip peripherals. The XC864 series features an internal clock source and embedded voltage regulator, supporting single voltage supply of 3.3 or 5.0 V.

The XE16xM series of MCUs are designed for use in real-time industrial drive applications, such as servo drives, HVAC compressors and blowers, pumps, advanced sensing and power supplies. The XE16xM series provides additional advanced safety features for SIL3 applications and 64-pin devices (the XE162M series) with a small footprint. The highly configurable serial

interface USIC supports multiple protocols, such as Asynchronous and Synchronous Serial Interfaces (ASC, SSC), I<sup>2</sup>C, LIN, and communication to 5D memory cards.

The TC1167 and TC1197 are designed for use in demanding real-time industrial applications, such as multi-axis controllers for up to five threephase complementary PWMs. They support multiple modulation strategies such as Space Vector Control or Direct Torque Control and provide multiprocessor support for reliability and safety.

In guantities of 20,000 units, the 8-bit microcontroller XC864 costs about \$1.05 per unit. The price of the 16-bit XE16xM series starts with the XE162M at about \$7 each. The unit price of the 32-bit microcontroller TC1167 is about \$20.16. The TC1197 is about \$26.46.

Infineon Technologies AG www.infineon.com

## CO GAS SENSOR MODULE

The CO Gas Sensor Module (#27931) is designed to allow a microcontroller to determine when a preset CO gas level has been reached or exceeded. Interfacing with the sensor module is done through a four-pin SIP header and requires two I/O pins from the host microcontroller. The sensor module is mainly intended to provide

> a means of comparing carbon monoxide sources and being able to set an alarm limit when the source becomes excessive.

The module is built around the MQ-7 CO sensor and features a SIP interface. Included in the kit is the module, a potentiometer adjustment tool, and complete documentation. The module requires 5 VDC at 165 mA (Purge Phase)/50 mA (Sense Phase). The unit is 1.50" H  $\times$  1.00" W  $\times$  1.00" D and operates over a 0 to 70°C range.

The CO Gas Sensor Module costs \$29.99.

Parallax, Inc. www.parallax.com

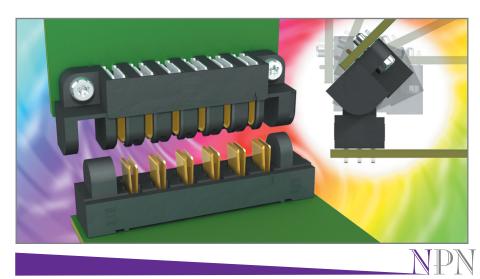

#### NEW HINGED POWERSTRIP

Samtec has expanded its rugged PowerStrip High Power Interconnect family with a hinged version of its 25-A PowerStrip/25 system. The FMPS/FMPT Series connectors are ideal for applications that call for blind mating or where PCB real estate is tight.

The hinged PowerStrip/25 Socket Terminal system (FMPS/FMPT Series) is a unique system that allows for 90° or horizontal (planar) board-to-board interfaces and a  $90^\circ$ mating radius. The design's flexibility allows the connectors to be mated at an angle convenient for production and then rotated to the final, permanent required orientation. It is available with up to eight power pins on 0.200" (5.08-mm pitch) and can achieve a robust current rating up to 25 A per contact at 75°C. Optional locking clips and a screw-down configuration for the socket are also available.

The hinged PowerStrip/25 joins High Power 35 A PowerStrip/35 connector systems, 25 A PowerStrip/25 connectors, discrete wire cables, and the 10 A Power-Strip/10 modular connector system.

The full line of Rugged/Power solutions also includes Power Mate, Mini Mate and Q Series High Speed/Power connectors and cables, and a variety of Rugged/Power Headers and Sockets.

It costs about \$0.25 per 25-A pin in guantities.

Samtec, Inc. www.samtec.com

- USB to JTAG

- Fast 720kb/s Download Speed

Serial Wire Debug (SWD) Support

Multicore Debugging Support

Auto JTAG Speed Recognition

The J-Link can be coupled with a number of available software modules to fit your application needs.

J-Flash is a stand-alone application used with the J-Link to program internal and external flash devices.

J-Link RDI permits the use of the J-Link with an RDI compliant debugger.

J-Link GDB Server is a remote server for GDB.

J-Link Flash Download is a module used to download your program into flash even if your debugger does not have a flash loader.

J-Link Flash Breakpoint permits you to set an unlimited number of software breakpoints while debugging in flash.

J-Link SDK is a standard DLL that extends the full functionality of the J-Link to your proprietary application.

We also offer a JTAG isolator which

can be used to JTAG Isolator offer electrical isolation between your target hardware and the J-Link. This is essential when the development tools are not connected to the same ground as the application. It is also useful to protect the development tools from electrical spikes that often occur in some applications, such as motor control applications.

Includes the J-Link, J-Link GDB Server, and the J-Link Flash Download. www.segger-us.com/ncu.html

J-Link Non-Commercial (NCU) Bundle

#### www.segger.com

## PCF2123 DEMO BOARD

The **RTC-DEMO-PCF2123** is a stand-alone demonstration platform for the new NXP SPI-based PCF2123. With a typical standby current of only 100 nA at 2.0 V, the PCF2123 is the lowest power real-time clock currently available. The unit is powered by a single 3-V coin cell battery and includes an eight-character alphanumeric LCD with 128-segment I<sup>2</sup>C LCD driver and a P89LPC932 8-KB flash microcontroller. Also included are an LM75B I<sup>2</sup>C temperature sensor and two miniature push buttons for user control. An additional user interface is available via an expansion header and the flash microcontroller is user programmable via a 10-pin ICP header.

The RTC-DEMO-PCF2123 is available from stock for \$69.

Future Designs, Inc. www.teamfdi.com

## STRONG, SILENT INDUSTRIAL PC

Ideal for a variety of embedded applications, the AMOS-**3000** is a robust, custom-designed system based on the ultra compact and versatile EPIA-P700 Pico-ITX board. Measuring only 13.5 cm  $\times$  4.5 cm  $\times$  13.1 cm, the AMOS-3000 is strong, durable, and heat-efficient—yet it is tiny enough to fit in the palm of your hand. The system can be installed easily using simple table, wall and VESA mounting options.

The AMO5-3000 is based on an EPIA-P700 Pico-ITX board, powered by either a 1-GHz C7 processor or an ultralow-voltage 500-MHz Eden processor coupled with the VX700 unified digital media chipset, supporting up to 1 GB of DDR2 50-DIMM system memory. The system has a certi-

fied operating temperature of  $-20^{\circ}$  to  $60^{\circ}$ C, vibration tolerance of up to 5 G<sub>RMS</sub>, and a shock tolerance of up to 50 G.

Storage is provided through a 44pin IDE interface for Disk on Module Flash drive. An optional storage subsystem expansion chassis offers support for a standard 2.5" SATA drive. An on-board RJ-45 connector provides Gigabit networking, while the VT1708A brings HD audio. Additional features include four USB 2.0 ports, on-board GPIO port, COM port, and programmable watchdog timer. System LED indicators are provided for power and HDD activity.

The AMO5-3000 has a list price of **\$380**.

VIA Technologies, Inc. www.via.com.tw

## SENSOR FILM MEASURES LOW CONTACT PRESSURES

**Pressurex Zero** is an easy-to-use, tactile pressure-indicating sensor film. Pressurex Zero characterizes contact surface pressure down to an extremely low 7.2 psi (0.5 kg/cm<sup>2</sup>). It is simply placed between contacting or mating surfaces to instantly and accurately measure and map pressure magnitude and distribution. Variations in contact surface pressure are immediately visible by the impression made on the film. The range for Pressurex Zero is 7.2 to 28 PSI (0.5 to 1.97 kg/cm<sup>2</sup>).

Pressurex comes in the form of a thin plastic sheet (4 or 8 microns), physically similar in thickness to paper, and is available in eight different pressure ranges. When placed between contacting surfaces, it instantaneously and permanently changes color directly proportional to the actual pressure applied. The precise pressure magnitude (psi or kg/cm<sup>2</sup>) is easily determined by comparing color variation results to a color correlation chart (conceptually similar to interpreting Litmus paper). Pressurex can also be scanned through one of Sensor Products's optical imaging systems. The film, which is available in eight different pressure ranges, is used in the design, manufacture, calibration, and quality

control of many products.

Pressurex is flexible, which enables it to conform to curved spaces. It is ideal for invasive, intolerant environments and tight spaces that are not accessible to conventional electronic transducers.

A 270 mm  $\times$  3 m roll of Pressurex costs **\$698**.

Sensor Products, Inc. www.sensorprod.com

#### ULTRASONIC SENSORS FEATURE EXTENDED RANGE AND COMPENSATION

The **U-GAGE T3OUX** is an ultrasonic sensor for challenging applications. With its extended functional range and advanced temperature compensation, the T3OUX sensor withstands hostile environments, providing superior ultrasonic sensing to solve even the toughest application challenges. The T3OUX sensor features a robust U-GAGE housing to resist harsh environmental conditions and provides a variety of model options to meet a broad range of application requirements.

The T3OUX ultrasonic sensor is available in a choice of three ranges for reliable sensing from 100 mm to 3 m and delivers high-accuracy performance with built-in temperature compensation across a wide range of ambient temperatures. Temperature compensation enables the sensor to self-correct for the temperature in its environment and maintain the highest accuracy in changing conditions. This robust sensor resists harsh environments with a rugged IP67 (NEMA 6) housing and fully

encapsulated electronics, and its 30-mm threaded barrel and a selection of mounting brackets allow simple installation. Additionally, models are available with a single analog or user-configurable discrete output, and all models provide highly visible LED status indicators for power, signal strength, and output.

The sensor starts at **\$249** for U.S. orders and depends on the configuration needed.

#### Banner Engineering Corp. www.bannerengineering.com

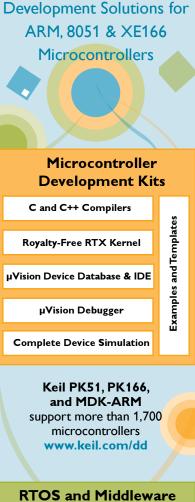

Components

Keil RL-ARM and ARTX-166 highly optimised, royalty-free middleware suites www.keil.com/rtos

> www.keil.com 1-800-348-8051

### QUICK-CONNECT WIRING SYSTEM

The new M16 powerfast wiring system is specifically designed for machine power distribution and motor control. The quick-connect M16 powerfast system provides a time- and cost-saving replacement for traditional hard-wiring installations and complies with NFPA 79: Electrical Standard for Industrial Machinery. These two-, three-, and four-pin connectors and tees provide up to 18 A in a compact form factor.

The cordsets are offered with Tray Rated, exposed run PVC flexlife cable. All connectors deliver IEC IP 67 protection and are rated for 600 V and up to 18 A. Tees are available with simple connectors or with branches.

Like most TURCK cordsets, the M16 powerfast line offers male or female options, straight connectors, standard and custom lengths, and pigtails or extensions. To complete the system, fully encapsulated mating receptacles with nickel-plated brass housing and 0.5" to 14 NPT, 0.375" to 18 NPT, M18, and M20 mounting threads are available.

Prices are dependent on the configuration, please contact TURCK directly.

TURCK, Inc. www.turck-usa.com

# NPN

# **CIRCUIT CELLAR**

Edited by David Tweed

Robert Lacoste recently wrote about transmission lines and time-domain reflectometry (TDR) in Circuit Cellar issues 224 and 225. Let's explore that topic a little further.

**Problem 1**—Suppose we use a step waveform (instead of a narrow pulse) to excite the transmission line circuit shown below. What sort of waveform would you expect to see at point A?

**Problem 2**—Can you reconcile your answer to the previous question with the waveform created by pulse excitation that Robert Lacoste discussed in Circuit Cellar 225?

What's your EQ?—The answers are posted at www.circuitcellar.com/eq/ You may contact the quizmasters at eq@circuitcellar.com **Problem 3**—Suppose you have a circuit that is capable of producing step waveforms with very fast rise times. How can you use a transmission line to convert the steps to narrow pulses?

Test Your

**Problem 4**—Joe is a ham radio operator, and he likes to operate on the 6-m band (50 to 54 MHz). One day Bill is visiting Joe's "shack," and notices that Joe has a tee adapter on the transmitter's antenna jack, and in addition to the cable to the antenna, there is a second piece of coax attached to the tee that doesn't seem to go anywhere. It appears to be about a foot long.

Bill asks Joe about it, who laughs and says, "Oh, that helps keep me legal!" What's going on here?

David Tweed contributed the four problems and answers in this issue.

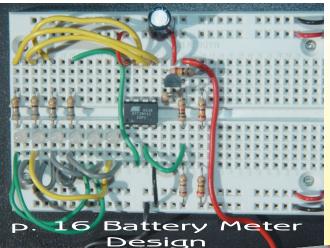

# Smart Lead-Acid Battery Meter An MCU-Based "Gauge" for SLA Batteries

Think sealed lead-acid (SLA) batteries are a thing of the past? Think again. They are bound to be around for years to come. Dale designed a state-of-charge meter for his SLA batteries. His multicolored LED meter simplifies battery charge testing.

Rechargeable batteries are found in almost all portable, mobile, and mission-critical electronic equipment. New technologies are storing more energy in less space than ever before. Sealed lead-acid (SLA) batteries are far from the leading edge of available options: they are heavy, poisonous, and lack energy density compared with newer options. Despite these apparent drawbacks, they are *everywhere*. Like COBOL, they will be with us for some time.

SLA batteries are especially popular in hobby robotics as well as hobby electronics in general. Their ubiquity in surplus channels makes them an easy choice for beginning roboticists. Low initial cost and dependable, well-documented performance endear them to novices and seasoned professionals alike. It also doesn't hurt to find that many standardized sizes and capacities are still being produced all over the world and will be for the foreseeable future.

Charging characteristics increase their appeal: A constant voltage charger is often a good first project for the curious electronics hacker. Off-the-shelf charging solutions abound and remain competitively priced.

#### A FUEL GAUGE

How much charge is left in the battery? I'm glad you asked! There are several methods available for determining the "state of charge" (SoC) or, conversely, the "depth of discharge" (DoD). I think I've seen those acronyms before, somewhere.

The most direct method is to simply measure the battery voltage and say, "Lo, here is the remaining charge." Fortunately for battery users and unfortunately for us battery measurers, most batteries have a relatively flat discharge curve. Lithium-based chemistries are the most

| Terminal voltage | State of charge |

|------------------|-----------------|

| 12.65            | 100%            |

| 12.45            | 75%             |

| 12.24            | 50%             |

| 12.06            | 25%             |

| 11.89 or less    | Discharged      |

**Table 1**—This is the state of charge versus voltage for a sealed leadacid battery at rest. These values were taken from "Battery University," a series of informative, on-line articles about rechargeable batteries by Isidor Buchmann and sponsored by Cadex Electronics.

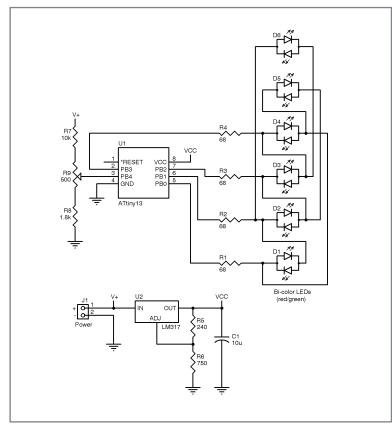

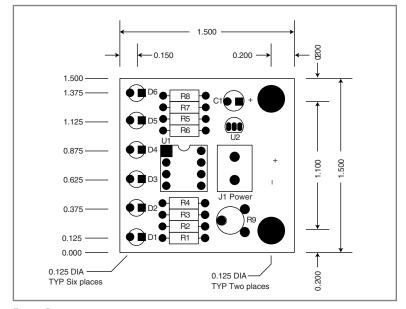

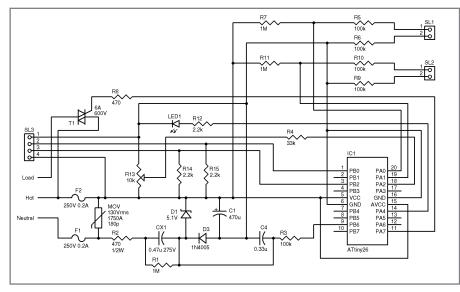

Figure 1—This is the smart SLA battery meter. I originally drew this using Advanced Circuits's free/gratis PCB Artist software. It enabled me to enter the schematic, lay out the PCB, then quote and order PCBs, all from the same program. This is a redrawn version.

notorious for steady, stable voltage output. Curse them and their dependable, high-energy densities! We will eventually use a variation of this method to determine

Figure 2—Here are the mechanical dimensions of the prototype PCBs. This will allow you to have a custom panel machined that will fit like a glove. The production version of the PCB will have the same dimensions but will have rounded corners.

the state of charge, after combining it with some other knowledge we have that is specific to lead-acid batteries.

Once upon a time, before SLA batteries were sealed, the specific gravity of the electrolyte could be measured and used as a good indication of the state of charge. You dipped an industriallooking turkey baster containing floaties into the different cells and slurped up a sample electrolyte using the high-tech squeeze bulb on the end. If you had a steady hand and good lighting, you probably didn't spray battery acid on your clothes and skin. Unfortunately, I often did. I don't test those kinds of batteries any more.

A more detailed method to determine SoC is to measure how much energy has gone into the battery during the charge cycle and then keep track of how much energy is then taken out during usage. "Counting coulombs" requires both current and voltage measurements to be integrated over time and must take into consideration temperature and age of the battery. In reality, temperature and age really have to be considered in any comprehensive methodology. Several "coulomb counter" circuits are available from Maxim Integrated Products, Linear Technology, Texas Instruments, and others. Also, if you can count individual coulombs per second, you know how many amps are flowing in a circuit, because that is the textbook definition-but you knew that.

Although there is no *linear* relationship between voltage and state of charge, there are well-known waypoints down the discharge curve for lead-acid batteries. These voltage levels are only truly representative of the state of charge after the battery has been allowed to rest for at least 8 hours. They are summarized in Table 1.

#### **MEASUREMENT CIRCUITRY**

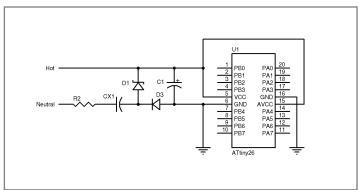

Figure 1 shows a simple data acquisition circuit that can be used to approximate the state of charge of an SLA battery. The input signal powers the entire circuit. The battery voltage is brought in via J1. From there, it is split into two paths. The first goes to an LM317L adjustable, positivevoltage regulator that is set to approximately 5 V using R5 and R6. I chose this for its wide input range, excellent output stability, small size, abundant availability, and low cost. The regulator's output is filtered by C1. Overall, this is a mundane power supply circuit. Its only special feature is that it will withstand a high input voltage and automatically shut itself down if it overheats.

The other path for the incoming power signal is to a voltage divider composed of R7, R8, and R9. R9 is a potentiometer allowing the calibration of the incoming signal to a known value.

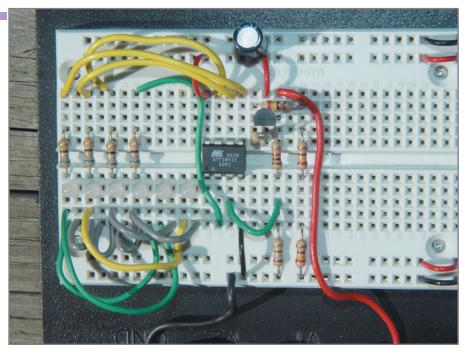

Photo 1—This is the first prototype of the battery meter built on a solderless breadboard. The extra resistors represent doing it the hard way when you don't have an exact value in stock when inspiration strikes.

This is handled in software to allow quick and reliable calibration of the battery meter in production (see Figure 2). I will describe more about the calibration procedure when I cover the firmware in detail.

The wiper pin of R9 leads into pin 3 of U1, the main brain of the circuit. I used one of my favorite Atmel AVRs, the ATtiny13, for its small size, ease of programming, versatile peripheral set, and low cost. The pri-

mary features that helped me select this part for the design were an on-chip ADC with up to 10 bits of accuracy, an internal clock, low current requirements, and reprogrammable I/O lines.

#### **TELL THE WORLD**

The AVR is happy to measure the incoming voltage and store the answer in a register or RAM location. That's not interesting at all. I wanted to add a simple but effective display using a minimum number of parts. I also wanted the display to produce "meaningful" information even with no user manual handy. A single

line of LEDs arranged as a bar graph would give a good report with a single glance; the more LEDs lit, the more power was left in the battery. Somewhere along the line I decided to spice it up and use multicolor LEDs to reinforce the message: green was good, yellow foretold doom, and red would announce failure. I suppose "multicolor" is a bit of a reach, as the LEDs I finally included were technically "bipolar" LEDs: a red

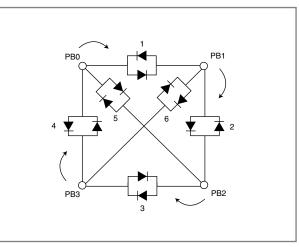

Figure 3—This is the geometric version of the LED array schematic, showing all the possible combinations of connections between the four I/O lines. That's how you light up 12 LEDs with only four I/O lines!

and a green LED die mounted inside the same package. Current applied in one direction would course through one die and illuminate it while reversing the current would light up the other side. Alternating the current rapidly would produce the illusion of both LEDs being lit simultaneously. This is alleged to be yellow, but it only looks yellow if you look at it quickly and sideways at the same time. It is yellow-esque, at best. Five or six multicolor LEDs would give enough of a range to make a useful display. Because each LED package is two distinct LEDs, I would have to come up with a way to drive a dozen or so LEDs with a small microcontroller.

#### FANCY LED MULTIPLEXING

Normally, 12 individual LEDs would require, at a minimum, 12 dedicated output driver lines to be able to individually and randomly address any LED. The ATtiny13 has six I/O lines available. Using a multiplexing technique sometimes referred to as "charlieplexing," I was able to drive the 12 LEDs using only four output pins. Maxim application note 1880 credits Charlie Allen with championing this technique within the organization. Maxim Integrated Products offers several devices that will perform that trick for you. Don Lancaster wrote about it in his "Tech Musings" column in August

2001 and gave several examples (www.tinaja.com). I'm sure I thought of it long before, but I must have neglected to write it down in my journal. Dang.

The number of LEDs that can be addressed depends on the number of I/O lines that you're willing to throw at it. The formula is n(n - 1), where n is the number of I/O lines. So, four I/O lines would give you 12 LEDs (i.e.,  $4 \times 3$ ). That translates to six bipolar LEDs. The next step up would be five I/O lines and 20 normal LEDs or 10 bipolar LEDs. That's too many. The next step down

Smaller than a sugar packet, the Rabbit<sup>®</sup> MiniCore series of easy-to-use, ultra-compact, and low-cost networking modules come in several pin-compatible flavors. Optimized for real-time control, communications and networking applications such as energy management and intelligent building automation, MiniCore will surely add sweetness to your design.

- Wireless and wired interfaces

- Ultra-compact form factor

- Low-profile for design flexibility

- Priced for volume applications

1.888.411.7228 rabbitwirelesskits.com 2900 Spafford Street, Davis, CA 95618

would be three I/O lines and six normal LEDs or three bipolar LEDs. That's too few. Six LEDs is just right.

Imagine the four I/O pins are wired to the four corners of a square. Now each square corner is connected by a bidirectional LED to every other corner. This makes four LEDs around the periphery of the square as well as two across the diagonals. My schematic skills omit the symmetrical beauty of this circuit and hint only at the possibilities.

We have 12 LEDs: six red and six green. They look just like regular LEDs when they are not illuminated. Some bipolar LEDs have three legs: one for each die and a common terminal. I used the two-legged variety of the 3-mm persuasion where each leg is attached to both the anode of one LED and the cathode of the other.

Instead of wiring a current-limiting resistor to each LED, I wired them to the I/O lines. This way there are only four resistors for all 12 LEDs. This works out well as there is only one LED on at a time, even when it looks like they are all illuminated. Because the current through any LED must flow through two resistors, the value of each resistor is half of what is required to limit the current through the LED. I calculated a maximum of 20 mA through each LED. I could probably have upped that number as the duty cycle is at most 1/6.

To illuminate any single LED, the I/O pin that is connected to its anode is programmed to be an output and to drive that output high. The corresponding cathode pin is also programmed to be an output and to drive its output low. The other two I/O lines are told to sit down and shut up. A more technical and accurate way to describe it would be to say that they are programmed to become inputs and not activate their internal pull-up resistors. They

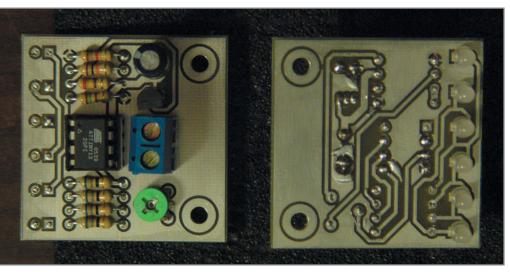

Photo 2—This is the assembled PCB. These boards made by Advanced Circuits are their BareBones special: double-sided, plated-though holes, no soldermask, no silkscreen. Believe it or not, they were built in under 24 hours! Every one perfect, every time.

effectively become tristated at this point and do not contribute to the current flow in the LED array. Each LED has its own pattern of ins, outs, highs, and lows.

#### WRITE THE SOFTWARE

I built a prototype of the circuit using a solderless breadboard (see Photo 1). I used an Atmel STK-500 to program the ATtiny13. Being an eight-pin DIP, it was relatively easy to pop it in and out of the prototype for programming. Anything larger would have wanted its own programming cable attached. The AVR devices have the nice capability of "in-system programming," or ISP. This allows the part to be programmed and reprogrammed in situ, without having to remove the part from the circuit and placed in a device programmer.

I wrote the code in C. I used the WinAVR port of the GCC compiler collection, which works well with Atmel's AVR Studio. These are all free programs, in various senses of the word (GCC is libre, or free as in speech, while AVR Studio is gratis, or free as in beer).

The first task was, as usual in embedded development, to light a single LED. This was a little more complex than the normal embedded "Hello, world!" monochrome monopixel. I had to constantly refer to my scribbled notes as to pin placement and LED array wiring (see Figure 3).

I played with various combinations of highs and lows and ins and outs. Once I could light up individual LEDs to my satisfaction, I wrote a routine to scan through a memory map of LEDs and light them or not, over and over, too quickly for the eye to detect. This produces the illusion of multiple LEDs being illuminated at the same time. This became the main loop of the final firmware.

Now I had a medium waiting for a message. The next step was to read the ADC peripheral and determine what voltage was being presented for analysis. Naturally, reading it once was not going to be adequate, due to sampling noise and other error terms, so I set up the on-chip Timer/Counter peripheral to interrupt periodically and in the interrupt service routine set about to oversample the ADC input. Eight successive samples are read and summed then divided by eight to give a rough arithmetic average. This number is compared to a series of preset values to determine how many LEDs of each color to light up. This is where the values from Table 1 come into play.

I broke down the basic thresholds from Table 1 and added a few more of my own devising because my

# The Newest **Optoelectronics**

#### **Kingbright** WWW.KINGBRIGHTUSA.COM

High Brightness LEDs www.mouser.com/ kingbright/a

www.mouser.com

ACIFIC SILICON SENSORS

SEQUL SEMICONDUCTOR

TOUCH SYSTEMS

NEWHAVEN DISPLAY

**Over A Million Products Online**

ORTEK KINGBRIGHT

#### New Products from:

PCB PolyLEDs www.mouser.com/ avagotechnologies/a

#### LedEngin, Inc. LZ4-4xxx10 Serially Connected MCPCB www.mouser.com/

ledengin/a **SHARP**

MICROELECTRONICS OF THE AMERICAS GM5BW High Power White LEDs www.mouser.com/ <u>Sharpsma/a</u>

The ONLY New Catalog Every 90 Days

Experience Mouser's time-to-market advantage with no minimums and same-day shipping of the newest products from more than 390 leading suppliers.

a tti company

The Newest Products For Your Newest Designs

multicolored bar graph could easily express more than the five original charge states.

If the input voltage is above 13.5 V, I assume that the battery is being charged. To announce this, I have the LEDs do the happy dance, where an upward sequence of green LEDs is marched up the bar graph. This is similar to what you may have seen on many cellular phones during their recharge period, except that mine is greener and happier.

If the voltage is between 12.65 and 13.5 V, the graph shows six of six bars, or green LEDs in this case. This represents a fully charged battery with 100% of its capacity available. You have to remember that in the real world, a battery has 100% of its rated capacity only once, if you're lucky, early in its life, and that it slowly degrades over time.

When the voltage is between 12.45 and 12.65 V, it is estimated that approximately 75% or more of the power is still available. Five green dots out of six indicate this stage.

Note that 12.24 V marks the 50% line. Only four green dots are displayed at this point. When 12.06 V is measured, it tells you that only about 25% of the charge remains, and three yellow LEDs are displayed, notifying you that it might be time to start thinking about finding the charger.

When the measured voltage drops further but is still above 12 V, two yellow LEDs describe this sad state of affairs. The battery is effectively flat at this point.

While still above 11.89 V, a single red LED will be lit to announce impending loss of battery power. Anything below this is considered a battery failure and will be displayed as a blinking red light. Below 11.5 V, the unit stops displaying anything in an effort to save what little power might be left.

#### **DUAL POWER**

One of the original requirements for the meter was to measure both 12- and 24-V battery systems, because these were the most common for SLA batteries. I had originally thought of

using different resistors in the inbound voltage divider, but this would have ultimately created two meters: one for 12-V systems and another for 24-V systems. My first thought to improve this was to use a jumper to select between the two ranges and have both sets of resistors installed, just in case. I finally decided to have the required duplication in software where it would weigh less and take up less shelf space. The firmware is actually checking the various waypoints down the discharge curve and also exactly double those voltages. This makes the meter "autoranging" within an admittedly small set of ranges. It also makes it hard for the end user to order the wrong meter or to configure it incorrectly. Note that I didn't say "impossible." Those of you with customers of your own will understand what I mean.

I added an overvoltage condition test for inputs of over 30 V. The

That's it!

The final version of the firmware is contained in a single file of approximately 300 lines of C code and takes up 99.4% of the ATtiny13's 1-KB flash memory. The file and its corresponding object file in Intel HEX format are posted on the Circuit Cellar FTP site.

#### SHOW & TELL

Once I had a working prototype of my new meter, I just had to show it off to some fellow robot builders. Last summer, I brought the battery meter, along with some other blinky toys that I had been working on, to an R2 Build Day hosted by Jerry Chevalier of the R2-D2 Builders Club. Several of the robot builders expressed interest in the meter and that got me thinking about making a real PCB and offering it for sale.

I had been playing with Advanced Circuits's PCB Artist software for several months but had not really

Several of the robot builders expressed interest in the meter and that got me thinking about making a real PCB and offering it for sale.

LEDs light up in an alternating red wig-wag pattern that screams out "uh oh, uh oh" to let you know you've hooked up the meter to the wrong wires.

One additional "waypoint" is coded into the firmware to allow quick and easy calibration of the meter. Then exactly 7.50 V is detected, which is below the normal operating range but still high enough to keep the voltage regulator happy, a special pattern of two yellow LEDs is lit on the meter. To calibrate, attach an accurate 7.50-V source (I happen to have one) and adjust the potentiometer R9 until the LEDs light up with the right pattern.

gotten the hang of it yet. I would tell myself to start out simply and work my way though a complete, if trivial, example. It never failed that I would eventually start trying to get all fancy and do a lot of things at once and would inevitably work myself into some indescribable corner where I would get frustrated and just end up walking away. It's ironic because Advanced Circuits's Drew Peterson lives to help people with PCB Artist questions. The trick is to be able to describe the problem you're having. If you can describe it, Drew can help you out. If you can't, other than "It is not doing what I want it to do," then vou're kinda stuck.

So I started over again, this time on a schematic-only design. I had built a small, five-LED "Cylon" scanner and needed a schematic to put up on my web page. It just needed to be lines, dots, and text. I had already laid out a PCB without the benefit of a schematic (because it was that trivial). This proved a good exercise in learning the user interface of PCB Artist.

The next step in PCB-fu was to learn to make my own symbols. In PCB Artist, all components are symbols, with a schematic view, a PCB footprint, and a link associating the two. Once you can build your own symbols effectively, the sky's the limit. I'm still a long way from being an expert, but I can rough out a board in 1 hour or so and have production-quality work in a few hours more. As I mentioned before, the software also enables you to order PCBs online. I am constantly amazed by this wonderful world of ours.

The PCBs arrived the same day as the last of the components, so I got busy soldering. I used through-hole parts exclusively on this design and the boards were straightforward to assemble. The finished PCB is  $1.500'' \times 1.500''$  (see Photo 2). The components are mounted on one side of the board, and the LEDs are mounted on the other side so that the meter can be flush-mounted in an enclosure, if desired.

The meters are available for sale on my web site (www.dalewheat.com). They are also available on the sites of the other vendors.

If you have any questions about this little circuit, please don't hesitate to contact me.

Dale Wheat is a full-time freelance writer working primarily with embedded systems and shiny things that blink or beep. Dale is married and the father of two adult children. He lives near Dallas, where he enjoys mowing two acres of grass in the summer and not mowing it in the winter. To find out what he has been up to, visit his personal web site dalewheat.com.

# ROJECT FILES

To download code, go to ftp://ftp.circuitcellar.com/pub/Circuit\_Cellar/2009/226.

# ESOURCES

I. Buchmann, "Charging the lead-acid battery," Battery University, www.batteryuniversity.com/partone-13.htm.

The Electropaedia, "State of Charge (SOC) Determination," www.mpoweruk.com/soc.htm.

D. Lancaster, "Tech Musings," www.tinaja.com/glib/muse152.pdf.

Maxim Integrated Products, Inc., "Application Note 1798: Frequency Undersampling in Coulomb-Counting: Measuring Current Flow in Battery Applications," 2002, www.maxim-ic.com/appnotes.cfm/appnote\_number/1798.

——, "Application Note 1880: Charlieplexing—Reduced Pin-Count LED Display Multiplexing," 2003, www.maximic.com/appnotes.cfm/appnote\_number/1880.

R2-D2 Builders Club, http://astromech.net.

D. Wheat, http://dalewheat.com.

# OURCES

PCB Artist software Advanced Circuits | www.4pcb.com

ATtiny13 and STK-500 Atmel Corp. | www.atmel.com

# Construct a USB GPIO Pod (Part 2) USB JTAG Module

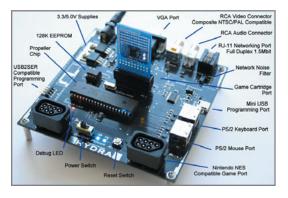

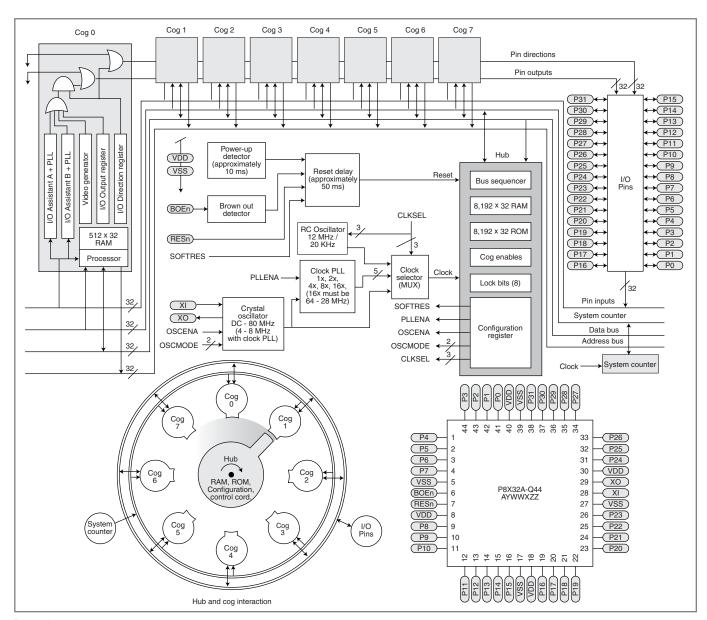

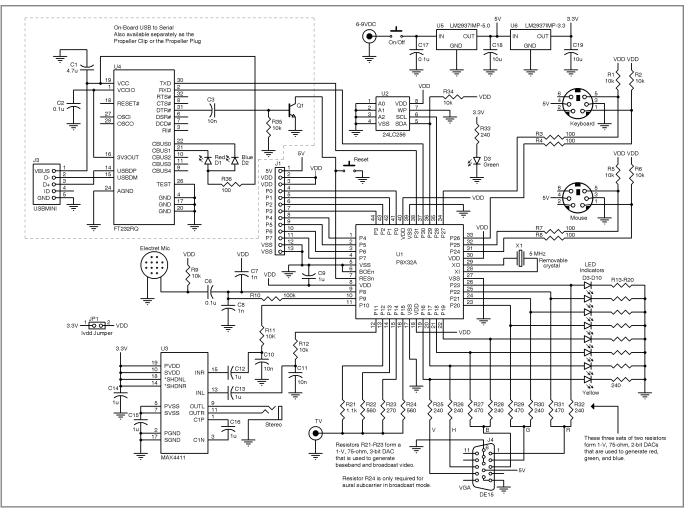

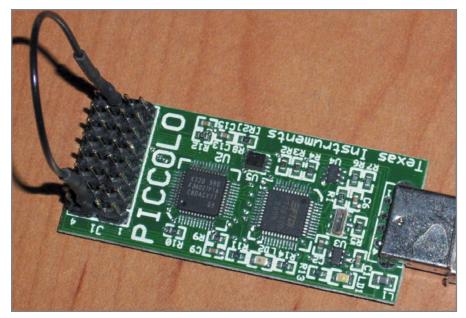

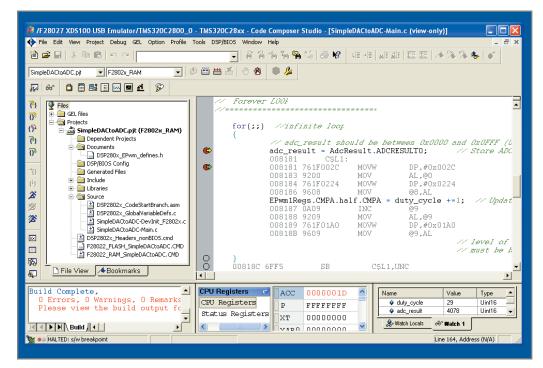

In the first part of this article series, DJ presented a general-purpose input/output (GPIO) pod that can plug into a USB port. Now he describes how to download a JTAG programming application and program a CPLD circuit.

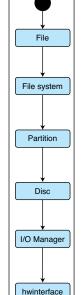

s I explained in the first part of this article series, you can use a general-purpose input/output (GPIO) module that plugs into a USB port on your computer to make up for the lack of a parallel port. While the flexibility of having a microcontroller in this pod enables you to do many things, the real advantage is that you can put a lot of logic-even entire applications-in the microcontroller. This month, I'll explain how to download an entire JTAG programming application into the module. I'll then describe how to use it to program a simple CPLD circuit from a Verilog program from my Linux workstation.

There are commercial devices that let you program JTAG devices over USB from Linux. Then again, there are devices that do a lot of the things you learn to do in Circuit *Cellar*, but it's no fun if you don't do it yourself, right? The module I built is a pure do-it-yourself solution. You can use it for more than just this one task, which saves money in the long run, too.

#### JTAG OVERVIEW

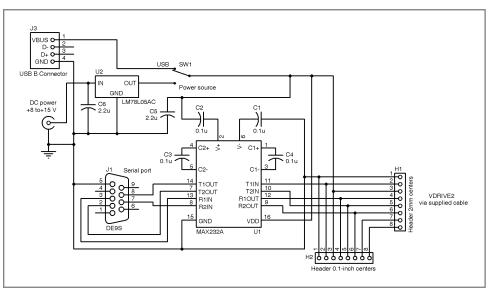

The Joint Test Action Group (JTAG) is a specification created for testing densely populated circuit boards. In addition to testing, many chips have extended their JTAG interface to include other operations, such as programming or debugging. The JTAG interface consists of five logic signals: Reset (optional), Clock, Mode Select, Data In, and Data Out. The signals are abbreviated TRST, TCK, TMS, TDI, and TDO. There are three types of operations, which,

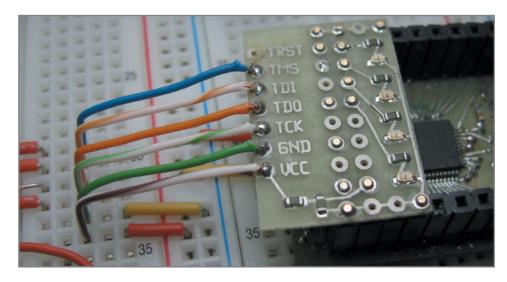

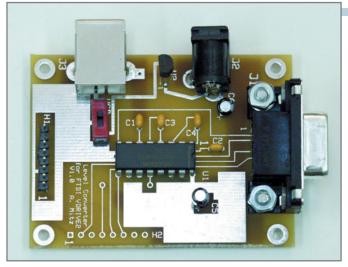

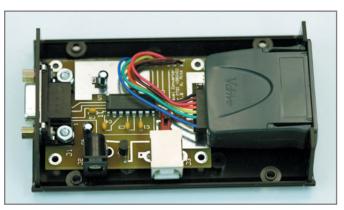

Photo 1-A closeup of the JTAG adapter. Most of the complexity is in the software; the adapter serves to manage the wiring itself. My project doesn't use TRST, so it is left unconnected.

in combination, yield all the operations the chip defines.

Not all chips include a TRST pin because it isn't always needed. When it is included, you can reset the chip's JTAG module by pulsing TRST low. When it is not present, the JTAG module can be reset by clocking in a reset command to the TMS port. Note that this doesn't reset the chip, just the JTAG interface.

The TMS pin controls a state machine, which selects the mode in which the interface operates. Chips that support JTAG use the same state machine, so a project with multiple JTAG chips can tie all the JTAG interfaces together-TRST, TCK, and TMS (in parallel) and TDI and TDO (chained in series)-and control all the chips at once. The state machine is designed so that a reset sequence of clocking five 1 bits on TMS always returns it to the idle state, regardless of where it started. Other combinations of clocked 1 and 0 bits maneuver the state machine into other states, where it can stay as long as the TMS

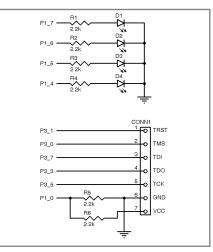

Figure 1—The JTAG adapter module is simple. R5 and R6 feed half the target VCC to P1.0, which is an ADC input on the pod. The rest is just blinky lights and connections.

bit remains low. Two of these states are key. One lets you shift bits into the instruction register via TDI (and shift its previous value out via TDO). The other lets you shift bits through the data register. In most chips, the instruction register selects which data registers (out of many) are used and allows a wide range of functionality.

After a register is selected (either the instruction register or one of the data registers), you can access it through the TDI and TDO pins. The state machine first loads the register with data from elsewhere on the chip. Then, much like a SPI port, the old data is clocked out of TDO while new data is clocked into TDI. Once this is done, the state machine stores the register's data elsewhere in the chip, performing whichever action is indicated.

Aside from a few well-defined common functions, each chip has its own set of registers and functions that it documents. However, they all follow the standard JTAG interface for accessing those registers and functions. Chip manufacturers will often provide a configuration file that describes these functions. Software that uses JTAG to talk to these chips will often read these configuration files to understand how to access these functions. When multiple devices are in the JTAG chain (TDO

chained to TDI), programming utilities can use the configuration for the chips they're not programming to learn how to bypass those chips and access the one they're interested in.

Do you really need to know all this to use JTAG? Not really. Aside from telling inputs from outputs, you don't even need to know this to port the programming application to the pod. However, it helps you understand that there is a lot of bit twiddling going on.

#### JTAG POD MODULE

To simplify connections to the project, I created a JTAG programming module for the USB-GPIO pod (see Photo 1). Aside from bringing out the specific JTAG signals I needed, there are two other functions this module provides.

First, I added a couple of LEDs to provide some visual feedback of what the JTAG protocol is doing. After all, I can't have a project without blinky lights, and the LED on the pod itself is used to give feedback about the hardware flow control used by the serial port software. Second, I needed to be able to monitor the target circuit's supply voltage (see Figure 1).

Because the pod can run at either 3.3 or 5 V, and the target circuit can run at any voltage, I used one of the pod's ADCs to compare the target's voltage with the pod's voltage. The reference voltage is set by the pod to its own supply voltage. I used a pair of resistors to divide the target's supply voltage in half and feed it into the ADC. If the voltages match, the resulting ADC value should be about 128 (on a scale of 0-255, or an 8-bit conversion). If the pod is running at 3.3 V and the target at 5 V, the result will be 5/3.3 times higher, or around 194. If the voltages are the other way, the result will be 3.3/5times as high, or around 84. If the target is not yet powered up, the result will be zero. While the R8C/20 does not have 5-V-tolerant inputs when running at 3.3 V, this at least enables me to find out quickly if the voltages are mismatched. Mostly, it just checks to see if the target is powered up at all, protecting the target from damage.

The pod's software is a port of the JTAG programming application, as provided in Xilinx's 2007 application

**Listing 1**—This is the top module for my CPLD project. The signals named on the line with module top correspond to pins. Each always block corresponds to some logic gates, and other logic modules are brought in by reference.

```

module top(ibin, nen, en, blank, lzblank, polarity, oseg2, oseg1, oseg0);

input [7:0] ibin;

input nen:

input en;

input blank;

input lzblank;

input polarity;

output [6:0] oseg2;

output [6:0] oseg1;

output [6:0] oseg0;

wire nen:

wire en;

wire blank;

wire lzblank:

wire polarity;

wire [1:0] bcd2;

wire [3:0] bcd1;

wire [3:0] bcd0;

reg [7:0] ibinh;

reg blank2;

reg blank1;

reg blank0:

reg

1z2;

reg lz1:

wire [6:0] oseq2t:

wire [6:0] oseg1t;

wire [6:0] oseqOt:

// Latch in the input value

always @ (ibin, nen, en)

begin

if (en & ~ nen)

ibinh <= ibin;</pre>

else

ibinh <= ibinh;</pre>

end

// Convert it to BCD

bcd b0 (ibinh, bcd2, bcd1, bcd0);

// Calculate leading zero suppression

always @ (bcd2, bcd1)

begin

1z2 <= (bcd2 == 0) ? 1 : 0;

|z| \le (bcd1 == 0) ? |z| : 0:

end

// Calculate blanking

always @ (lz2, lz1, lzblank, blank)

begin

blank2 <= (lzblank & lz2) | blank;</pre>

blank1 <= (lzblank & lz1) | blank;</pre>

blank0 <= blank;</pre>

end

// Convert to seven segment format

sevenseg012 s2 (bcd2, oseg2t);

s1 (bcd1, oseg1t);

s0 (bcd0, oseg0t);

sevenseg

sevenseq

// Apply blanking and polarity, and output

blanker digit2 (oseg2t, polarity, blank2, oseg2);

blanker digit1 (oseg1t, polarity, blank1, oseg1);

blanker digit0 (oseg0t, polarity, blank0, oseg0);

endmodule // top

```

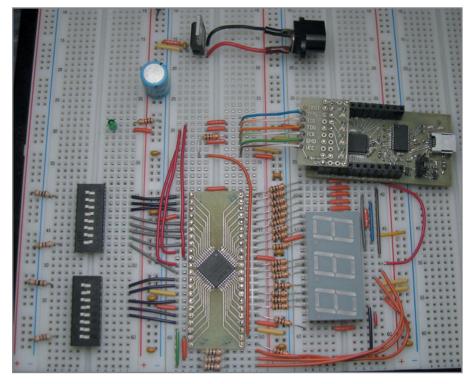

**Photo 2**—My CPLD prototype. At the top is a 3.3-V power supply. On the left are two DIP switches to provide manual input to the CPLD, shown center-mounted on a DIP adapter. At the right is the LED display, and above that is the pod with the JTAG adapter module. Having programmable pins on the CPLD means wiring up the circuit the easiest way, which can be seen here as short, neat connections.

note titled "Xilinx In-System Programming Using an Embedded Microcontroller" (XAPP058). I used the core files as-is, but wrote my own version of ports.h and ports.c to correspond to my pod's hardware. I had to provide two interfaces.

First, I had to provide a source for the CPLD data. This data was created by the Xilinx WebPack utility, which produces (among other things) a Xilinx Serial Vector Format (XSVF) file. The file is a set of binary commands describing how to program the CPLD. The host application feeds this data across the USB link, so the port on the pod has a serial UART driver that reads this data.

The second interface is the I/O for the JTAG signals. I simply mapped these to GPIO signals on port 3. Conveniently, I'd used the SPI pins to allow for future use of the SPI peripherals on the R8C to drive the JTAG interface even faster.

At first, I ported XAPP058 to run on the host, using a simple serial protocol to toggle the output bits and read the

input bits. It was slow, clocking at only a few kilohertz (one serial byte per logic pin change). By running the application on the pod and sending only the XSVF data across the USB link, I avoided the overhead. The serial port was configured to support full hardware flow control, so no special host application was required. I could use any terminal emulator with a "send raw file" option. However, I wrote a small utility to automate the communication. It resets the pod, which gives control to the pod's initialization function. That let me check that the power supplies match. Once they matched, I sent a command to turn control over to the XSVF application, and started sending the .xsvf file across. When the programming was done, control returned to my pod function and it sent the completion status to the host utility.

How much of a difference does it make? Running the application on the host and sending each change output or read input over the USB interface turns out to be expensive. Programming the Listing 2—This is a sample session of building and downloading a pod application.

```

$ cd pod/xsvf ; make

make: Nothing to be done for `all'.

$ sudo ../../host/uflash/uflash xsvf-pod.elf

version = "VER.1.00"

Status: Seq: Ready Erase: Normal Program: Normal ID: ID'd

Status: Seq: Ready Erase: Normal Program: Normal ID: ID'd

00ff00

done!

```

XC9500XL, which has only a 28-KB bit file, takes almost 8 minutes! Varying the pod's CPU clock, or the data rate between the FT232R and the R8C, has almost no effect on this time. It's all USB packet overhead for all those bit changes. Moving the application to the pod's CPU makes the bit twiddling fast, especially if I inline the pod-specific instructions, which saves even the function call overhead. By avoiding the overhead, the programming time is reduced to 12 s, about 40 times faster.

#### SAMPLE CPLD CIRCUIT

I got the idea for the circuit from a

Usenet posting. The original poster was asking for the best way to turn an 8-bit binary number (0-255) into three seven-segment digits (000 through 256). Although there were other suggestions involving ROMs or special TTL chips, I suggested an inexpensive CPLD. At that point, it occurred to me that such a project would be a useful way to teach myself about CPLDs and Verilog. The project was well defined-eight binary inputs representing a number from 0 to 255, and 21 logic outputs to directly drive three seven-segment LED displays. Other pins would be used for other features if I had space in the chip.

Make sure you're signed up to receive Circuit Cellar's monthly electronic newsletter. *News Notes* will keep you up to date on Circuit Cellar happenings. Stay in the loop!

Register now. It's fast. It's free. www.circuitcellar.com/newsletter/

After some searching, I chose the Xilinx XC9500 family of CPLD chips. They were available with a variety of voltage requirements, packages, and logic cell counts. Also, they were inexpensive. The smallest member of the family was only \$1 per chip and available online. It turned out that the smallest chip wasn't big enough for this project, so I chose the second smallest-the XC9572XL. It is a 3.3-V part with 72 logic cells that's available in a 44-pin TQFP. While the definition of logic cell varies from manufacturer to manufacturer, in general each cell includes some form of flip flop and a wide range of combinatorial logic (AND and OR gates, multiplexers, and so on). The program you download into the chip decides which gates and other signals are connected to each other. Another advantage of this family is that the program is stored in the chip itself, so no other supporting logic is required once the chip is programmed.

I chose Verilog to describe the circuit I wanted, again, as a way to learn Verilog. Alternatives to Verilog are VHDL and schematics, but Verilog was simpler for this project than VHDL and more powerful than schematics. The full Verilog sources for this project are posted on the Circuit Cellar FTP site. There are three source files, which correspond to two independent modules and the logic that ties them together. Each source file defines one or more logic blocks in the form of modules. Like software functions, each logic block has a set of parameters that represent its inputs and outputs. Unlike software functions, these inputs and outputs are electrical connections, representing wires. To use one logic block in another module, you instantiate a copy of the block in your own logic. When you do this, you give each instance its own name and specify which signals in your module will connect to which inputs and outputs in that instance. Think of modules as a definition of a chip, and instantiating one as buying a chip to use.

First, I needed a way of decoding the binary number into a three-digit decimal number. In bcd.v there is a large case table, with one entry for each input combination. Each case describes the three output digits. I actually used a script to generate this, rather than type it all in by hand, but at least I didn't need to try to figure out the logic behind each output bit the Xilinx tools did it all for me.

Next, I needed a way to map the binary encoding of a digit into a seven-segment encoding for that digit. There are two of these in sevenseg.v, as the hundreds digit has only three possible values. Adding a smaller table for that digit reduces the amount of internal logic needed. Again, I used a case table to describe each combination, with default entries (not all binary inputs are valid) of "don't care" to help reduce the logic needed.

The last module is the top-level module for this chip, unimaginatively named top.v (see Listing 1). The other two modules had inputs and outputs, but they existed only for referencing from other modules. For the top-level

"Producing prototypes

Creative"

on-the-fly allows me to be more

- Declare your independence from board houses

- Affordable, entry-level price tag

- The best milling speed, resolution, and accuracy in the industry

- Single-sided, double-sided, and multilayered machining without hazardous chemicals

- Optional vacuum table and autosearch camera for layer alignment

ProtoMat<sup>®</sup> S-Series PCB Milling Machines

For complete details visit: www.lpkfusa.com or call: 1-800-345-LPKF

# 3 PORT INTERFACE MIDIO RS-485 to Ethernet Converter

110100101110100110010100110

Only

\$**170**

#### **Powerful feature**

- Protocol converter RS485 between Ethernet

- Offer TCP/IP Communication to Devices with RS485 I/F

| Specification                                                                                         |                                                                                                                              |                                                     |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|

| Network                                                                                               | : TCP, UDP, DHCP, ICMP, IPv4, ARP, IGMP, PPPoE, Ethernet, Auto MDI/MDIX , 10/100 Base-TX Auto negotiation (Full/half Duplex) |                                                     |  |

| Serial                                                                                                | : RS485 3 Ports, 1,200~115,200 bps, Terminal block I/F Type                                                                  |                                                     |  |

| Control program : IP Address & port setting, serial condition configuration, Data transmit Monitoring |                                                                                                                              |                                                     |  |

| Accessory                                                                                             | : Power adapter 9V 1500mA, LAN cable                                                                                         |                                                     |  |

| Etc                                                                                                   | : - DIP Switch(485 Baud Rate setting)                                                                                        | - LED: Power, Network, 485 Port transmission signal |  |

· • • •

# MP3P DIY KIT, Do it yourself

# (Include Firmware Full source Code, Schematic)

# • myAudio (MP3 DIY KIT IDE)

#### **Powerful feature**

- MP3 Encoding, Real time decoding (320Kbps)

- Free charge MPLAB C-Compiler student-edition apply

- Spectrum Analyzer

- Application: Focusing for evaluation based on PIC

- Offer full source code, schematic

#### Specification

Microchip dsPIC33FJ256GP710 / 16-bit, 40MIPs DSC VLSI Solution VS1033 MP3 CODEC NXP UDA1330 Stereo Audio DAC Texas Instrument TPA6110A2 Headphone Amp(150mW) 320x240 TFT LCD Touch screen SD/SDHC/MMC Card External extension port (UART, SPI, 12C, 12S)

#### **Powerful feature**

- Play, MP3 Information, Reward, forward, Vol+/-

- Focusing for MP3 Player

- SD Card interface

- Power: battery

- offer full source code, schematic

| Item          | Specification                                   |

|---------------|-------------------------------------------------|

| MCU           | Atmel ATmega128L                                |

| MP3 Decoder   | VS1002 / VS1003(WMA)                            |

| IDE Interface | Standard IDE type HDD(2.5", 3.5")               |

| Power         | 12V, 1.5A                                       |

| LCD           | 128 x 64 Graphic LCD                            |

| Etc           | Firmware download/update with AVR ISP connector |

### Powerful feature

- Play, MP3 Information, Reward, forward, Vol+/-

- Focusing for full MP3 Player (Without case)

- IDE Interface

- Power: Adapter

- Offer full source code, schematic

# www.icbank.com

module, the inputs and outputs are the pins on the chip. There are eight inputs for the binary number, and 21 outputs for the LED segments. There were enough pins and logic cells left over to add a pair of latch enable pins, two types of blanking (display and leading zero), and an output polarity control pin.

While Verilog looks like generic software programming code, it's describing hardware. You can follow the interconnections in top.v, as I coded the logic blocks from the input pins through to the output pins. First, I latched the input pins into a register called ibinh (input binary, held). I connected this register to the BCD decoder b0, returning the three digits as bcd2, bcd1, and bcd0. Next, I added logic to detect when leading zeros were present (1z2, 1z1—the third digit is always on) and to compute the blanking signals blank2 through blank0.