## PCB的布线

最短路径、减少干扰

# PCB布线流程

- 1. 了解制造厂商的制造规范 线宽、线间距、过孔要求、层数要求

- 2. 确定层数并定义各层的功能

- 3. 设计布线规则 线宽、线间距、过孔大小

- 4. 定义不同net的走线宽度

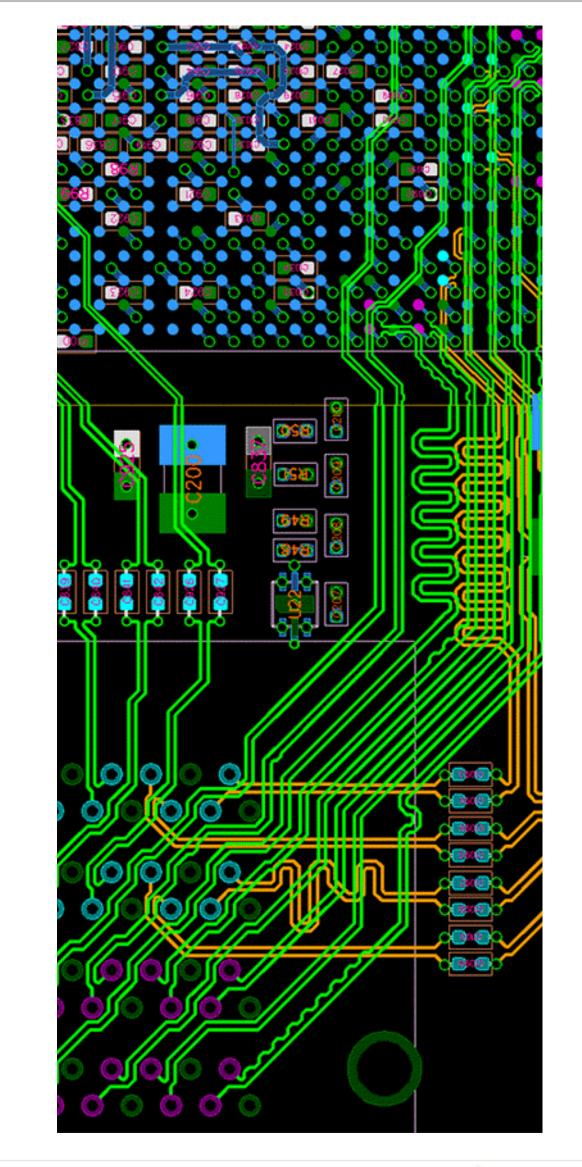

- 5. 关键信号线走线 电源、时钟、差分信号、敏感的模拟信号....

- 6. 其它信号线走线

- 7. 铺地/电源

- 8. DRC检查

- 9. 对照原理图上的连线逐线高亮检查

- 10.调整丝印

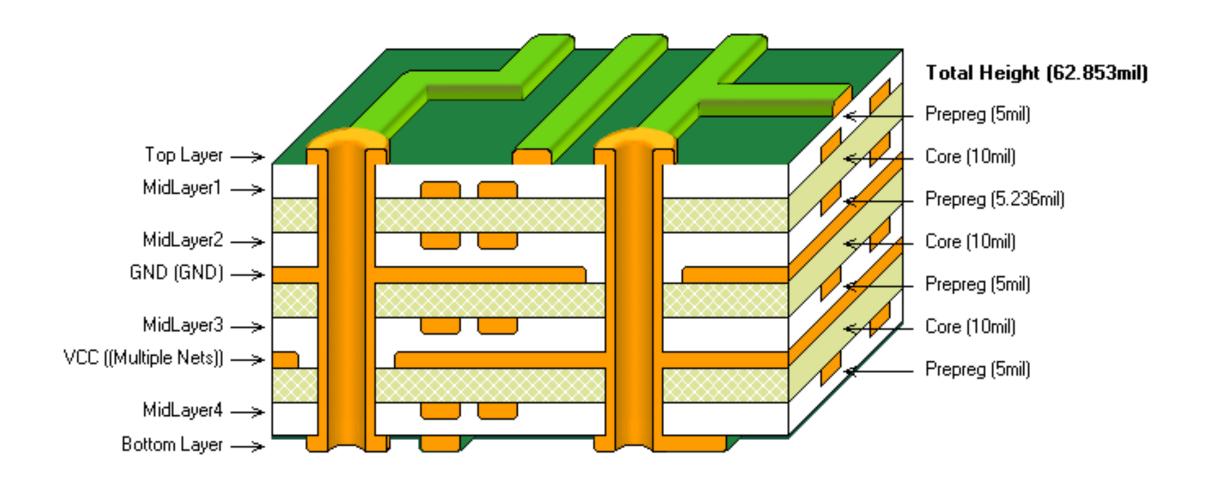

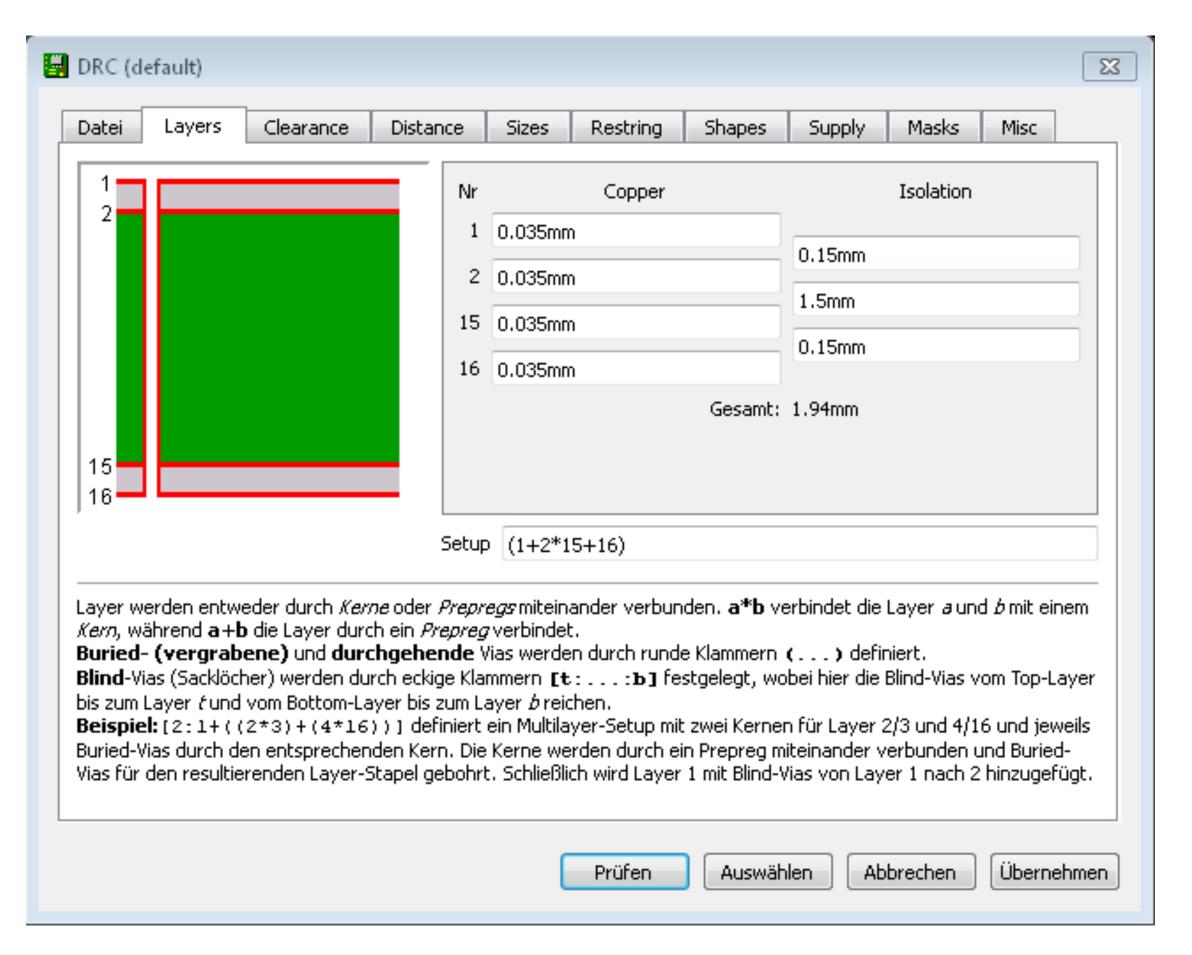

#### 选择层数

- 根据电路特点规划层数:

- 高速/低速、模拟/数字、阻抗要求

- 器件封装及散出

- 抗干扰、可靠性要求

- 成本

- 定义各层的功能

- 关闭未曾用的层

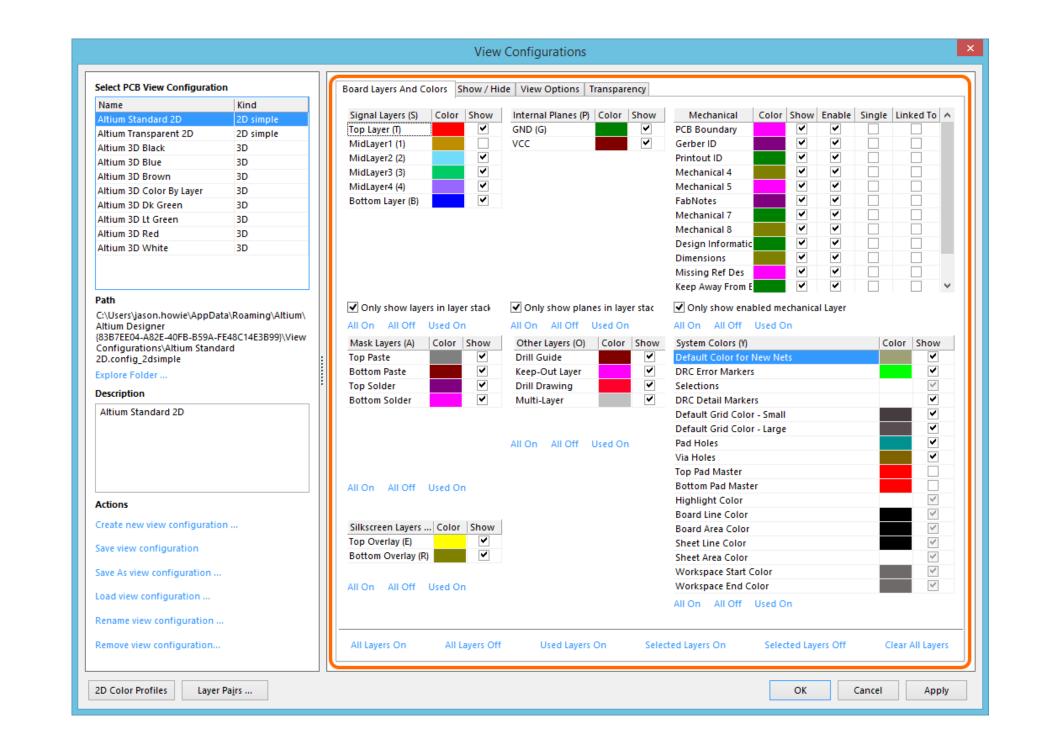

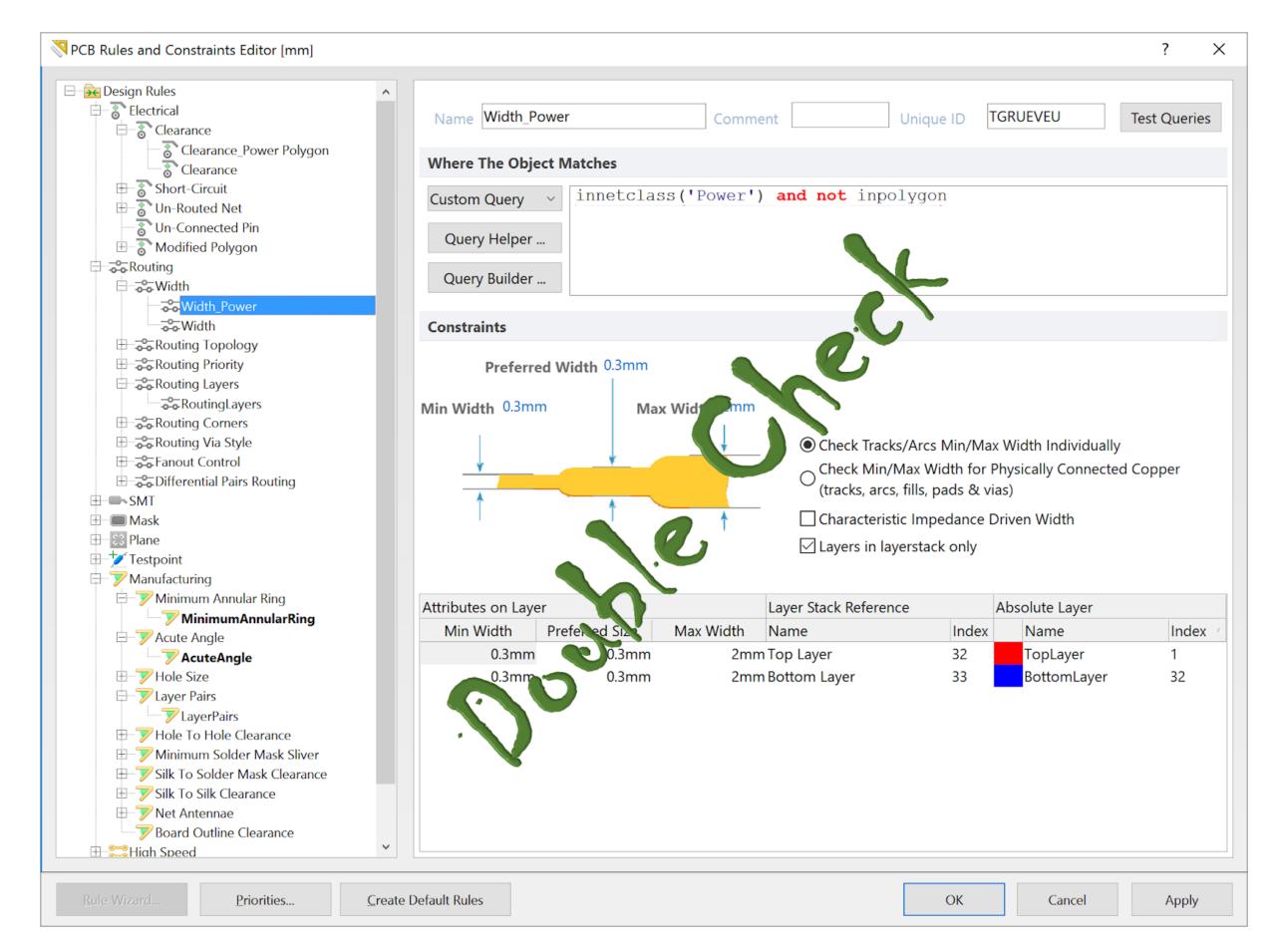

### 设定布线规则

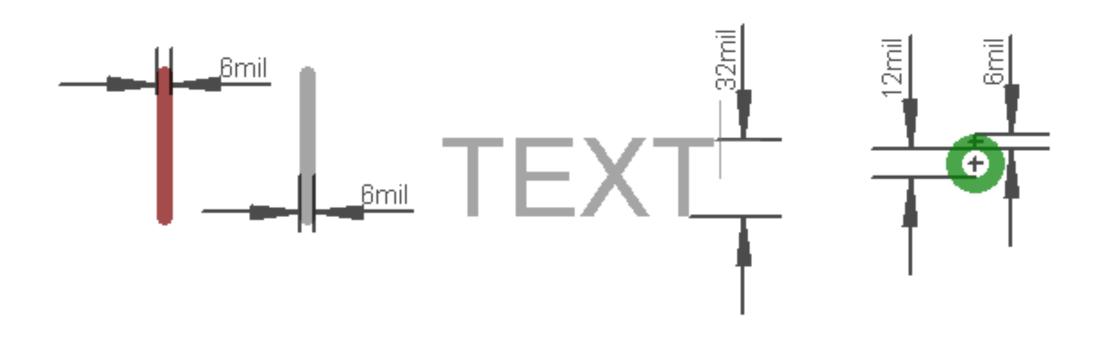

\_Minimum trace/silkscreen/text/hole size

\_Minimum trace/via/pad space

- · 线宽 不同的net可以单独定义

- 过孔形状和孔径(内径、外径)

- 丝印的文字字体和字号

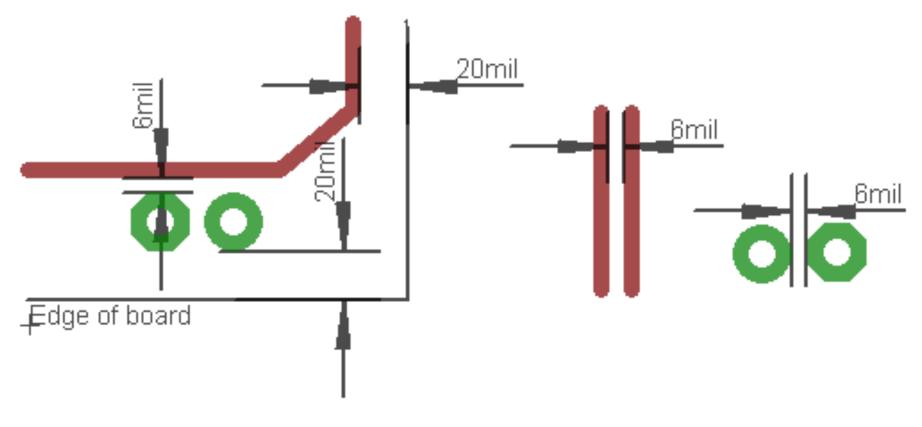

- 安全间距:

- 走线和走线之间

- 走线和孔径之间

- 孔径和孔径之间

- 走线/孔径和板卡边沿之间

- 走线层面和方向 此处可设置使用的走线层和每层 的主要走线方向。

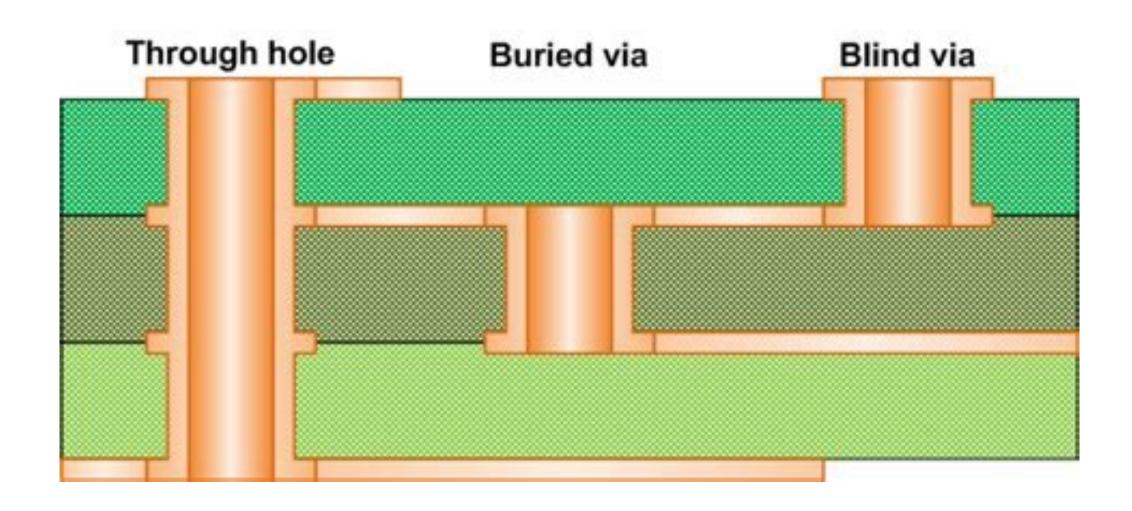

#### 过孔的选择

- · 从成本和信号质量综合考虑选择合理的尺寸

- · PCB板上的信号走线尽量在同一层,尽量不要使用不必要的过孔,布局的时候规划好走线

- · 高速数字信号线(尤其是时钟信号)尽量避免跨层走线,减少过孔对信号的反射和干扰

- · 电源和地的管脚要就近放置过孔,过孔和管脚之间的引线越短越好,同时电源和地的引线 尽可能粗以减少阻抗

- · 在信号换层的过孔附近放置一些接地的过孔,以便为信号提供最近的回路

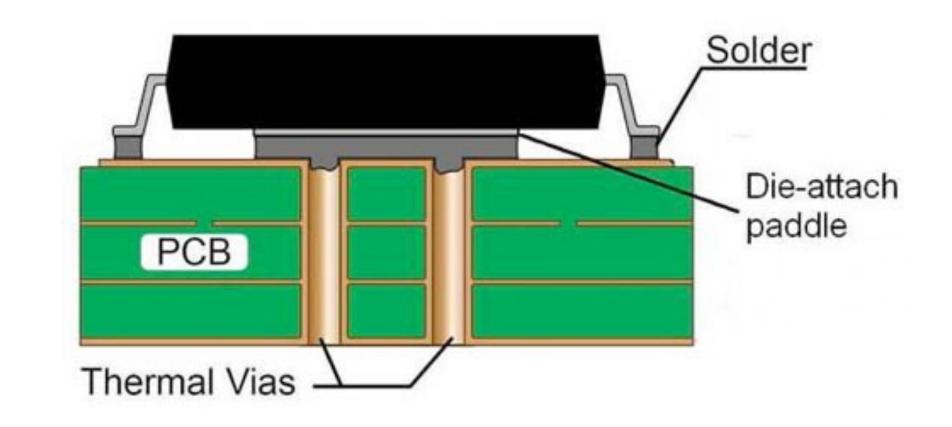

- 利用过孔进行导热

#### 一般走线规则

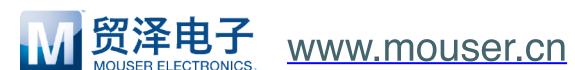

- 走线方向

- 输入和输出端的导线应尽量避免相邻平行

- 相邻层的走线方向成正交结构

- 避免将不同的信号线在相邻层走成同一方向,以减少不必要的层间窜扰

- · 当 PCB 布线受到结构限制(如某些背板)难以避免出现平行布线时,特别是在信号速 率较高时,应考虑用地平面隔离各布线层,用地线隔离各信号线

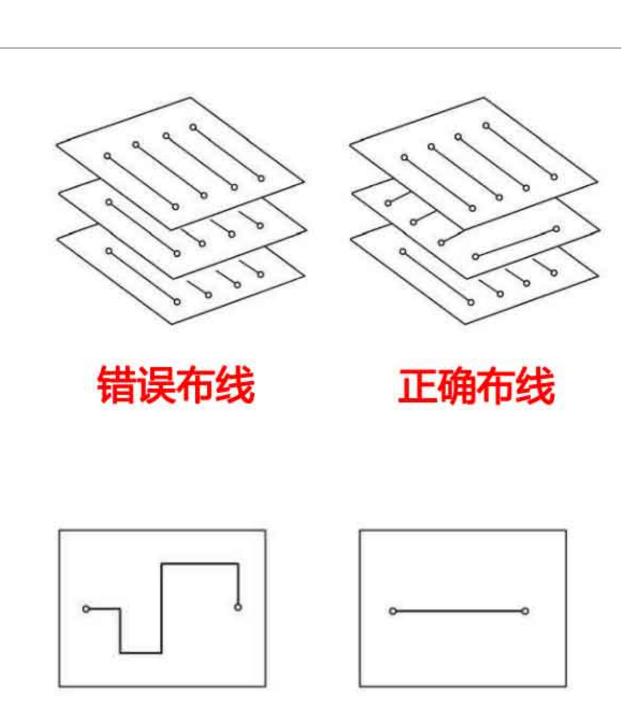

- 器件和器件之间的走线尽可能短且直

- 电源及临界信号走线使用宽线,电源线要根据电流的大小计算需要的宽度

- 确保模拟、数字线路相互分离,不要将数字信号线和模拟信号线并行布线,避免在ADC 封装的下方铺设数字信号线

- 相同属性的一组总线, 应尽量并排走线, 做到尽量等长。同一级电路的接地点应尽量靠近, 并且本级电路的电源滤波电容也应接在该级接地点上

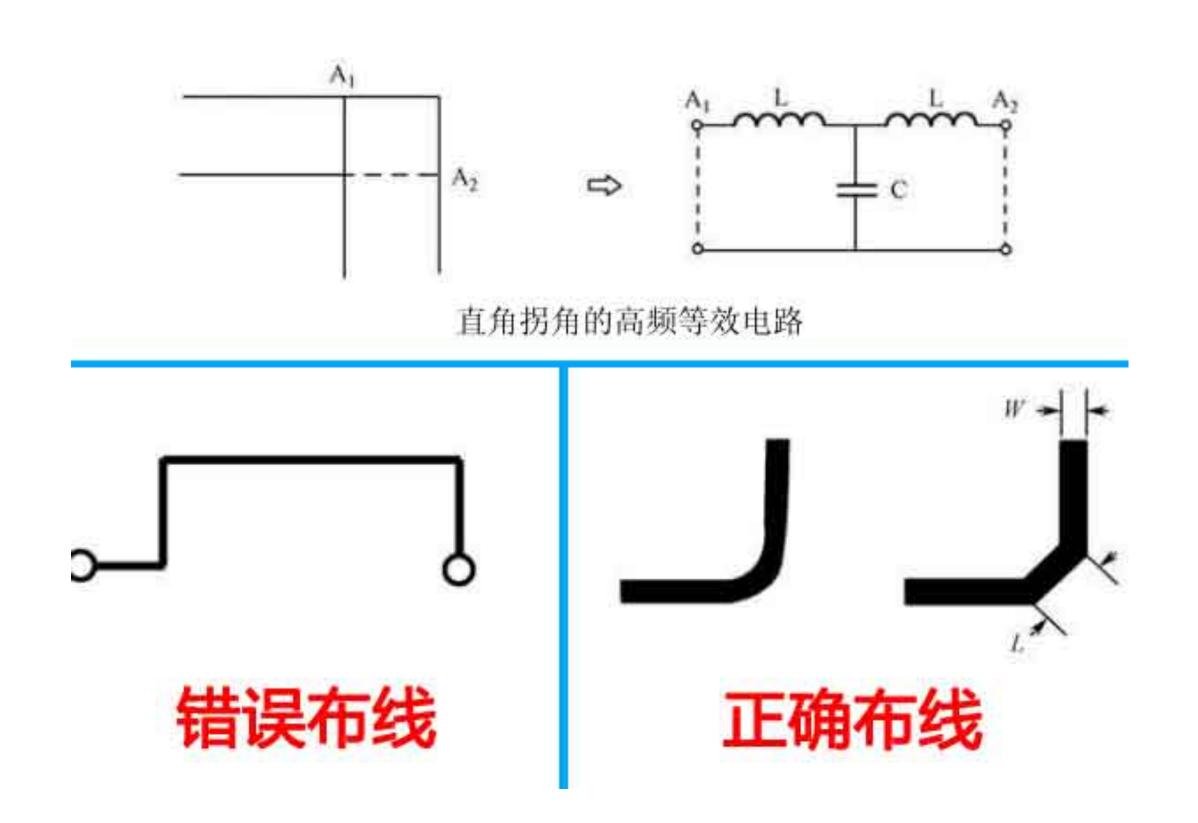

错误布线

正确布线

正确布线

错误布线

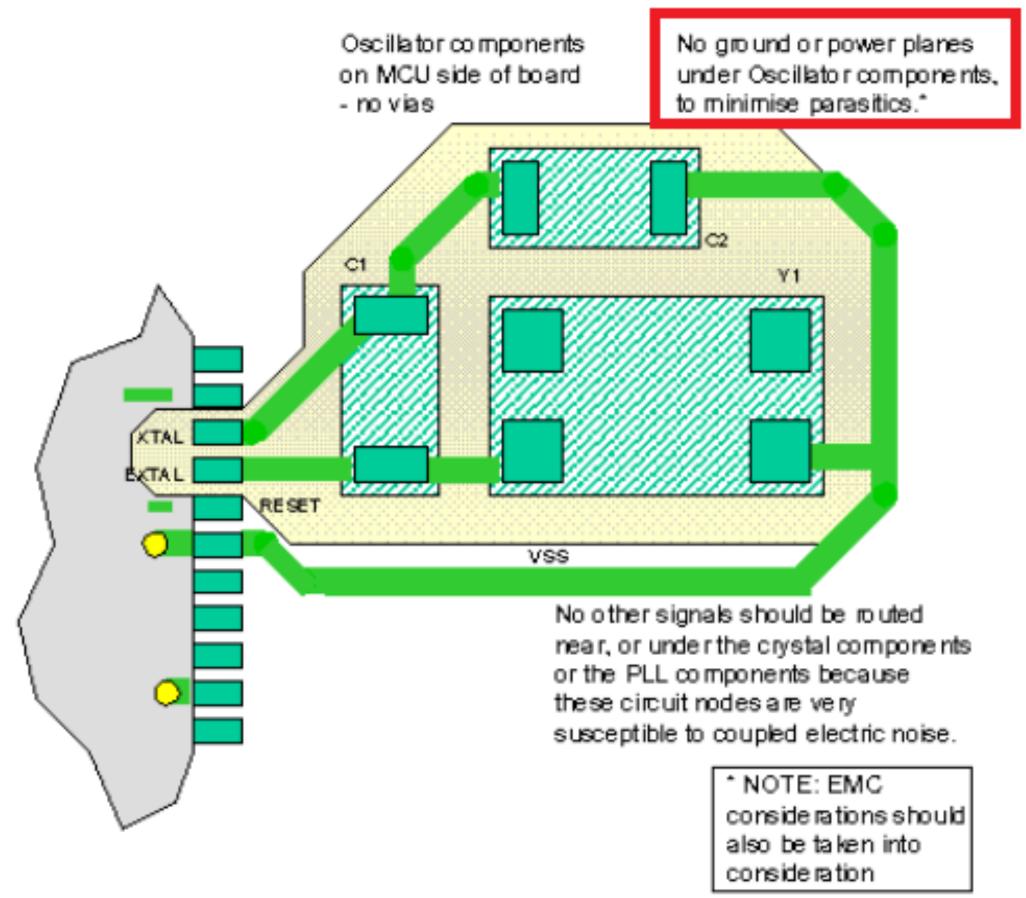

#### 时钟布线

Figure 4. Schematic of External Components

Figure 5. Recommended PCB Layout

- 晶振 连到其输入、输出端的线尽量短,最好不要有过孔,以减少噪声干扰以及分布电容的影响

- 晶振可以采用环绕敷铜,并将晶振外壳接地,以 改善晶振对其他元器件的干扰。

- 尽量避免和其它信号线并行走线,且应远离一般信号线,避免对信号线的干扰。

- 应避开板上的电源部分,以防止电源和时钟互相干扰,时钟电路下面不要有电源层或地层

- 当一块电路板上用到多个不同频率的时钟时,两根不同频率的时钟线不可并行走线。

- 时钟线还应尽量避免靠近输出接口。

#### 差分信号线

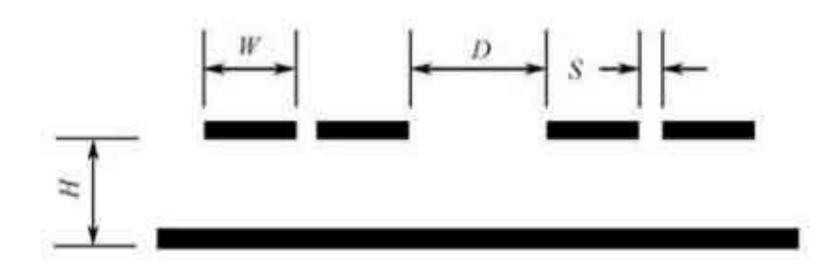

D一两个差分对之间的距离: S一差分对两根信号线间的距离: W一差分对走线的宽度: H一介质厚度

PCB 上的差分对走线

- 成对走线,尽量平行、靠近 保持差分对的两信号走线之间的距离S在整 个走线上为常数

- ·确保D>2S,以最小化两个差分对信号之间的串扰。

- 将两差分信号线的长度保持相等,以消除信号的相位差。

- 避免在差分对上使用多个过孔,因为过孔会产生阻抗不匹配和电感,必 须打孔的时候,应两线一同打孔。

#### 避免直角走线

- 在高速传输的时候,直角或锐角走线在拐角处产生额 外的寄生电容和寄生电感,影响高速信号的传输,对 于低速的信号,影响可以忽略不计

- 尽量不采用直角的是为了避免工艺上的问题

- 在走线确实需要直角拐角的情况下,可以采取两种改 进方法:

- ① 一种是将90°拐角变成两个45°拐角

- 2 另一种是采用圆角

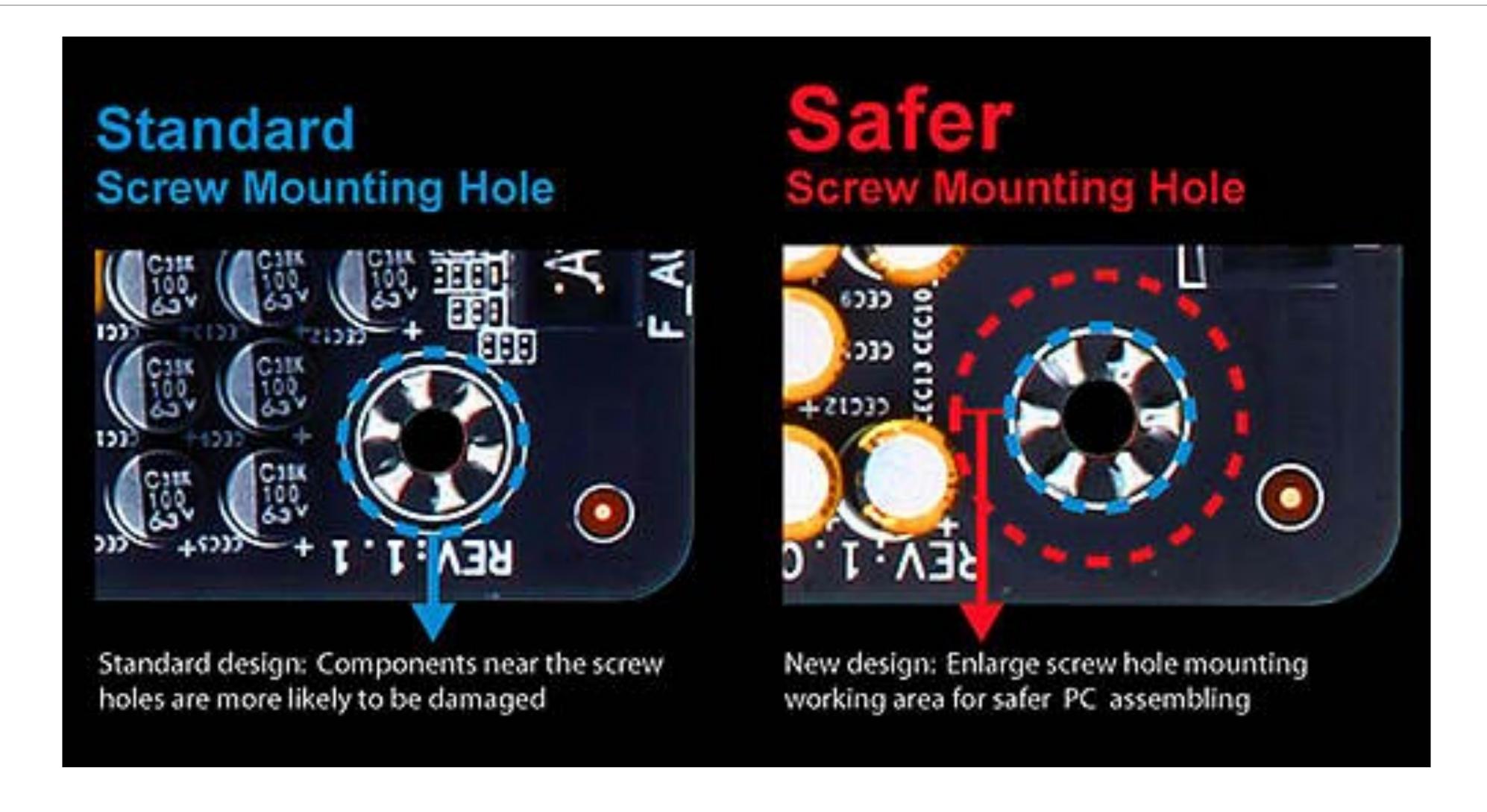

#### 在安裝孔和走线之间保留一定的距离

#### 接地和填充

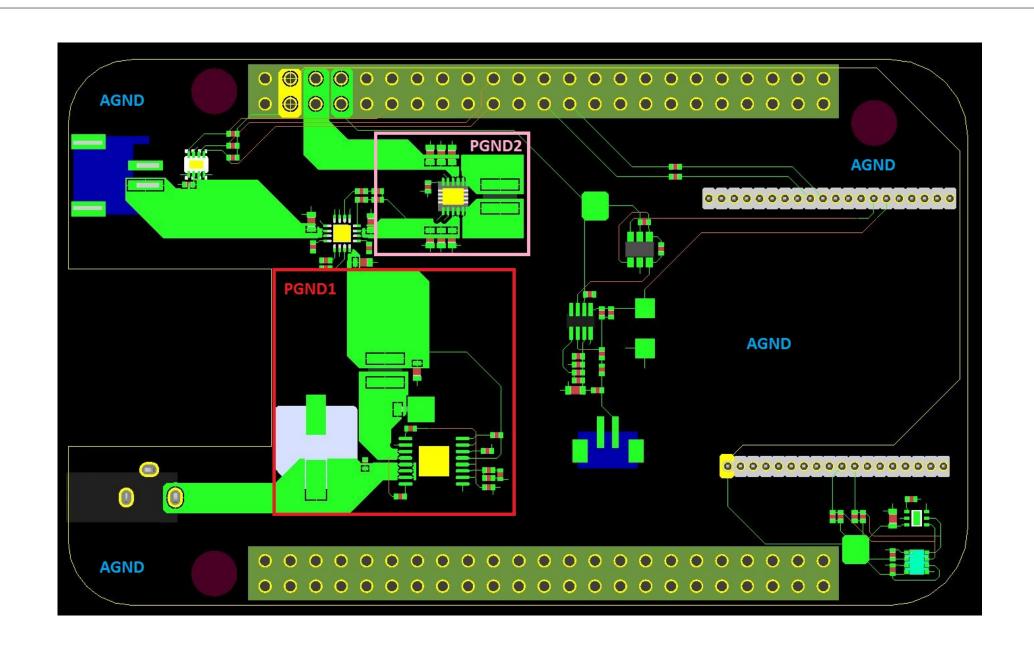

- 多层板可以采用独立的地层,数字信号分布在一侧,模拟信号分布在另一侧

- 最好是地线比电源线宽,它们的关系是:地线>电源线>信号线。

- 数字地与模拟地分开

- 用大面积铜层做地线用,把没被用上的地方都与地相连接作为地线用

- 抑制高频干扰、降低电源或地线的阻抗、 方便布线

- 注意分割铺设的区域、设定好铺设规则

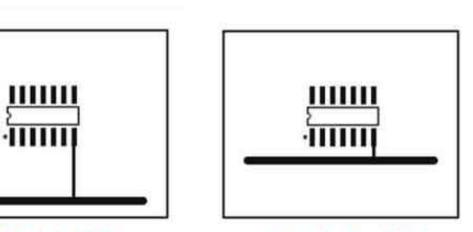

#### 电源布线及去偶

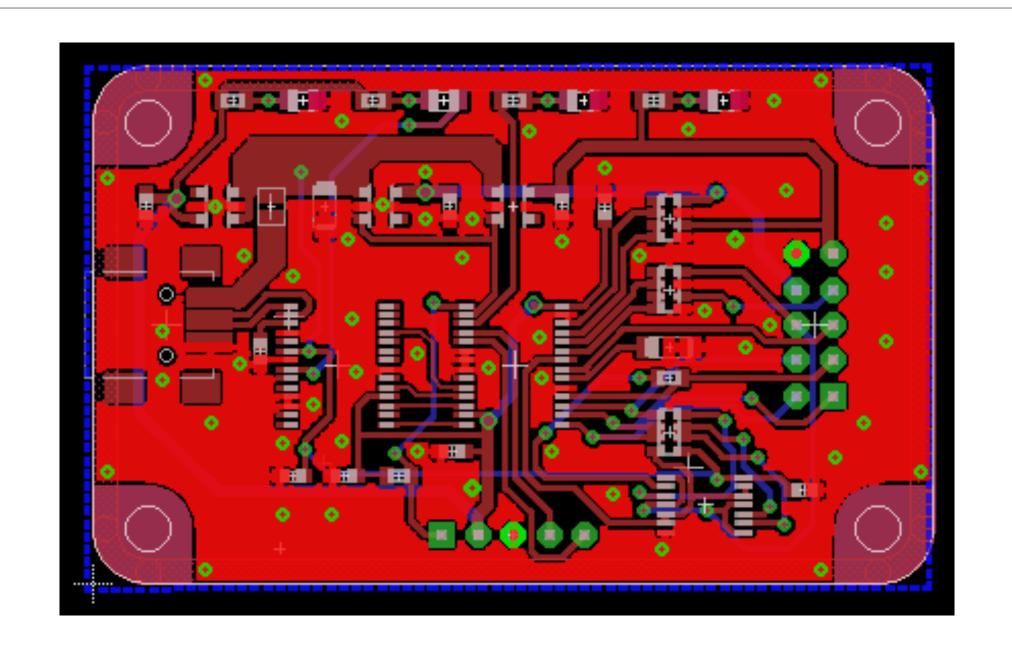

- 电源线尽可能粗 减少环路阻抗, 从而降低压降、干扰。

- 供电方向 与数据、信号的传递方向相反,即:从末级向前级推进的供电方式,这样有助于增强抗噪声能力。

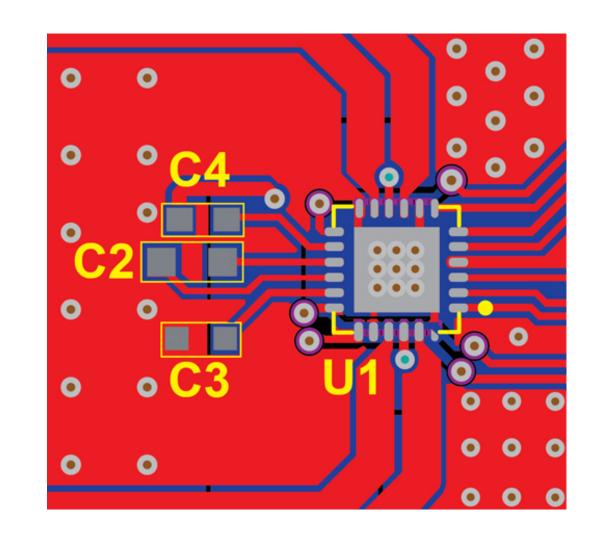

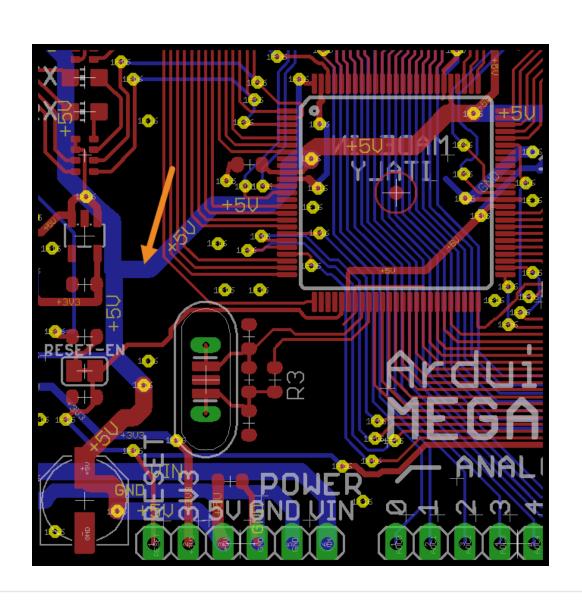

- ·采用两个电源平面分别连接所有AVDD和DVDD,每个PCB板的AVDD和DVDD引脚至少增加一个10µF去耦电容。

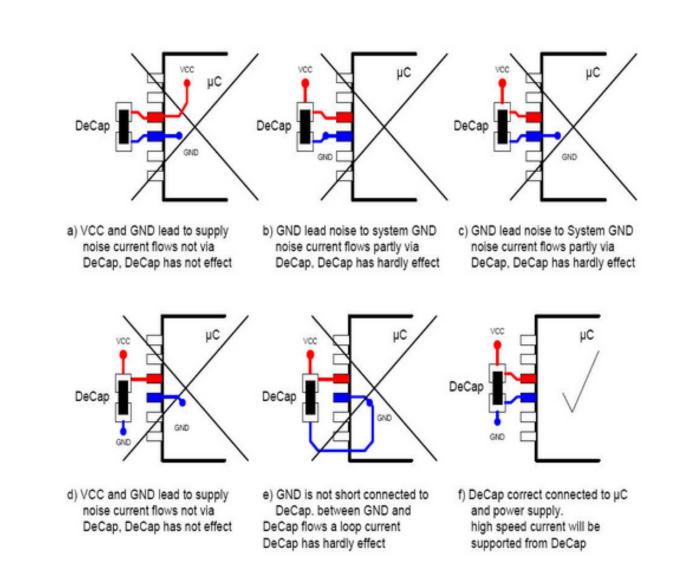

- · 在器件的AVDD和DVDD的引脚与地之间连接0.1µF陶瓷去偶电容,电容须靠近器件放置,以便降低寄生电感,尽可能采用贴片电容

- 去偶电容的多少和值取决于器件工作的速度、负载、管脚数量、布线难度,数字电路的如果有多个电源管脚,尽可能在每一个电源管脚放置一个0.1uF的去偶电容,当有些电源管脚距离很近且布局困难的时候,这些电源管脚可以共享一个去偶电容

Always

poor

Often

adequate

Tracks as short and wide as practicable

This example shows a decoupling capacitor

The same considerations apply for IC connections to planes

www.mouser.cn

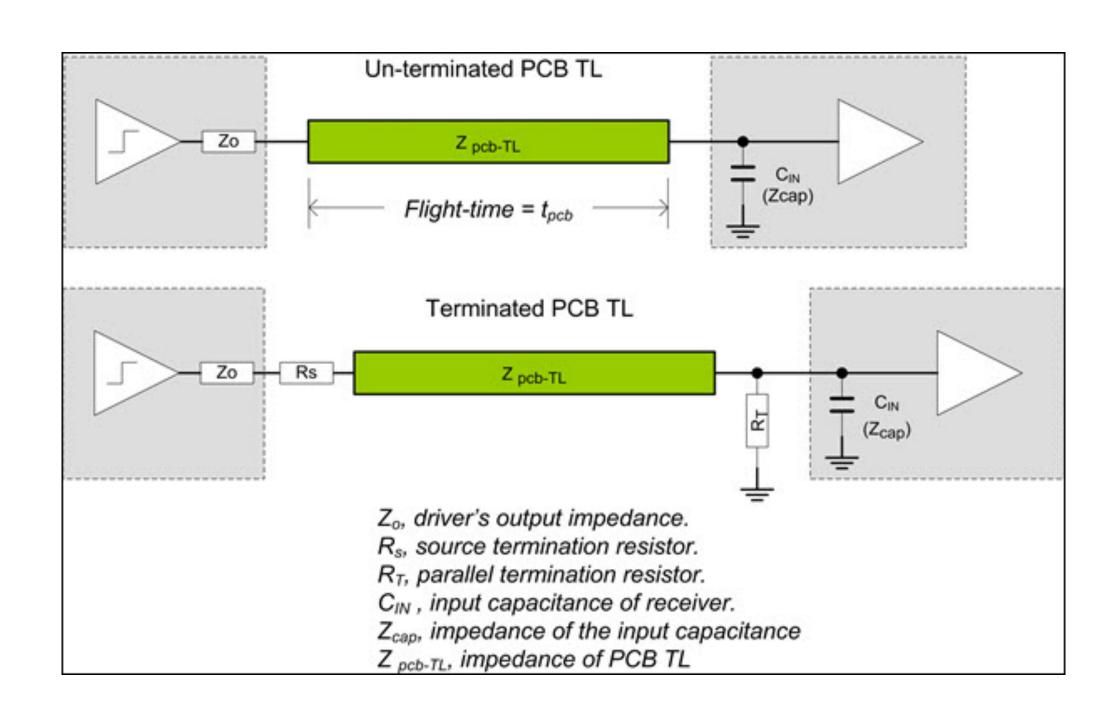

#### 走线阻抗及终端匹配

- · 高速数字电路和射频电路,对PCB导线的阻抗是有要求 的, 低速电路可以忽略

- 发送端阻抗 == 走线阻抗 == 接收端阻抗要匹配,以达到 最佳的传输效果,降低反射

- 走线阻抗要根据板材计算其宽度, 走线过程中尽可能不 要出现阻抗的变化 - 线宽一致

- 减少跨层走线,尽可能少用过孔

- 注意发送端阻抗匹配 串行匹配电阻,接收端阻抗匹配 -并行匹配电阻,放置的位置

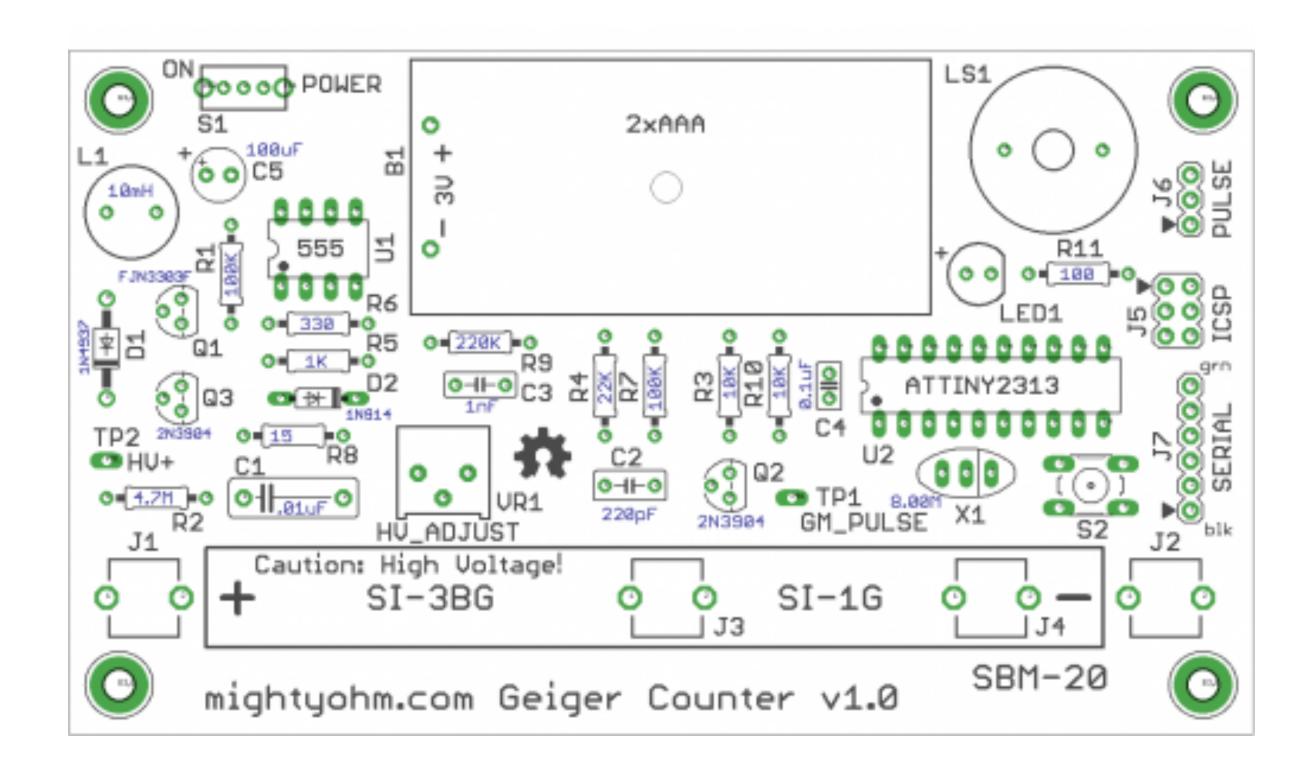

#### 丝盯

- · 在PCB上下两表面印刷上标识图案和文字代号的专用 层,开发者、测试、安装者、使用者都会用到

- 清楚、规则、整齐、归属明确、无歧义

- 字符不能覆盖在焊盘或过孔上,同一层的丝印不能互 相重叠

- 清楚表明元器件、连接器装联的方向,极性器件如指 示灯、三极管、跳塞、开关、端子、配线需要明确的 极性标识

- 器件密集的区域可以将丝印字符对应、有序地放置在 其它区域并加上适当标识

- · 丝印字体一般采用EDA软件支持的缺省字体,AD的不 好,需要修改

#### 检查

- 1. ERC (电气规则检查)

- 2. DRC(设计规则检查)-线宽、线间距、加工厂工艺要求、高速设置、短路

- 3. 对照原理图逐线高亮检查

#### 关于贸泽电子 - www.mouser.cn

- · 与非网/摩尔吧多年合作伙伴

- ・全球领先的电子元器件授权分销商

- · 700家原厂/500万现货库存

- · 小批量采购, 170元免邮费

- ・1-2周交货