# 原理图的设计和风格

设计不仅是给自己看的....

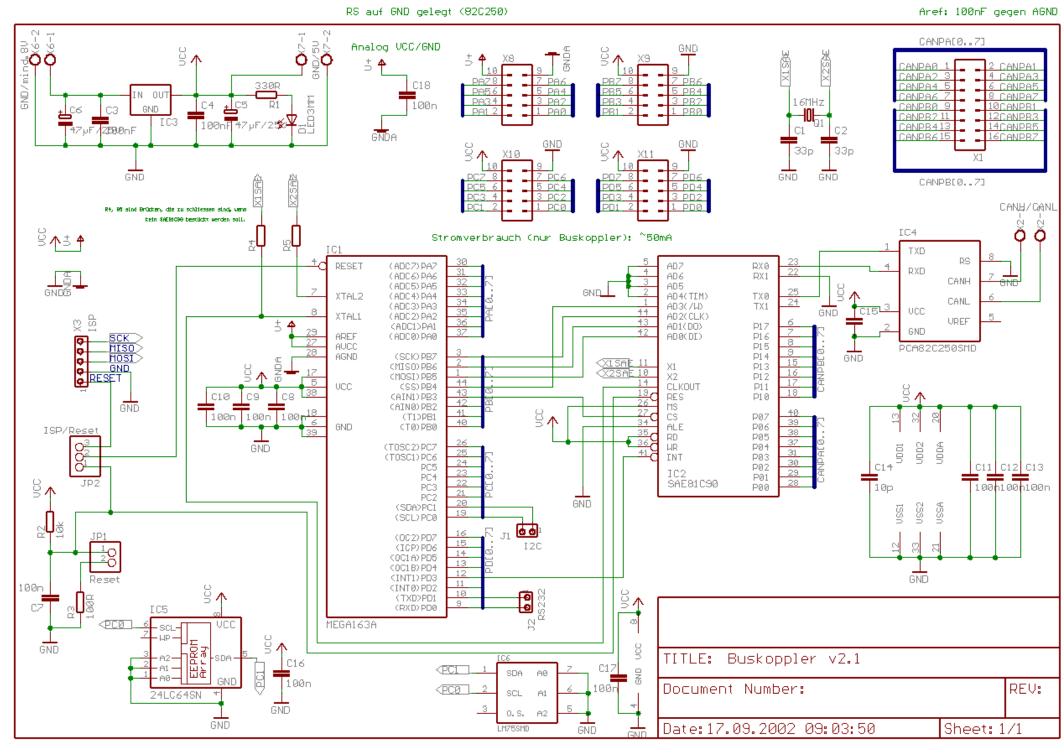

v2.1 RX1(SAE81C90) auf GND gelegt

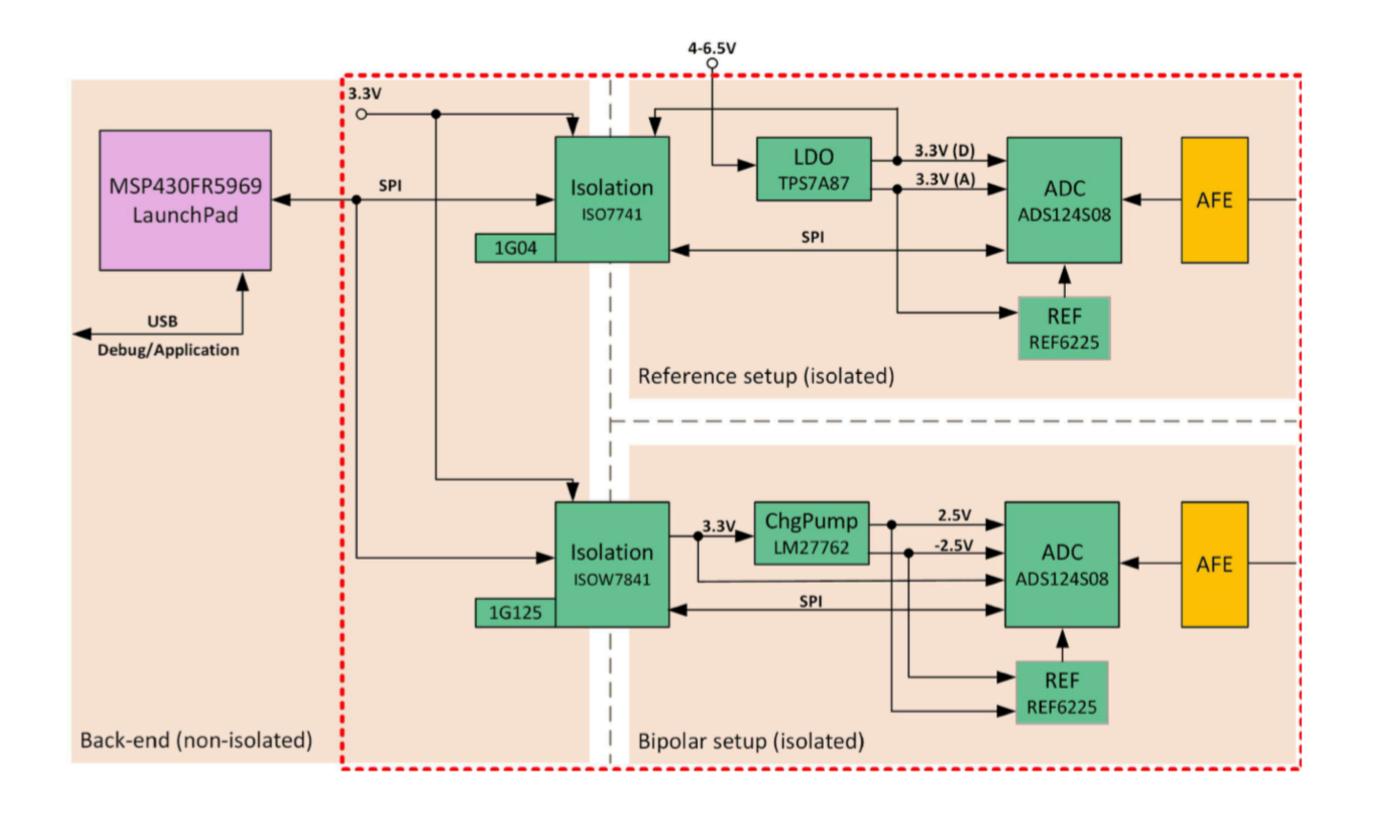

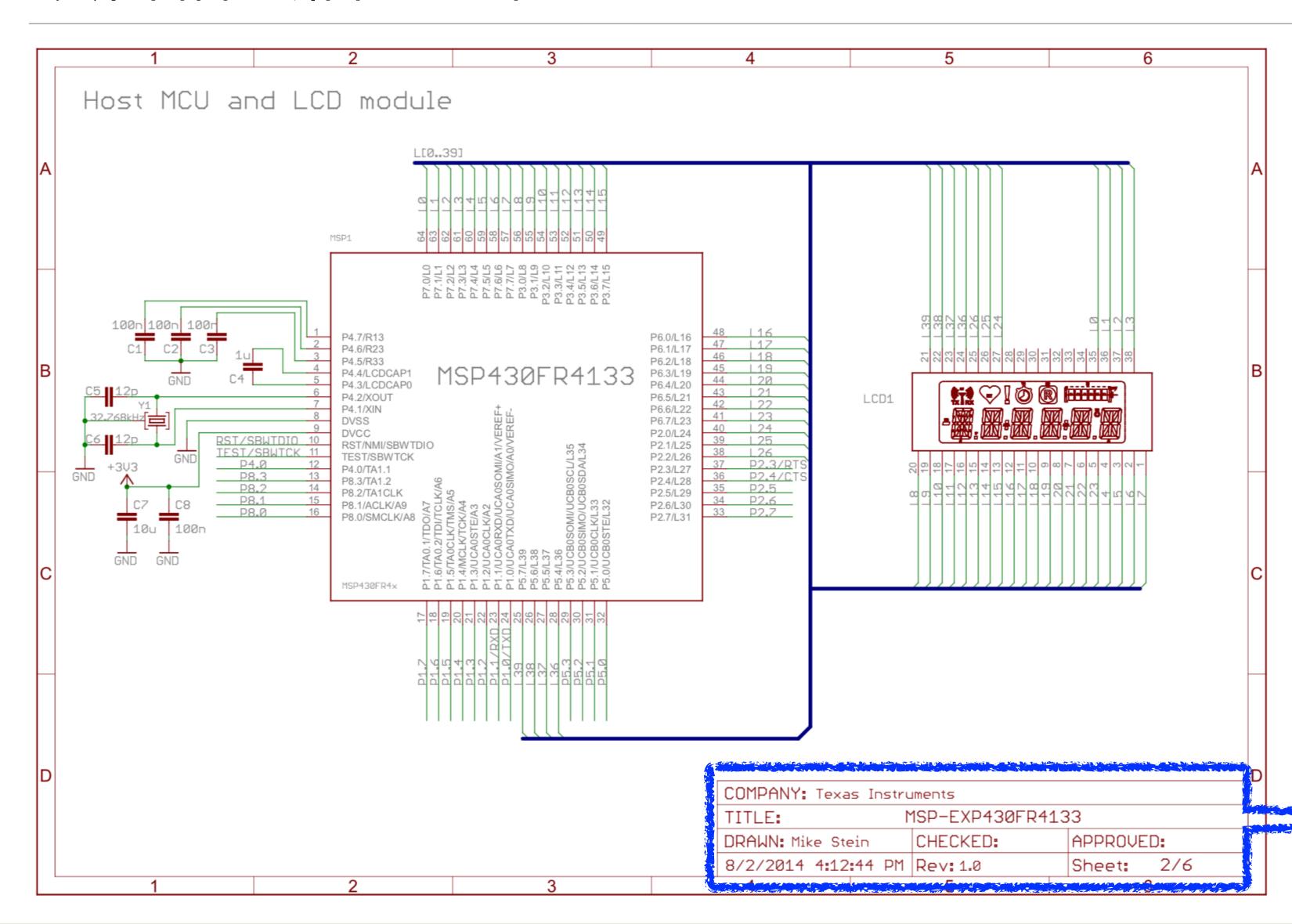

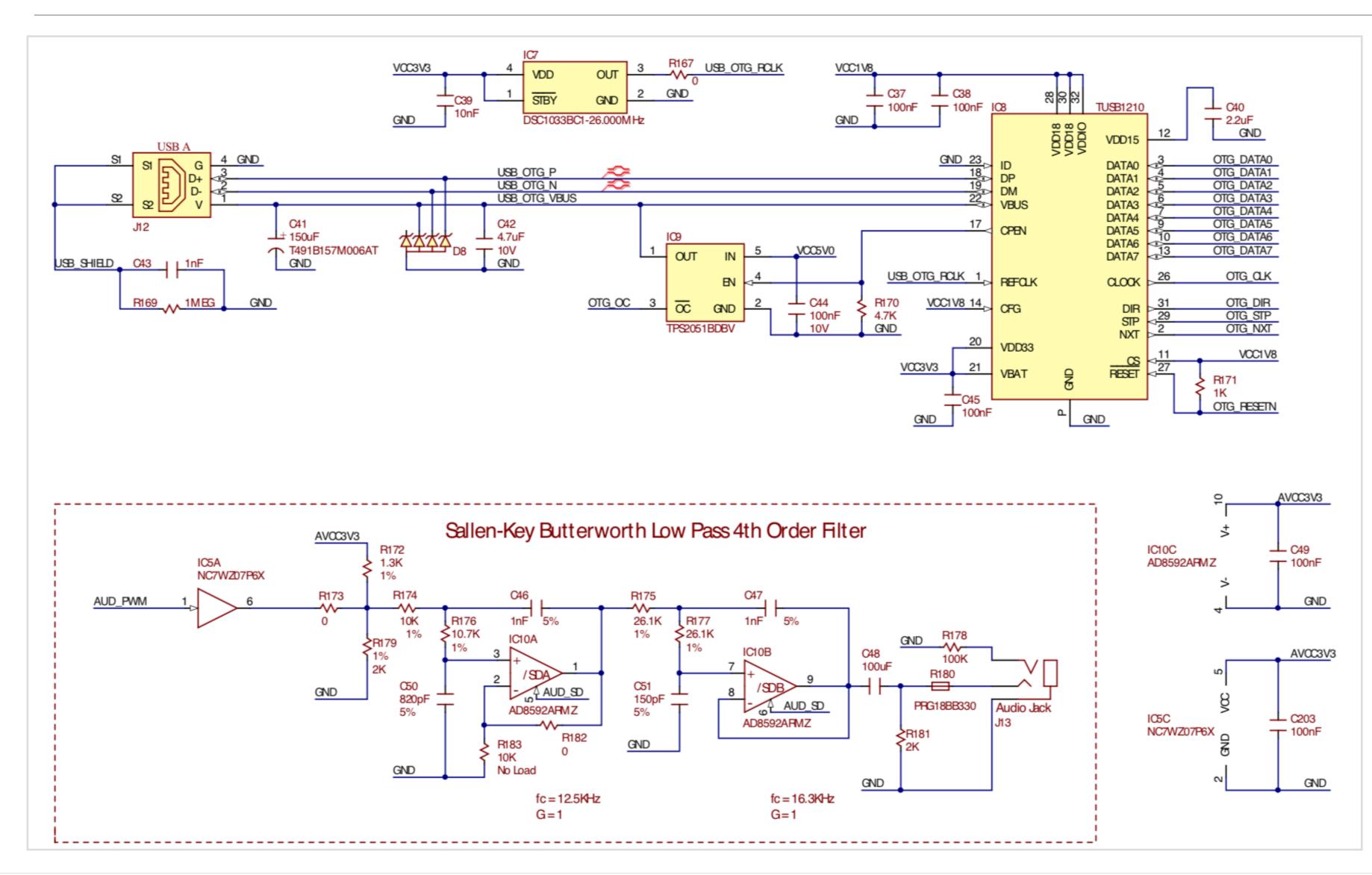

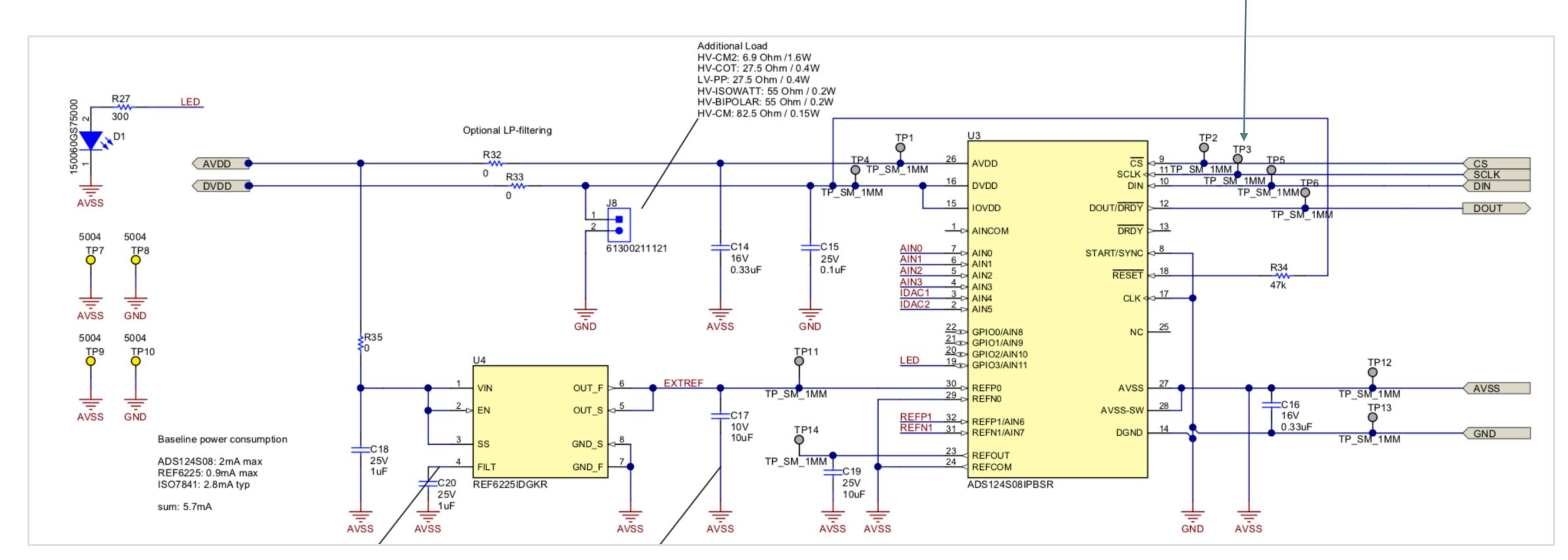

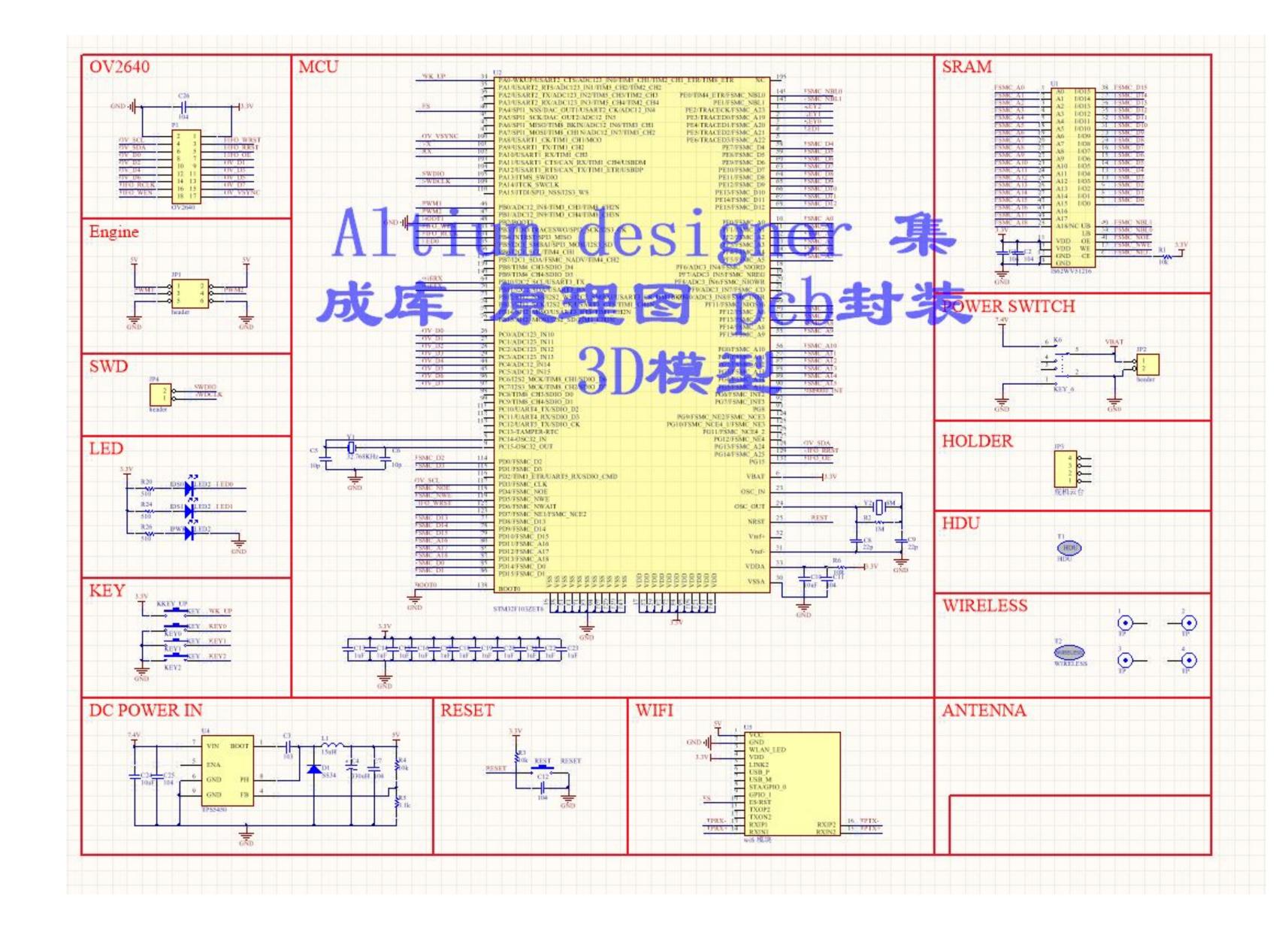

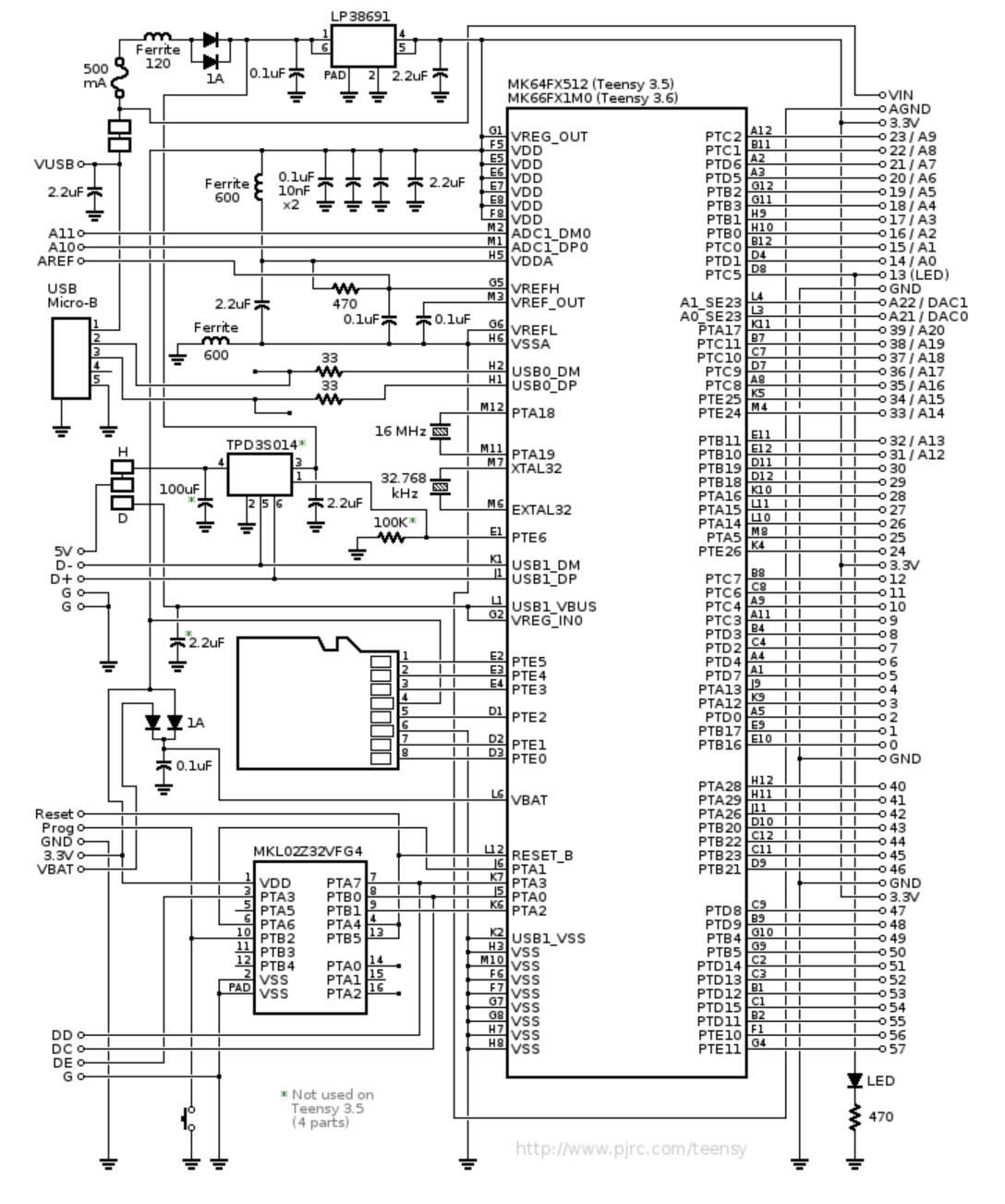

#### 系统框图

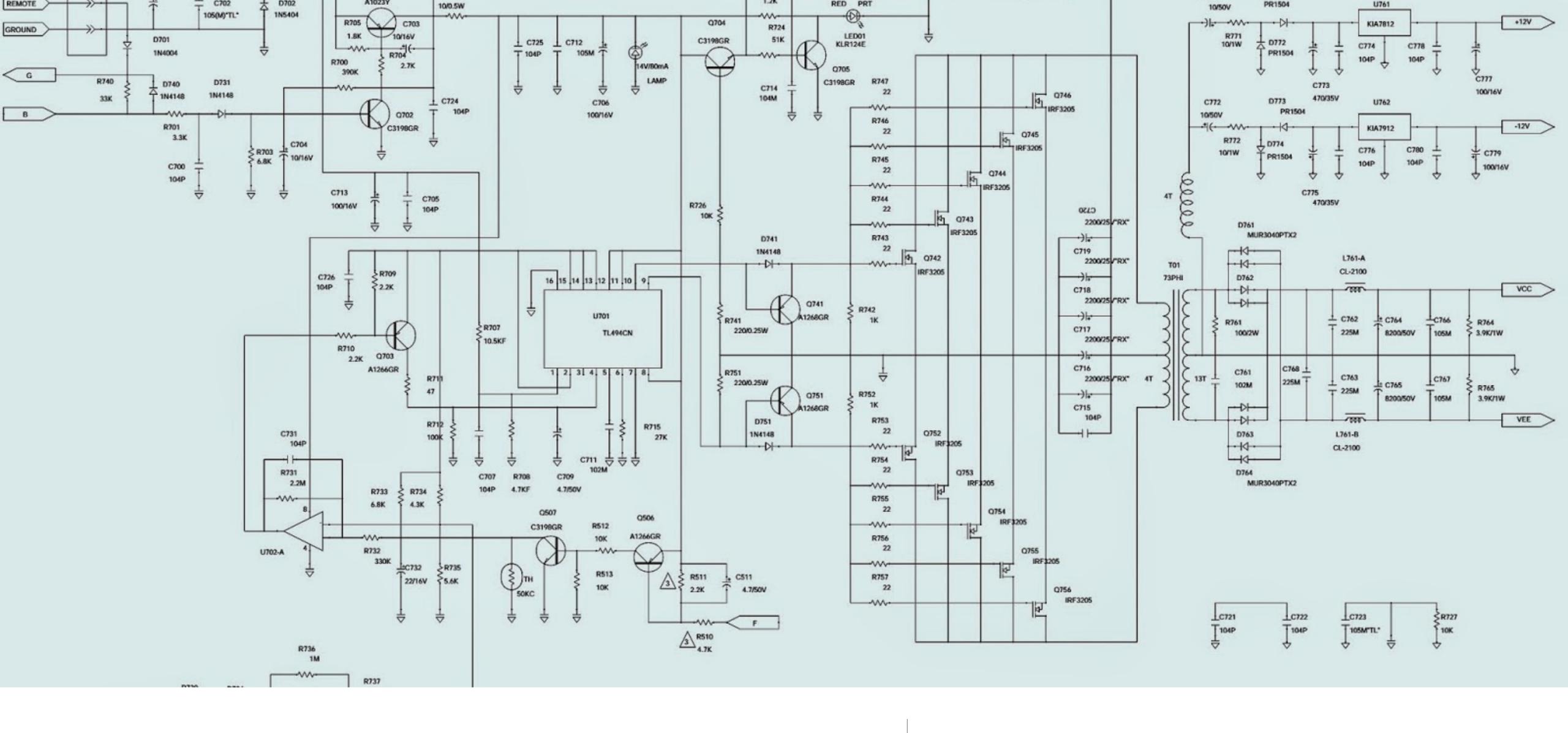

#### 系统原理图

Avcc: 10uF und 100nF gegen AGND

#### 原理图设计流程

- ①创建工程和文件

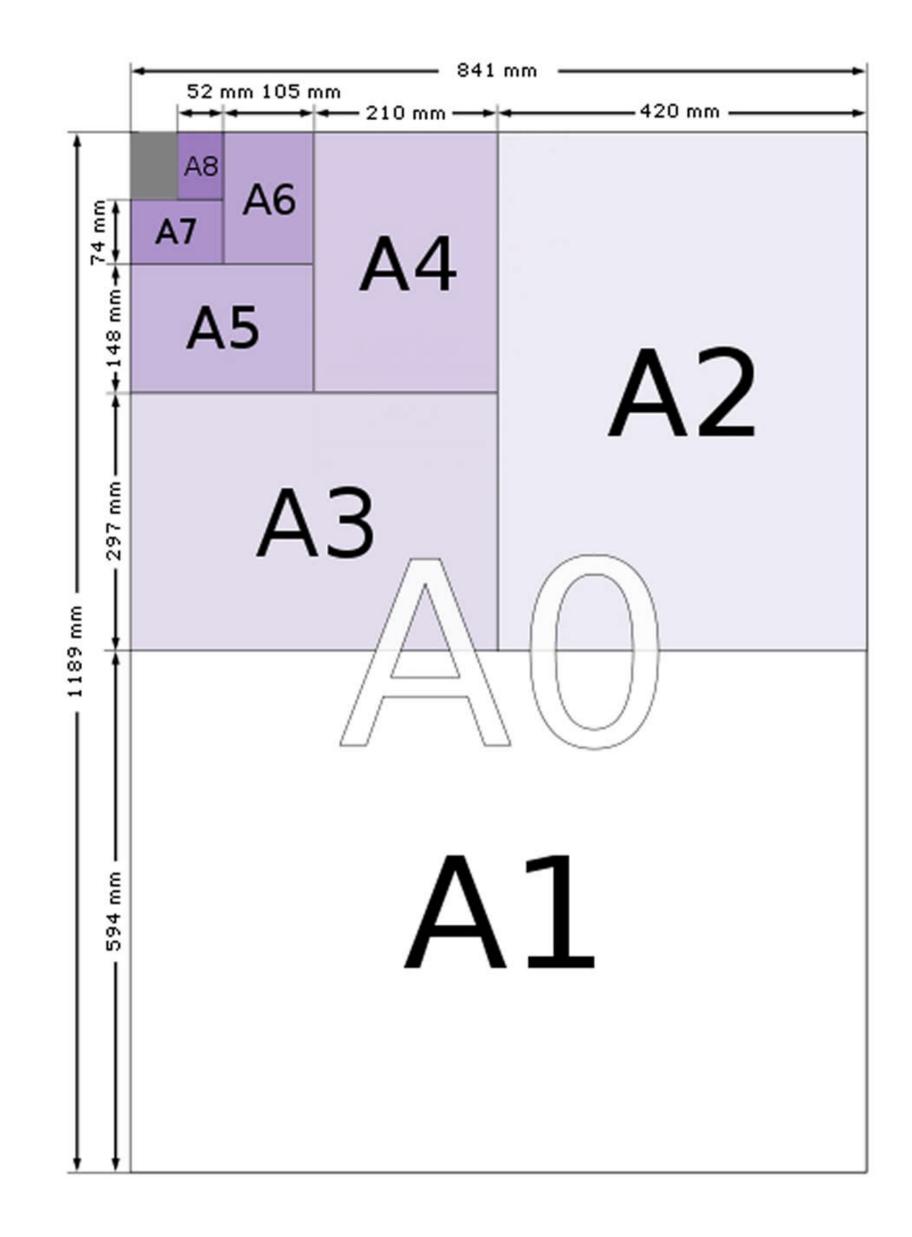

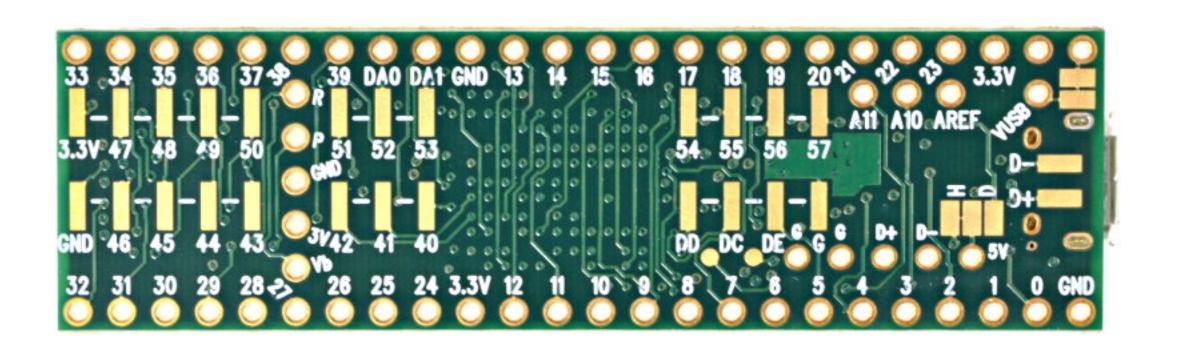

- ② **设置图纸大小:** 根据图纸的复杂程度、各元器件的原理图库,一般A4比较合适,一个设计可以采用多页

- ③ 设置文件环境:格点大小、格点属性、光标属性、电气格点属性、图纸颜色等

- ④ 加载元器件符号库:如果有已经构建好的符号,则直接加载来用,如果没有的话需要依照数据手册进行构建

- ⑤ 放置元器件: 合理化、按照信号流程、可以翻转、旋转放置,方便连线、清晰理解

- ⑥ **原理图连线**: 减少交叉,尽量少用最好是不用文字的Net进行标记

- (7) **调整修改原理图:** 网标有没有重复、错误的连接、虚连接

- ⑧ ERC检查(电气规则检查): 电气连接上的错误

- ⑨报表输出:产生用于布局布线的Netlist、用于采购元器件的BOM清单

- ⑩ **文件输出**:保存、备份、导出到PDF或其它格式、打印

# 可读性:方便阅读、理解并能够正确使用,减少由于误理解导致的设计错误

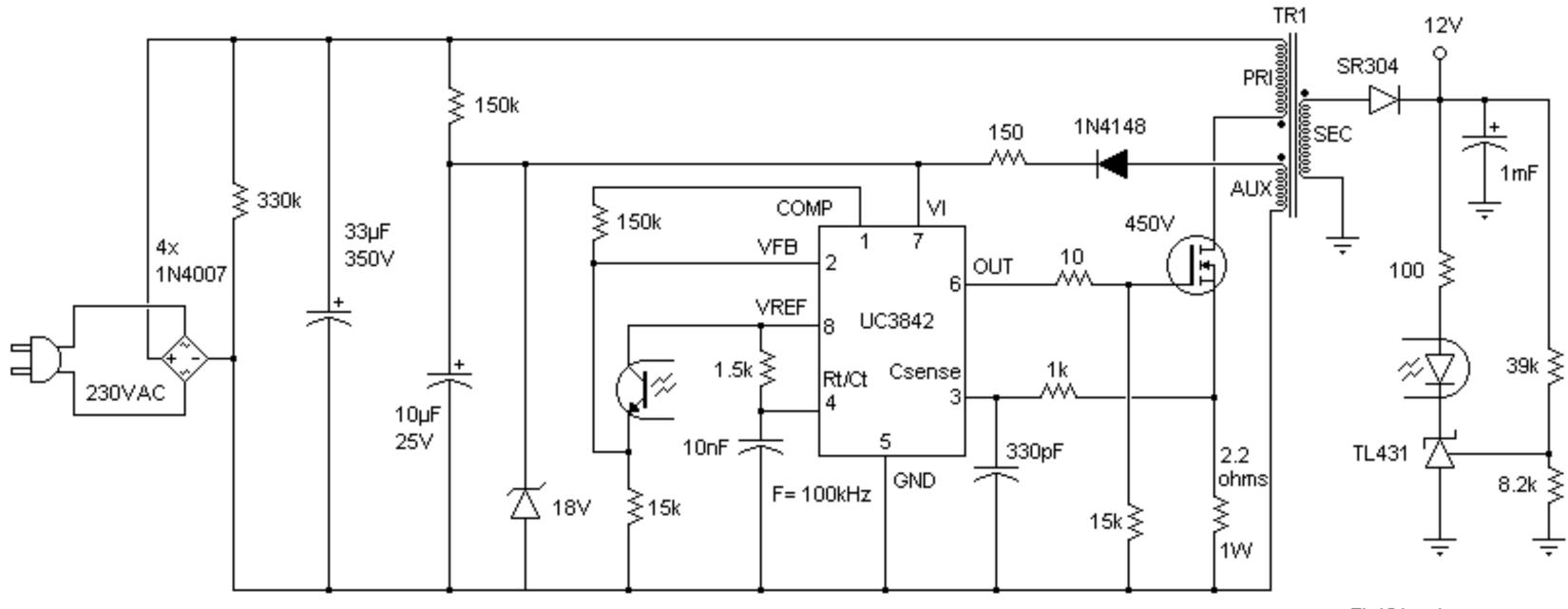

#### UC3842 Flyback Converter Auxiliary Power Supply 15W

http://uzzors2k.000webhost.com/

TR1: Standby flyback transformer from ATX supply

PRI = Winding with most inductance AUX = next highest inductance SEC = Remaining or third highest inductance

TL431 reference adjustable for variable output voltage

- · 给人阅读 从逻辑上理解电 路的构成、工作原理

- 给机器阅读-产生网表、用 于后期的布线

- 跟物理上的板卡没有直接对 应关系

## 图纸大小的选用

- · 根据电路的复杂程度选择A4、A3,便于打印、阅读

- · 可以分成多页,每个页面为独立的功能 处理器、 电源、存储、网络接口、视频等等

- · 设定合适大小的Grid 与原理图符号的Grid同步

# 项目相关信息的标注

- 单位

- 绘图人

- 版本号

- 时间

www.mouser.cn

# 信号流 - "左、上"到"右、下"

- 符合自然阅读习惯

- 先放置核心器件

# 关键信号放置测试点,关键器件关键信息加以说明

- · 标号、值 (comment)

- 重要的属性 耐压、精准度、功率等

- · 在PCB设计的时候需要注意的地方进行标注

- · 不宜放置太多不必要的信息,导致阅读困难

测试点 - TP

# 信号的连接

- ·尽可能不用net

- · 尽可能不要用区块来强硬割裂

- 直观、符合人的阅读直觉

## 其它要点

- · 容限大的电阻、电容值 / 封装尽可能统一, 以降低总体成本

- · 靠近某些管脚的关键器件(去耦电容、匹配电阻)需要在电路图上体现并尽可能 用文本标注

- · 字体、字号、排放位置要统一, 保证较强的可阅读性

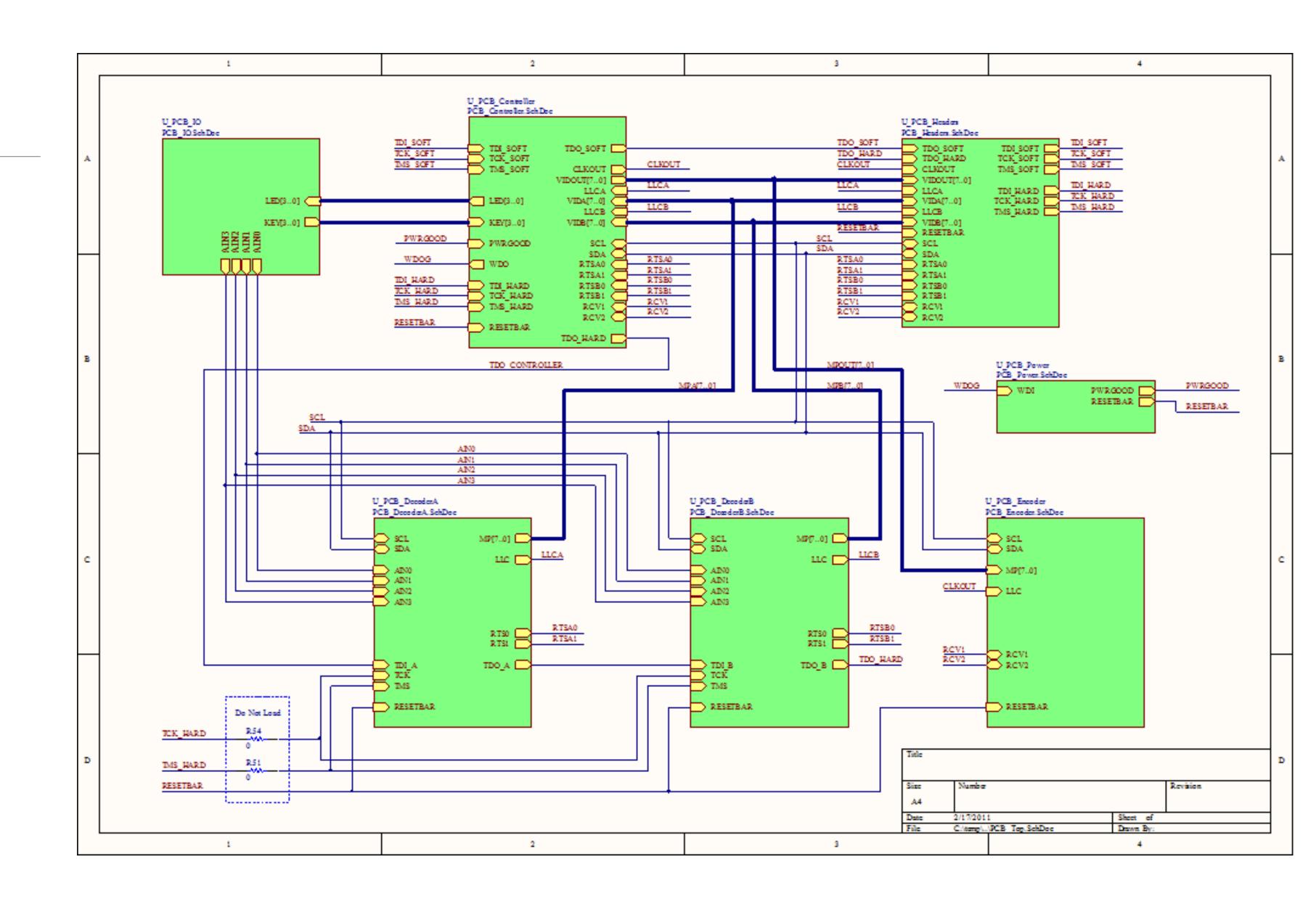

## 多页层级设计

- 每个EDA软件的使用方法不同

- 确保页面之间的连接规范、对应

- 可以通过功能进行划分:

- ①模拟

- ②数字

- ③电源

- 4时钟

- 通过ERC进行检查

- 通过打印进行检查

www.mouser.cn

# 规范、易读、风格

## 万无一失 - ERC及基于netlist的检查

·ERC反复检查,不放过任何一个Warning,修正空悬管教以及连接错误的连线

·netlist联系原理图和PCB之间的桥梁,是抽象的元器件之间的连接关系 - 元器件 的封装、个数、引脚之间的连接关系

·打印对比 - netlist同原理图中的每一个连接——检查

## 关于贸泽电子 - www.mouser.cn

- · 与非网/摩尔吧多年合作伙伴

- ・全球领先的电子元器件授权分销商

- · 700家原厂/500万现货库存

- · 小批量采购, 170元免邮费

- ・1-2周交货