实验目的

- (1)熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法;

- (2)通过实验理解基本逻辑门电路;

- (3)学习用Verilog HDL数据流级描述基本门电路。

实验任务

设计一个4变量多数表决器,在4个输入中A代表2,B、C、D分别代表1,当输入数值大于或等于3时,输出为高电平,否则,输出为低电平。

实验原理

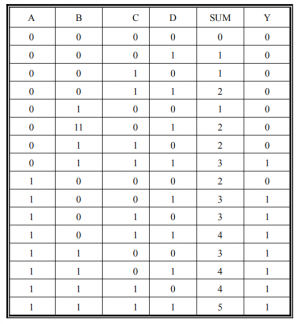

4变量多数表决器,可以理解为四人投票,将所投的票数加起来,若大于等于3票,则投票通过。注意:每个人的票数不同。由此可得到如下表1-5所示的真值表。定义四个输入A,B,C,D和一个输出Y。则他们的关系写成逻辑表达式经化简可得到:

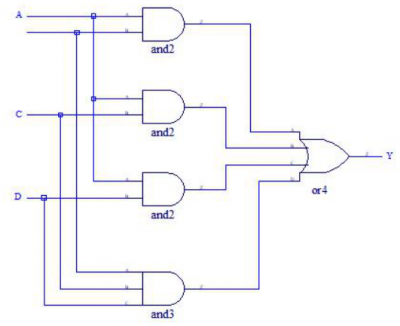

Y=AB+AD+AC+BCD

逻辑电路

Verilog HDL建模描述

4变量多数表决器程序清单voter4.v

module voter4 ( input wire a, //定义输入的低位进位及两个加数a、b、c、d input wire b, input wire c, input wire d, output wire led //定义显示输出结果的led ); assign led = (a&b)|(a&c)|(a&d)|(b&c&d); //根据逻辑表达式赋值 endmodule

实验步骤

- 打开Lattice Diamond,建立工程。

- 新建Verilog HDL设计文件,并键入设计代码。

- 综合并分配管脚,将输入信号a、b、c、d分配至拨码开关,将输出信号led分配至板卡上的LED。a/M7,b/M8,c/M9,,d/M10,led/N13

- 构建并输出编程文件,烧写至FPGA的Flash之中。

- 按下对应按键/拨动拨码开关,观察输出结果。