准备工作

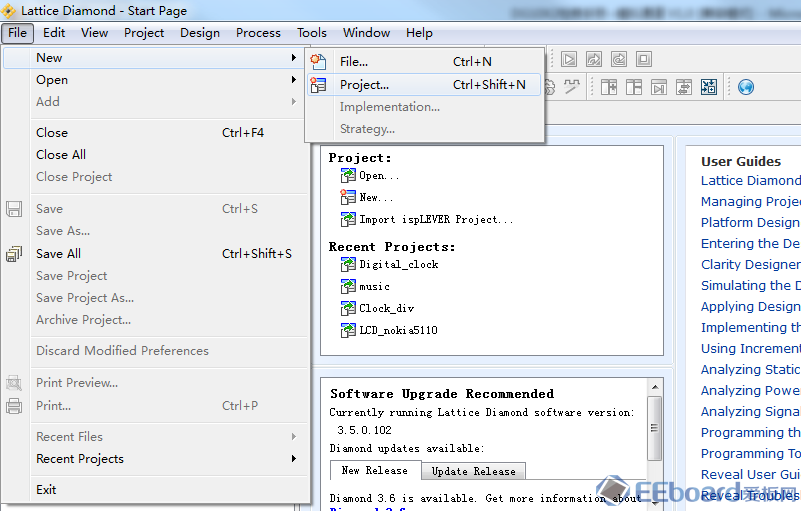

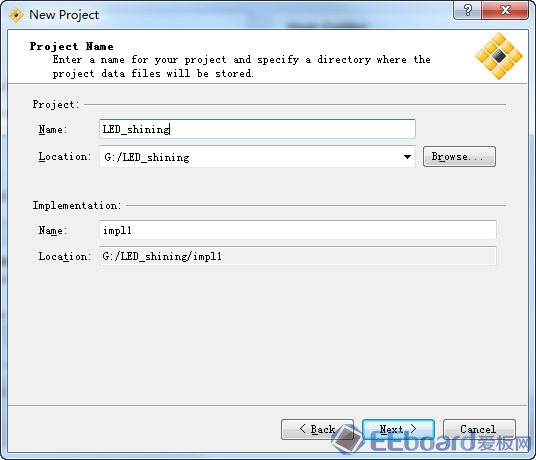

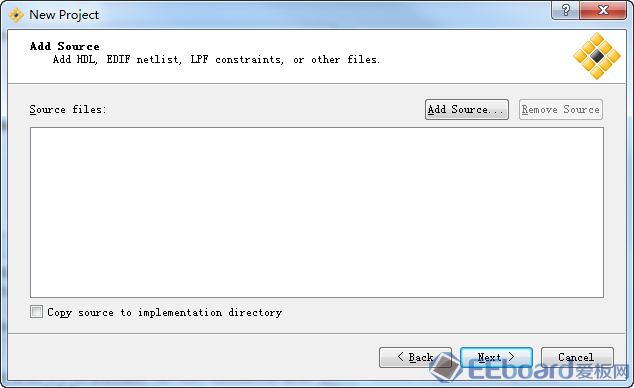

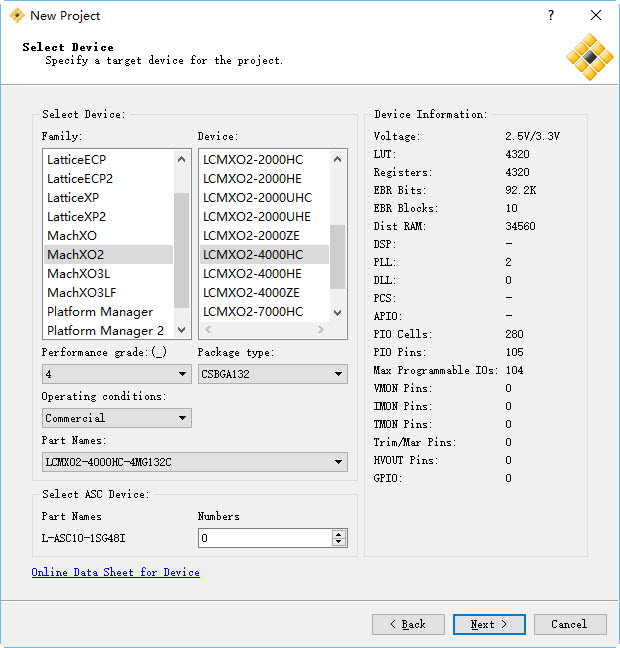

1 运行第一个例程

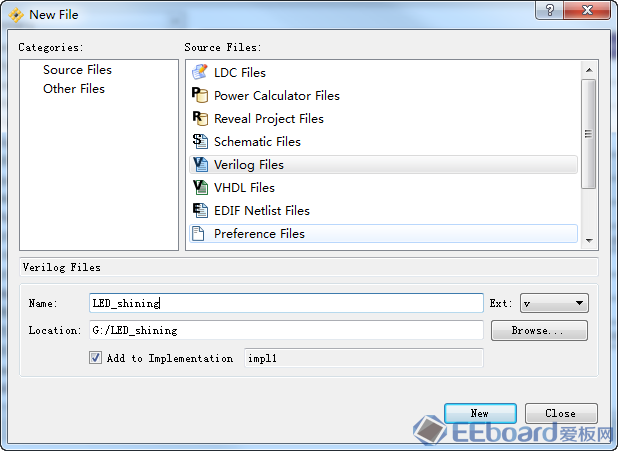

下面我们可以开始可编程逻辑的开发,我们以控制LED交替闪烁为例,完成自己的第一个程序:

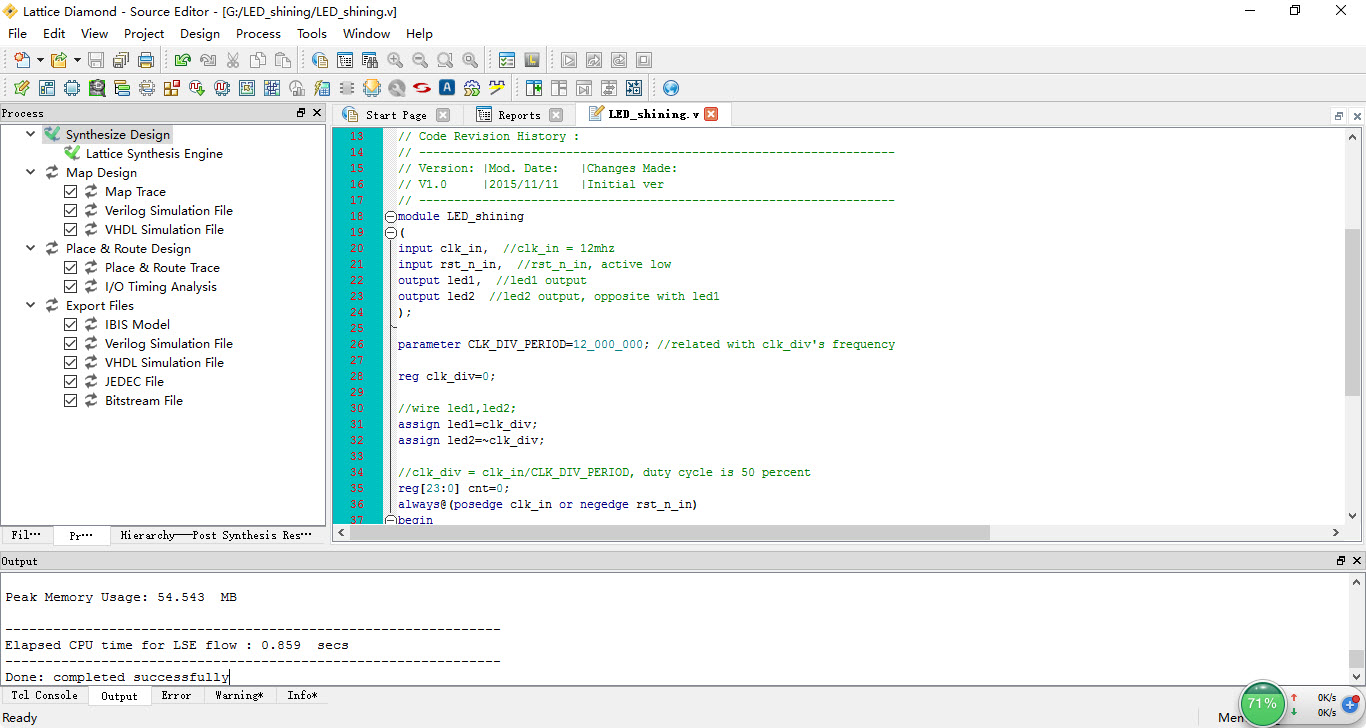

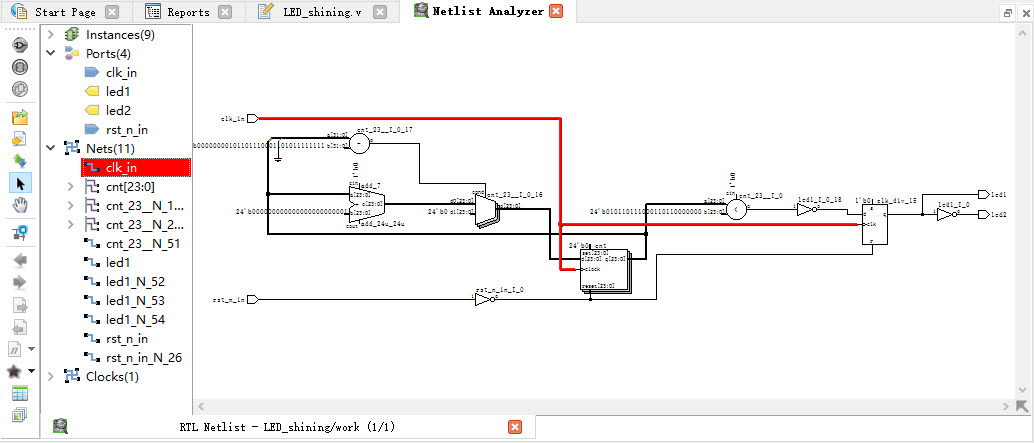

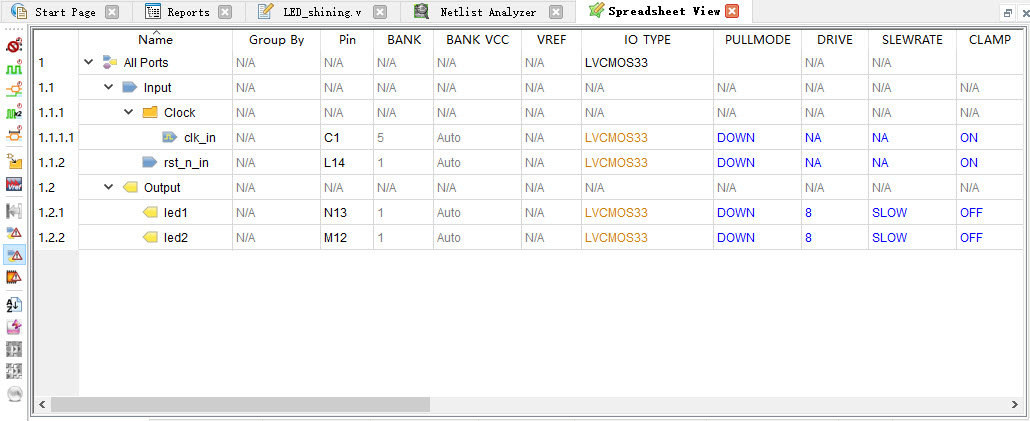

- 程序源码已经准备好,如下,将代码复制到设计文件LED_shining.v中,并保存。

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // Module: LED_shining // // Author: Step // // Description: LED_shining // // Web: www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2015/11/11 |Initial ver // -------------------------------------------------------------------- module LED_shining ( input clk_in, //输入系统12MHz时钟 input rst_n_in, //输入复位信号 output led1, //输出led1 output led2 //输出led2,与led1取反 ); parameter CLK_DIV_PERIOD=12_000_000; //分频常数定义 reg clk_div=0; //定义reg型变量,用作分频后时钟输出 //wire led1,led2; //wire型变量定义,可以省略,verilog里默认是wire型 assign led1=clk_div; //持续赋值语句,将分频后时钟赋给led1,产生闪烁效果 assign led2=~clk_div; //取反赋值给led2,与led1形成交替闪烁 //偶数分频电路 clk_div = clk_in/CLK_DIV_PERIOD, 占空比50%,CLK_DIV_PERIOD必须为偶数 reg[23:0] cnt=0; //分频用的计数器,2**cnt-1>CLK_DIV_PERIOD,计数器最大值要大于分频常数 always@(posedge clk_in or negedge rst_n_in) begin if(!rst_n_in) begin cnt<=0; clk_div<=0; end else begin if(cnt==(CLK_DIV_PERIOD-1)) cnt<=0; else cnt<=cnt+1'b1; if(cnt<(CLK_DIV_PERIOD>>1)) clk_div<=0; else clk_div<=1; end end endmodule

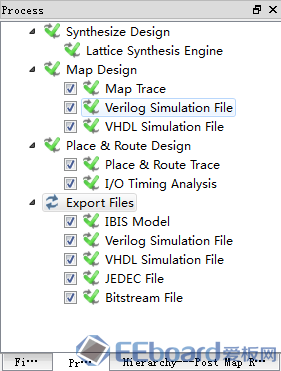

到这里完成了第一个程序流文件的生成,下面可以下载到FPGA中。

2 工程仿真

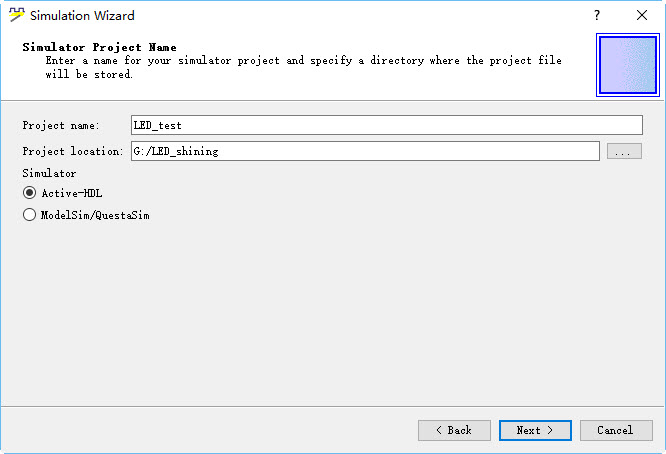

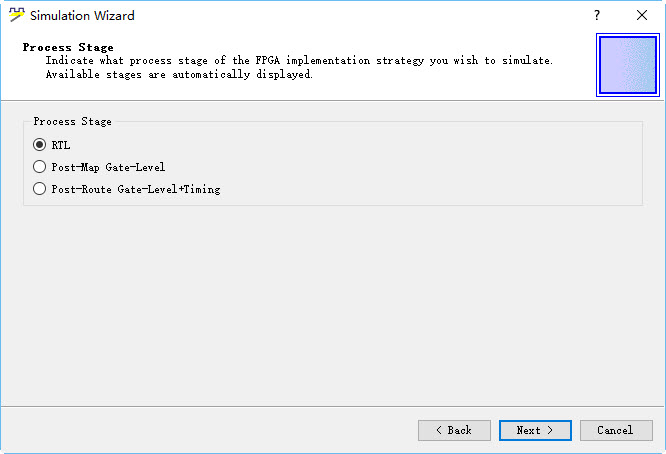

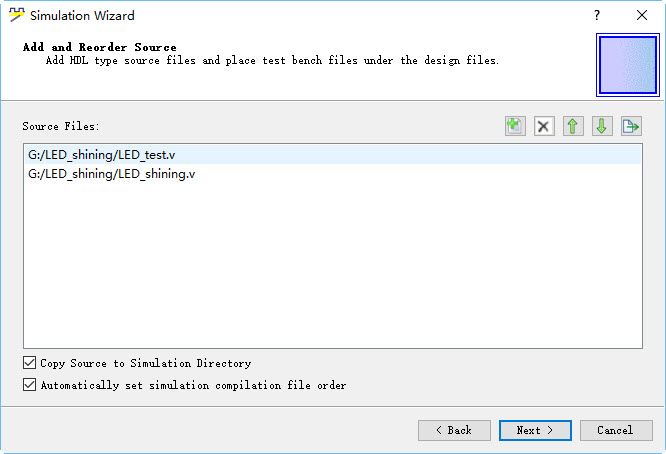

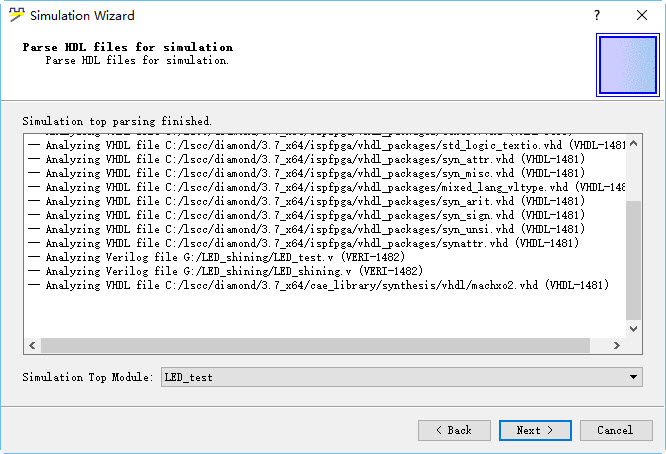

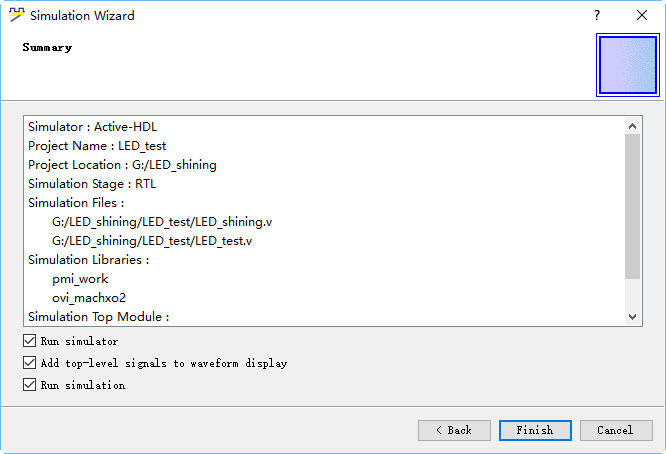

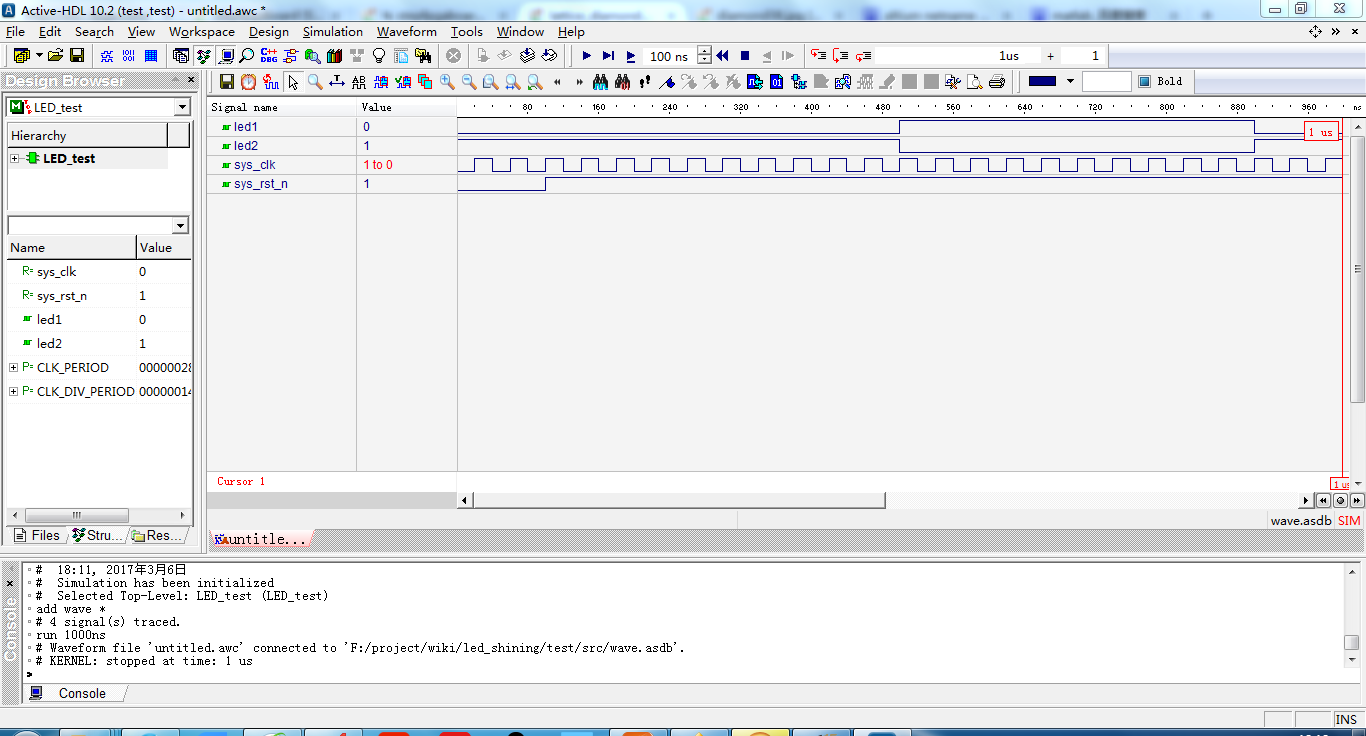

上面我们走了整个工程开发的过程,例程较为简单,对于复杂的工程开发需要预仿真和后仿真等,保证最终的程序设计逻辑和时序符合我们的设计要求。 仿真软件很多,这里我们使用软件自带的Active-HDL软件进行功能仿真:

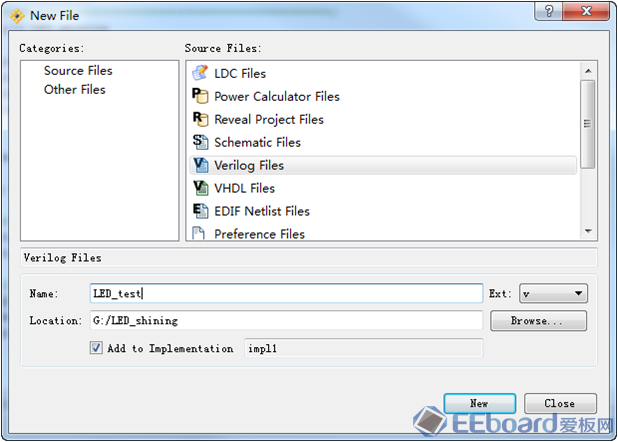

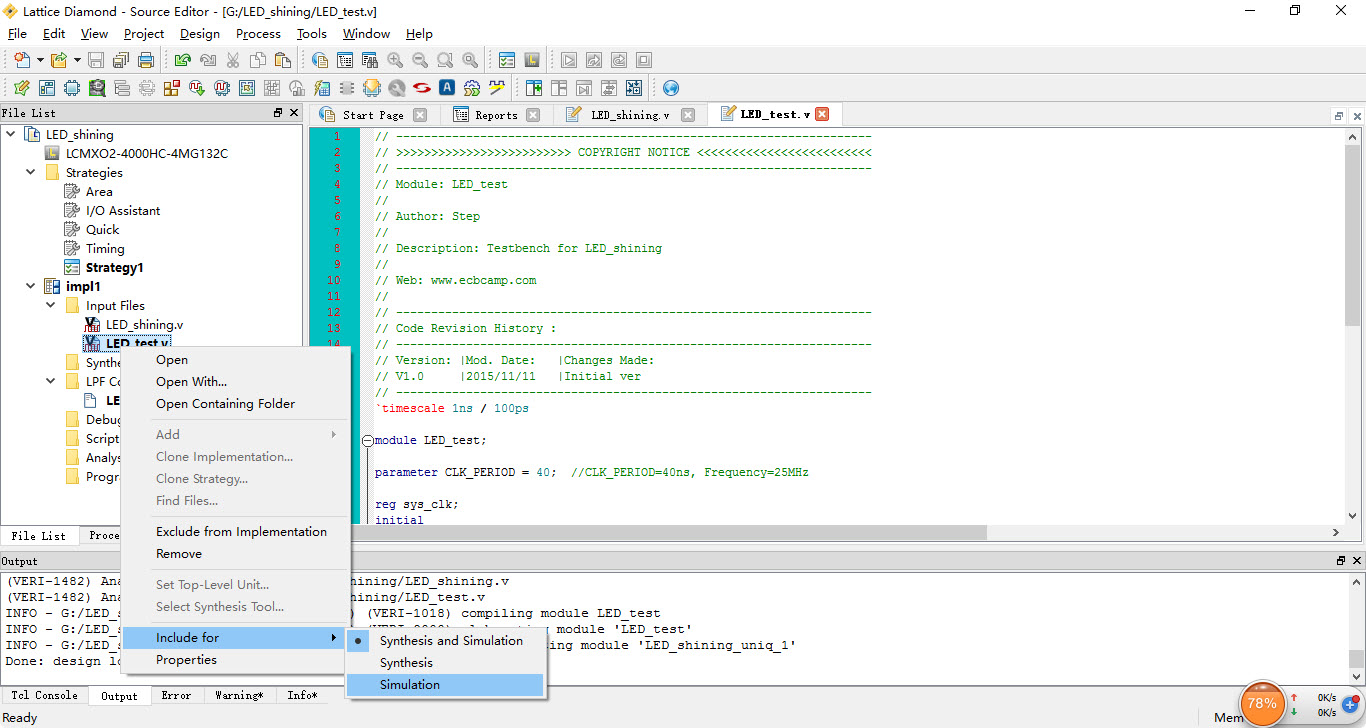

- 测试源码如下,复制到LEDtest.v文件并保存。为了方便仿真,我们在LEDtest.v调用LEDshining模块时将CLKDIV_PERIOD重新赋值为20:

// -------------------------------------------------------------------- // >>>>>>>>>>>>>>>>>>>>>>>>> COPYRIGHT NOTICE <<<<<<<<<<<<<<<<<<<<<<<<< // -------------------------------------------------------------------- // Module: LED_test // // Author: Step // // Description: Testbench for LED_shining // // Web: www.stepfpga.com // // -------------------------------------------------------------------- // Code Revision History : // -------------------------------------------------------------------- // Version: |Mod. Date: |Changes Made: // V1.0 |2015/11/11 |Initial ver // -------------------------------------------------------------------- `timescale 1ns / 100ps module LED_test; parameter CLK_PERIOD = 40; parameter CLK_DIV_PERIOD=20; reg sys_clk; initial sys_clk = 1'b0; always sys_clk = #(CLK_PERIOD/2) ~sys_clk; //产生周期为40ns的时钟激励,频率25MHz reg sys_rst_n; //产生一个初始100ns低电平然后变高电平的复位信号激励 initial begin sys_rst_n = 1'b0; #100; sys_rst_n = 1'b1; end wire led1,led2; //module例化 LED_shining # (.CLK_DIV_PERIOD(CLK_DIV_PERIOD)) LED_shining_uut ( .clk_in(sys_clk), //传递时钟 .rst_n_in(sys_rst_n), //传递复位信号 .led1(led1), //传递输出led1 .led2(led2) //传递输出led2 ); endmodule

3 下载程序到FPGA

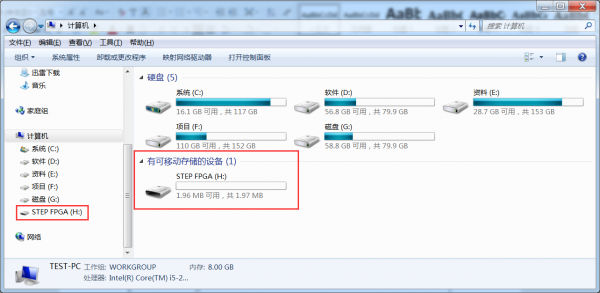

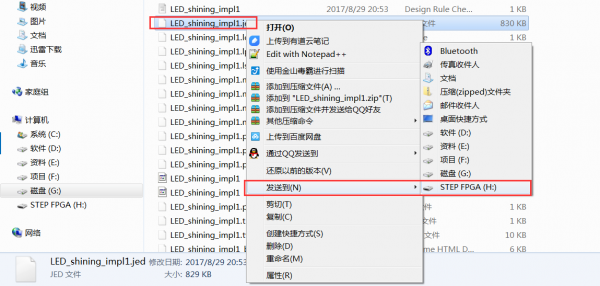

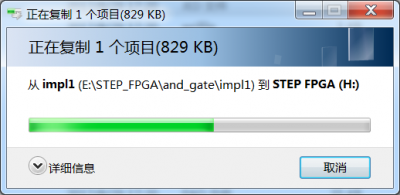

专用的编程芯片已经集成到小脚丫开发板上,因此只需要一根Micro USB线和电脑相连,就可以完成供电和编程的功能,该MXO2-C版本在进行程序下载时与Lattice MXO2其它版本不同,将板卡与PC链接后,将被识别成“大容量存储设备”,你只需要将程序生成的.JED文件复制进入板卡之中,即可完成下载。 将编译完成的程序下载到开发板:

- 观察FPGA开发板的LED交替闪烁,成功了。

4 STEP MXO2入门教程

到这里我们了解了用Diamond软件进行开发的完整流程。 接下来我们开始STEP-MXO2入门教程一步一步进入可编程逻辑设计。