实验1.3 卡诺图变换

1.实验目的

- 熟悉和掌握FPGA开发流程和Lattice Diamond软件使用方法 * 通过实验理解基本门电路

- 掌握用Verilog HDL描述逻辑电路 ===== 2.实验任务 ===== 了解并掌握4变量卡诺图的化简方法

3.实验原理

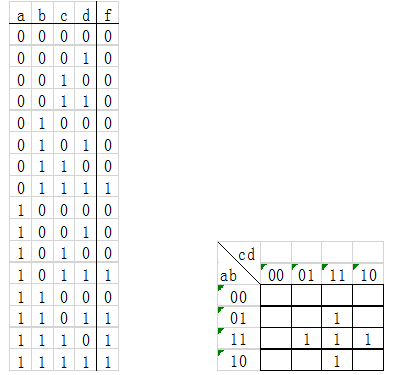

卡诺图:在真值表的输出列种,每个“1”输出都代表一个相应的乘积项。所以, 如果“1”输出项多余8个,我们就得设法减少乘积项数,使得逻辑函数在器件上得以实现。“卡诺图”是种完成函数化简的非常简单实用的图形化方法,特别是对于含有2、3和4个变量的布尔函数,对于多于4个变量的布尔函数化简,卡诺图的化简方法就开始变得繁琐。 卡诺图画圈原则:

- 对相邻的值为“1”的小方块画包围圈,画若干包围圈;

- 每个包围圈中必须含有2n个小方块(n=0,1,2,……)

- 小方块可重复被包围,但每个包围圈中必须含有其他包围圈没有的新小方块

- 不能漏掉任何值为1的小方块

- 包围圈所含的小方块数目要尽可能多,包围圈数目要尽可能少

- 画包围圈的顺序由大→小 * 普通列表项目

- 将每个包围圈中的最小项合并成一项→乘积项;

- 留下相同的因子,消去不同的因子

- 对各个包围圈合并成的乘积项求逻辑和;

多输入电路的真值表与对应的卡诺图如下图所示:

4.Verilog HDL建模描述

LED默认状态为点亮,若其他LED不加控制,则会常亮,影响显示状态。以下代码目的为改变其默认参数,使之常灭:

assign empty=8'b1111_1111;

由于LED为低电平触发,若直接将z连接在LED管脚上,LED亮将代表输入为低电平,LED灭代表输入为高电平。所以有如下代码,使之更符合我们的思维习惯:

assign led=~z;

本实验代码编写比较简单,只需一个f的组合逻辑即可,重点在卡诺图简化:

assign f=b&c&d|a&c&d|a&b&d|a&b&c;

五、 实验步骤

1.新建工程

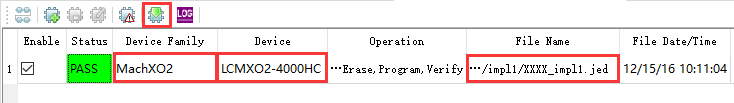

双击![]() 打开Lattice Diamond软件,点击File—New—Project新建工程,输入工程名称,指定工程保存目录,单击Next,选择设备如下:

打开Lattice Diamond软件,点击File—New—Project新建工程,输入工程名称,指定工程保存目录,单击Next,选择设备如下:

- Family选择MachXO2,

- Device选择LCMXO2-4000HC,

- Performance grade选择4,

- Package type选择CSBGA132,

- Operating conditions选择Commercial,

- Part Names为LCMXO2-4000HC-4MG132C。

- 选择综合工具Lattice LSE,完成。

2. 输入Verilog文件

点击File—New—File新建文件,类型选择Verilog Files,输入文件名称,选择保存路径,输入实验中的源代码后保存,编辑器会自动检查有无编辑错误,在下面的Output一栏会输出检查结果,如果有错误更正后重新保存直到没有报错为止。

3. 输入仿真文件

按照步骤(2)新建一个Verilog仿真文件,输入实验例程中仿真文件的代码后保存。在软件File List一栏中,右键单击“仿真文件”—Include for—Simulation,将文件设置为仿真文件(设置完成后文件图标的V会消失)。

4. 功能仿真

点击Tools选择Simulation Wizard或点击图标,按照仿真向导指示新建仿真工程,

- 输入工程名称,选择工程目录,选择Simulator为Active-HDL,

- Process Stage选择RTL,

- Add and Reorder Source:确认参与仿真的文件列表,Next

- Parse HDL files for simulation:软件会编译仿真文件,若报错需修改后重新仿真

- Summary:确认仿真工程信息,勾选Run simulator、Add top-level signals to waveform display和Run simulation,然后Finish

仿真软件会自动启动、运行仿真并显示仿真结果。查看仿真结果是否符合预期功能,如果不符合电路功能,则修改Verilog代码保存后,在Active-HDL中选择Design—Compile All 重新编译文件,编译通过后,在Simulation中重新开始仿真。

5. 综合

在Lattice Diamond软件的Process一栏,双击第一项Synthesize Design进行综合(确保仿真文件设置为simulation后不参与综合),综合结果会在下面的Output一栏中给出,如果有错误则修改Verilog文件后重新综合直至综合成功为止。

6. 分配管脚

7. 布局布线

双击Process一栏的Map Design和Place & Route Design完成FPGA内部的布局布线。

8. 生成配置文件

勾选并双击JEDEC File生成可下载的jed文件。