STEP小脚丫FPGA学习平台是苏州思得普信息科技公司专门针对FPGA初学者(尤其是学习数字电路的在校同学)打造的一系列性价比最高、学习门槛最低的学习模块系列。板上选用的芯片兼具了FPGA和CPLD的优点,瞬时上电启动,无需外部重新配置FPGA,是学习数字逻辑绝佳的选择。系列中所有板子的大小兼容标准的DIP40封装,尺寸只有52mm x 18mm,非常便于携带,而且能够直接插在面包板上或以模块的方式放置在其它电路板上以即插即用的方式,大大简化系统的设计。

最新推出的STEP-MXO2-LPC在易用性方面做了大幅升级:

- 使用了USB Type C接口提供板上+5V供电、FPGA的配置,并新增了UART通信的功能,因此无需再通过其它端口与PC进行数据通信

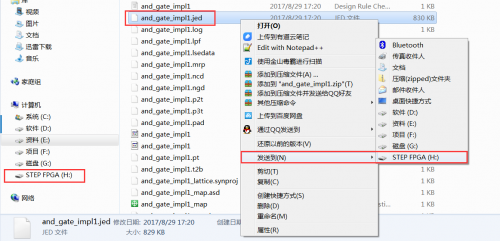

- 支持U盘模式(连接到上位机的USB端口,上位机自动弹出StepFPGA的U盘盘符)的下载,任何操作系统的电脑 - Windows、Mac OS以及Linux(包括树莓派)都可以在不安装任何驱动程序的情况下,直接将生成的jed配置文件发送到StepFPGA盘中即可完成编程

- 为配合这款小脚丫FPGA的使用,我们特别升级了Web IDE系统,用户不必再下载安装Diamond软件,即可在任何一款电脑上通过浏览器进行FPGA的编程和编译。图形化的界面使得操作非常直观、便捷

习惯于使用Diamond编程FPGA的用户仍然可以使用Diamond软件进行编译、生成jed文件,只是最终的下载只需要将要下载的文件发送到StepFPGA盘中即可。

Web IDE的代码编程界面

Web IDE的管脚定义界面

小脚丫STEP-MXO2-LPC

硬件规范

- 核心器件:Lattice LCMXO2-4000HC-4MG132

- 板载资源:

- 两位7段数码管;

- 两个RGB三色LED;

- 8路用户LED;

- 4路拨码开关;

- 4路按键;

- 36个用户可扩展I/O(其中包括一路SPI硬核接口和一路I2C硬核接口)

- 支持的开发工具思德普开发的Web IDE以及Lattice官方提供的Diamond

- 支持MICO32/8软核处理器以及RISC-V软核

- 板上集成FPGA编程器,采用U盘的模式

- 一路USB Type C接口,可用于给核心板供电、给FPGA下载JED文件以及同上位机通过UART通信

- 板卡尺寸52mm x 18mm

引脚定义

STEP-MXO2-LPC包装

其中包含:

- 小脚丫STEP MXO2-LPC板卡

- 包装盒

- 产品说明书

上电测试

STEP-MXO2-LPC开发板通过USB端口供电,采用了Type接口。开发板出厂内置测试程序,上电后:

- 数码管:循环显示0~7之间的数字

- 流水灯:依次闪烁实现流水效果

- 三色灯:两个三色灯逐次显示红,绿,蓝,白颜色

- 拨码开关:控制数码管、流水灯及三色灯闪烁的速度,

- 四位拨码开关全部拨至下端,闪烁速度最快(0.5s左右)

- 四位拨码开关全部拨至上端,闪烁速度最慢(2s左右)

- 四位拨码开关处于其他状态时,闪烁速度适中(1s左右)

- 按键开关:控制数码管、流水灯及三色灯闪烁的方向及显示的亮度,

- K1:控制数码管、流水灯及三色灯闪烁的方向或顺序

- K2:控制所有显示的亮度,分六级亮度等级,按K2亮度增强

- K3:控制所有显示的亮度,分六级亮度等级,按K3亮度减弱

- K4:软件复位

使用说明:

STEP-MXO2-LPC的编程芯片已经集成到小脚丫开发板上,因此只需要一根USB Type C线和电脑相连,就可以完成供电和编程的功能,无需安装驱动。

开发过程可以使用思德普的Web IDE或Lattice的Diamond软件,该软件的安装和操作简单易上手,操作过程与其他厂商的FPGA设计工具大同小异。

STEP-MXO2-LPC板在进行程序下载时与STEP MXO2-V2版本不同,将该板卡与PC连接后,将被识别成“大容量存储设备”,盘符为StepFPGA,你只需要将程序生成的.JED文件复制进入板卡之中,即可完成下载。

编程FPGA的方式有两种:

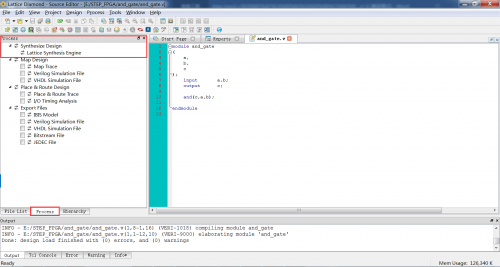

第一种方法: 采用Lattice的Diamond软件(只能下载安装在Windows电脑上使用)

操作步骤如下:

1.安装Lattice Diamond软件

2.新建工程,输入设计文件,综合、管脚约束、布局布线并输出JED文件;

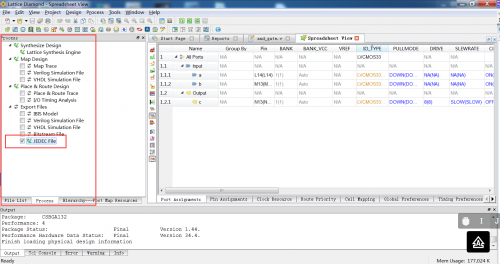

设计输入 综合

管脚分配 编译生成JED文件

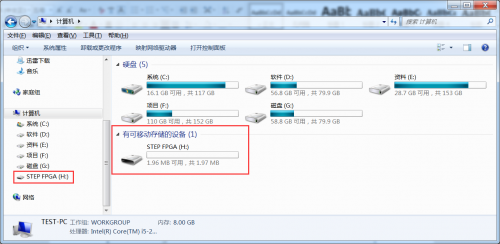

3.将板卡连接至PC,在电脑资源管理器中会出现一个名为STEP FPGA的U盘;

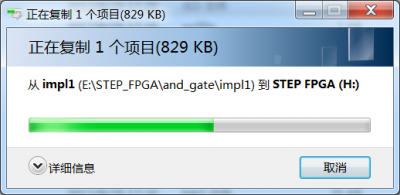

5.将JED文件复制进入名为STEP FPGA的大容量存储设备中;

6.下载完成。

第二种方法:采用思得普开发的网页版编译工具,参见页面:快速上手小脚丫线上设计工具:

在小脚丫网站www.stepfpga.com注册账号后就可以体验使用线上设计工具,基于浏览器端的开发环境,无需下载FPGA设计工具到本地电脑。使用方便简单。

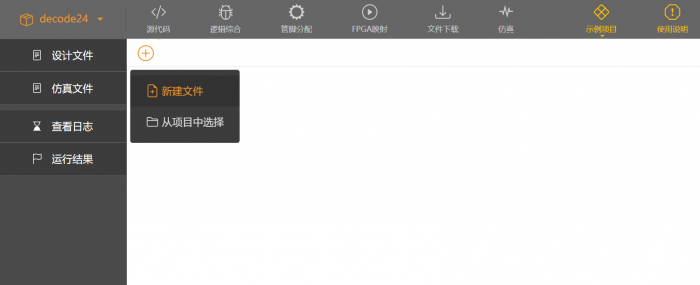

1.新建项目

点击新建项目会进入创建新项目界面,左侧是项目文件组成,可以在这里查看项目所需文件以及软件生成的日志等等。在上方是FPGA设计的流程图标,可以按顺序创建源文件、综合、分配管脚、产生编译文件、仿真(还在完善)以及下载工程和编译文件。

填写项目的一些基本信息,比如名称,选择的小脚丫板卡,标签信息,项目描述等等。

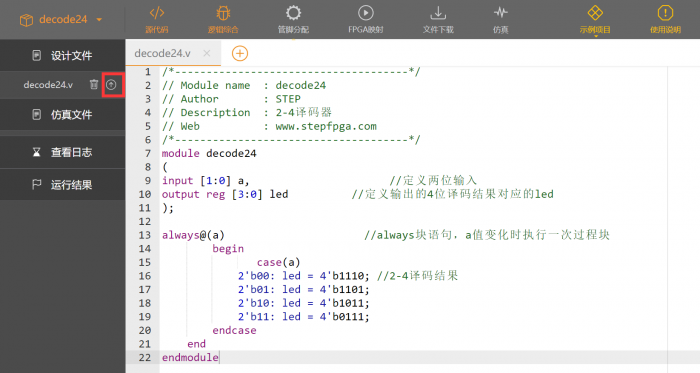

2.创建源文件

提交创建项目后进入编辑界面,点击界面上的+号可以新建源文件(也可以从其他项目拷贝文件)。

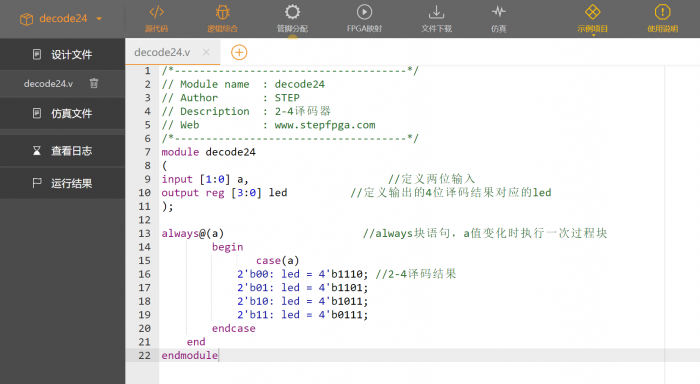

3.设置顶层文件

源文件创建完成后需要设置顶层文件,点击左侧栏文件名称后的箭头图标(如下图)

设置完成后文件名称后的箭头图标消失,说明该文件目前是顶层文件。如果项目里包含多个源文件也是同样设置。

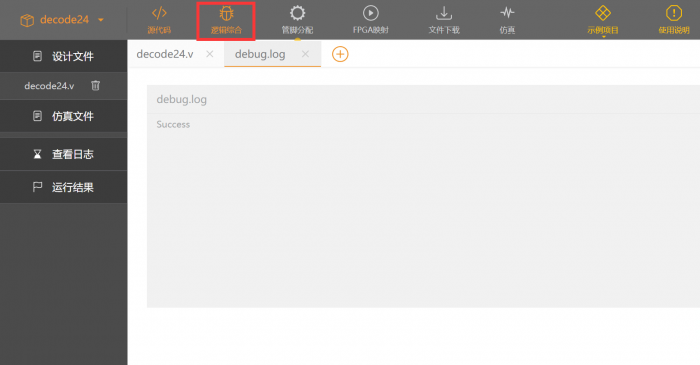

4.逻辑综合

设置好顶层文件后点击逻辑综合,开始进行综合。

综合完成后显示日志,如果有错误的话会显示报错信息。

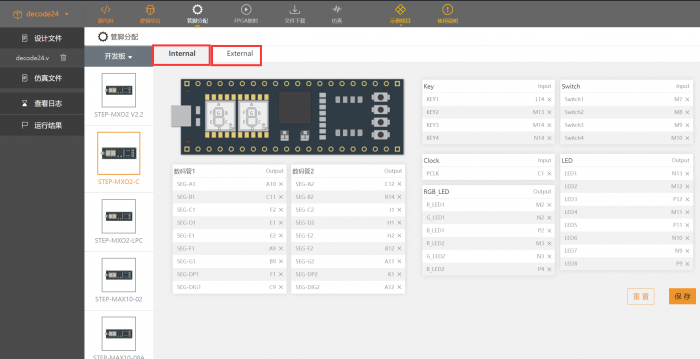

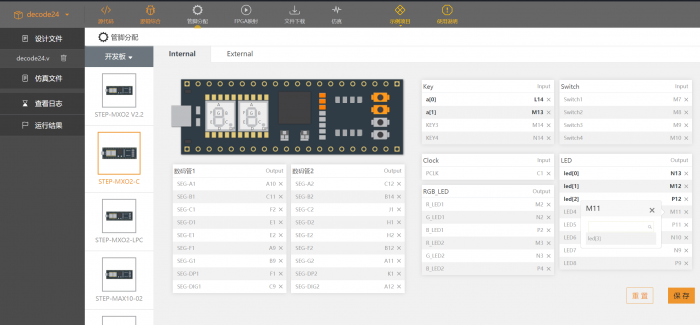

5.管脚分配

综合通过后进行管脚分配。小脚丫板卡可配置的管脚分为板上部分(internal)和扩展部分(external)。

分配管脚过程很简单,点击想要分配的外设,会自动弹出所有输入输出信号,选择确定就可以。所有信号分配完毕点击保存按键,如果分配错误可以选择重置。

板上外设被分配使用后会以黄色来标记。

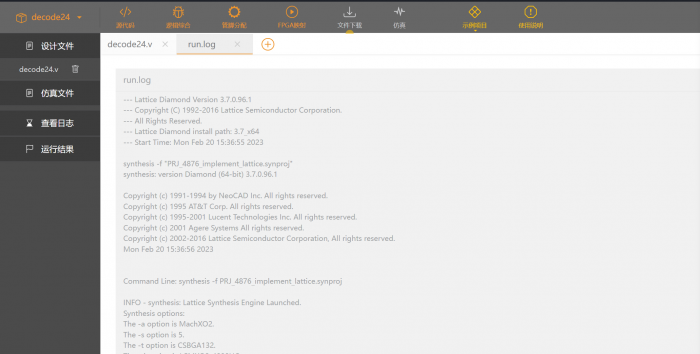

6.映射生成流文件

分配完成后点击映射来产生FPGA的变成文件,完成后生成日志,如果有错误会显示报错信息。

7.下载文件

可以在下载界面下载打包整个工程,也可以只下载需要的FPGA编程流文件(Lattice小脚丫产生jed文件,Intel小脚丫产生pof和sof文件)

文件下载 - 可以将完整的项目下载到本地电脑,也可以将生成的JED文件下载到U本地电脑再复制到“U盘”中

文档资料