1. 基本功能特性

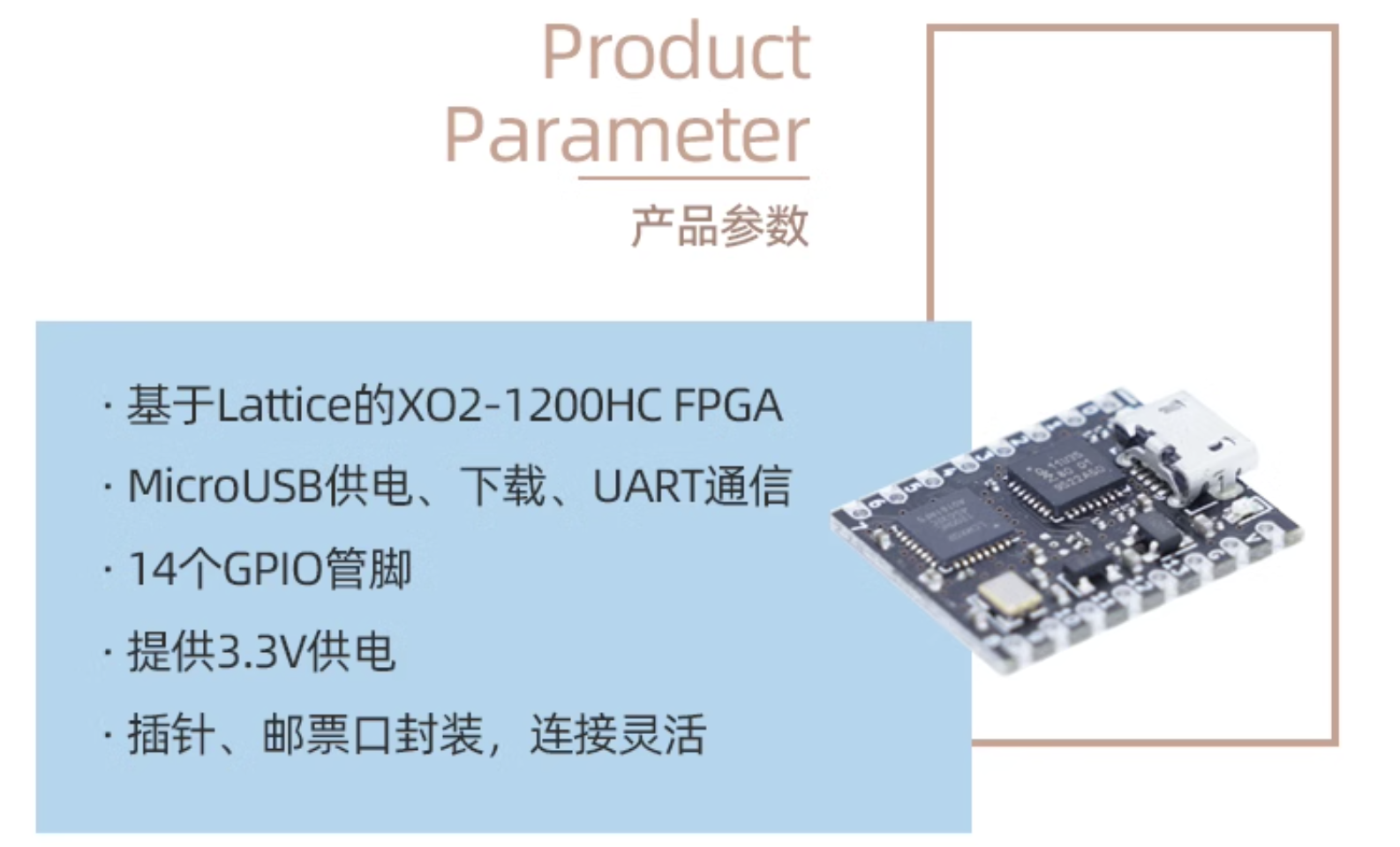

- 基于Lattice的XO2-1200HC FPGA

- 1280个LUTs

- 64Kbits 嵌入块RAM

- 一个PLL

- 支持DDR/DDR2/PDDR

- 内置可以双启动的Flash用于配置FPGA

- 内部有2个I2C、1个SPI和一个定时器硬核

- 3.3V供电

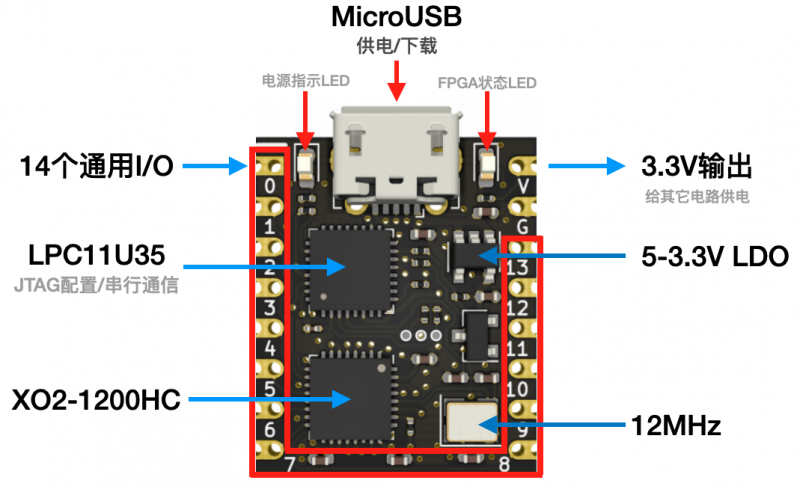

- 通过MicroUSB供电,支持DAPLink方式对FPGA进行配置以及UART通信

- 12MHz外部时钟,FPGA可以通过内部PLL进行高速工作(测试用400MHz的时钟产生DDS),选用12MHz时钟的原因是为了能够和LPC11U35共用以节省成本;

- 14个GPIO管脚,其中第14个管脚和板上的心跳LED等共用;

- 板上2个LED:

- 一个3.3V的电源指示灯 - PWR

- 一个FPGA逻辑状态指示灯 - HB,用于验证FPGA的逻辑

- 板上5V-3.3V LDO,可以通过PIN 16对外供电,最大150mA

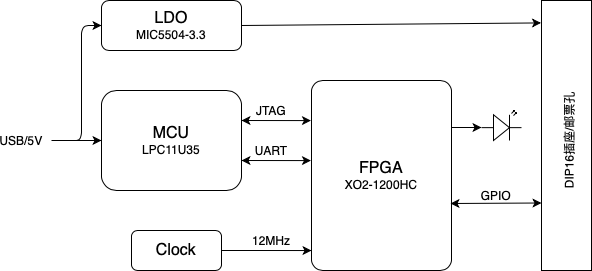

基于Lattice XO2-1200HC的FPGA核心模块构成框图

基于Lattice XO2-1200HC FPGA、板载下载器/串口通信的FPGA模块连接框图

板卡尺寸示意图

16Pin 模块管脚 | FPGA芯片XO2-1200HC管脚 | 16Pin 模块管脚 | FPGA芯片 XO2-1200HC管脚 | 功能 |

1 - DIO_0 | 8 | 16 - 3.3V |

| 对外连接 |

2 - DIO_1 | 9 | 15 - GND |

| 对外连接 |

3 - DIO_2 | 10 | 14 - DIO_13/LED | 27 | 对外连接/板上功能D2 |

4 - DIO_3 | 11 | 13 - DIO_12 | 20 | 对外连接 |

5 - DIO_4 | 12 | 12 - DIO_11 | 21 | 对外连接 |

6 - DIO_5 | 13 | 11 - DIO1_0 | 23 | 对外连接 |

7 - DIO_6 | 14 | 10 - DIO_9 | 25 | 对外连接 |

8 - DIO_7 | 16 | 9 - DIO_8 | 17 | 对外连接 |

UART - TXD | 4 | UART - RXD | 5 | 板上功能 |

Clock (12MHz) | 28 |

|

| 板上功能 |

2. 关键器件的技术资料:

3 编译环境

这块核心模块使用的是Lattice的XO2-1200HC的FPGA,QFN32封装,因此使用的FPGA编译工具为Diamond(点击可以查看详细的下载、使用方法),针对这个器件Diamond可以免费使用其全功能,下载了Diamond以后,需要申请License - 提交自己电脑的Mac地址,会通过邮件收到license.txt的文件,复制到相应的目录中即可使用。

注意,在使用Diamond的过程中要正确选择器件及其封装,并在管脚分配的时候正确映射相应的管脚,最后生成jed的可配置文件。

4 FPGA的编程下载过程介绍

不同于Lattice官方使用的FPGA开发板,需要通过Diamond软件中的按钮进行编程操作,我们这个核心板使用了DAPLink的操作方式,使得编程和UART通信更容易。

此核心模块是通过MicroUSB连接器同PC进行连接,确保你用的USB线是“数据线“,而不是只能充电的线,将该模块同PC连接上,你将看到:

- 模块上的电源指示灯常亮、右侧的心跳灯以每秒一次的节奏在闪,表明板卡中预装的测试程序正常运行;

- 在电脑端你会看到一个STEPLINK的盘符,无论你用的是Windows的系统还是Mac OS、Linux,都会出现这个盘符,双击进入STEPLINK的盘,你会看到一个txt的说明文件和一个HTML网页文件,点击txt的说明文件,了解这个板卡的信息;点击HTML网页文件,可以直接跳转到该模块在电子森林上的资源页面;

- 当你要用jed文件重新编程该模块的时候,您只需将要配置的jed文件拖到该STEPLINK的盘中,或者在FPGA的项目页面中,找到你要配置的jed文件,鼠标悬浮点击右键,发送到STEPLINK盘即可