此平台为配合小脚丫FPGA核心模块的综合技能训练平台,在2020年为全国上千在校学生所采用,通过2周在线直播授课的方式,完成该平台上所有功能模块的逻辑编程。

该平台可以支持Lattice XO2版本和Intel/Altera MAX10M02/08版本的小脚丫核心模块,关于这两种模块的使用以及详细的技术文档请参见:

- STEP-MXO2小脚丫:基于Lattice XO2-4000HC的FPGA学习模块,板载编程器,有基于FT232HL下载器(Diamond软件中直接加载使用)和基于STM32F072下载器(U盘模式直接复制、发送JED文件)的两个版本

- STEP-MAX10:基于Altera MAX10的FPGA学习板,带板载编程器

该平台的主要构成:

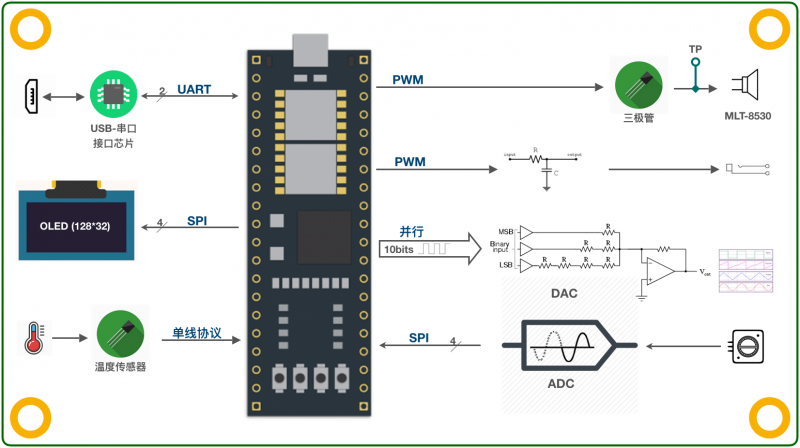

1. 任意波形/信号发生器的功能:

- 能够通过R-2R阶梯网络生成0-2MHz的任意波形(目前是采用GBW=3MHz的TLV271作为输出级运算放大器,若更换更高带宽的运算放大器,搭配FPGA内部的PLL能够生成更高频率的模拟信号),包括正弦波、三角波、锯齿波、方波等,由于单电源供电,输出信号的幅度设定为3Vpp,输出信号的波形、频率以及幅度皆可调节;

- 同时可以通过PWM的方式用一根数据线搭配R、C构成的低通滤波器生成0-20KHz的任意波形,可同上述用R-2R构成的高速信号发生器进行对比;

通过该功能,能够掌握DDS生成任意波形/信号的原理、使用方法、以及DAC的工作原理、构成方式、信号的频谱构成等;

2. ADC数据采集的功能:

- 板上有一颗SPI接口的串行ADC,可以采集电位计上的电压,通过旋转电位计,可以观察采集到的电压值的变化;

- 也可以将1中的DDS信号发生器产生的波形送到ADC的输入端,构成一个环路,即便在家没有任何测试仪器的情况下也可以通过本地产生的波形信号进行电路和逻辑的调试;

- 串行ADC的采样率最高为280ksps,可以对频率为20KHz以内的信号(音频信号的范围)进行采样并显示在OLED屏上;

- 延伸的功能 - 对信号进行频谱分析,通过FFT变换得到被采集信号的基频及多个高次谐波的分量信息;

通过这个功能,可以掌握ADC的工作原理以及在数据采集中的应用方式、SPI总线的使用、模拟信号带宽、ADC采样率、SPI总线速率等之间的时序关系;

3. 传感器信息输入

- 能够通过单总线采集温度传感器(使用经典的18B20器件)的数据并显示出来;

通过这个功能,可以学会单总线的逻辑实现以及传感器数据的处理,对于理解物联网产品比较有帮助;

4. OLED图形化信息显示

- 板上采用了一块128*32分辨率的OLED作为信息显示终端,可以显示温度传感器的温度值、通过ADC采集到的电位计的电压值、DDS信号发生器生成的波形以及必要的菜单信息等;

通过这个功能可以掌握SPI显示屏的使用、SPI总线逻辑以及屏上信息的文本、图形化显示等。越来越多的电子产品、创意设计都采用图形化的OLED显示屏成为信息展示的终端,无论用MCU还是FPGA的系统,在电赛中的很多项目中也会用到信息的图形化显示。

5. 蜂鸣器输出

- 板上有一个经三极管驱动的蜂鸣器,可以通过PWM来实现声音的输出,比如播放音乐、声音报警等;

这个功能可以给学习者更有趣的方式了解PWM的应用

6. UART通信

- 板载USB-UART芯片CH340C,能够实现FPGA和上位机PC的通信;

通过这个功能,可以体会异步串行通信UART的工作原理、逻辑实现、优势、应用等,打通了同PC的连接,延伸了板卡的功能,能够使用PC上的软件进行数据采集、分析以及控制等。

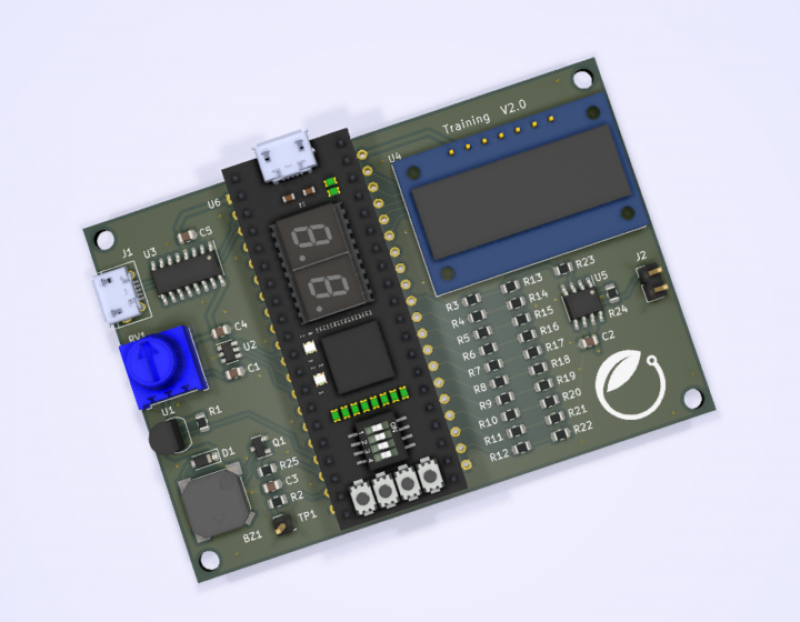

基于小脚丫FPGA的综合技能训练板3D效果图

基于小脚丫FPGA的综合技能训练板的功能框图

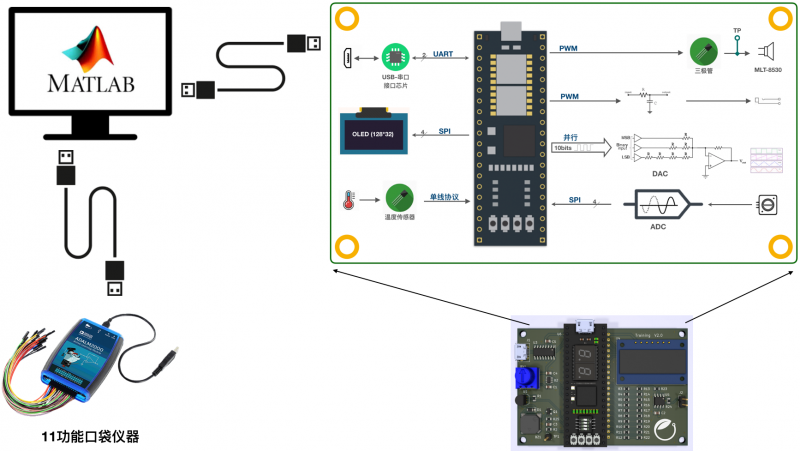

基于小脚丫FPGA的综合训练口袋实验系统沟通

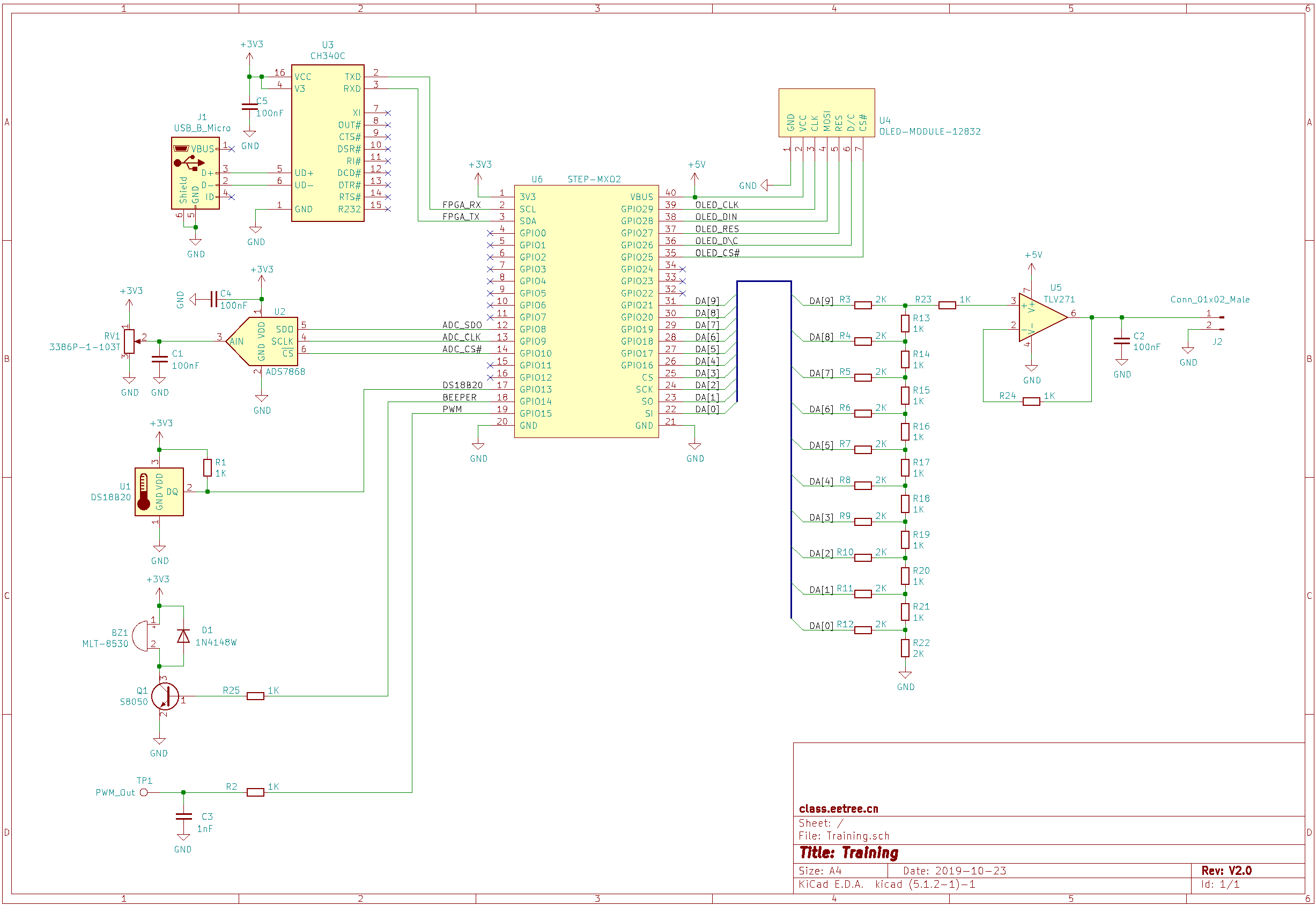

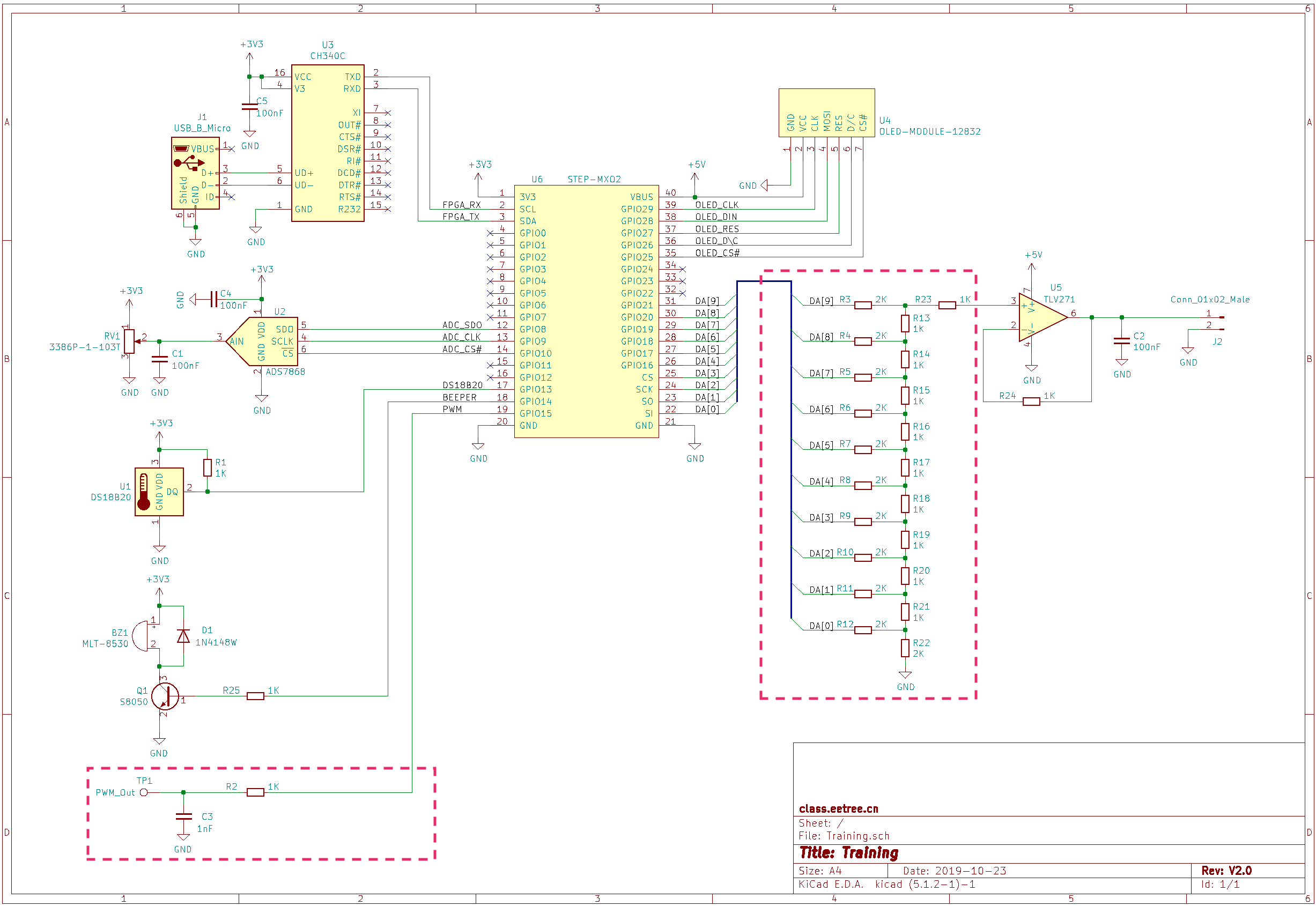

基于小脚丫FPGA的综合技能训练板的原理图

用于DDS信号源的DAC

在本平台上有两种方式可以实现DAC的功能,见图中红色虚线标记的部分。

综合技能训练板上的DAC功能

- 由R-2R构成的高速10位并行DAC - 上图中右侧红色虚线的部分

- 由PWM构成的简易DAC - 上图中左侧红色虚线的部分, 关于PWM的使用方法可以参见pwm_verilog中的详细介绍以及相关的技术文章。

FPGA编程的管脚分配文件

1 使用基于Lattice XO2-4000HC的小脚丫FPGA, 使用diamond工具

小脚丫FPGA模块的管脚 | DAC的数据位 |

x | ClkIn |

Pin 31 | DA[9] |

Pin 30 | DA[8] |

Pin 29 | DA[7] |

Pin 28 | DA[6] |

Pin 27 | DA[5] |

Pin 26 | DA[4] |

Pin 25 | DA[3] |

Pin 24 | DA[2] |

Pin 23 | DA[1] |

Pin 22 | DA[0] |

Pin 19 | PWM_Out |

Pin 39 | OledClk |

Pin 38 | OledDin |

Pin 37 | OledRes |

Pin 36 | OledDc |

Pin 35 | OledCs |

Pin 2 | UartRx |

Pin 3 | UartTx |

Pin 12 | AdcSdo |

Pin 13 | AdcClk |

Pin 14 | AdcCs |

Pin 17 | DS18B20 |

Pin 18 | Beeper |

2 基于Intel MAX10M02/08的小脚丫FPGA模块,使用Quartus工具

小脚丫FPGA模块的管脚 | DAC的数据位 |

x | ClkIn |

Pin 31 | DA[9] |

Pin 30 | DA[8] |

Pin 29 | DA[7] |

Pin 28 | DA[6] |

Pin 27 | DA[5] |

Pin 26 | DA[4] |

Pin 25 | DA[3] |

Pin 24 | DA[2] |

Pin 23 | DA[1] |

Pin 22 | DA[0] |

Pin 19 | PWM_Out |

Pin 39 | OledClk |

Pin 38 | OledDin |

Pin 37 | OledRes |

Pin 36 | OledDc |

Pin 35 | OledCs |

Pin 2 | UartRx |

Pin 3 | UartTx |

Pin 12 | AdcSdo |

Pin 13 | AdcClk |

Pin 14 | AdcCs |

Pin 17 | DS18B20 |

Pin 18 | Beeper |

相关技术文档

- 基于小脚丫FPGA的综合技能训练板的原理图PDF文件下载

- 小脚丫FPGA综合技能训练板功能说明

- Lattice XO2-4000HC版本小脚丫的管脚分配文件,只用于DDS信号源部分的管脚,用于Diamond编译软件

- Intel MAX10M02/08版本小脚丫的管脚分配文件,用于Quartus编译软件

- 综合训练底板网盘资料 链接:https://pan.baidu.com/s/1LCCQNDidzrbjKMnqa4COMg 提取码:y67p

应用案例及参考代码: