本人有幸参加本次2025寒假一起练活动,本项目是基于硬禾课堂提供的iCE40UP5K FPGA开发平台,设计并实现了一款可定时的音乐闹钟。

该项目的具体要求是:

使用扩展板上的12颗彩灯对应于12个小时;在核心板上的FPGA产生时钟,在OLED显示评上通过模拟或者数字的方式显示当前的时间-小时、分、秒,同时将“小时”的信息通过12颗彩灯来显示,还需要具有定时的功能,通过扩展板上的按键设置时间,到该时间点即(彩灯闪烁+音频播放),持续5秒钟时间)音频播放通过扩展板上的蜂鸣器来实现)

项目采用模块化设计理念,充分发挥FPGA并行处理优势,在单一芯片内完成时序控制、状态机管理、外设驱动等复杂功能,体现了硬件系统集成设计的核心思想。

设计思路:

本项目我将其分成两大部分进行解决。一部分是时钟部分,一部分是闹钟部分。时钟部分首先从RTC提取出时间信息,将时间信息给12个RGB三色灯和OLED显示屏,并将“小时”的信息显示出来。闹钟部分通过两个按键设计了定时系统,锁定的时间到达时通过蜂鸣器播放5S音乐。

启动后需要通过run键唤醒彩灯,按下k1使闹钟的小时+1,按下k2使闹钟的分钟+1,闹钟是从0开始算的,是在设定好的闹钟时间上增加一分钟或一小时,不是在当前时间上增加一分钟或一小时,举个例子,清零后按1下k1、按2下k2就会使蜂鸣器在时间1:02时响起,再按一次k1就会使蜂鸣器在时间2:02时响起。

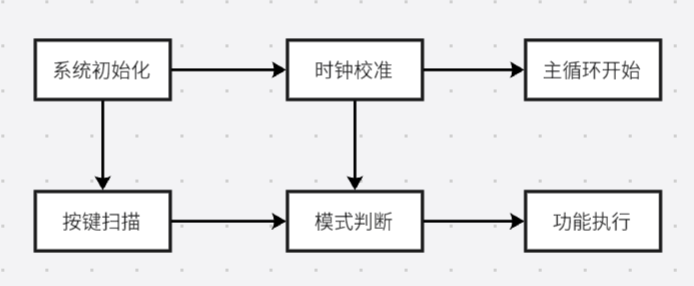

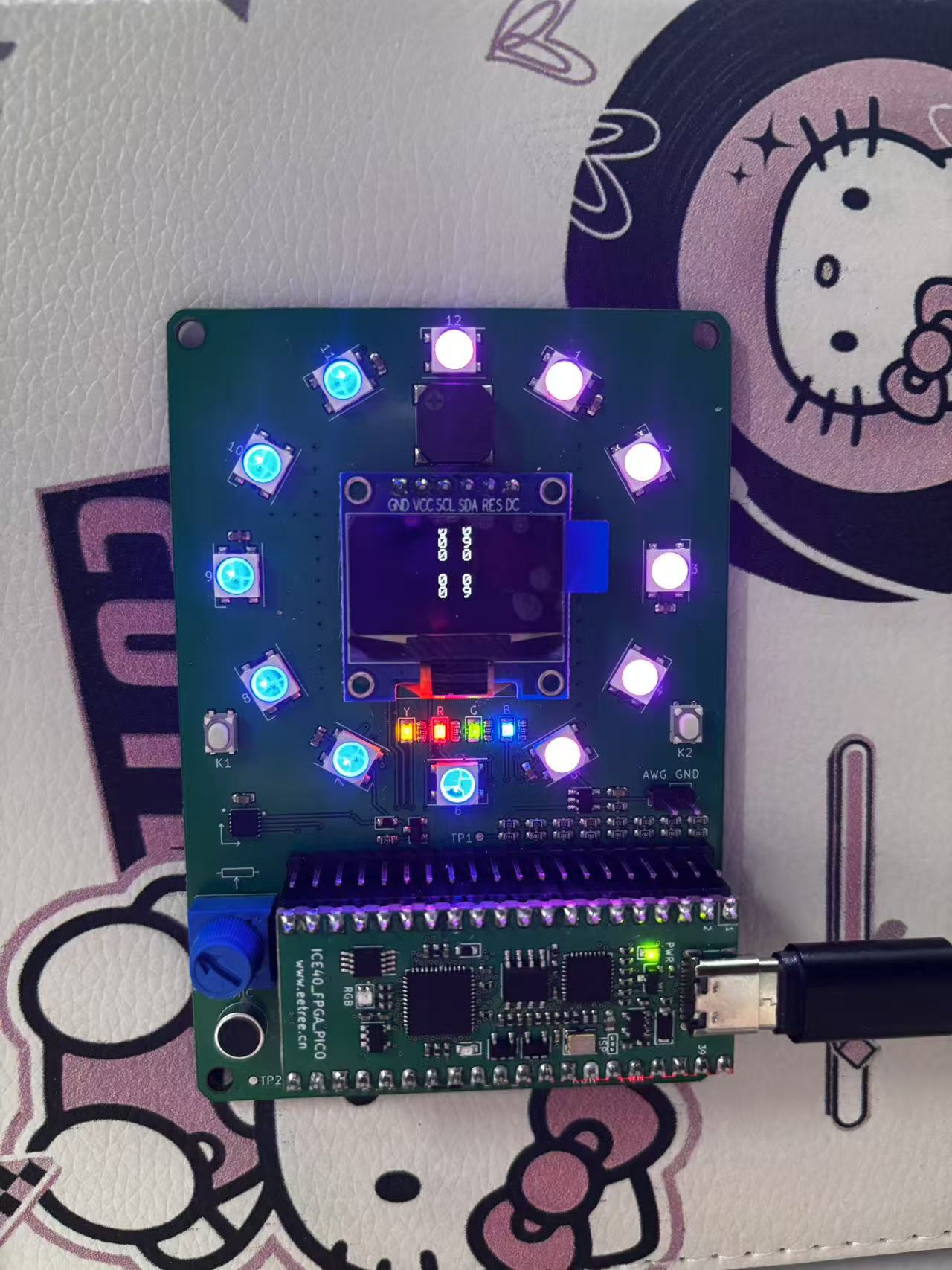

主程序的流程图如下:

硬件平台介绍

核心控制单元是iCE40UP5K FPGA核心板,属于Lattice半导体iCE40 UltraPlus系列FPGA开发板,拥有5280逻辑单元(LUT4架构)、1MBit单端口RAM,支持DAPLink调试与程序下载,管脚兼容树莓派Pico扩展接口。

外围扩展模块由一圈灯扩展板,拥有12颗WS2812B智能彩灯(串行级联控制),一块0.96寸OLED显示屏(SSD1306驱动芯片,SPI接口),4路机械按键(独立式设计),以及无源蜂鸣器(PWM驱动)组成,依靠USB Type-C接口供电。

系统架构设计流程图

设计思路

利用FPGA硬件的并行特性,将各功能模块独立封装,通过全局状态机协调工作。例如,OLED刷新与LED控制时序可同步运行互不干扰。

利用扩展板上的两个按钮k1k2设置闹钟时间,按下k1使闹钟的小时+1,按下k2使闹钟的分钟+1,利用红加蓝形成的紫色彩灯凸显小时的显示,闹钟时间到时,采用红蓝双色闪烁彩灯展示。

代码介绍

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) begin

nummax <= nummax1;

num <= 6'd0;

delay_cnt<=64'd0;

end

else if(num <= nummax) begin

if(delay_cnt <= 64'd1500000) begin

delay_cnt <= delay_cnt + 1'd1;

case(alarm_trigger)

1'd0: tone <= mem0;

default: tone <= mem1[num];

endcase

end

else begin

delay_cnt <= 64'd0;

num <= num + 1'd1;

end

end

else begin

num <= 7'd0;

end

end

闹钟部分代码如上,实现音乐的持续时间为5S和音源的选择。

delay_cnt阈值控制音符持续时间,alarm_trigger选择正常播放模式或报警模式。

reg [23:0] clk_1s_cnt;

always @(posedge clk) begin

if (clk_1s_cnt >= 24'd11_999_999) begin // 12MHz/12,000,000 = 1Hz

clk_1s_cnt <= 0;

clk_1s <= ~clk_1s;

end else begin

clk_1s_cnt <= clk_1s_cnt + 1;

end

end

always @(posedge clk_1s) begin

{sec_ten, sec_unit} <= (Second >= 59) ? 6'd0 : Second + 1;

end

以上为OLED时间显示功能的部分代码,时钟分频与时间更新,实现实时显示时、分、秒。使用一个24位的计数器生成1Hz的时钟信号clk_1s,用于时间的更新。这里计数器最大值设置为5,999,999,因为12MHz时钟下,每6,000,000个周期是0.5秒,所以clk_1s每0.5秒翻转一次,形成1Hz的方波。

always@(tone) begin

case(tone)

//太长了且重复性高影响观看,省略,用于确定音乐频率

default:time_end = 20'd1048575;

endcase

end

reg [17:0] time_cnt;

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) begin

time_cnt <= 1'b0;

end else if(time_cnt>=time_end) begin

time_cnt <= 1'b0;

end else begin

time_cnt <= time_cnt + 1'b1;

end

end

always@(posedge clk_in or negedge rst_n_in) begin

if(!rst_n_in) begin

piano_out <= 1'b0;

end else if(time_cnt==time_end) begin

piano_out <= ~piano_out;

end else begin

piano_out <= piano_out;

end

end

endmodule

以上是蜂鸣器部分代码,根据tone的值选择time_end。这里每个tone对应一个特定的time_end值,不同音调对应的计数器阈值。这个阈值决定了PWM的频率,计数器达到这个值时会翻转输出信号,从而生成不同频率的方波。每个时钟周期计数器递增,直到达到time_end后复位。always块控制piano_out的输出。每当计数器达到time_end时,输出翻转,生成50%占空比的方波。当tone_en无效时,输出保持低。

功能演示

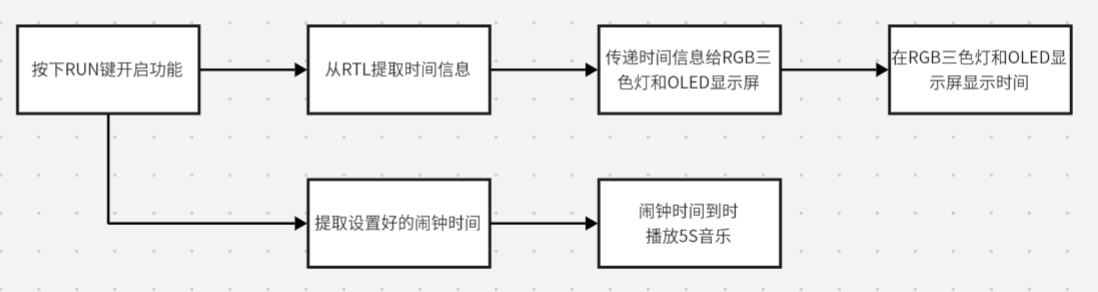

正常时间显示模式,OLED界面布局,LED呈现的灯效表现,开始测试之前可能需要先按下run键唤醒彩灯并清零。

显示屏上以(时间)小时

分钟

秒钟

(闹钟)小时

分钟

的形式显示时间。

蜂鸣器播放音乐片段,还设置了模式交互功能,利用扩展板上的两个按钮k1k2设置时间,按下k1使闹钟的小时+1,按下k2使闹钟的分钟+1,闹钟是从0开始算的,是在设定好的闹钟时间上增加一分钟或一小时,不是在当前时间上增加一分钟或一小时,举个例子,清零后,是按一下k1、按23下k2就会使蜂鸣器在时间1:23时响起,不管闹钟时间到了没有再按一次k1就会使蜂鸣器在时间2:23时响起。

音乐和彩灯

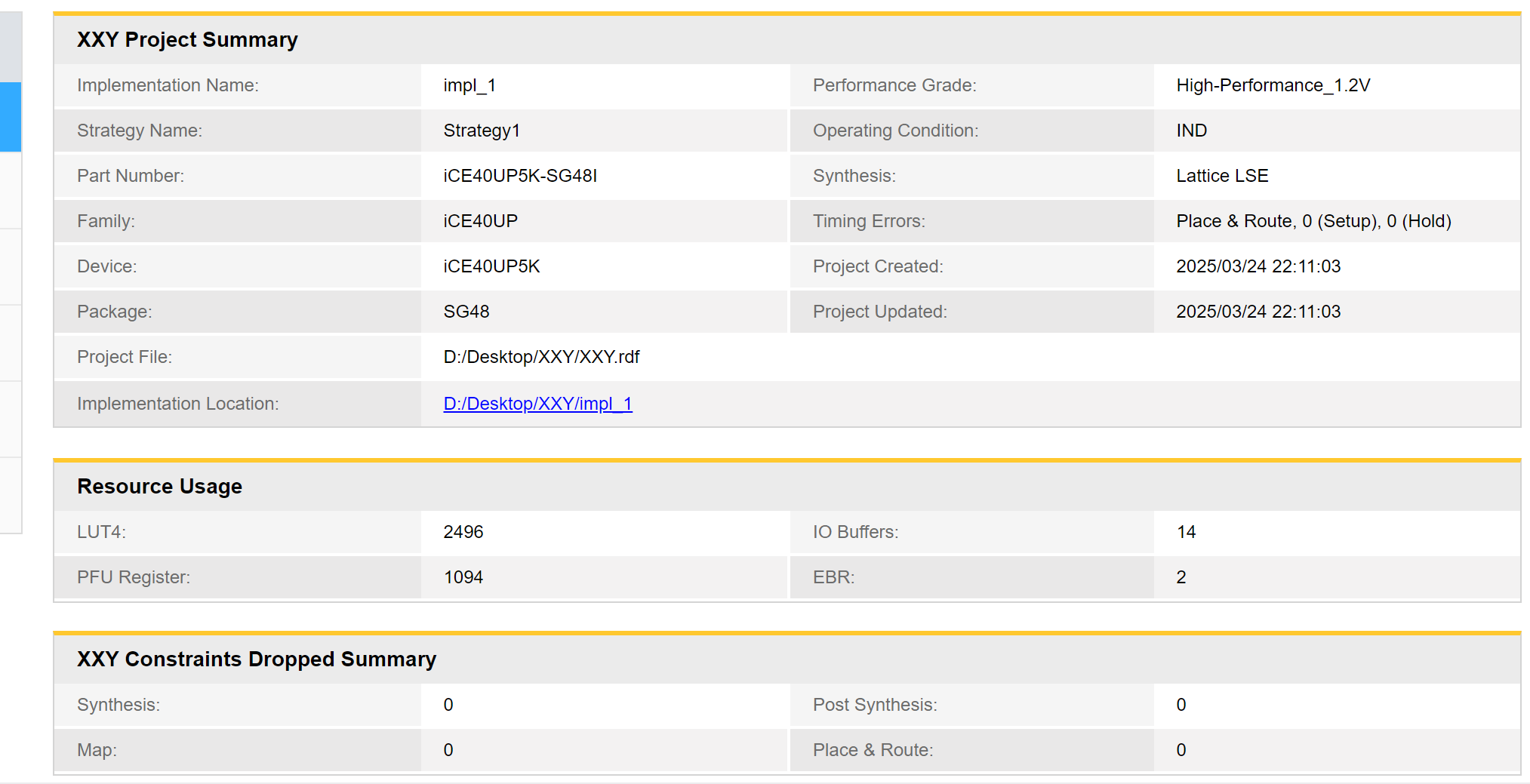

资源报告

技术难点与解决方案

在项目执行的过程中我遇到了一些比较棘手的问题,在时钟部分中RGB灯的显示出现错误,以及在调试的过程中有时会出现过了显示的时间但是灯并没有熄灭,最终导致12个灯颜色混乱,无法看出时间,经过多次排查和向老师请教后发现是数据时序偏差超过了芯片容忍范围,通过采用状态机精确控制时间的方式解决了问题。

在闹钟部分,设定响一段时间的音乐在结束后,蜂鸣器改为发出蜂鸣声,一直响个不停,虽然把视频剪辑一下就看不出来问题,但还是影响项目的完成程度,除此之外,过程中还发现了资源占用超标、综合后逻辑单元超限的问题,通过多个模块共用分频时钟的形式共享计数器、显存和音乐共用Block RAM等方式进行了优化。遇到这些问题后,我询问了几位使用过ICE40UP50K的同学,又反复观看了老师的直播课程,对照老师的源代码进行了一定的修改,最后解决了问题。

心得体会

通过参与本次硬禾课堂的实践项目,我深刻体会到硬件系统设计的复杂性与挑战性。在开发过程中,不仅需要掌握Verilog语法,更要理解硬件并行的本质特征。例如,在调试驱动时,传统单片机思维中的顺序执行方式完全不适用,必须构建精确的时序状态机。

我在项目实践中最大的收获是建立了完整的硬件开发思维体系。从需求分析到模块划分,从仿真验证到板级调试,每个环节都需要严谨的工程思维。特别是在资源受限的iCE40UP5K平台上,学会了通过算法优化和架构调整来平衡功能与性能。

建议未来项目可增加更多跨平台对比内容,例如比较FPGA实现与ARM Cortex-M方案在相同功能下的性能差异。此外,期待硬禾课堂能提供更多实战案例库,方便学习者参考借鉴。

本次实践不仅巩固了数字电路基础知识,更培养了解决复杂工程问题的能力。面对调试过程中层出不穷的异常现象,逐步形成了“现象观察→逻辑分析→方案验证”的系统化排错方法论。这些经验对我后续的嵌入式系统开发具有重要指导意义。