一、项目介绍

本次项目利用小脚丫 FPGA STEP BaseBoard V4.0 套件,设计一个交通灯控制系统,模拟常见的十字路口交通信号灯切换逻辑,并为学习数字电路设计与 FPGA 开发提供实践机会。

通过该项目,不仅加深了对数字逻辑电路知识的理解,如时序电路、状态机等,还掌握了 FPGA 硬件开发平台的基本使用方法,提升了从理论到实际工程应用的转化能力,为今后从事相关领域的研究与开发奠定基础。

二、硬件介绍

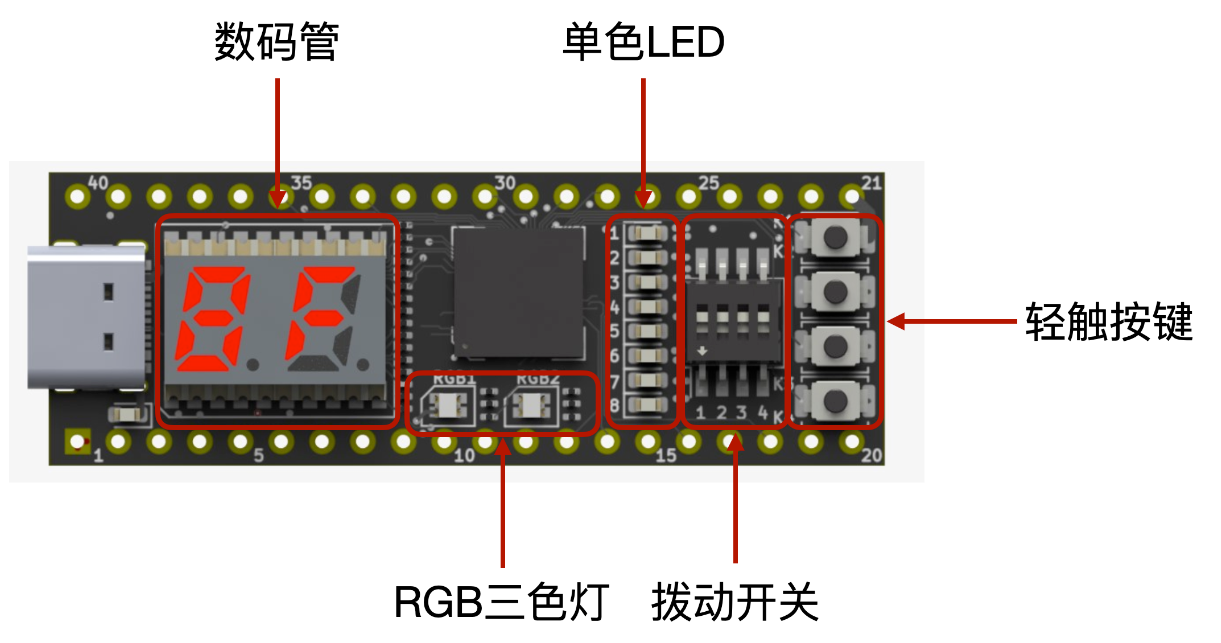

小脚丫 FPGA STEP BaseBoard V4.0 套件作为核心硬件平台,具备丰富的资源。它搭载了高性能的 FPGA 芯片,拥有足够的逻辑单元来实现复杂的数字逻辑功能,能够快速处理交通灯控制系统中的各种状态转换与信号计时需求。

板载多个可编程输入输出引脚,方便连接外部设备,如用于显示交通灯状态的 LED 灯。这些 LED 灯通过不同颜色(红、黄、绿)直观地呈现交通信号灯的状态,让我们可以实时观察系统运行效果。此外,套件还配备了时钟源,为系统提供稳定的时钟信号,确保各个模块按照精确的时序协同工作。

同时配备环境光、红外距离传感器RPR-0521RS,使用IIC进行通讯,可以实现环境光的监测,利用红外进行距离测量。

STEP-MXO2-LPC开发板:

BaseBoard V4.0扩展版:

三、项目设计思路介绍

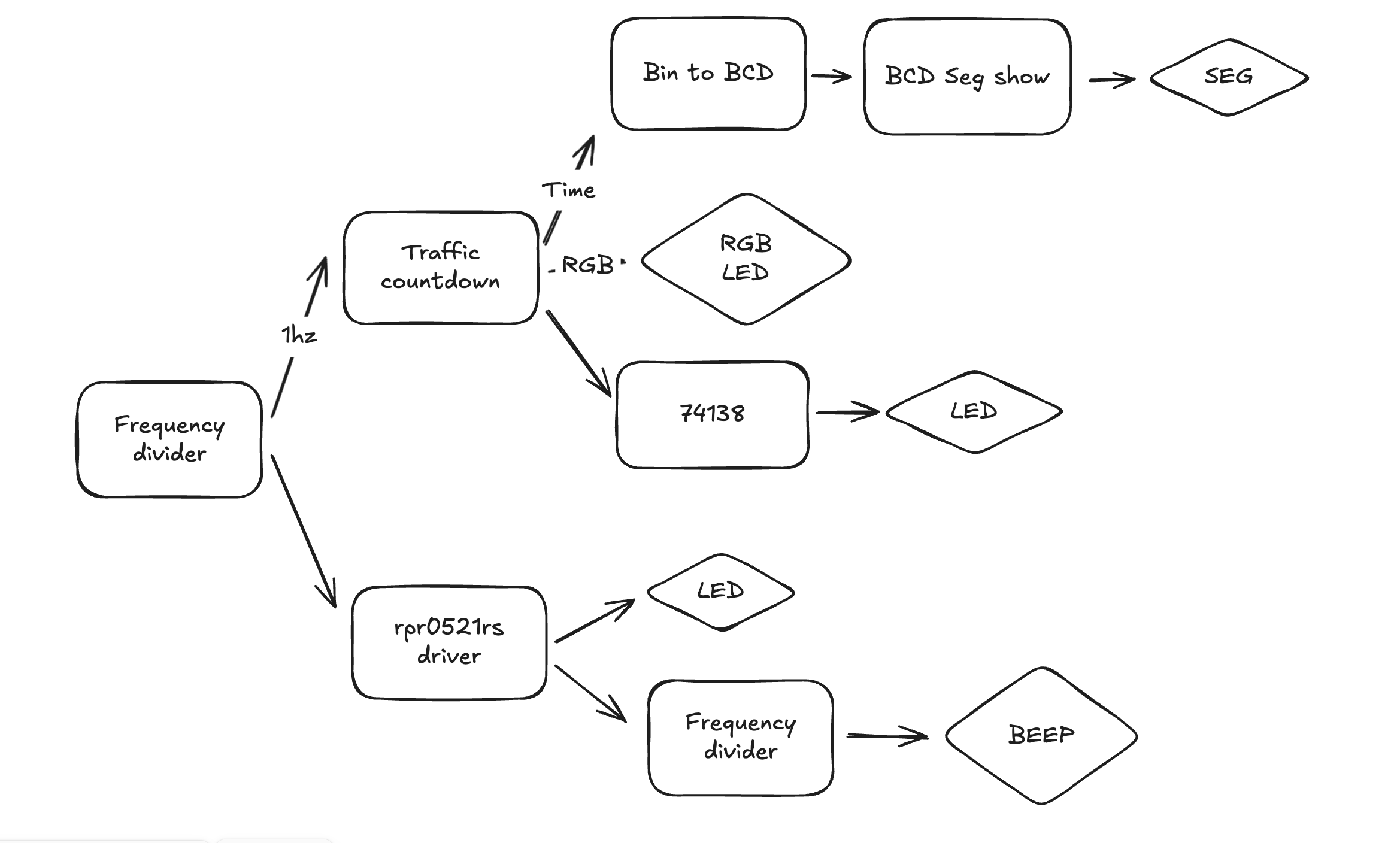

在本次基于小脚丫 FPGA STEP BaseBoard V4.0 套件的设计中,整体架构涵盖两大关键部分。

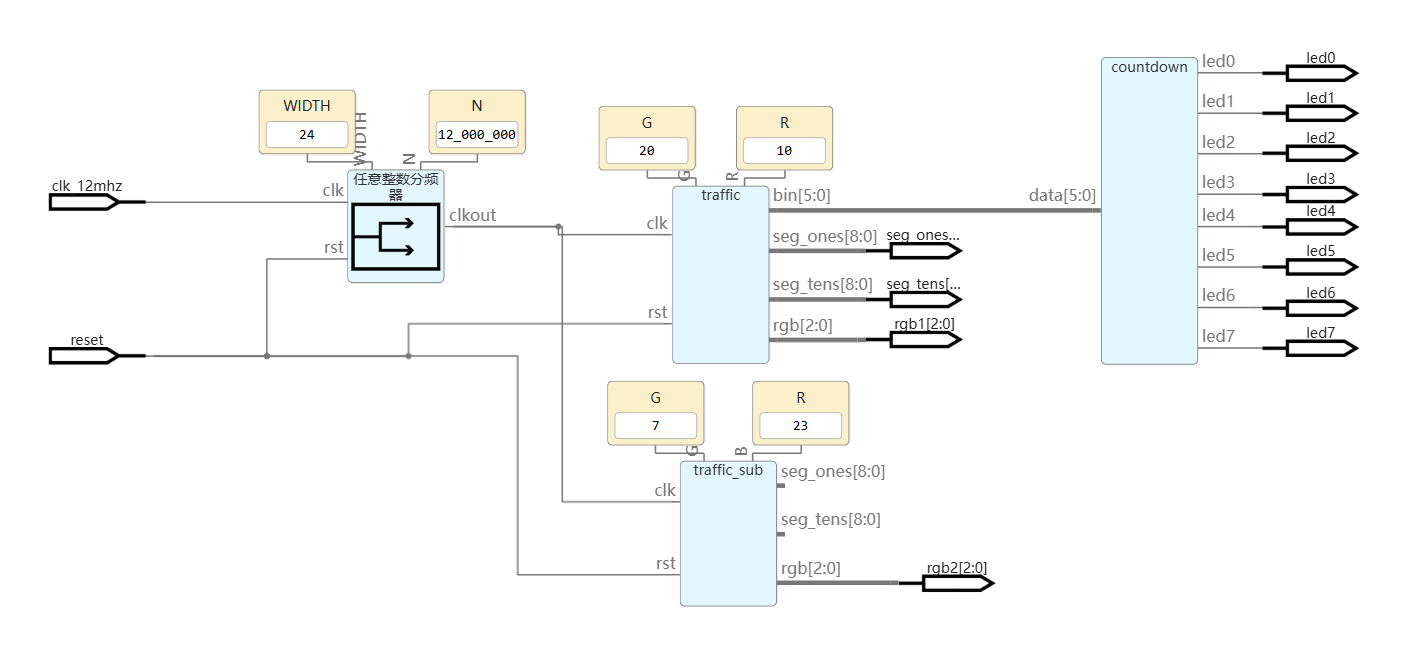

第一部分为交通灯核心管控部分,利用板载时钟源,经精心设计的分频器精准分频得到稳定的 1Hz 时钟信号,将其作为交通灯控制系统精准计时的基石。此系统集成倒计时逻辑以及红绿灯状态的智能调控功能,借助数码管和LED动态呈现倒计时进程,以 RGB LED 灯鲜明展示红绿灯实时状态,确保交通模拟的直观与准确。

第二部分是环境感知反馈部分,由环境光监测与红外距离传感器协同作业,依托专业驱动模块,依据环境光亮度差异驱动不同数量的 LED 亮起,实现光强可视化;同时,当检测到物体进入设定的红外距离阈值后,迅速触发蜂鸣器发出警报,提升系统的环境交互性与安全性。

四、软件流程图和关键代码介绍

webide项目地址:https://www.stepfpga.com/project/16704/gui?type=top

1. 交通灯控制系统

always @(posedge clk or negedge rst) begin

if (!rst) begin // Reset重置

mode = 2'b00;

counter = G;

end else begin

case(mode) // 绿、黄、红灯三个状态

2'b00: begin

if (counter == 1) begin

mode <= 2'b01;

counter <= Y;

end else begin

counter <= counter - 1;

end

end

2'b01: begin

if (counter == 1) begin

mode <= 2'b10;

counter <= R;

end else begin

counter <= counter - 1;

end

end

2'b10: begin

if (counter == 1) begin

mode = 2'b00;

counter <= G;

end else begin

counter <= counter - 1;

end

end

endcase

end

end

always @(*) begin // RGB LED显示部分

case (mode)

2'b00: rgb = 3'b101; // Green

2'b01: rgb = 3'b001; // Yellow

2'b10: rgb = 3'b011; // Red

default: rgb = 3'b000;

endcase

end

本代码为主干路控制代码,初始状态为绿灯,支路初始状态则为红灯。

关键部分则是红绿灯的倒计时与循环部分。

实际生活中,红绿灯倒计时显示到1之后就会转换状态,而不会显示0,这一点需要注意。

2. 两位十进制数显示

a. Bin to BCD

always @(*) begin

bcd = 8'b0;

for (i = 5; i >= 0; i = i - 1) begin

if (bcd[3:0] > 4)

bcd[3:0] = bcd[3:0] + 3;

if (bcd[7:4] > 4)

bcd[7:4] = bcd[7:4] + 3;

bcd = {bcd[6:0], bin[i]};

end

end

使用加三位移法,将二进制数转换为BCD码以便显示。

b. BCD Segment show

always @(*) begin

seg[0] = 9'h3f;

seg[1] = 9'h06;

seg[2] = 9'h5b;

seg[3] = 9'h4f;

seg[4] = 9'h66;

seg[5] = 9'h6d;

seg[6] = 9'h7d;

seg[7] = 9'h07;

seg[8] = 9'h7f;

seg[9] = 9'h6f;

end

assign seg_ones = seg[bcd[3:0]];

assign seg_tens = seg[bcd[7:4]];

利用状态机对BCD码进行显示。

3. rpr0521rs driver

利用例程lab8进行修改

我主要对数据处理部分进行修改

// Prox Beep控制

always@(prox_dat2[11:9]) begin

if (prox_dat2[11:9] < 3'b010)

beep_en <= 1'b0;

else

beep_en <= 1'b1;

end

// Lux LED灯控制

always@(1) begin

if(lux < 20000)

Y_out <= 8'b00000000;

else if(lux < 40000)

Y_out <= 8'b00000001;

else if(lux < 80000)

Y_out <= 8'b00000011;

else if(lux < 160000)

Y_out <= 8'b00000111;

else if(lux < 320000)

Y_out <= 8'b00001111;

else if(lux < 640000)

Y_out <= 8'b00011111;

else if(lux < 1280000)

Y_out <= 8'b00111111;

else if(lux < 2560000)

Y_out <= 8'b01111111;

else

Y_out <= 8'b11111111;

end

其中ALS部分,为了扩大环境光的检测范围,每两个阈值之间为2倍关系。

五、功能展示图及说明

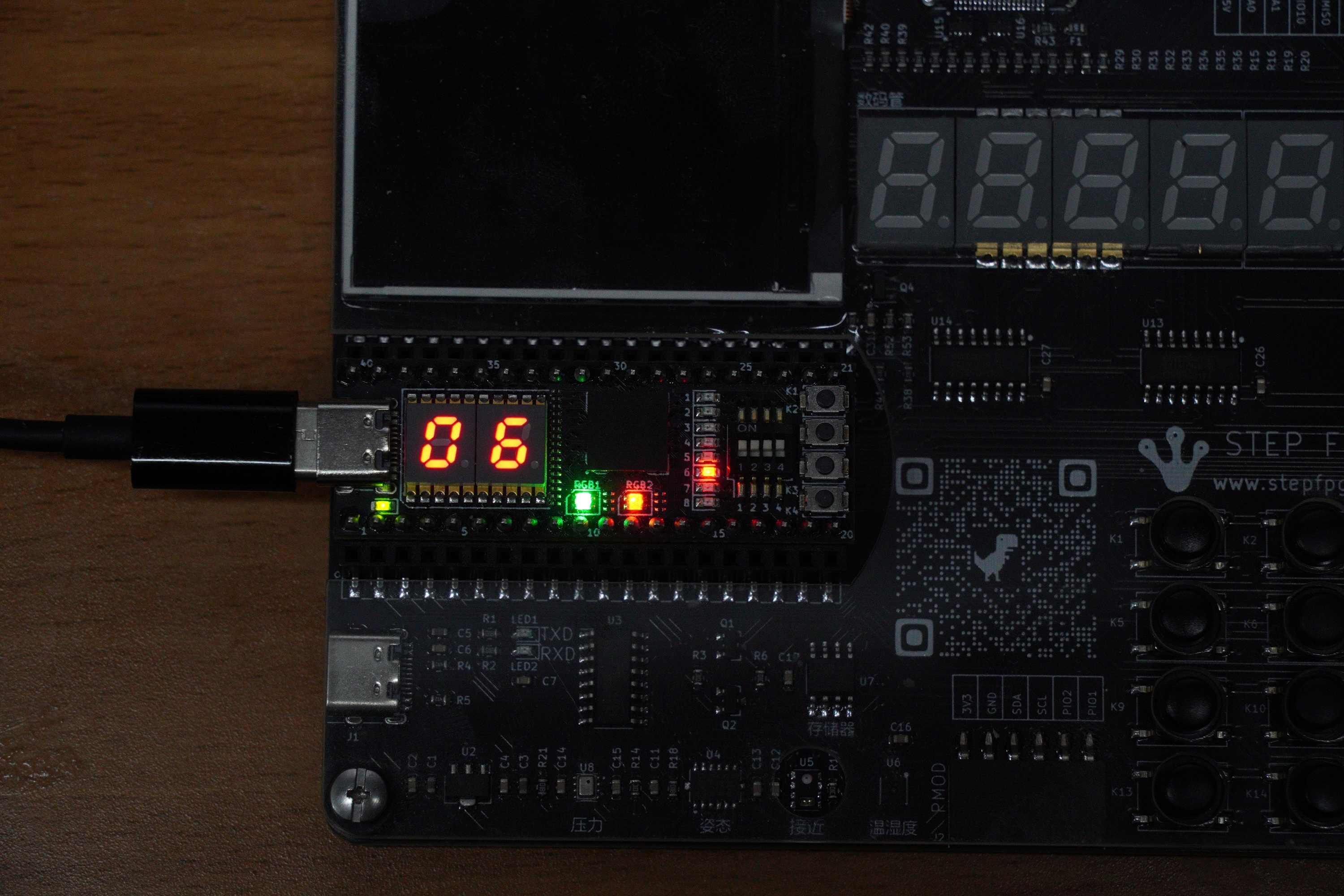

1. 交通灯控制系统

数码管显示主干路的倒计时,左侧LED为主干路,右侧为支路,8个红色led则为最后8s倒计时。

主路绿灯,支路红灯。

主路黄灯,支路红灯。

主路红灯,支路绿灯。

2. 环境光与距离传感部分

低光照情况下,LED亮6个。

手电筒照射,LED都不亮。

六、FPGA资源占用报告

- 交通灯控制系统

Design Summary:

Number of registers: 56 out of 4635 (1%)

PFU registers: 56 out of 4320 (1%)

PIO registers: 0 out of 315 (0%)

Number of SLICEs: 80 out of 2160 (4%)

SLICEs as Logic/ROM: 80 out of 2160 (4%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 21 out of 2160 (1%)

Number of LUT4s: 159 out of 4320 (4%)

Number used as logic LUTs: 117

Number used as distributed RAM: 0

Number used as ripple logic: 42

Number used as shift registers: 0

Number of PIO sites used: 36 + 4(JTAG) out of 105 (38%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

EFB used : No

JTAG used : No

Readback used : No

Oscillator used : No

Startup used : No

POR : On

Bandgap : On

Number of Power Controller: 0 out of 1 (0%)

Number of Dynamic Bank Controller (BCINRD): 0 out of 6 (0%)

Number of Dynamic Bank Controller (BCLVDSO): 0 out of 1 (0%)

Number of DCCA: 0 out of 8 (0%)

Number of DCMA: 0 out of 2 (0%)

Number of PLLs: 0 out of 2 (0%)

Number of DQSDLLs: 0 out of 2 (0%)

Number of CLKDIVC: 0 out of 4 (0%)

Number of ECLKSYNCA: 0 out of 4 (0%)

Number of ECLKBRIDGECS: 0 out of 2 (0%)

- 环境光与距离监测

Design Summary

Number of registers: 215 out of 4635 (5%)

PFU registers: 212 out of 4320 (5%)

PIO registers: 3 out of 315 (1%)

Number of SLICEs: 743 out of 2160 (34%)

SLICEs as Logic/ROM: 743 out of 2160 (34%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 350 out of 2160 (16%)

Number of LUT4s: 1485 out of 4320 (34%)

Number used as logic LUTs: 785

Number used as distributed RAM: 0

Number used as ripple logic: 700

Number used as shift registers: 0

Number of PIO sites used: 13 + 4(JTAG) out of 105 (16%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

EFB used : No

JTAG used : No

Readback used : No

Oscillator used : No

Startup used : No

POR : On

Bandgap : On

Number of Power Controller: 0 out of 1 (0%)

Number of Dynamic Bank Controller (BCINRD): 0 out of 6 (0%)

Number of Dynamic Bank Controller (BCLVDSO): 0 out of 1 (0%)

Number of DCCA: 0 out of 8 (0%)

Number of DCMA: 0 out of 2 (0%)

Number of PLLs: 0 out of 2 (0%)

Number of DQSDLLs: 0 out of 2 (0%)

Number of CLKDIVC: 0 out of 4 (0%)

Number of ECLKSYNCA: 0 out of 4 (0%)

Number of ECLKBRIDGECS: 0 out of 2 (0%)

七、对本次活动的心得体会

通过本次利用小脚丫 FPGA STEP BaseBoard V4.0 套件设计交通灯控制系统的项目实践,收获颇丰。一方面,切实提升了自己的专业技能,从对 FPGA 的初步了解到能够独立完成一个具有实际应用场景的系统开发,对数字电路、硬件描述语言以及系统设计流程有了更深入的理解与掌握。

在项目实施过程中,也发现了一些有待改进的地方。对于初学者而言,套件的配套资料还需要更完善,入门引导略显不足,建议可以增加一些针对新手的简易教程,以更通俗易懂的方式介绍套件的基本使用与常见项目开发流程,帮助初学者更快上手。

总的来说,本次项目是一次极具价值的实践经历,为今后的学习与研究积累了宝贵经验,也期待在后续的学习中能够继续深入探索 FPGA 技术的更多应用领域,不断提升自己的专业素养。

八、资料链接:

任务要求:交通灯控制系统 - 图形化编程

开发版资料:小脚丫 FPGA STEP BaseBoard V4.0 套件

WebIDE项目:交通灯控制系统