项目介绍

本项目采用小脚丫FPGA开发板实现了交通灯的管理, 由于使用的是web ide 和本地的diamond软件, 所以两者的任务是分开的, 任务一和任务二实现了计时和蜂鸣器报警功能, 任务三和任务四实现了光照传感器和接近传感器控制LED灯模拟行人靠近的功能。

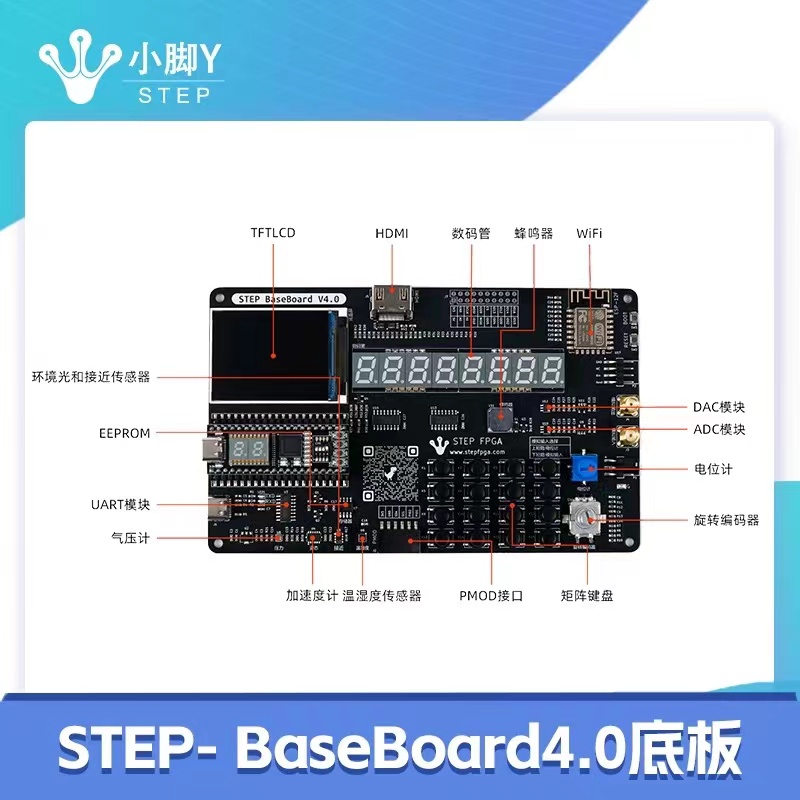

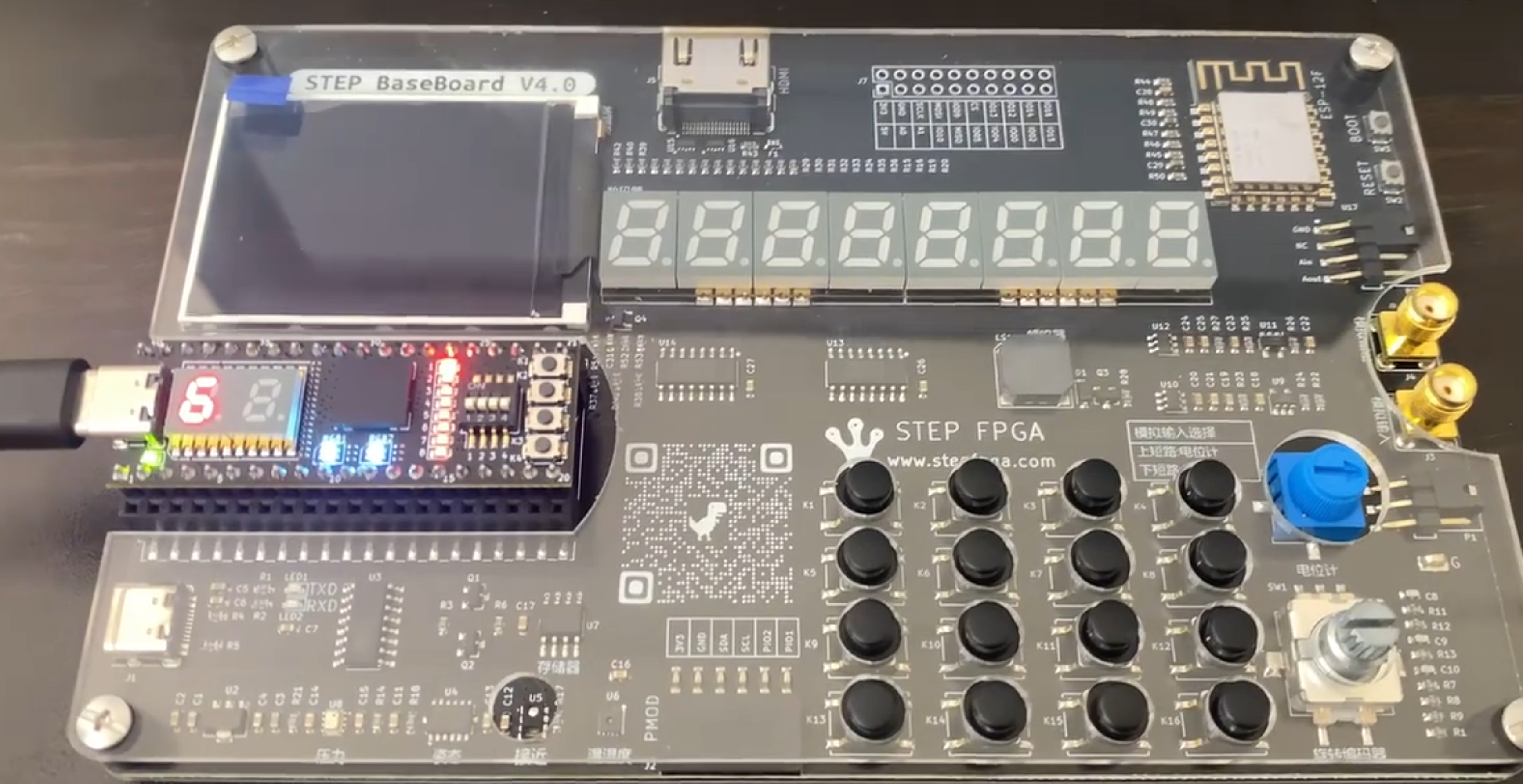

硬件介绍

小脚丫fpga开发板是由苏州思得普科技公司专门针对FPGA初学者打造的性价比最高、学习门槛最低的学习模块系列。经过不同版本的迭代。核心板和底板均具有丰富且开源的例程。

其具有4320个LUT,支持U盘直接拖动下载,省去了烧录器。 其配备的WEBIDE更是为初学者提供了简易的上手平台。

底板也具备着丰富的例程资源和外设模块来供大家学习使用。新上手FPGA的用户可以在小脚丫的社区找到充足的Demo和教程。

项目设计思路介绍

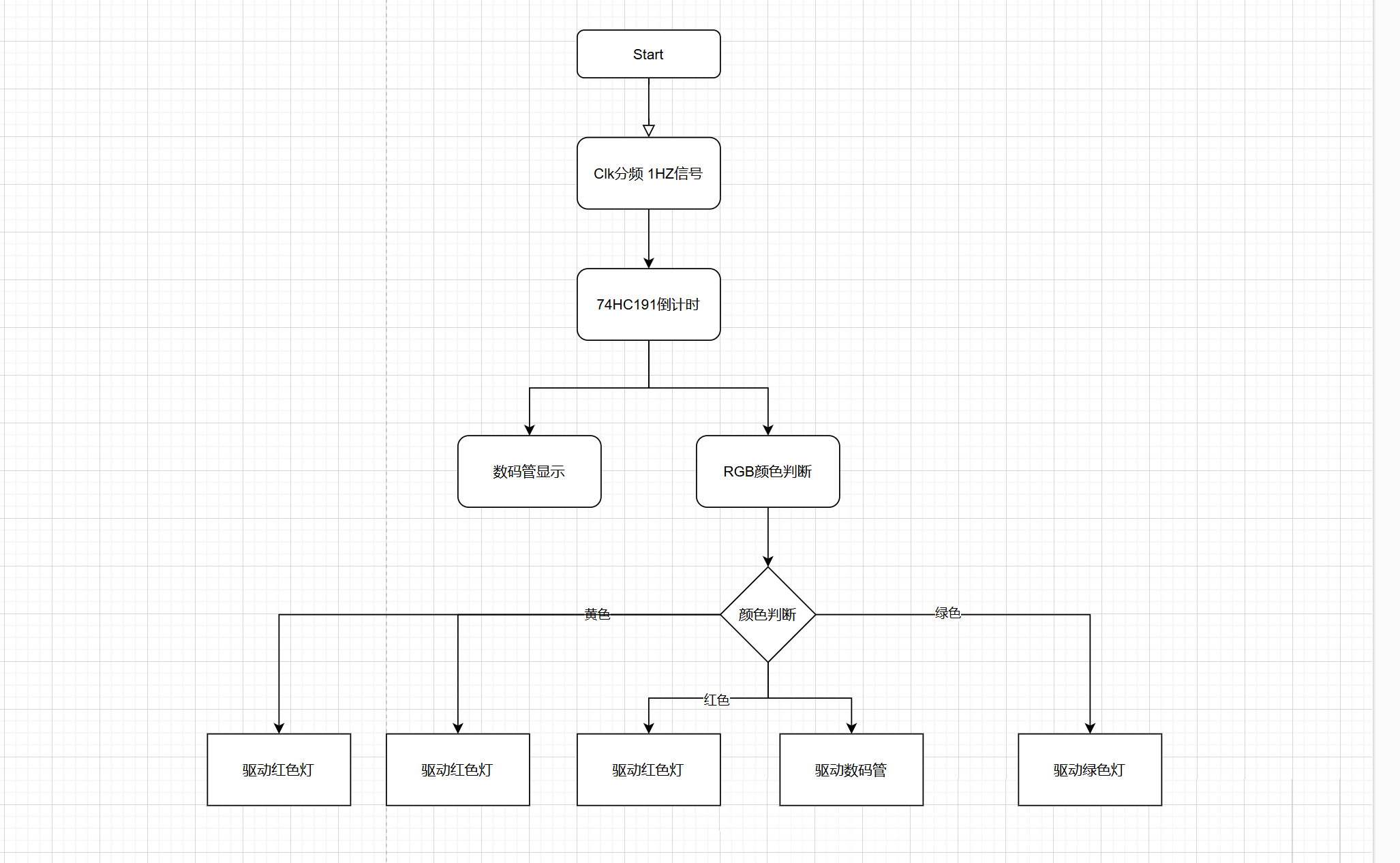

任务一和任务二

任务一和任务二需要在数码管上显示计时信息和驱动蜂鸣器报警。其中对于数码管的计时驱动还需要使用常规的74系列的元器件。 我的思路是首先从系统时钟开始,然后设置一个合适的分频的值,从而来获取1HZ的频率,然后使用74HC191器件来实现定时器的功能。通过设置定时器的初值,和计数方向,使其定时器可以在0-9之前循环计数。然后通过四个引脚将计数的二进制输出。通过四个引脚进入数码管驱动模块从而点亮数码管。而对于蜂鸣器,也需要从时钟进行分频。 不过决定蜂鸣器的开关的是由实际上74元器件的输出引脚决定的。 我这里设置的是当输出为4‘b0000的时候那么触发蜂鸣器开启或者关闭。由于是一个无源蜂鸣器。所以对于蜂鸣器的开关只需要判断输出使能位然后把分频后的时钟输入到蜂鸣器的输入即可。然后通过对当前0的次数进行计数来判断应该输出的灯的颜色。从而来控制显示不同颜色的灯光。

功能框图

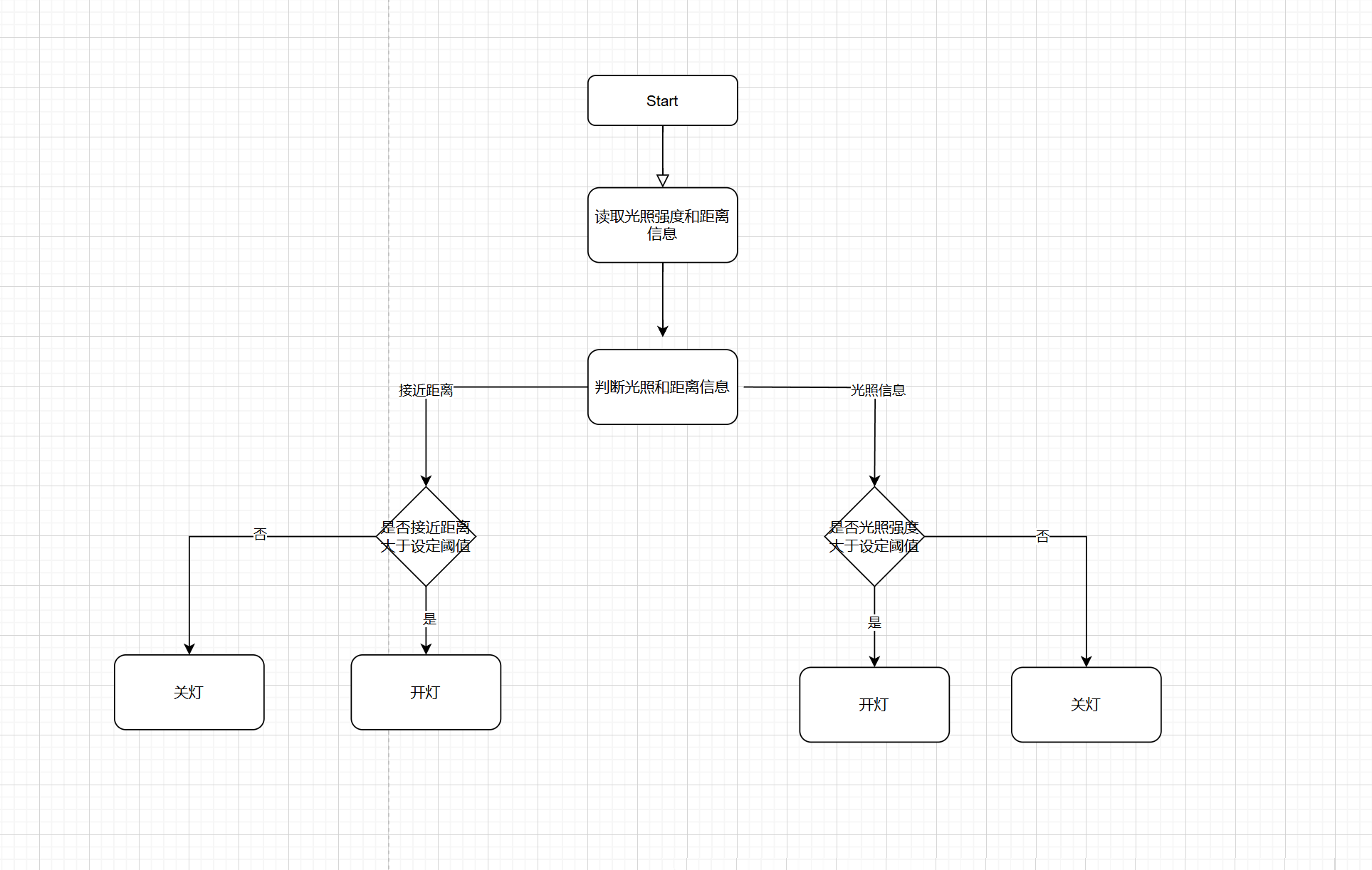

任务三和任务四

对于任务三和任务四,需要驱动底板上的光照和接近传感器来实现对LED灯的控制,得益于小脚丫提供了丰富的例程。我们可以直接在LAB8的代码上进行修改。 官方提供的demo是显示光照强度在底板的数码管上。然后根据接近的距离来点亮小脚丫核心板上的LED灯。我们需要在上面做一点小的修改。 使其判断光照强度低于某一个阈值的话点亮LED灯,然后高于某一个阈值的话关闭LED灯。同理于接近距离。

功能框图

软件流程图和关键代码介绍

任务一和任务二

任务一的主要难点就是在于其74系列器件的选型,我这里是使用的74HC191它正好可以充当一个计时器。从而当时钟输入的时候可以对预先设定的值进行计数。

触发保持模块代码, 其根据74HC191的输出决定是否使能蜂鸣器。

数码管的显示模块,其根据官方数码管显示的demo修改而来,移除了定义的模块使其可以通过74系列原件的输出直接控制8个引脚的输入从而点亮数码管。

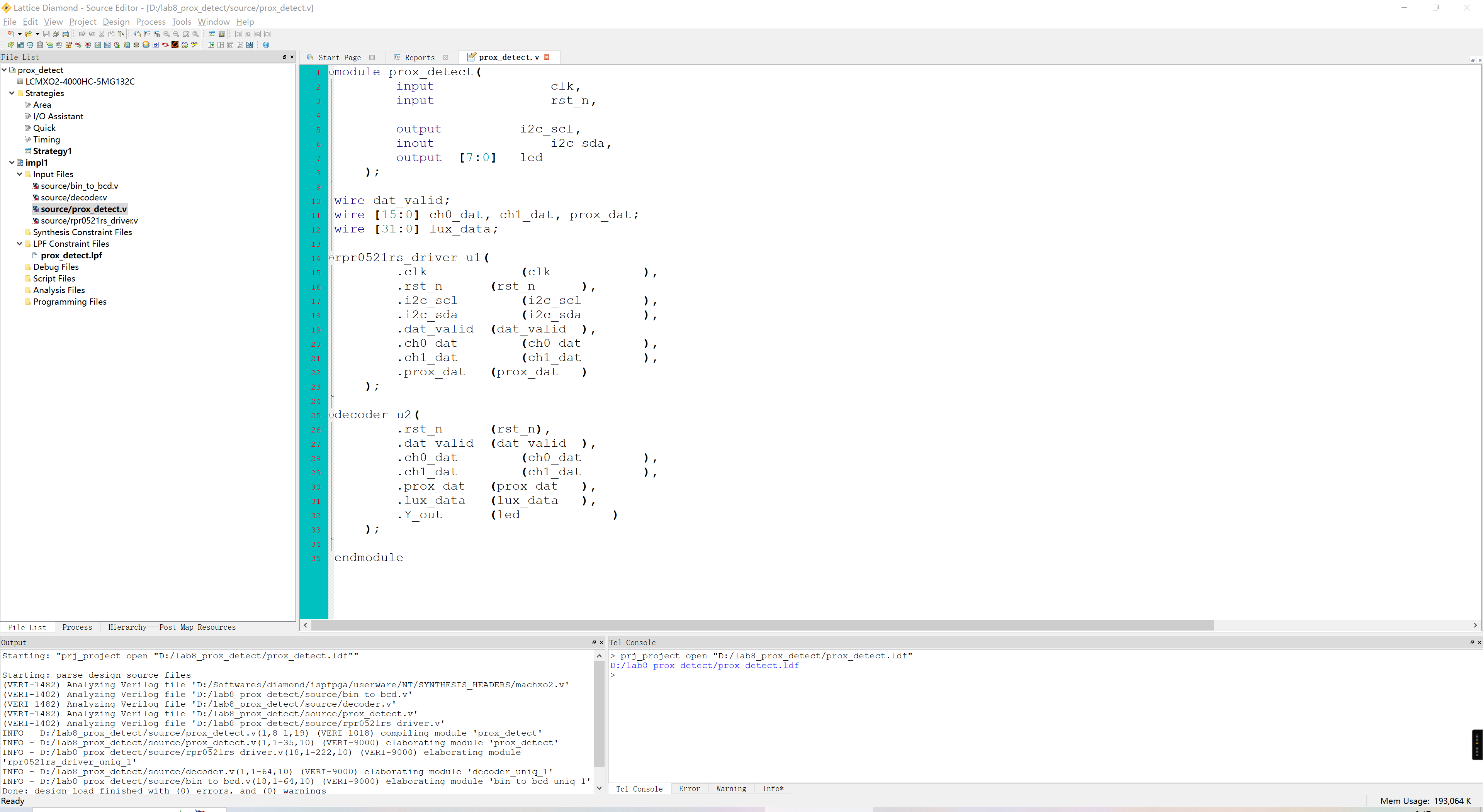

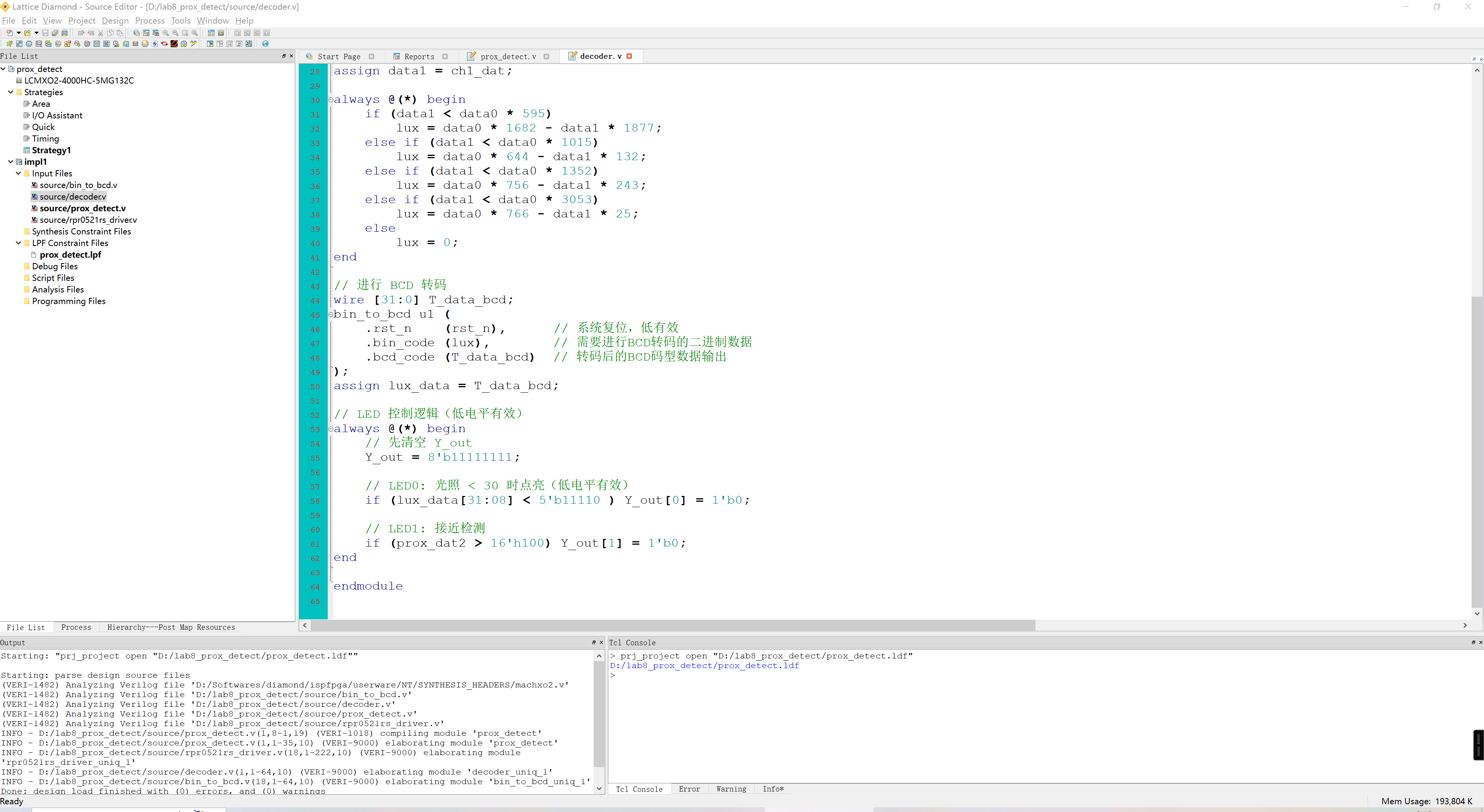

任务三和任务四

任务三和任务四我从LAB8中移除了数码管的显示驱动, 和在顶层文件中对数码管调用的函数。

然后修改decoder模块中对原本接近传感器判断距离的代码。如下所示

// LED 控制逻辑(低电平有效)

always @(*) begin

// 先清空 Y_out

Y_out = 8'b11111111;

// LED0: 光照 < 30 时点亮(低电平有效)

if (lux_data[31:08] < 5'b11110 ) Y_out[0] = 1'b0;

// LED1: 接近检测

if (prox_dat2 > 16'h100) Y_out[1] = 1'b0;

end

功能展示图及说明

任务一和任务二的FPGA资源占用情况

任务三和任务四的FPGA资源占用情况

任务一和任务二的功能演示和说明

数码管会以每秒一次的频率进行倒计时,当倒计时为0的时候,蜂鸣器打开。具体的效果请查看视频演示。

任务三和任务四的功能演示和说明

接近传感器和光照传感器控制LED灯0和LED1开启。具体效果请查看视频。

项目中遇到的难题和解决方法

我最大的问题就是没有学习过数字电路和Verilog, 在最初的时候我刚接触到小脚丫FPGA我甚至不知道该怎么点亮一个LED。 后来便自己在B站上找了一个大学教Verilog的教程,一直跟着学习语法,结构等。逐渐的我可以可以看懂基础的verilog代码了,也可以读懂小脚丫的demo了。再接着完成了这次项目的开发。我的建议是一定不要怕犯错,在解决问题的途中一定要敢于犯错。从而在每一次犯错的过程中总结经验然后用于下一次更好的产出。

对本次活动的心得体会

这次活动对我来说难度有点高, 因为之前并没有学习过数字电路。 没有接触过FPGA,非常感谢电子森林能够提供这次学习的机会。 小脚丫FPGA上手真的非常快,因为小脚丫社区的资料也是超级详细还有详细的步骤和代码。我觉得这个生态体系真的非常好。我希望小脚丫能够修复一下WebIDE,图形化编程中经常会造成图形视图丢失的问腿。尤其是在模块修改保存和设计视图切换的时候非常容易出问题。但是总体功能非常好!我希望小脚丫官方能修改一下这个WEBIDE,可以带给用户更好的体验!