内容介绍

内容介绍

1. 项目介绍

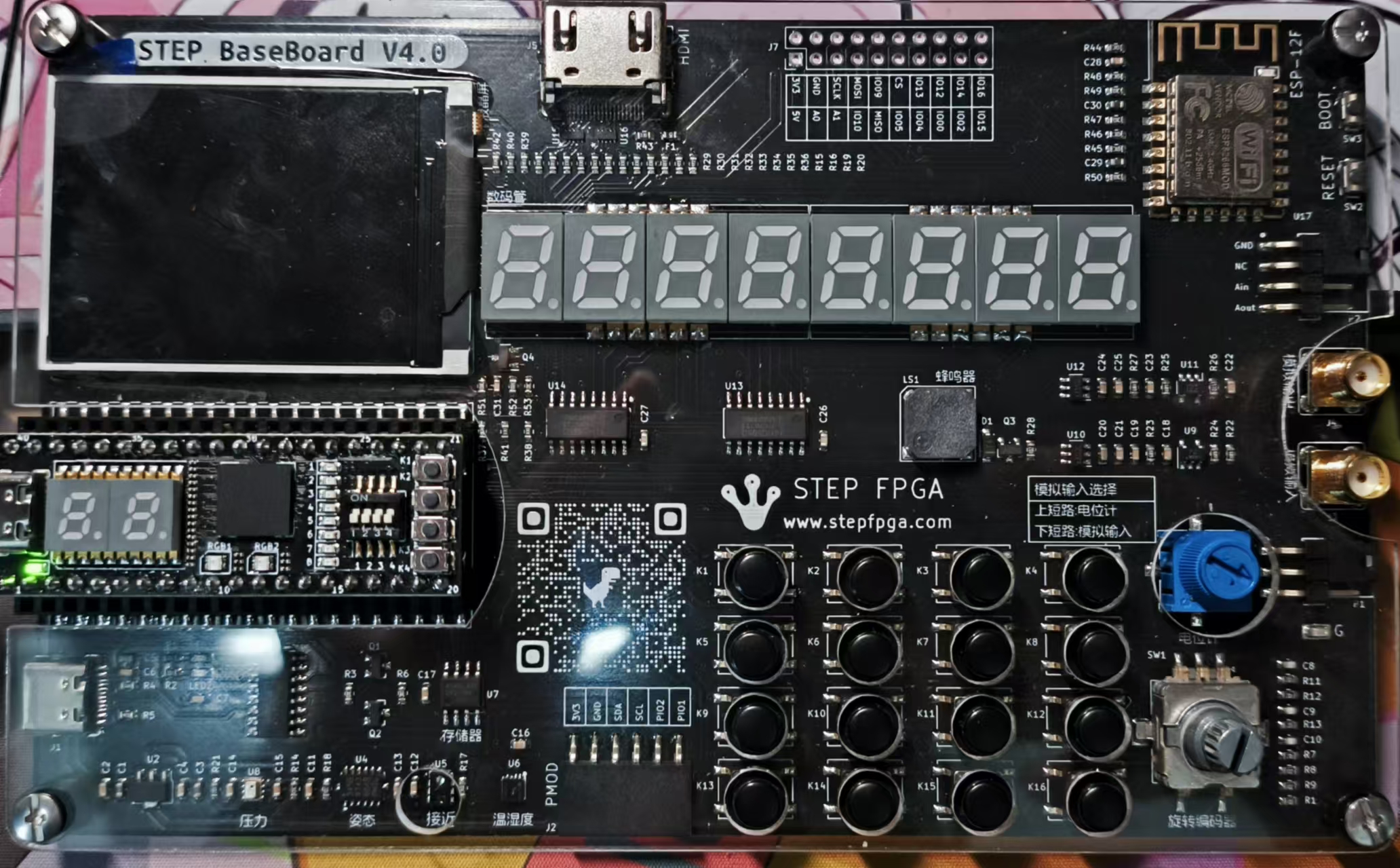

本项目旨在设计并实现一个智能交通灯控制系统,该系统能够根据环境光照强度自动控制路灯的开启与关闭,并通过数码管显示红绿灯剩余时间、光照值以及发出警示音。系统采用STEP MXO2-LPC FPGA核心板,结合STEP-BaseBoaed-V4.0开发板,完成了交通灯控制系统。

2. 硬件介绍

- FPGA开发板

使用STEP MXO2-LPC作为控制核心。STEP MXO2-LPC核心板是一款基于Lattice MachXO2系列FPGA的嵌入式开发板,具有低功耗和高性价比的优点,适用于快速原型设计、教学和工业应用。 - 数码管显示模块

使用直连的2段数码管显示交通灯的剩余时间(以秒计),74HC595芯片驱动8位数码管显示当前光照值。 - 蜂鸣器模块

采用单片蜂鸣器模块,用于在绿灯状态下发出提示音报警。 - 接近传感器(PSR-0521RS)

PSR-0521RS传感器用于检测人员的靠近和光照强度。 - 路灯驱动模块

8个红色LED点阵组成路灯阵列,当光照强度低于30lux时自动点亮。

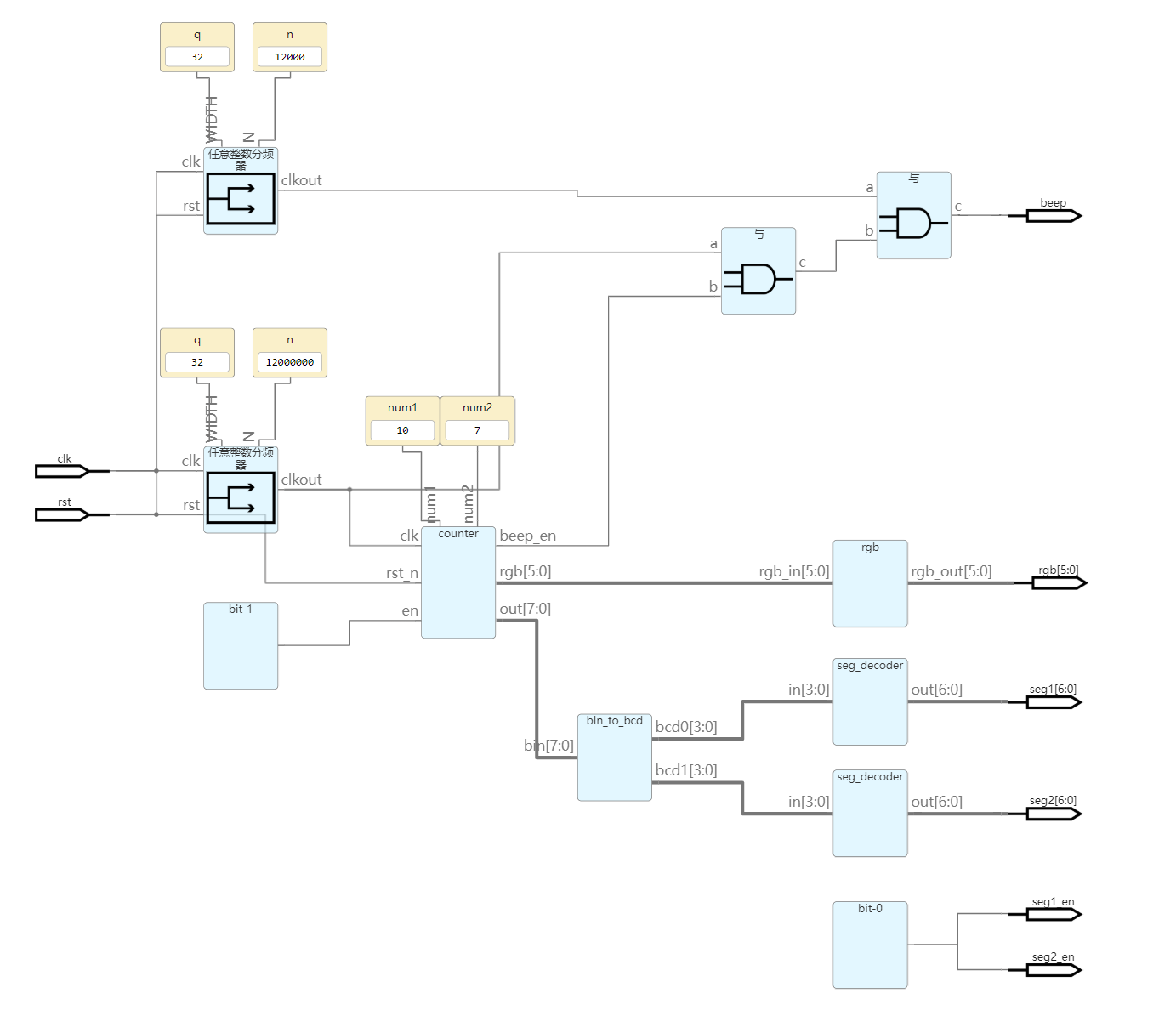

3. 方案框图和设计思路

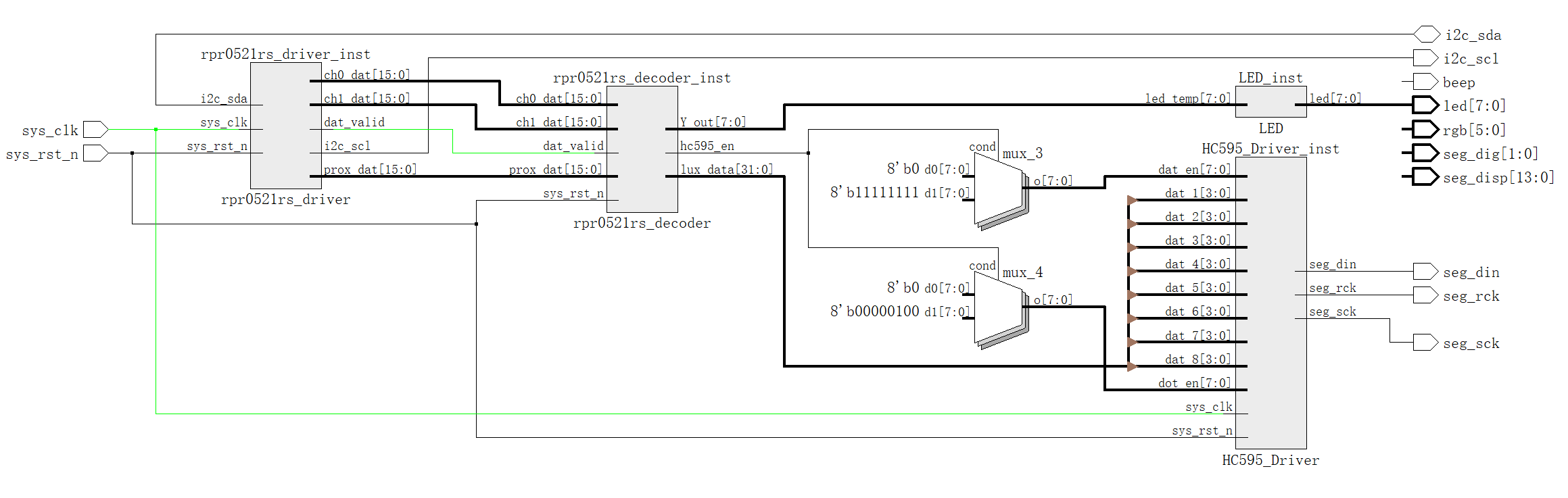

3.1 任务1、2(使用webide)

3.1.1 方案框图

3.1.2 设计思路

- 生成一个频率为1s的clkout信号,连接到counter模块,以此来进行剩余时间的计数。

- 在counter模块中设计采用有限状态自动机(Finite State Machine, FSM)来控制整个过程,状态包括:红灯状态,绿灯状态和黄灯状态。状态机根据时间控制,实现交通灯的自动切换。图中num1,num2分别代表红灯,绿灯的时长。RGB灯发出对应颜色的光,同时使用bcd模块(bin_to_bcd)+数码管译码器模块(seg_decoder)显示剩余时间。

- 绿灯时使能beep模块,每1s响一次,以1kHz的频率发出声音。

3.1.3 关键代码介绍

counter模块内代码,其中flag作状态机,值为0,1,2分别表示红,绿,黄三种状态。

wire [15:0] num;

reg [7:0] out_temp;

reg [1:0] flag;

reg beep_en_temp;

reg [5:0] rgb_temp;

always @(negedge clk or negedge rst_n) begin

if (rst_n == 1'b0) begin

out_temp <= num1;

rgb_temp <= 6'b100100;

flag <= 2'b00;

beep_en_temp <= 0;

end else if (en)

begin

if (out_temp == 0)begin

if(flag==2'b00) begin //红灯->绿灯

out_temp <= num2;

rgb_temp <= 6'b010010;

flag <= 2'b01;

beep_en_temp <= 1;

end else if(flag==2'b01) begin //绿灯->黄灯

out_temp <= 3;

rgb_temp <= 6'b110110;

flag <= 2'b10;

beep_en_temp <= 0;

end else begin //黄灯->红灯

out_temp <= num1;

rgb_temp <= 6'b100100;

flag <= 2'b00;

beep_en_temp <= 0;

end

end else

out_temp <= out_temp - 8'b1;

end

else

out_temp <= out_temp;

end

assign out = out_temp;

assign rgb = rgb_temp;

assign beep_en = beep_en_temp;

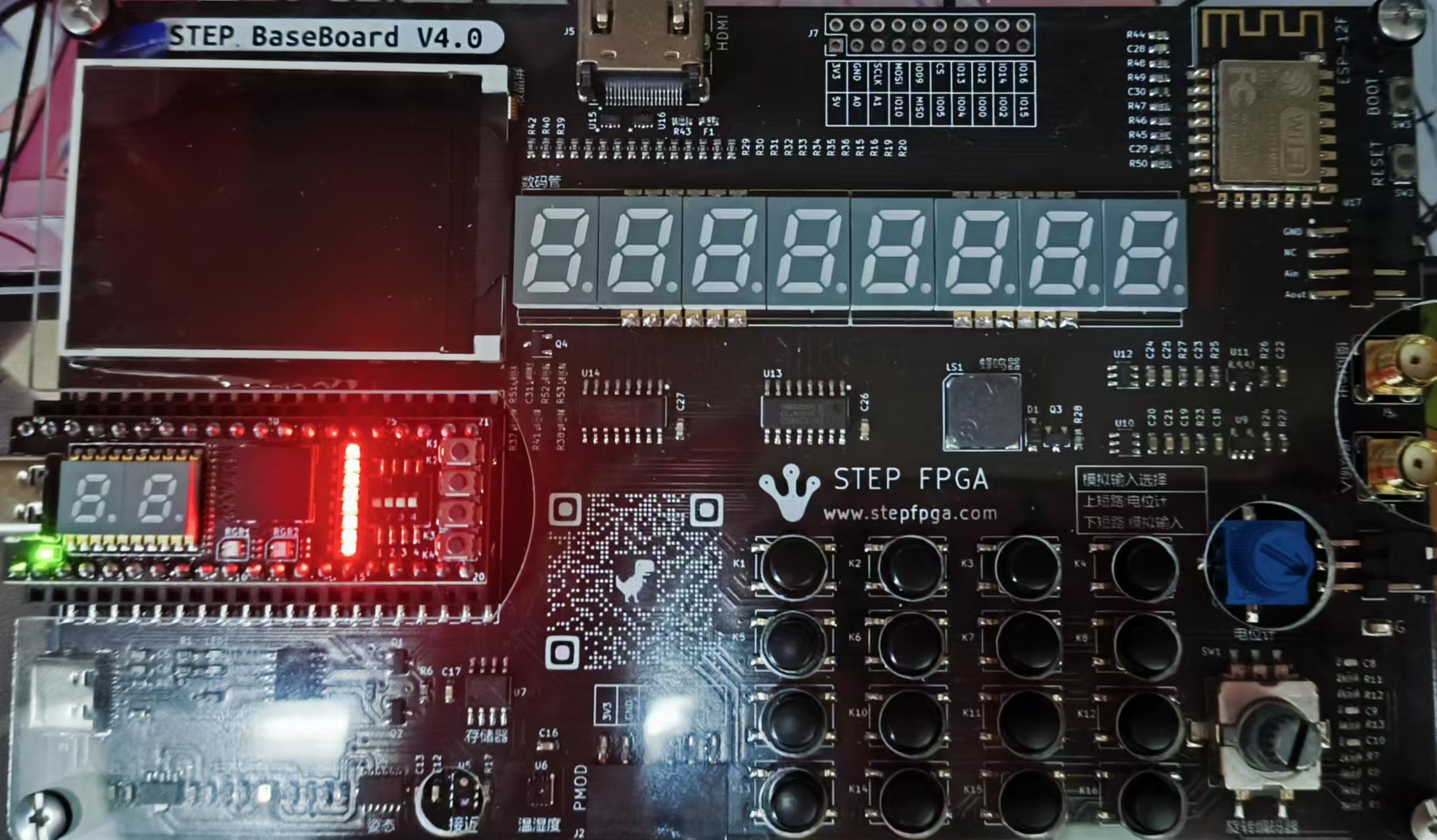

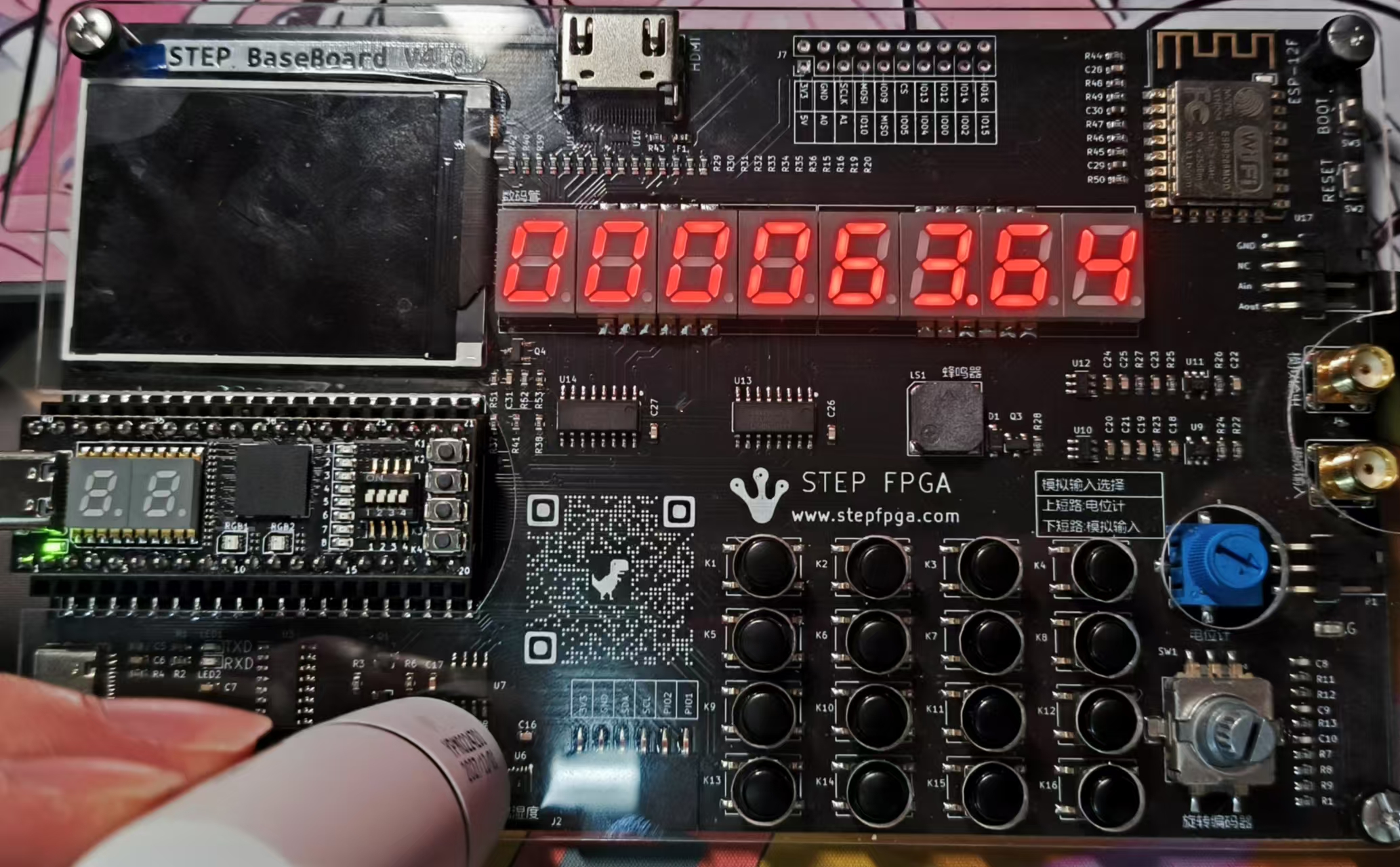

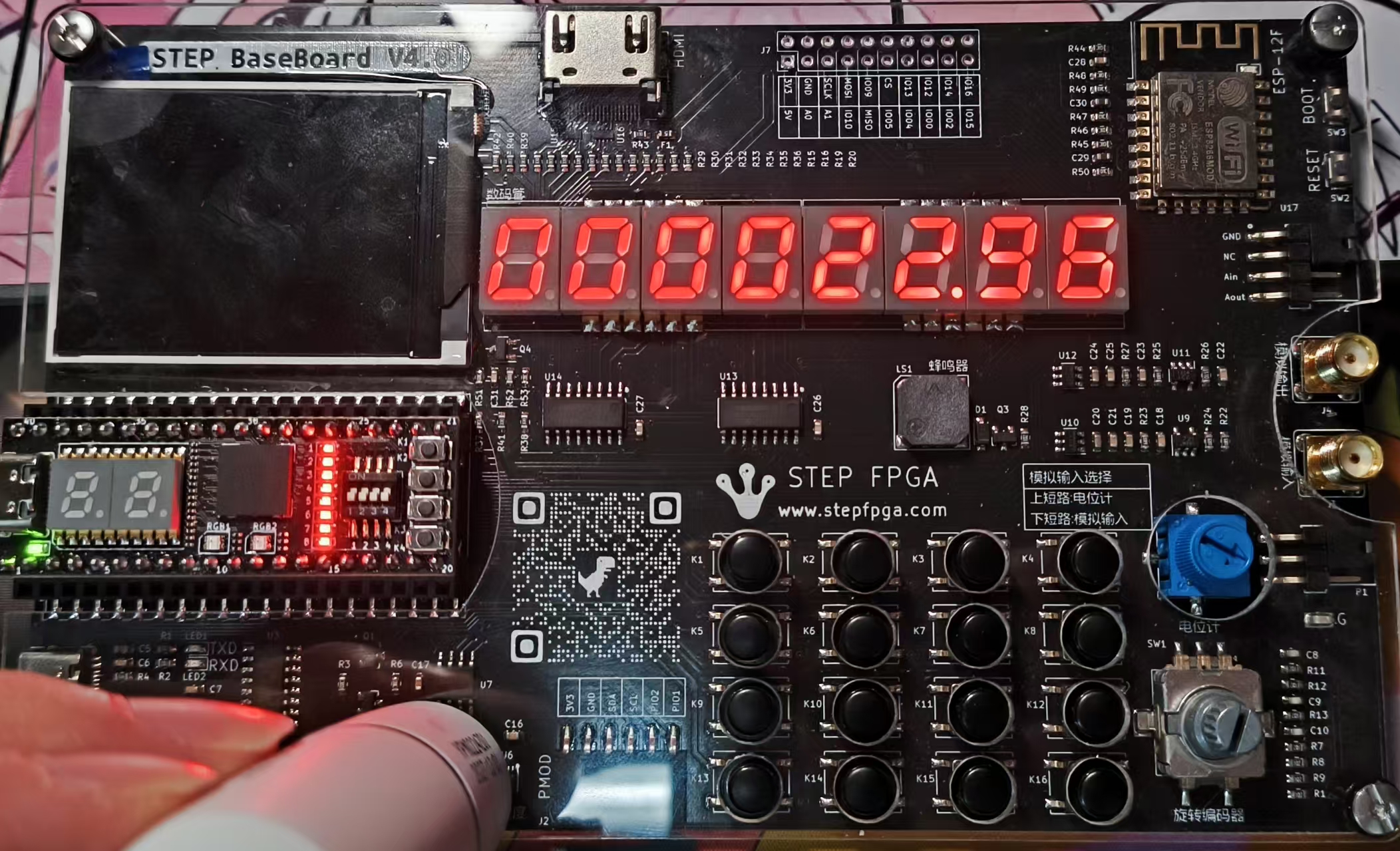

3.1.4 功能展示

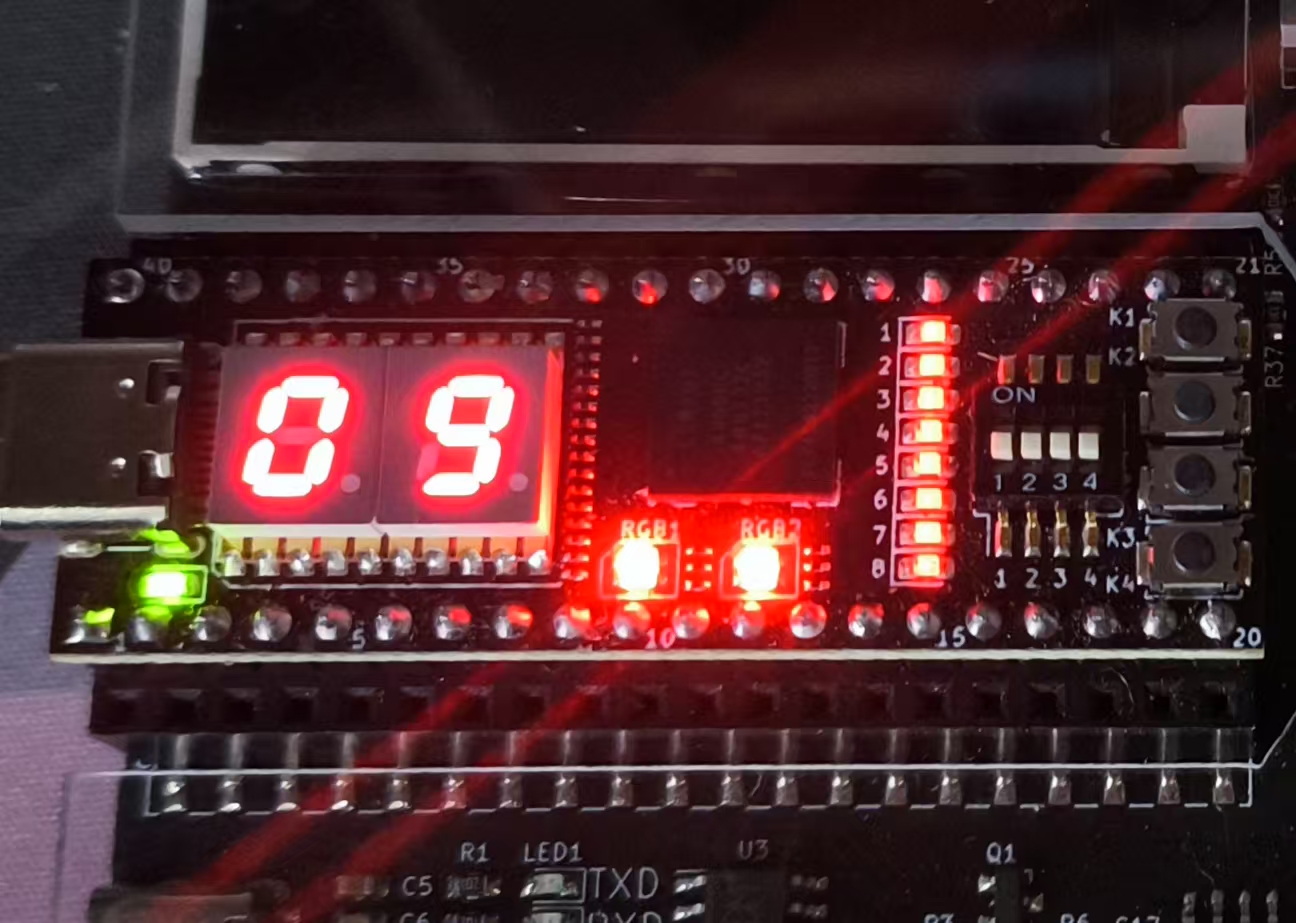

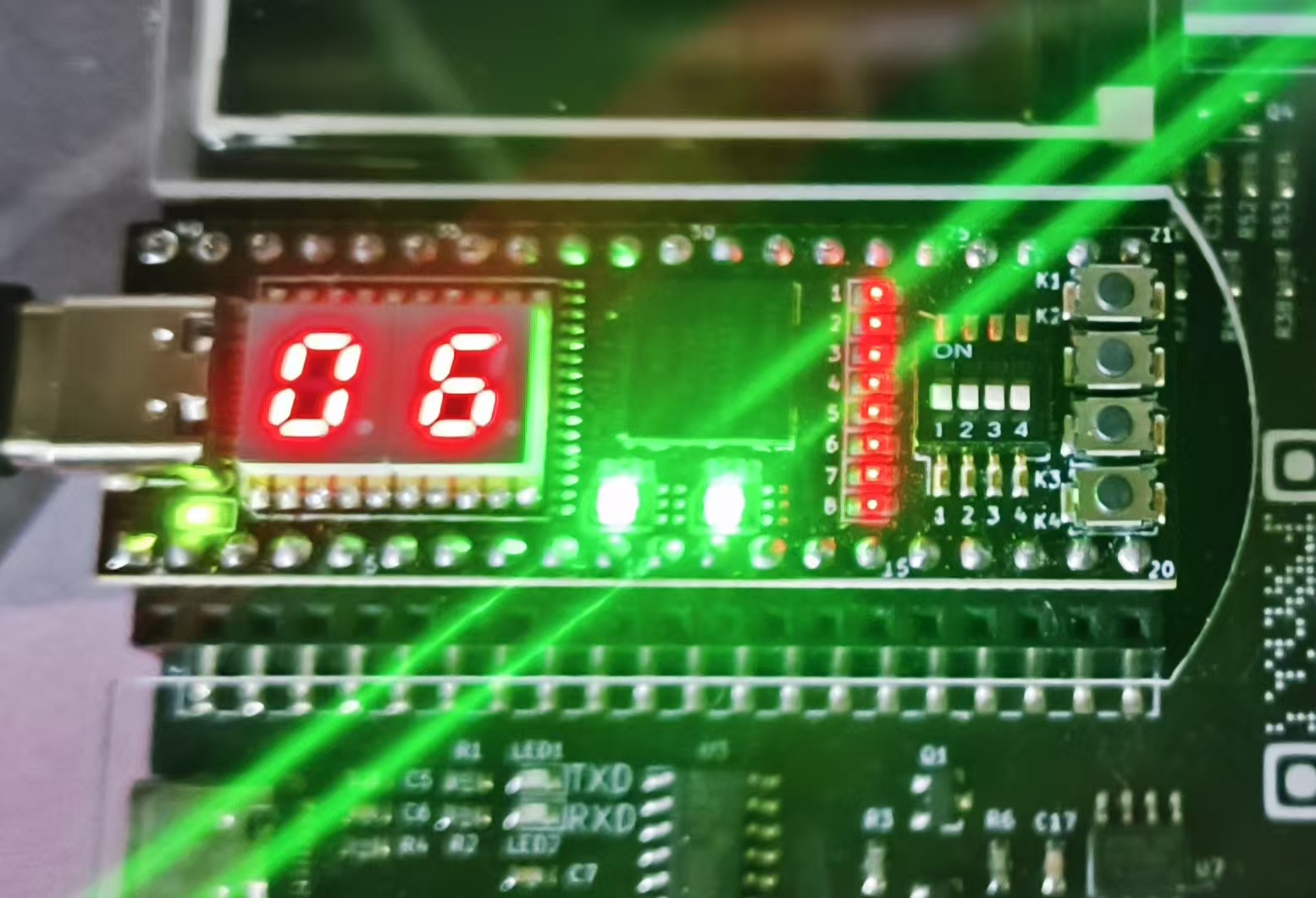

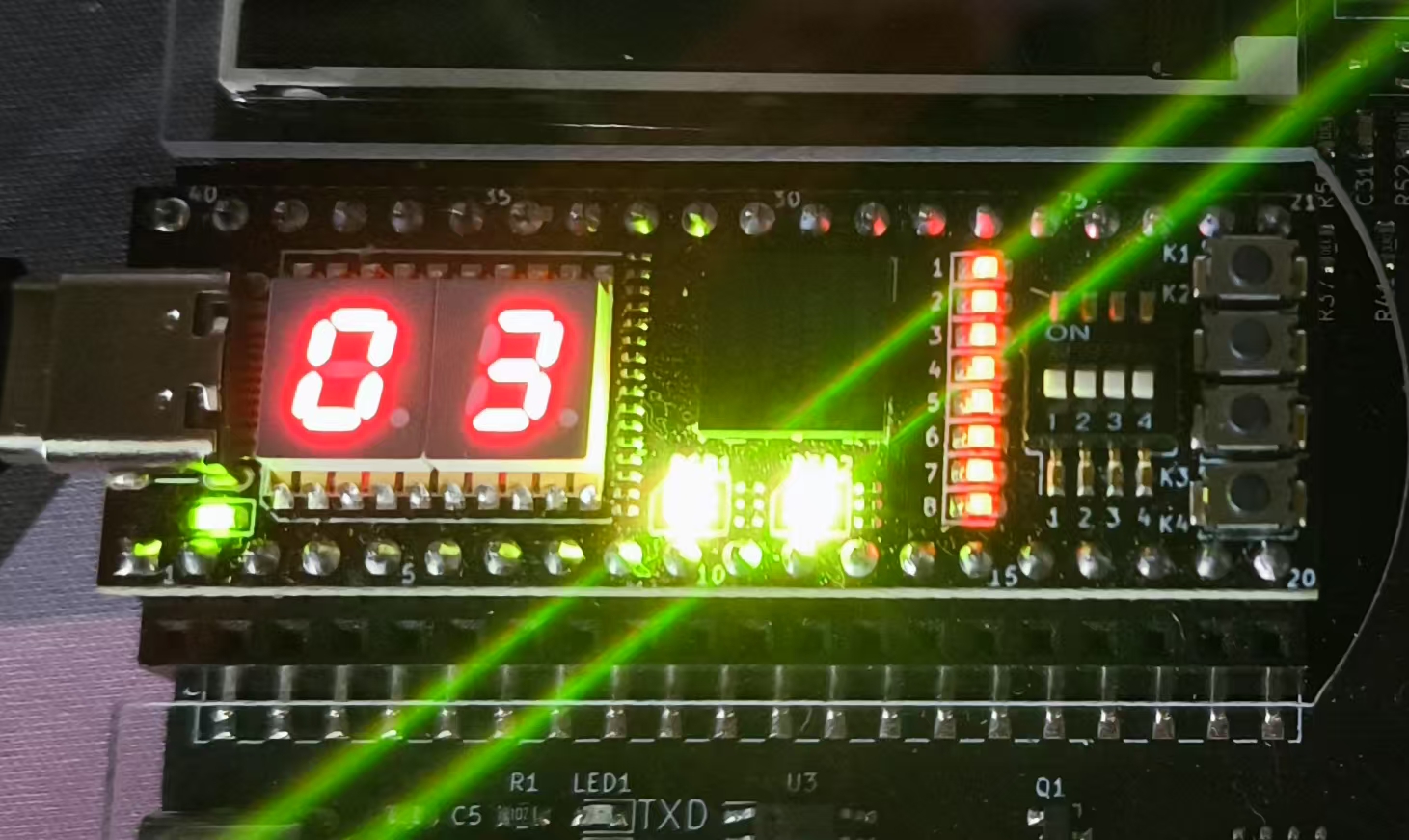

红灯 | 绿灯 | 黄灯 |

|---|---|---|

| | |

3.1.5 资源占用

Design Summary:

Number of registers: 78 out of 4635 (2%)

PFU registers: 78 out of 4320 (2%)

PIO registers: 0 out of 315 (0%)

Number of SLICEs: 108 out of 2160 (5%)

SLICEs as Logic/ROM: 108 out of 2160 (5%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 66 out of 2160 (3%)

Number of LUT4s: 215 out of 4320 (5%)

Number used as logic LUTs: 83

Number used as distributed RAM: 0

Number used as ripple logic: 132

Number used as shift registers: 0

Number of PIO sites used: 25 + 4(JTAG) out of 105 (28%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

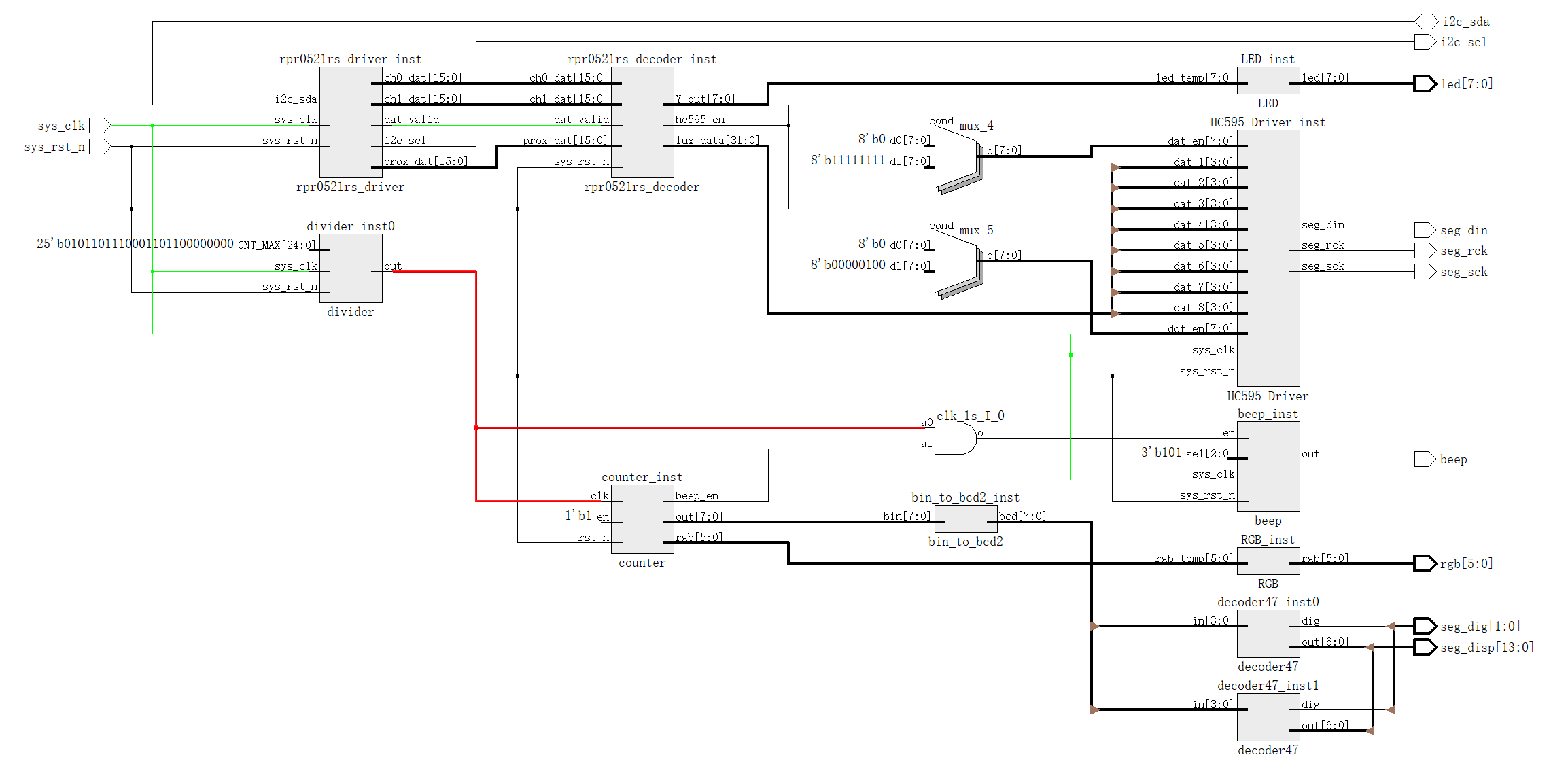

3.2 任务3、4(使用diamond)

源码见附件/source_2,项目见附件/project2.ldf

3.2.1 方案框图

3.2.2 设计思路

基于官方驱动距离和光照传感器的例程,修改使其适应任务要求:

- 在decoder模块(rpr0521rs_decoder)中,新增hc595_en端口,根据距离控制数码管亮灭。

- 修改Y_out输出逻辑,当光照强度小于30lux时,使所有LED点亮。

3.2.3 关键代码介绍

//rpr0521rs_decoder.v

always@(prox_dat2[11:9]) begin

if (prox_dat2[11:9]<3'b010) begin //

hc595_en <= 1'b0;

end else begin //

hc595_en <= 1'b1;

end

end

always @(lux) begin

if (lux >= 32'd30000) begin

Y_out <= 8'h00;

end else begin

Y_out <= 8'hff;

end

end

//project_top_module.v

HC595_Driver HC595_Driver_inst(

// 连接系统时钟信号

.sys_clk (sys_clk ),

// 连接系统复位信号

.sys_rst_n (sys_rst_n ),

// 连接光照数据的第31-28位

.dat_1 (lux_data[31:28] ),

// 连接光照数据的第27-24位

.dat_2 (lux_data[27:24] ),

// 连接光照数据的第23-20位

.dat_3 (lux_data[23:20] ),

// 连接光照数据的第19-16位

.dat_4 (lux_data[19:16] ),

// 连接光照数据的第15-12位

.dat_5 (lux_data[15:12] ),

// 连接光照数据的第11-8位

.dat_6 (lux_data[11:08] ),

// 连接光照数据的第7-4位

.dat_7 (lux_data[07:04] ),

// 连接光照数据的第3-0位

.dat_8 (lux_data[03:00] ),

// 根据HC595使能信号决定数据使能

.dat_en (hc595_en ? 8'b1111_1111 : 8'b0000_0000),

.dot_en (hc595_en ? 8'b0000_0100 : 8'b0000_0000),

.seg_rck (seg_rck ),

.seg_sck (seg_sck ),

.seg_din (seg_din )

);

3.2.4 功能展示

距离远 光照强 | 距离远 光照弱 |

|---|---|

| |

距离近 光照强 | 距离近 光照弱 |

| |

3.2.5 资源占用

Design Summary:

Number of registers: 328 out of 4635 (7%)

PFU registers: 323 out of 4320 (7%)

PIO registers: 5 out of 315 (2%)

Number of SLICEs: 1288 out of 2160 (60%)

SLICEs as Logic/ROM: 1288 out of 2160 (60%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 475 out of 2160 (22%)

Number of LUT4s: 2574 out of 4320 (60%)

Number used as logic LUTs: 1624

Number used as distributed RAM: 0

Number used as ripple logic: 950

Number used as shift registers: 0

Number of PIO sites used: 38 + 4(JTAG) out of 105 (40%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

3.3 总系统的实验(整合四个任务)

源码见附件/source_total,项目见附件/project_total.ldf

3.3.1 方案框图

线路说明:

- 绿线为系统时钟(12MHz),divider模块为分频器,产生1Hz的信号(即红线)。

3.3.2 资源占用

Design Summary:

Number of registers: 406 out of 4635 (9%)

PFU registers: 401 out of 4320 (9%)

PIO registers: 5 out of 315 (2%)

Number of SLICEs: 1381 out of 2160 (64%)

SLICEs as Logic/ROM: 1381 out of 2160 (64%)

SLICEs as RAM: 0 out of 1620 (0%)

SLICEs as Carry: 534 out of 2160 (25%)

Number of LUT4s: 2756 out of 4320 (64%)

Number used as logic LUTs: 1688

Number used as distributed RAM: 0

Number used as ripple logic: 1068

Number used as shift registers: 0

Number of PIO sites used: 38 + 4(JTAG) out of 105 (40%)

Number of block RAMs: 0 out of 10 (0%)

Number of GSRs: 1 out of 1 (100%)

4. 难题与解决方法

Verilog代码复杂

- 解决方法:采用模块化设计,将系统分解为独立的小型功能单元(如倒计时counter、传感器驱动等),降低代码复杂性,使得调试和维护更加容易。

5. 项目完成情况

- 功能实现

系统均完成了核心功能:灯光开关闭合,时间与光照值显示以及报警音输出。数码管可实时显示剩余时间和光照强度,蜂鸣器在绿灯状态下发出每秒一次的提示音。 - 系统稳定性

通过多次实验验证系统运行稳定,能够满足实际应用场景中的实时性需求。

6. 心得与展望

通过本项目,我入门了fpga的数字逻辑世界。参与此次项目让我掌握了Verilog编码、硬件电路设计等技能,为下学期的数电实验课程打下了良好的基础。

软硬件

附件下载

project.zip

团队介绍

仅本人

评论

0 / 100

查看更多

猜你喜欢

2025寒假练 - 基于小脚丫FPGA实现交通灯控制系统该项目使用了小脚丫FPGA STEP BaseBoard V4.0套件,实现了交通灯控制系统的设计,它的主要功能为:红绿灯切换,环境亮度检测,环境较暗时开灯,接近时亮灯报警,蜂鸣器催促通过。

FuShenxiao

510

2025寒假练-基于小脚丫FPGA实现交通灯控制系统该项目使用了基于Lattice MXO2的小脚丫FPGA核心板,实现了交通灯控制系统的设计,它的主要功能为:在数码管上显示计时信息、蜂鸣器报警、接近检测和环境光感知。。

lbbxy

403

2025寒假练-基于小脚丫FPGA实现交通灯控制系统该项目使用了小脚丫FPGA,实现了交通灯控制系统的设计,它的主要功能为:实现了交通灯控制系统红绿黄灯的基础变化,在数码管上显示计时信息,在黄灯时蜂鸣器报警,同时接近传感器检测人员走近,走近时蜂鸣器以2s间隔报警且音调随距离的增近而增大,且八位数码管上实现数值大小。环境光感知,自动点亮路灯,越暗,八个led小红灯实现流水灯亮。。

Hipon123

279