Hackaday上的项目汇总-自制CPU的相关项目

收藏

分享

脑图

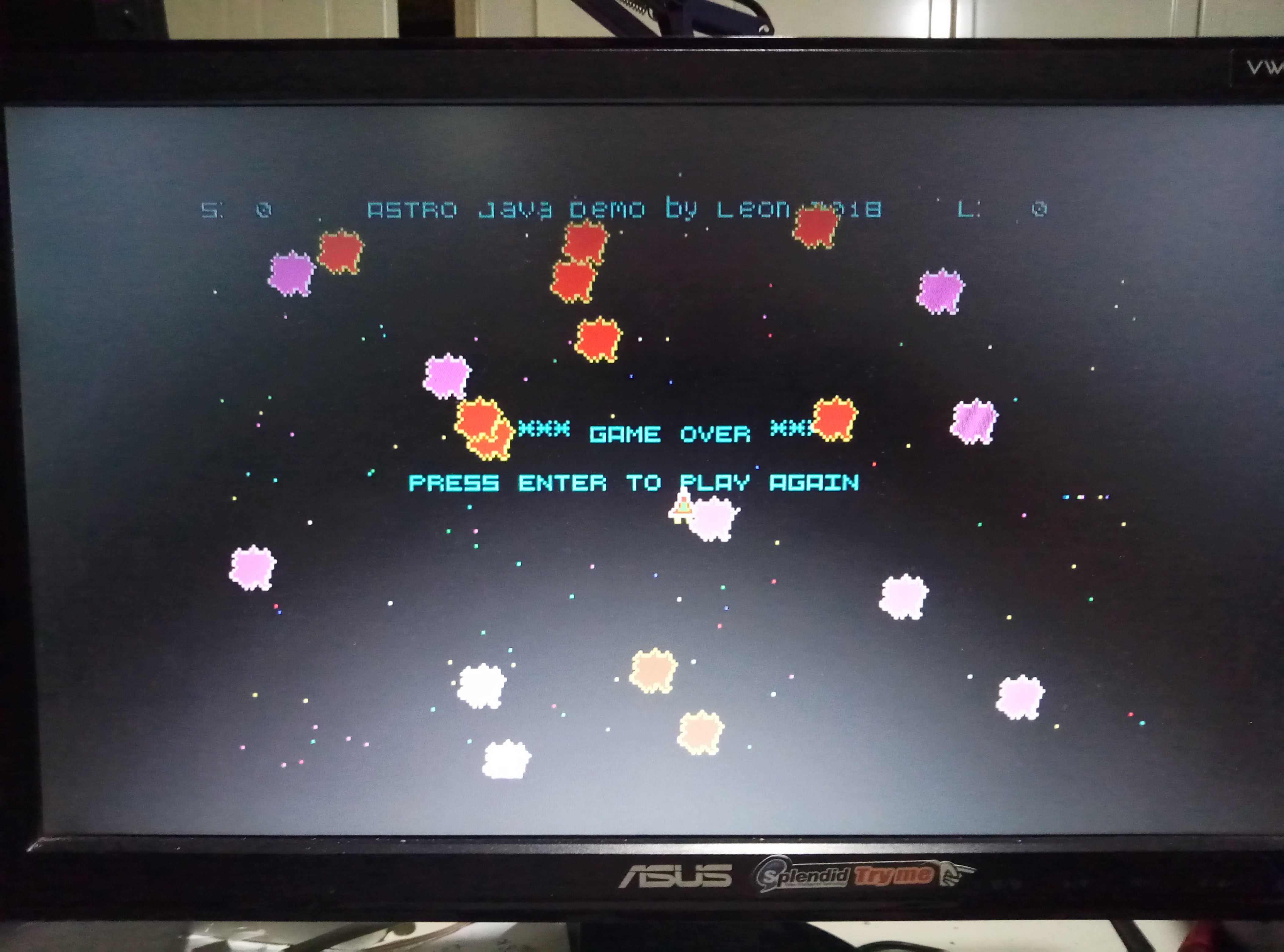

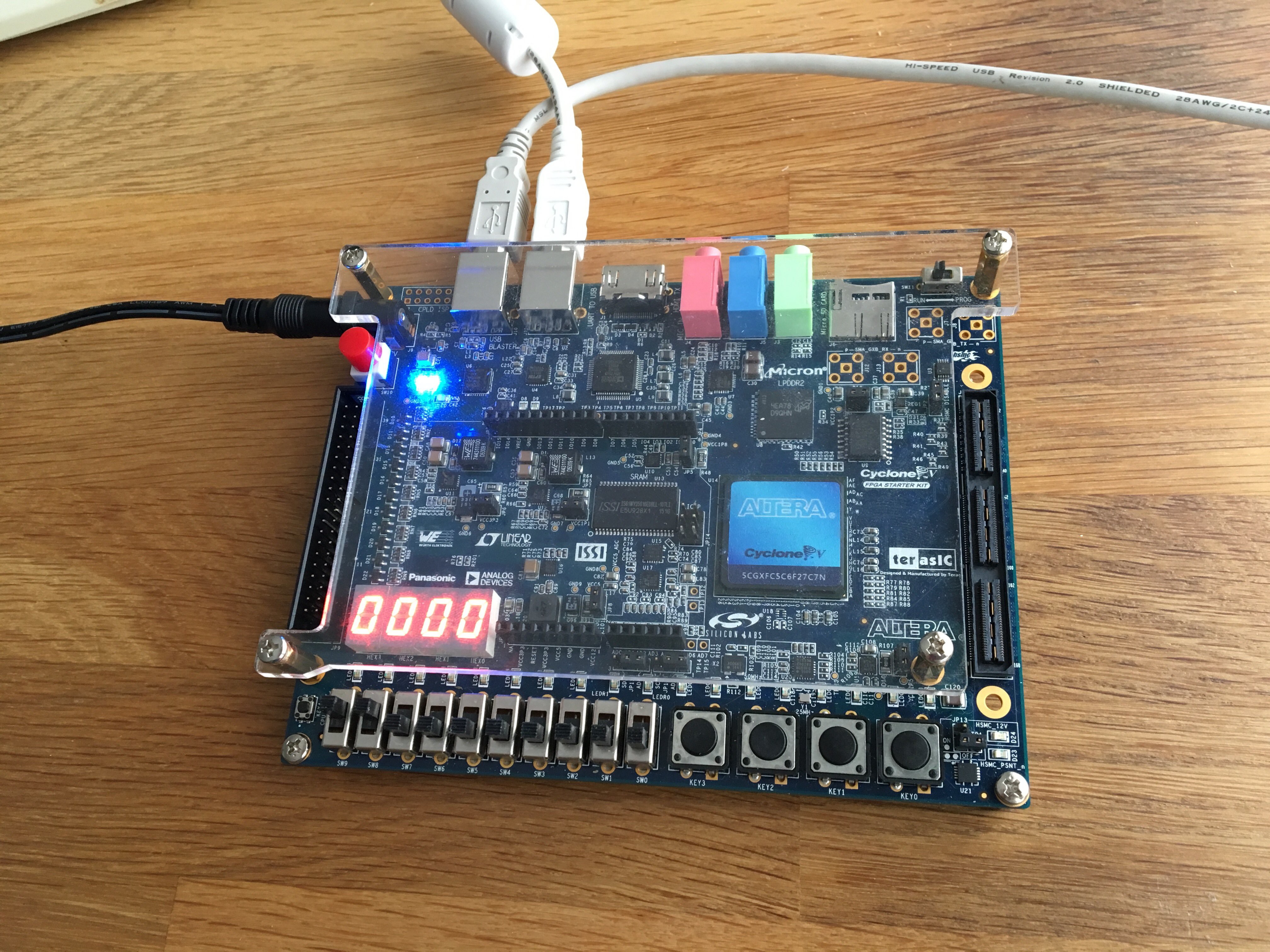

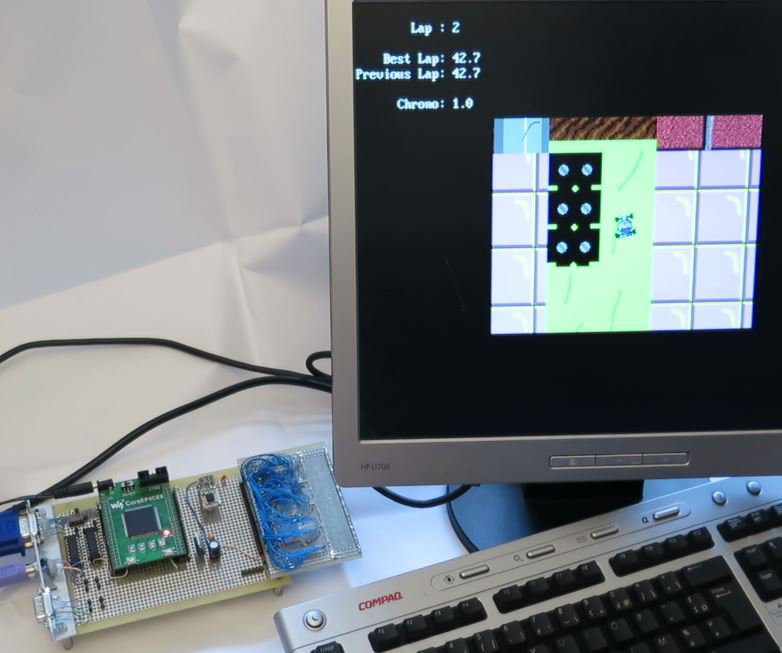

描述:我开始探索FPGA并制造了一个CPU,然后当我意识到它确实有效时,我设定了一个目标,就像我小时候用的80年代的家用电脑一样,我想我做到了。我构建了一个视频控制器,一个UART,编写了一个汇编程序并移植了PA Tiny Basic添加了固定点等等。 它开始感觉像家用电脑。 我添加了SPI以使用SD卡并编写了简单的FAT系统支持。 对于声音,我制作了两个音频通道和一个噪声通道。

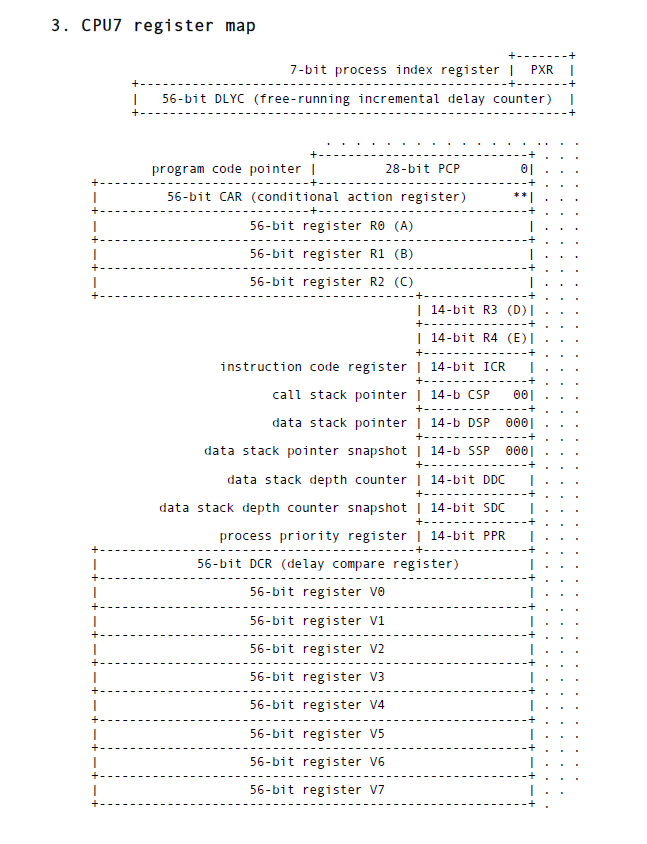

描述:一个长期项目,可在FPGA中运行,但仅作为阵列模拟。 努力进一步推进核心。

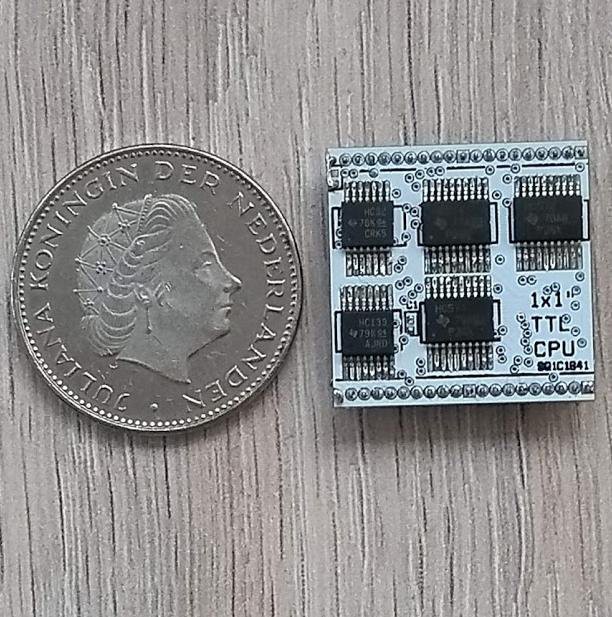

描述:采用TTL芯片构建的微处理器。 在一平方英寸。

描述:灵感来自https://hackaday.io/project/25091-one-page-computing-challenge,以及有很多4位CPU和大量8位CPU的事实,但6位的非常罕见。

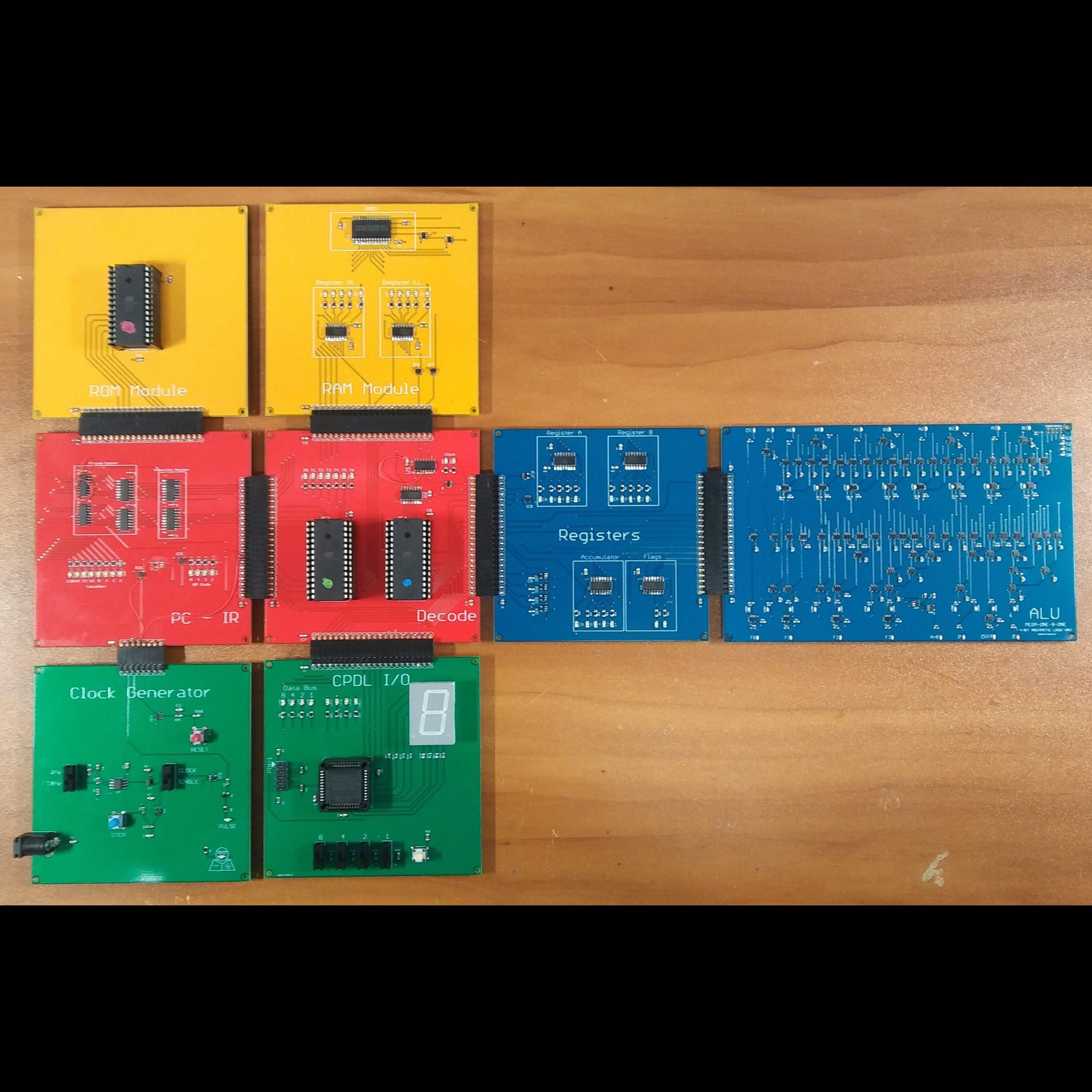

描述:该项目旨在创建一个模块化的bitlice风格的4位CPU,可用于实际应用,也可作为计算机体系结构教育的平台。

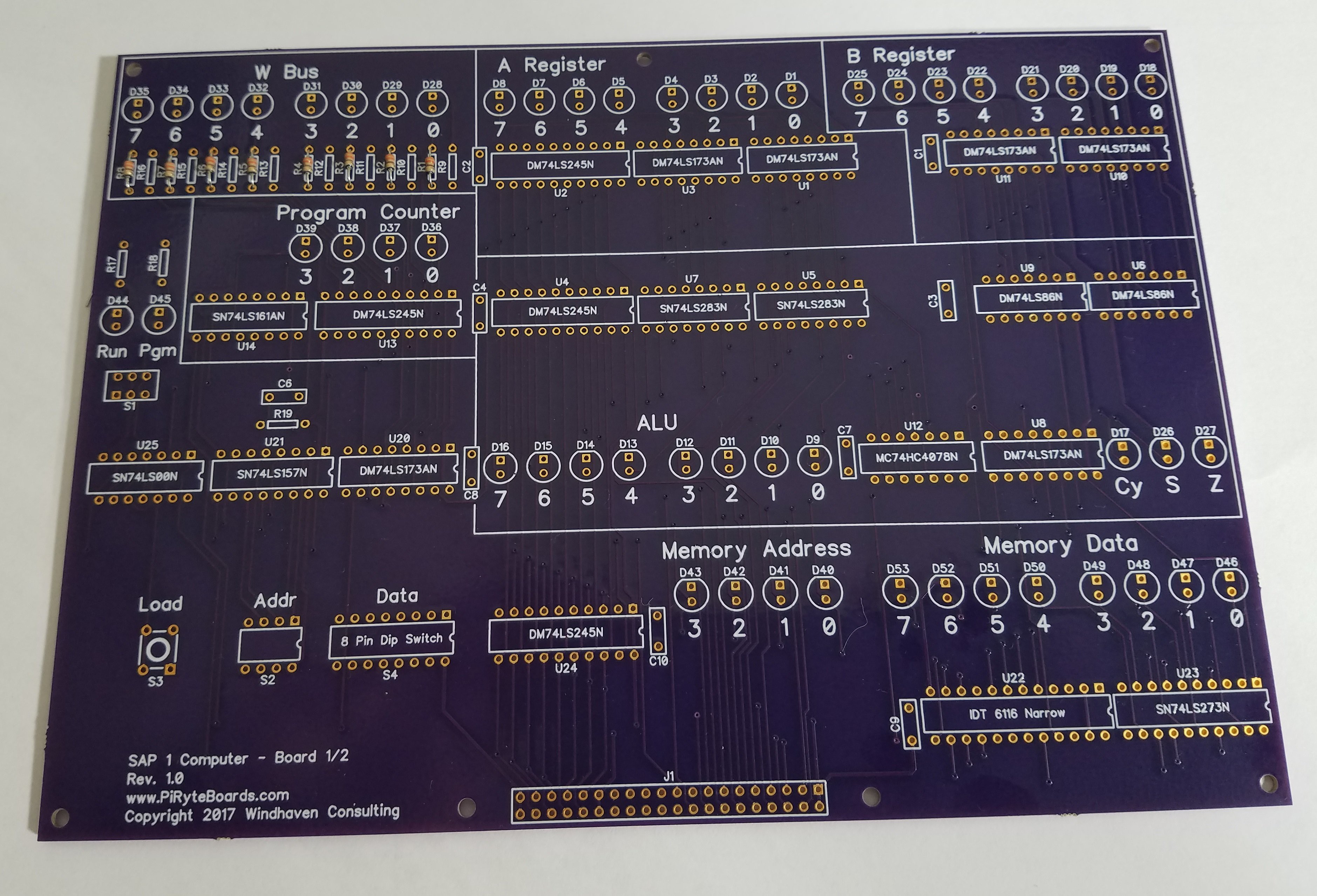

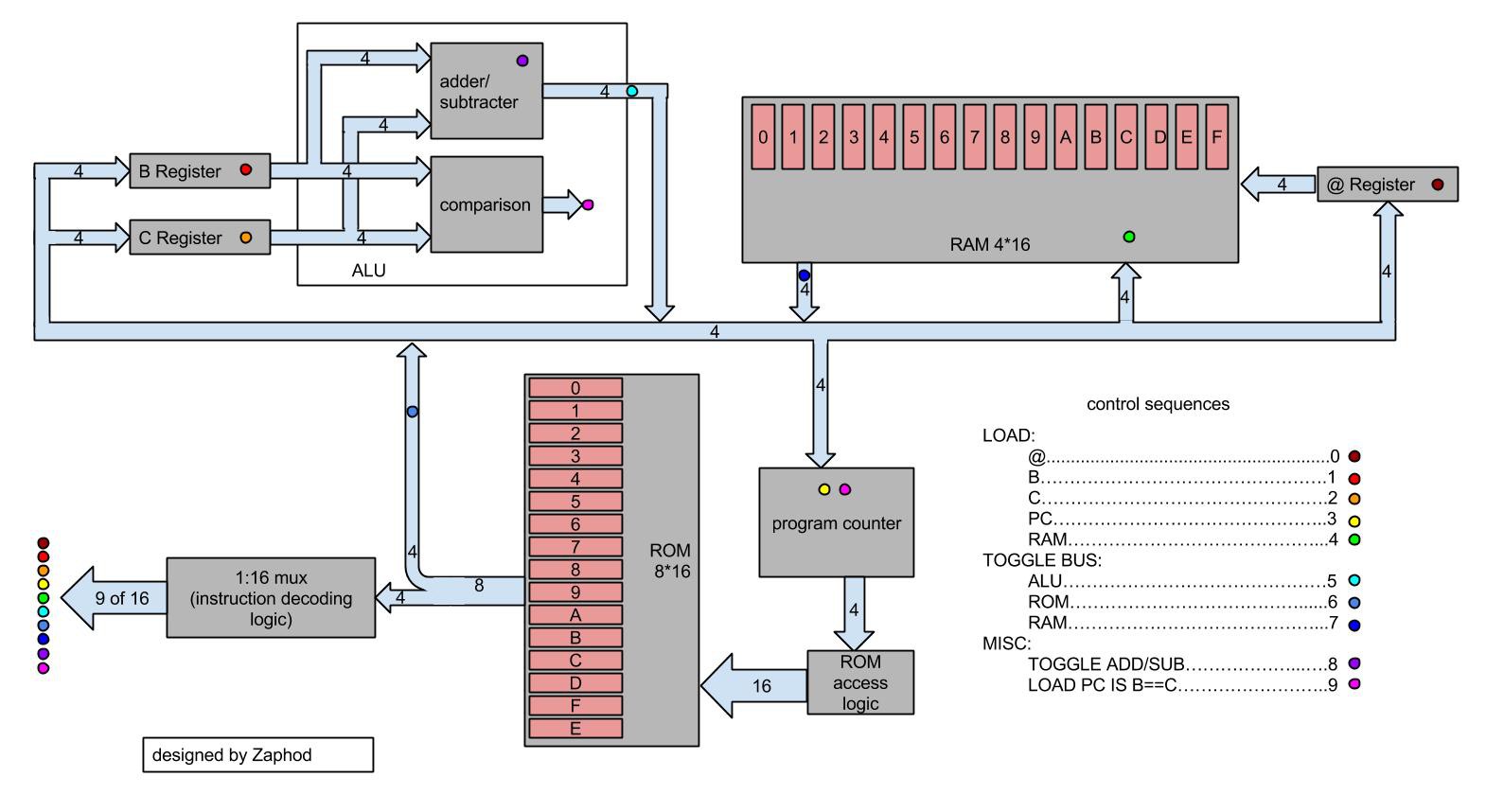

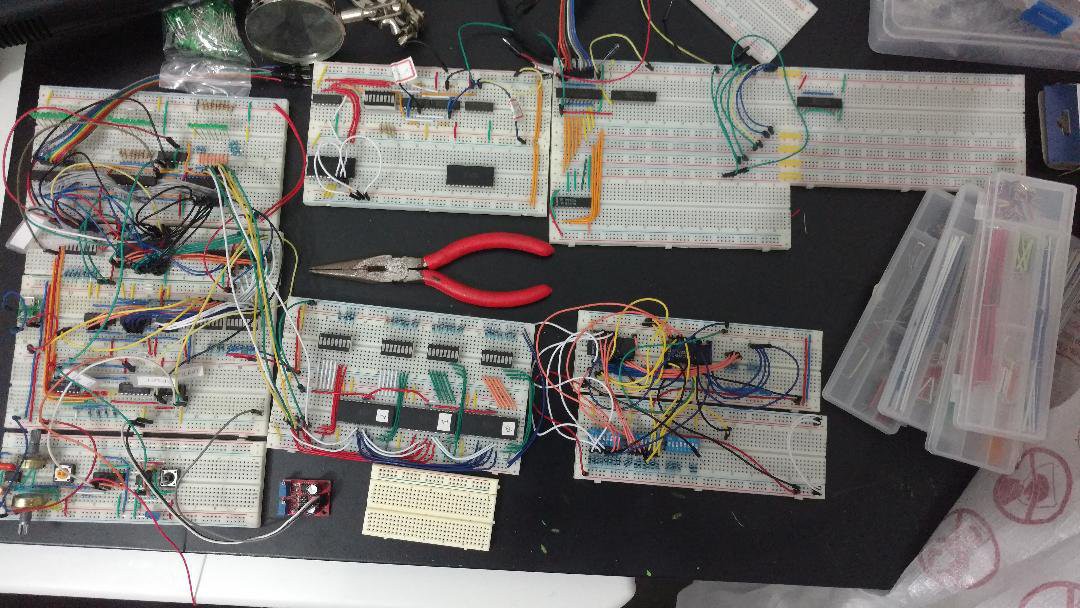

描述:SAP 1计算机实际上是一台“尽可能简单”的计算机,带有两个寄存器,ALU,存储器地址寄存器,指令寄存器,程序计数器和用于数据和指令的16字节存储器。 这台计算机,我希望这个项目能够很好地展示几乎所有微处理器中从最早开始到今天的数字电子学的一些基本原理。

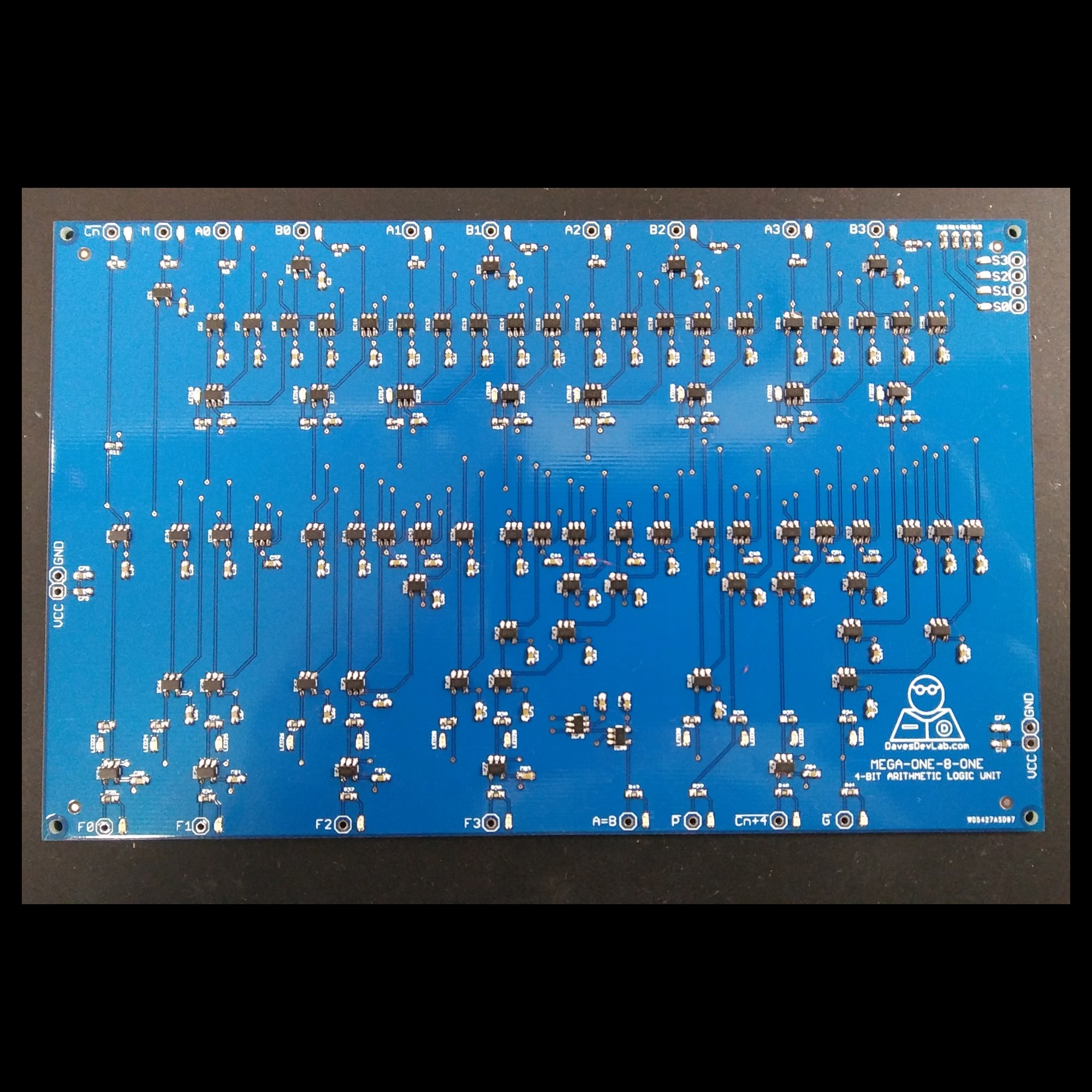

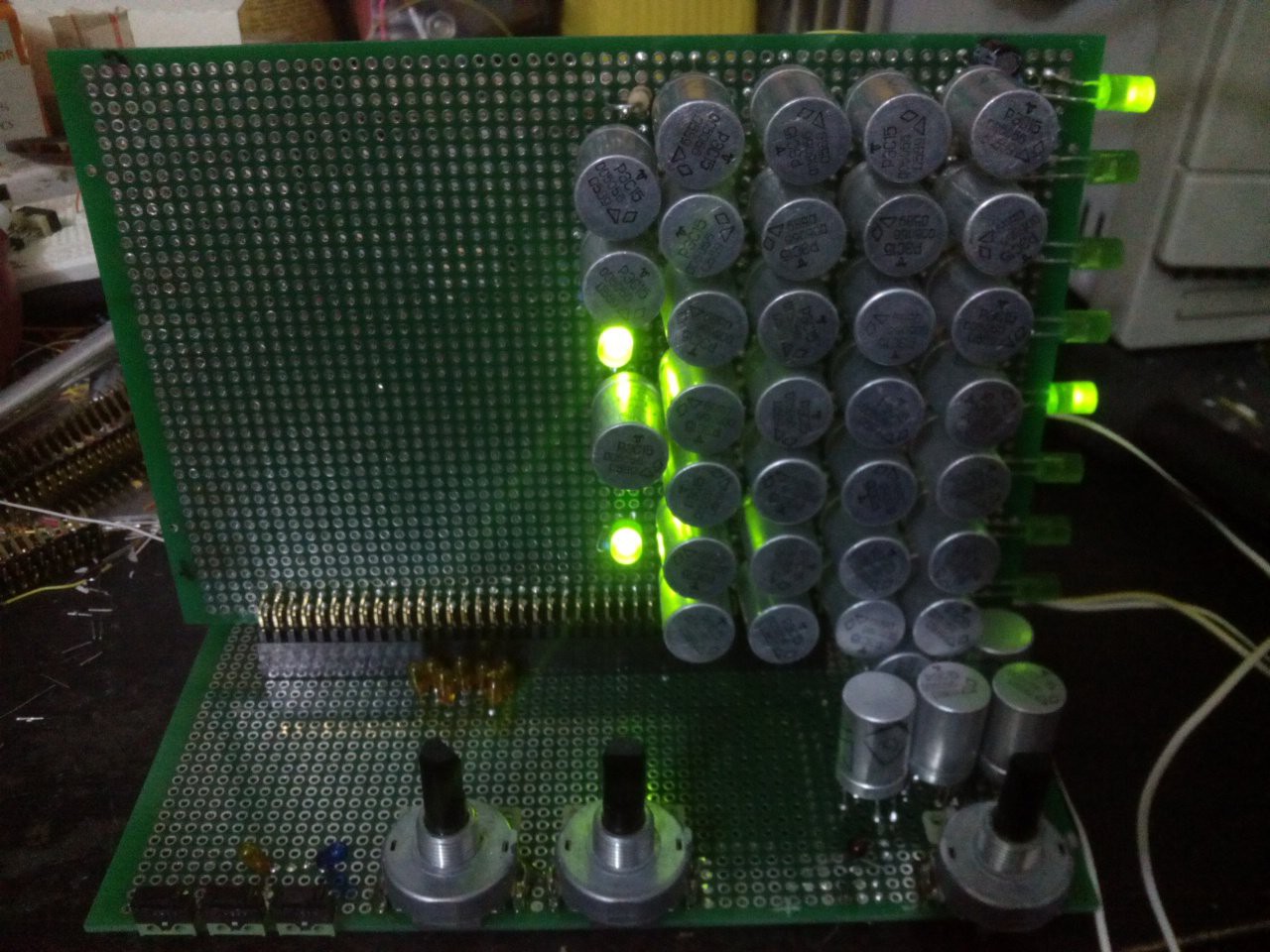

描述:该项目旨在创建一个逻辑块精确复制经典74181 ALU。 设计的每个部分都使用单独的逻辑门以及添加的LED,以便基本了解74181的实现方式。 该设计采用基于74LVC的器件,支持+ 3.3V和+ 5V工作。

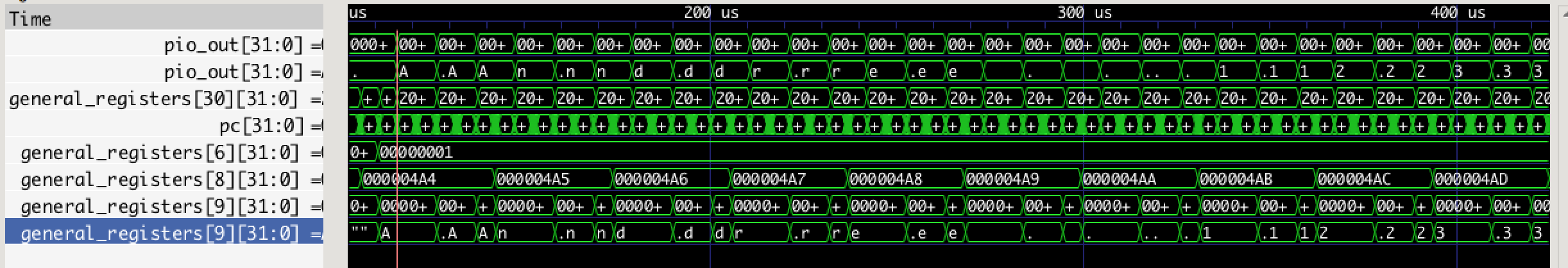

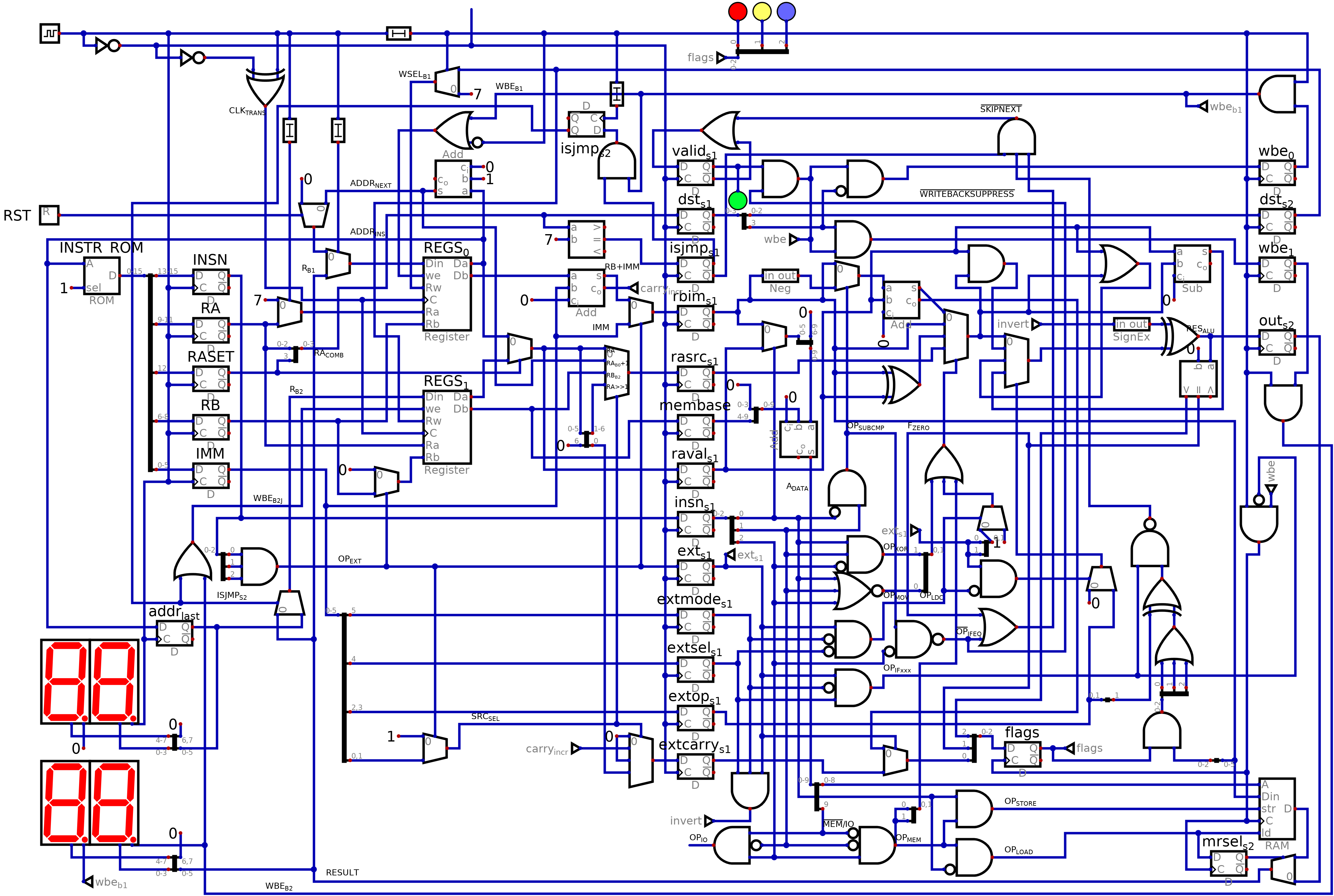

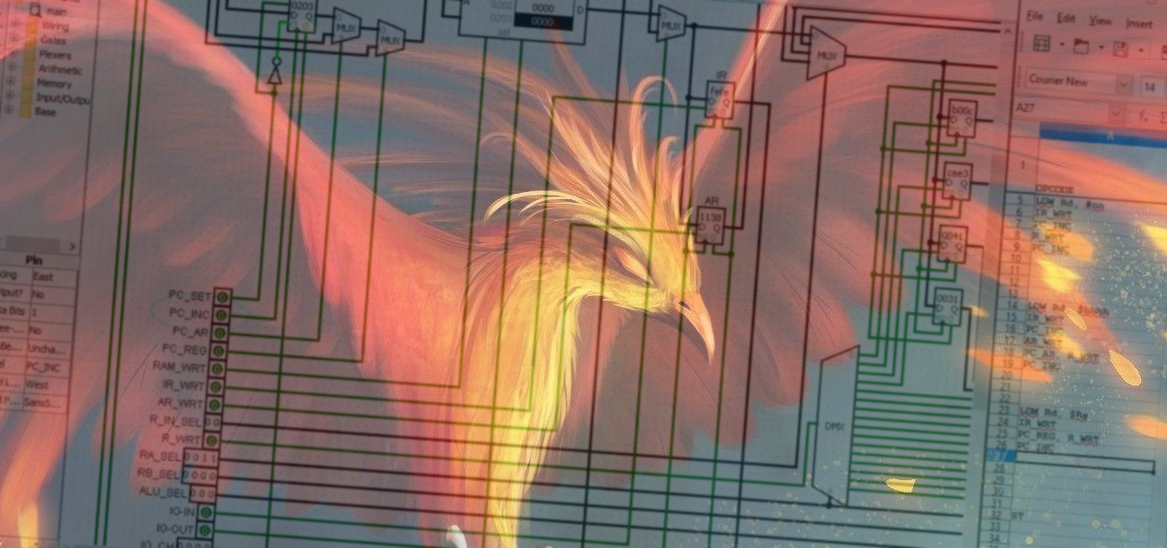

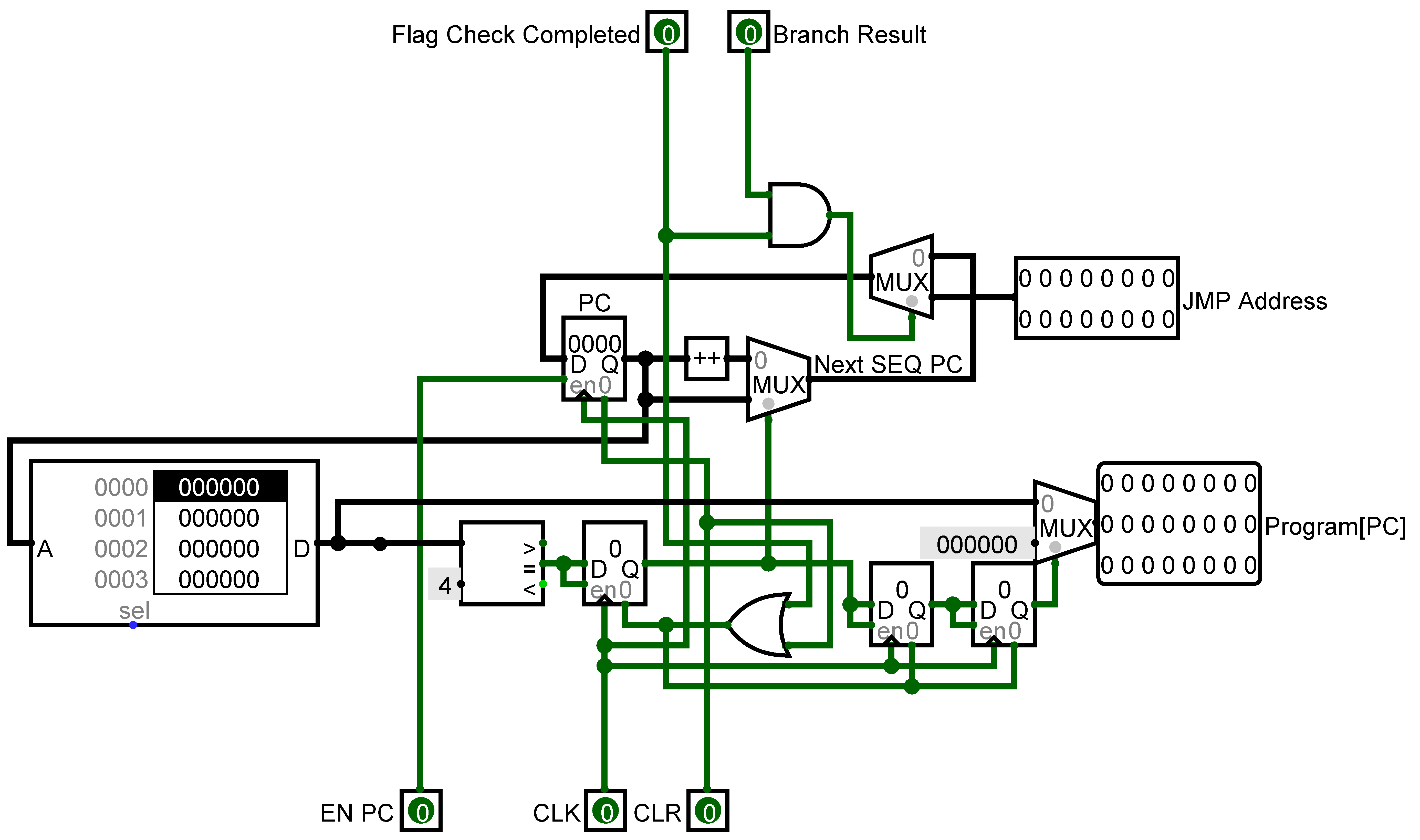

描述:基于8位计算机的旧(废弃)项目,这是一个在Logisim中创建的16位CPU。

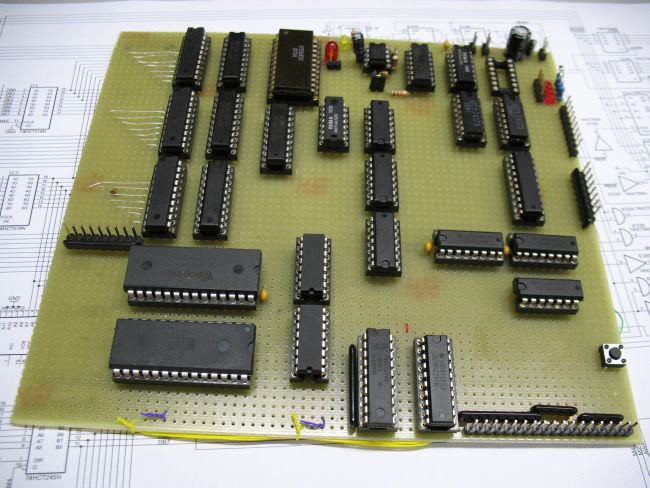

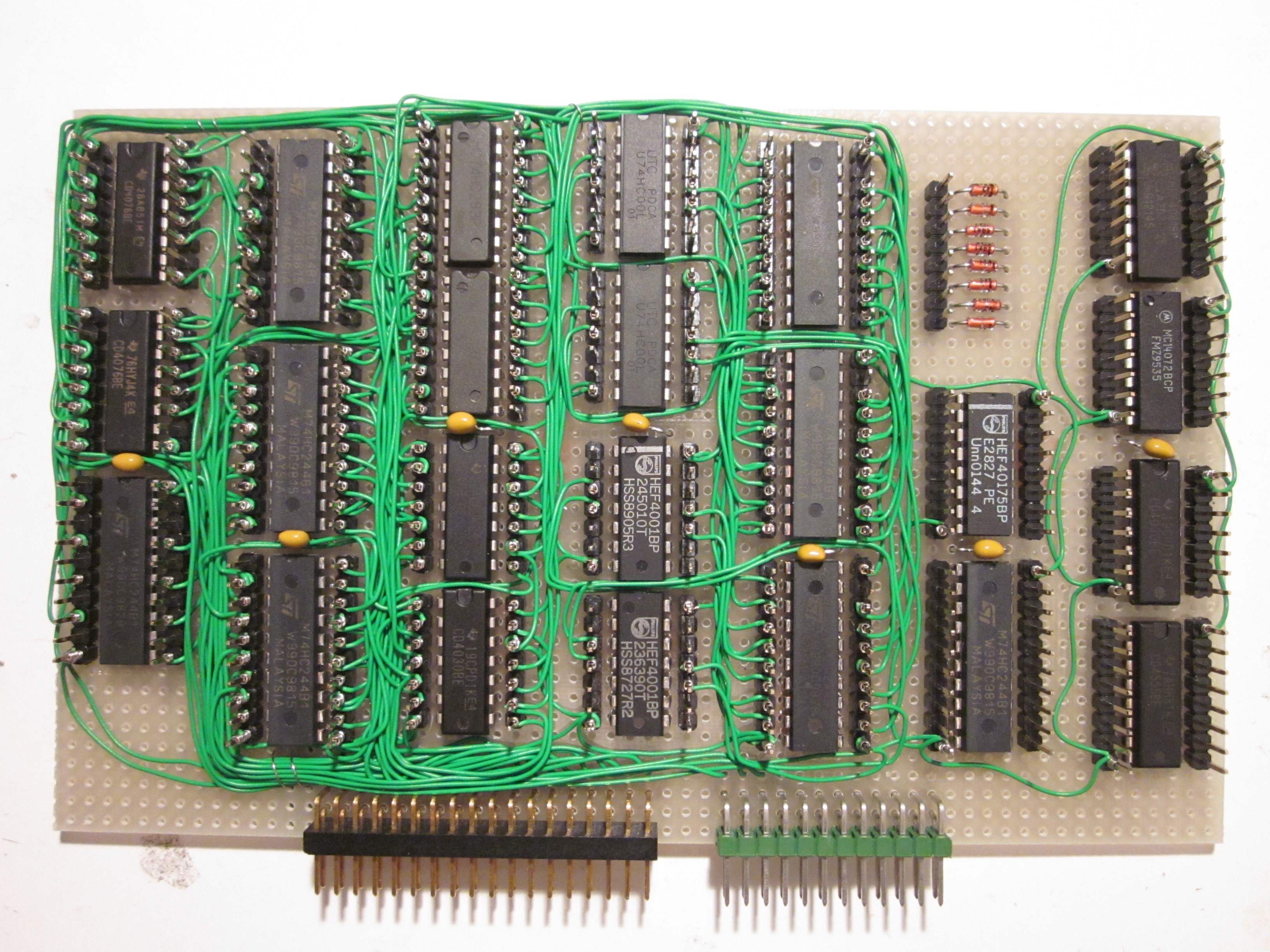

描述:使用74xx(TTL)逻辑芯片从头开始设计和构建我自己的8位计算机。

描述:欢迎来到关于MARK-II项目的页面! MARK-II是一个爱好项目。 它是简单的片上系统(SoC),具有用VHDL编写的自定义CPU和外设。 SoC可与配备MAX10 FPGA的定制FPGA板合成。 在C中还有用于编程MARK-II的全功能工具链。整个项目在MIT许可下分发,除了一些小部件(vbcc前端,文档(CC下许可))。 并且可以在我的github repo免费获得。

描述:DME CPU是一个在FPGA中实现的16位处理器。 用户和管理员模式,分页和中断相当完整。 它目前可以访问512kb的总内存(FPGA板上的SRAM数量)。 每个进程最多有64kb的寻址,分为32页(2K)。

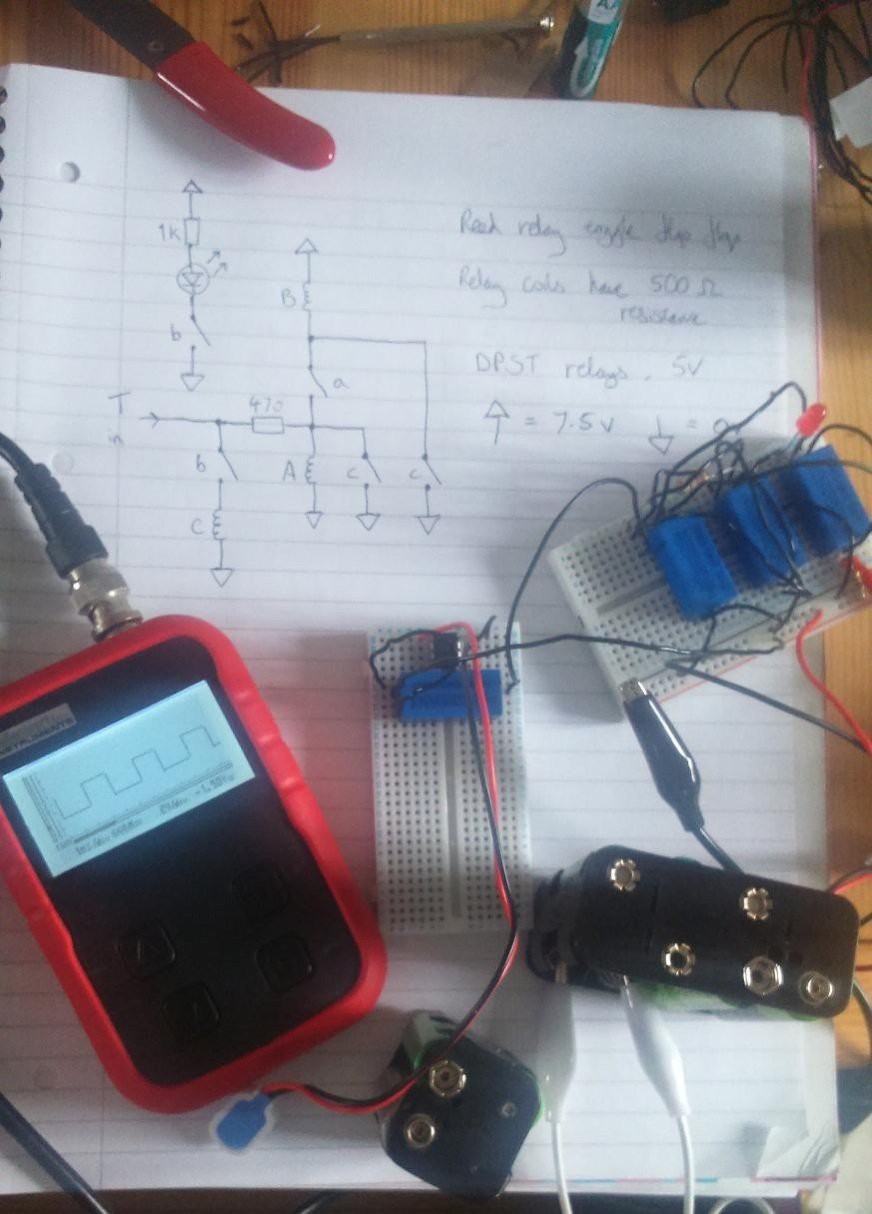

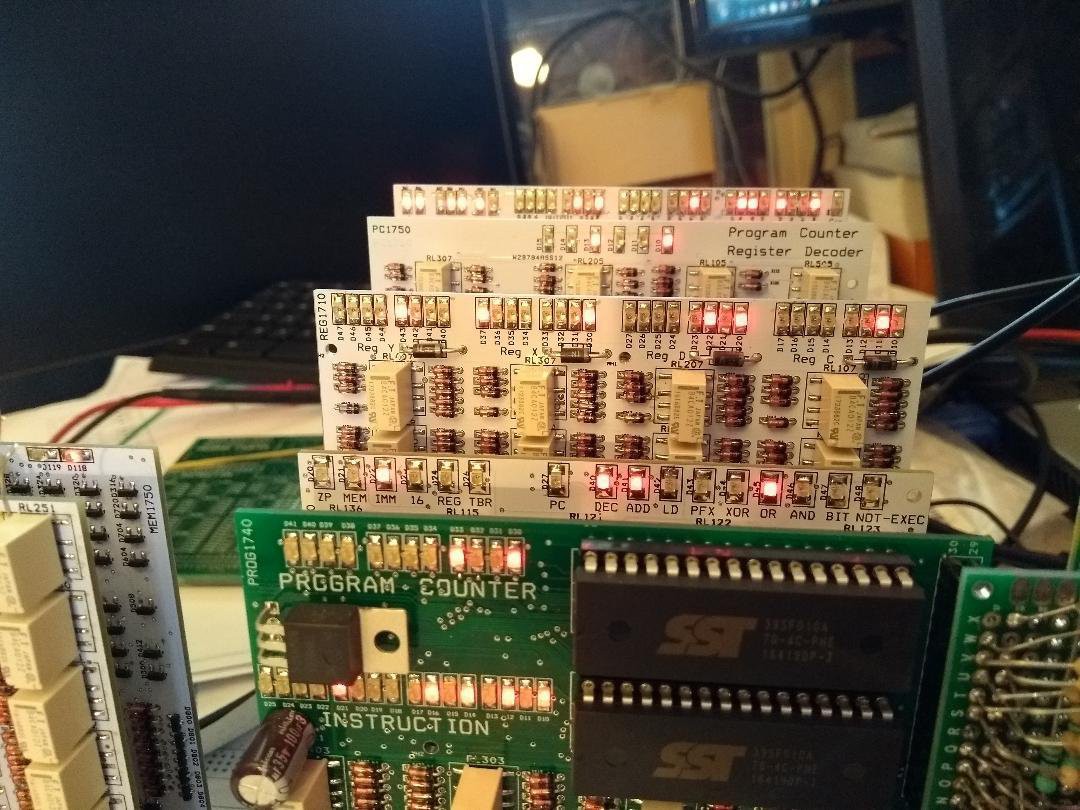

描述:AMBAP项目(https://hackaday.io/project/14628-ambap-a-modest-bitslice-architecture-proposal)在建筑探索和低级原型设计方面分歧太大。“AMBAP”是一个已被证明富有成效的拟议比特式架构的名称。 现在,我已经为继电器实现找到了一个合适的名称,所以现在是时候把它自己分成一个项目了。

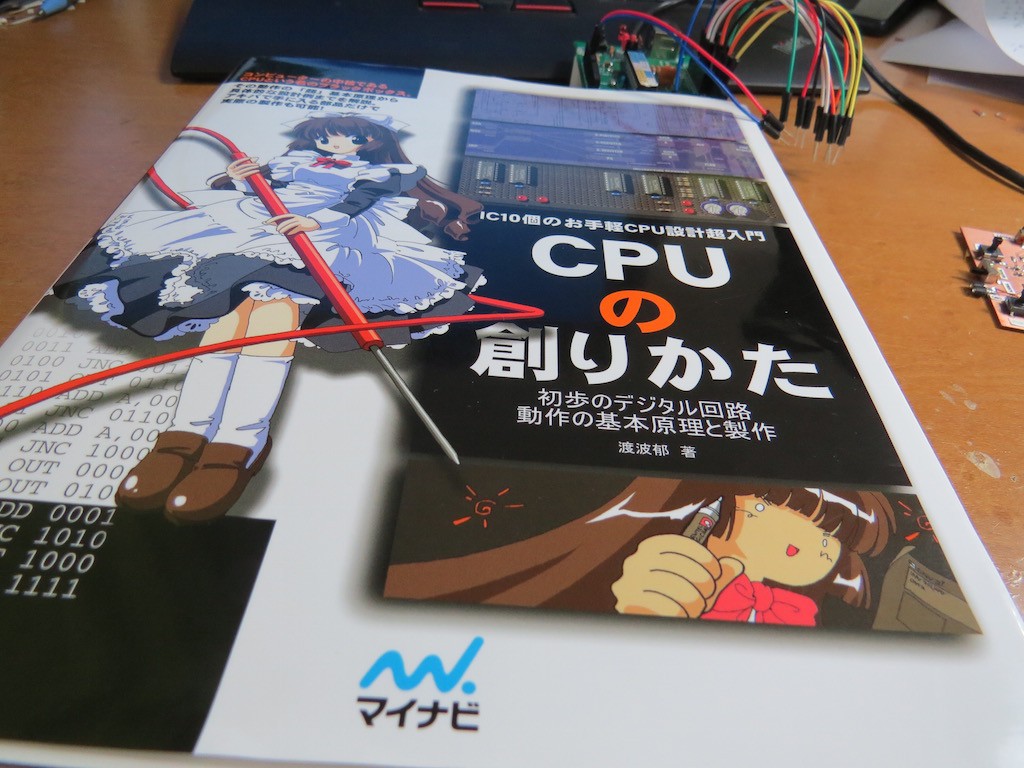

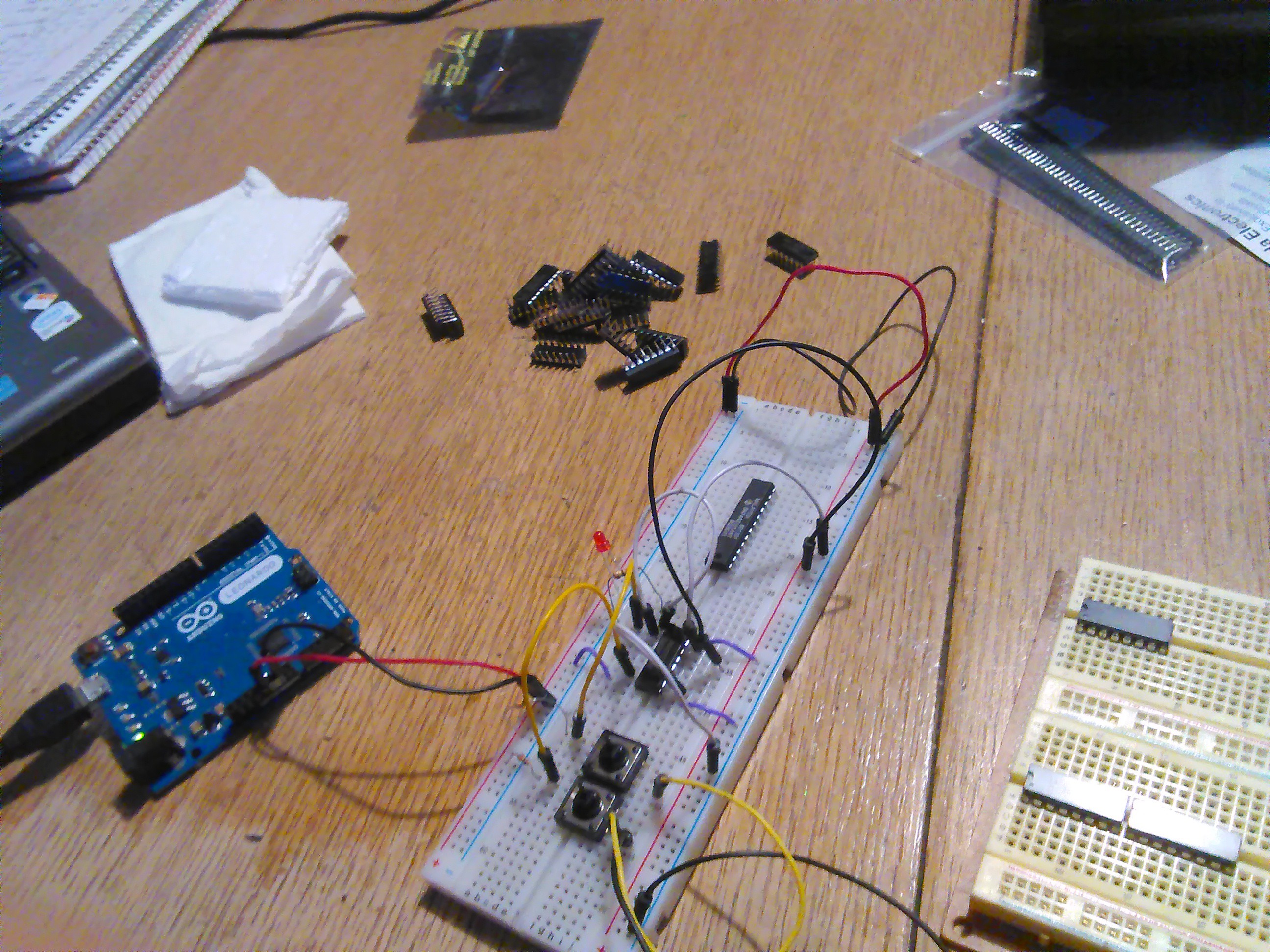

描述:我想从根本上理解并制作简单的CPU。 这次我找到了一本非常好的日本书,表示如何通过TTL从头开始制作CPU并制作电路。 在本书中,存储程序的ROM由一堆DIP开关和二极管组成,我避免使用它,而且ROM部分由Arduino模拟...

描述:这个电路是一个示范/吸引力,说明一个世纪前计算机的起点和方式。 我想为孩子们建立一个,以激发他们的好奇心,并安全地玩数字化的想法。这不是一台真正的计算机,而是一个玩具计算器,需要两个16位操作数(二进制/十六进制,让我们教育!)并执行加/减/乘/除“旧方式”(就像ENIAC仍然是一个东西)。

描述:该项目涉及使用单掷(ST)常开继电器进行计算。 该项目的最初目的是收集有关ST计算电路的想法,并展示小例子的工作原型。 最后,我希望使用自制继电器或干簧继电器制作ST继电器。

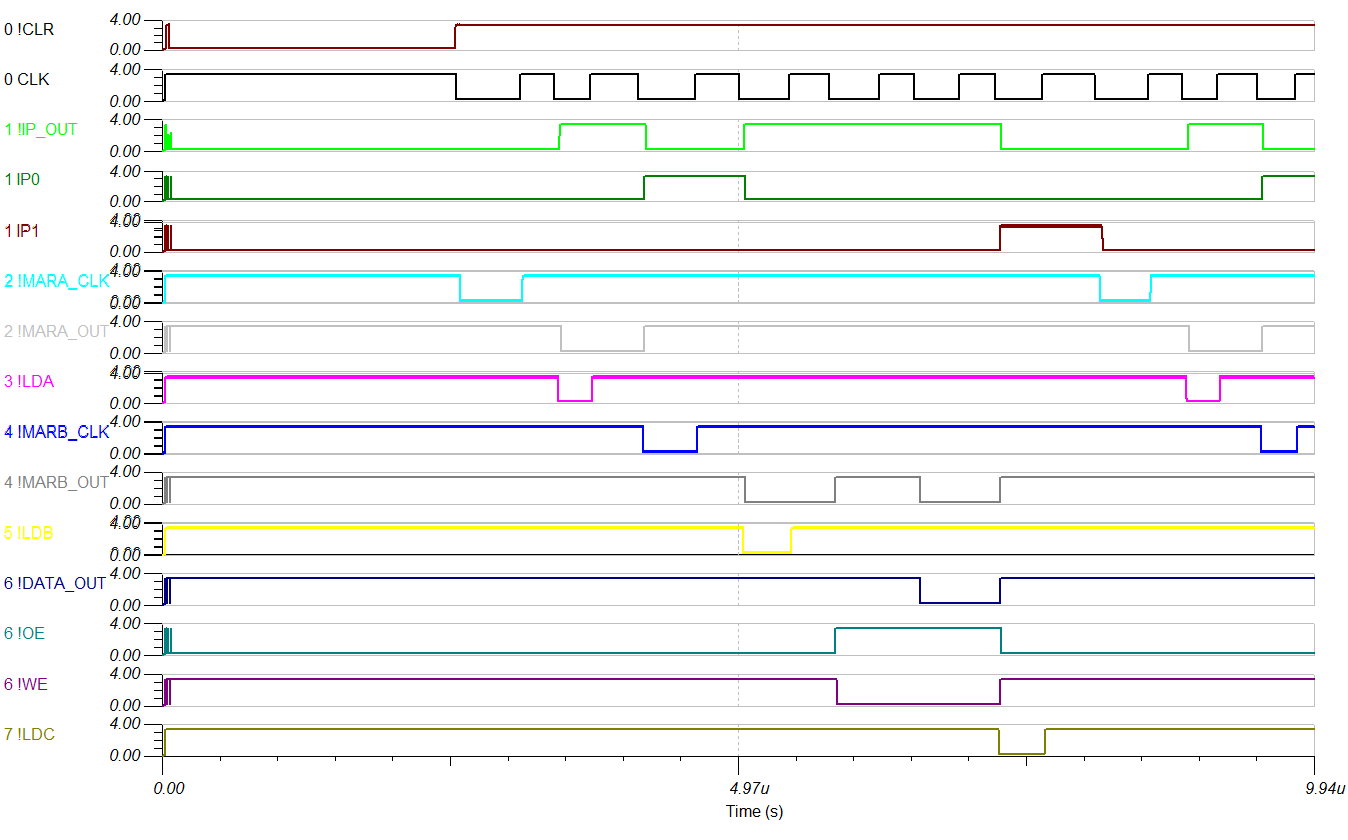

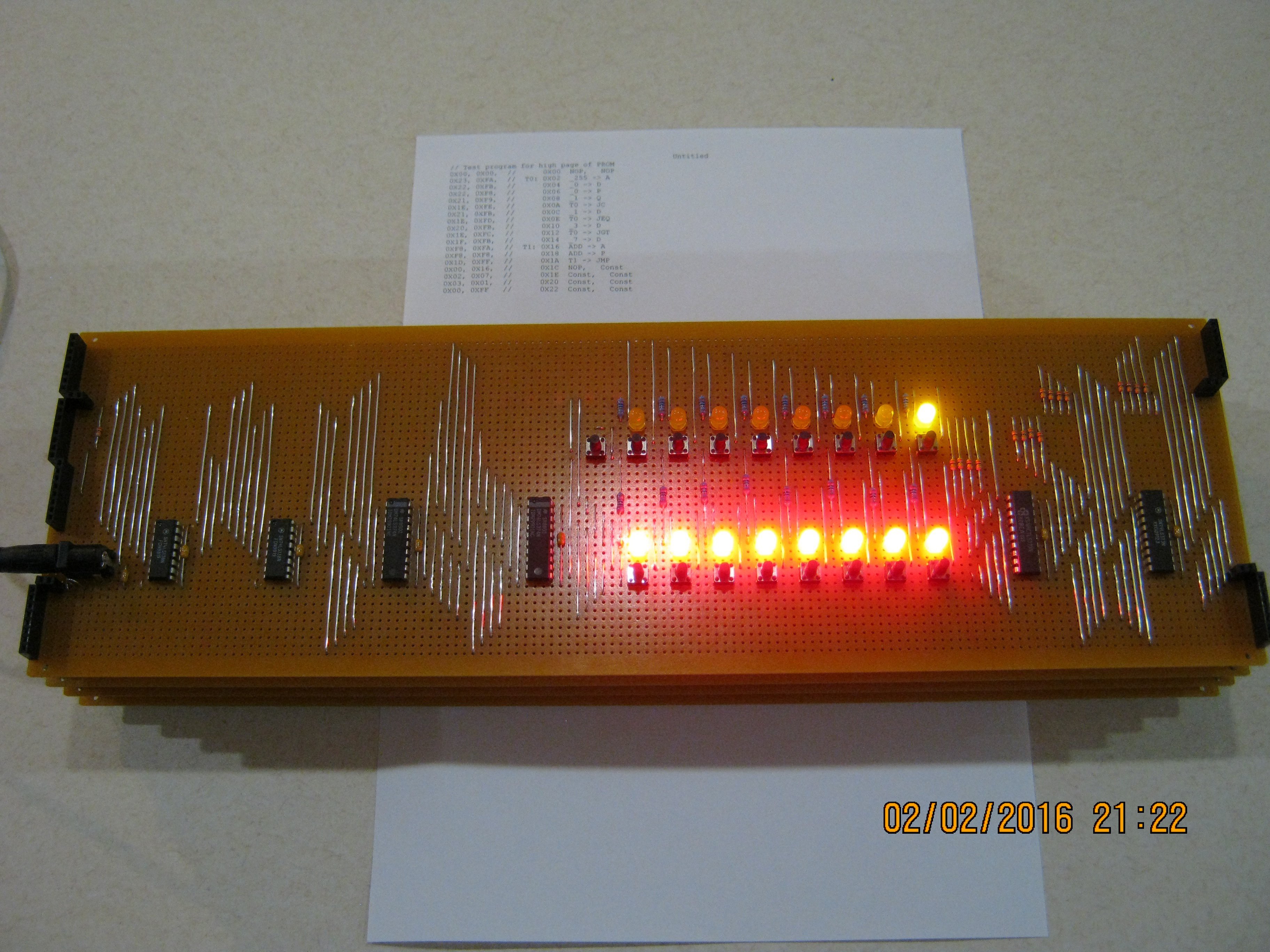

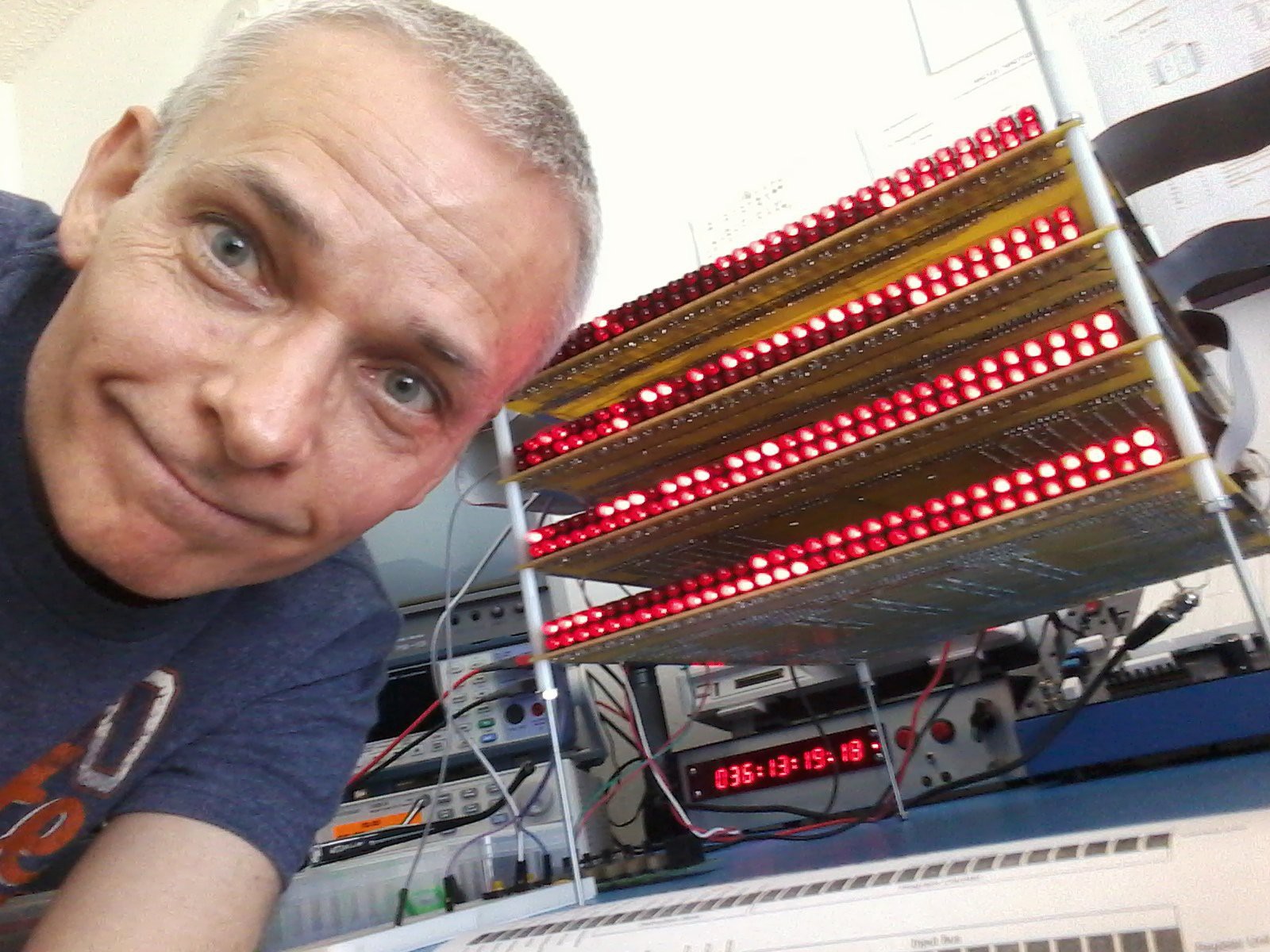

描述:主要的网站是www.blinkingcomputer.org - 下面是11月17日主页的摘录。目标是:*足够简单,以便每个人都能看到它是如何工作的,这意味着很多LED *复杂到足以证明一个主要的想法 CPU *小到足以让任何有时间构建它的人都能负担得起*足够快速建立并保持我(以及那些跟随我的)家庭生活*足够快以运行一些复杂的软件*足够慢以便每个人都可以看到它正在运行 并逐步理解它*足够扁平,以便可以一次性看到整个状态CPU是Raspberry Pi托管的,它将:*是主存储器和任何内存映射IO *控制时钟,所以你可以单步进入软件 *运行编译器*运行作业队列*托管网络摄像头,这样您就可以提交作业并看到它看到它正在运行。

描述:microYasep是一个最小的核心,因此更新后的功能不可用,但对于不进行内存密集型操作的MPU应用程序来说并不重要。

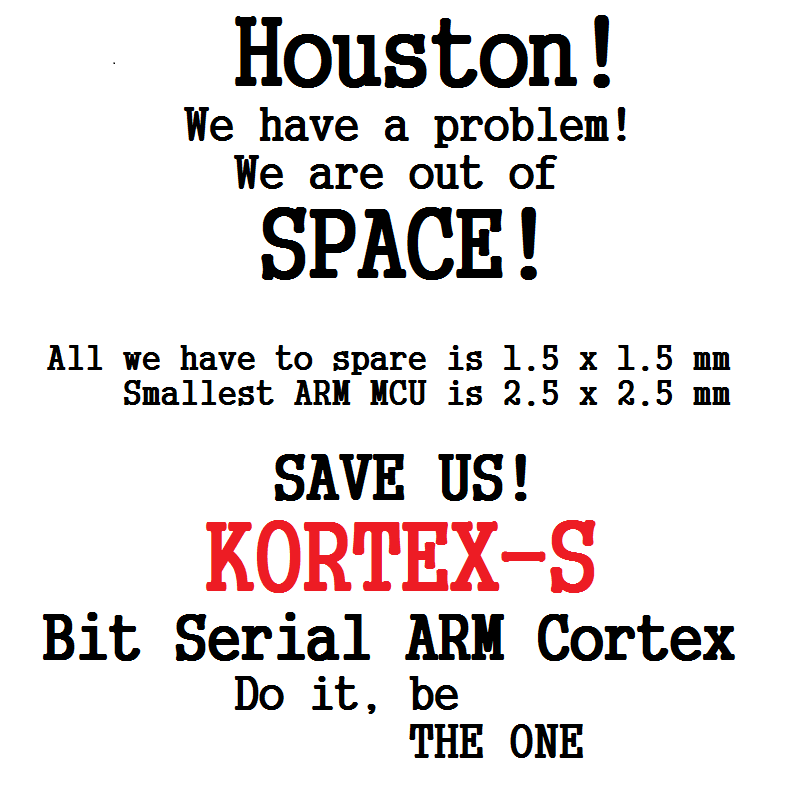

描述:ARM CPU的位串行实现。 非常慢,非常小。 目标是它可以适应非常小的FPGA。

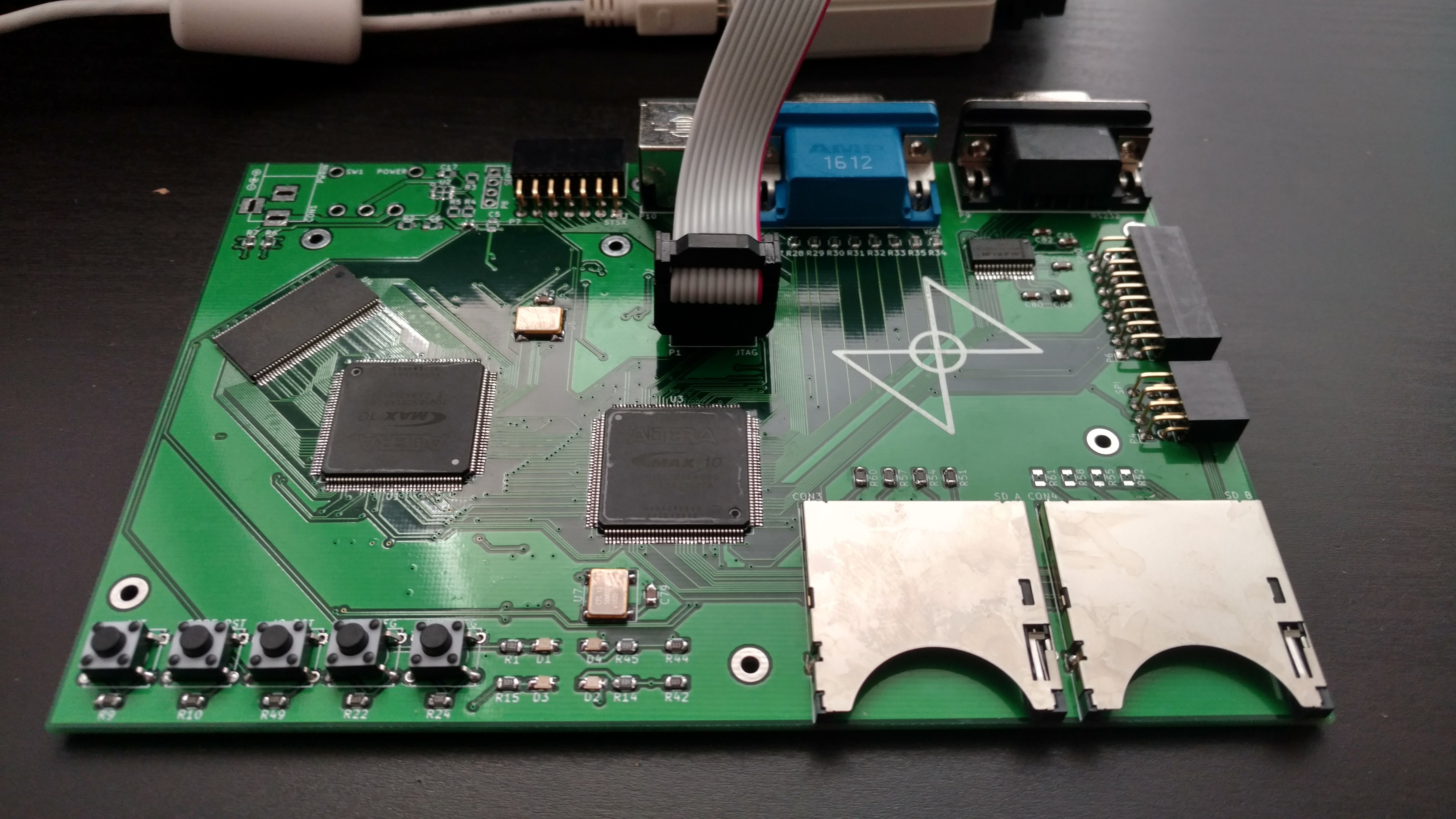

描述:项目epRISC旨在从头开发计算机。 该项目的核心是一个32位RISC CPU,采用Verilog实现,运行在定制的双FPGA开发板上。

描述:cpu是从Nakano,K。等人的设计扩展的堆叠机器。 (见链接)。 寄存器以通常范围的算术运算符和堆栈操作指令堆叠排列。 除了堆栈顶部(名为top)和next-to-top-stack(名为next)之外,没有命名寄存器。 CPU设计来自http://www.cs.hiroshima-u.ac.jp/~nakano/wiki/,并获得GPL许可。 我添加了加载/存储操作码和程序计数器push / pop。 加载和存储启用寄存器间接寻址,而PC操作启用功能。 堆栈大小为16的单周期版本占用大约1100个逻辑单元(Altera DE2中的33,000个),运行速度为75 MHz。 三台堆栈机器和一个VGA适配器共享SRAM用于显示和数据。 每个堆栈计算机都从其自己的片上存储器执行代码。 编译器是用Matlab编写的,但也适用于open sourc。

描述:这是一个古怪的想法,我已经工作了一段时间,但它仍处于发展的早期阶段。 最终目标是使其成为可靠的FPGA软核模型,甚至更好 - 一个小芯片。

描述:一个简单,可扩展,易于实现的bitlice架构的适度提案。可与继电器,锗或硅晶体管,DTL,DCTL,TTL,CBJT,ECL,CMOS一起使用......

描述:指令存储器处理16位指令。

描述:我的第四个家酿啤酒CPU。破解了解码器逻辑问题。

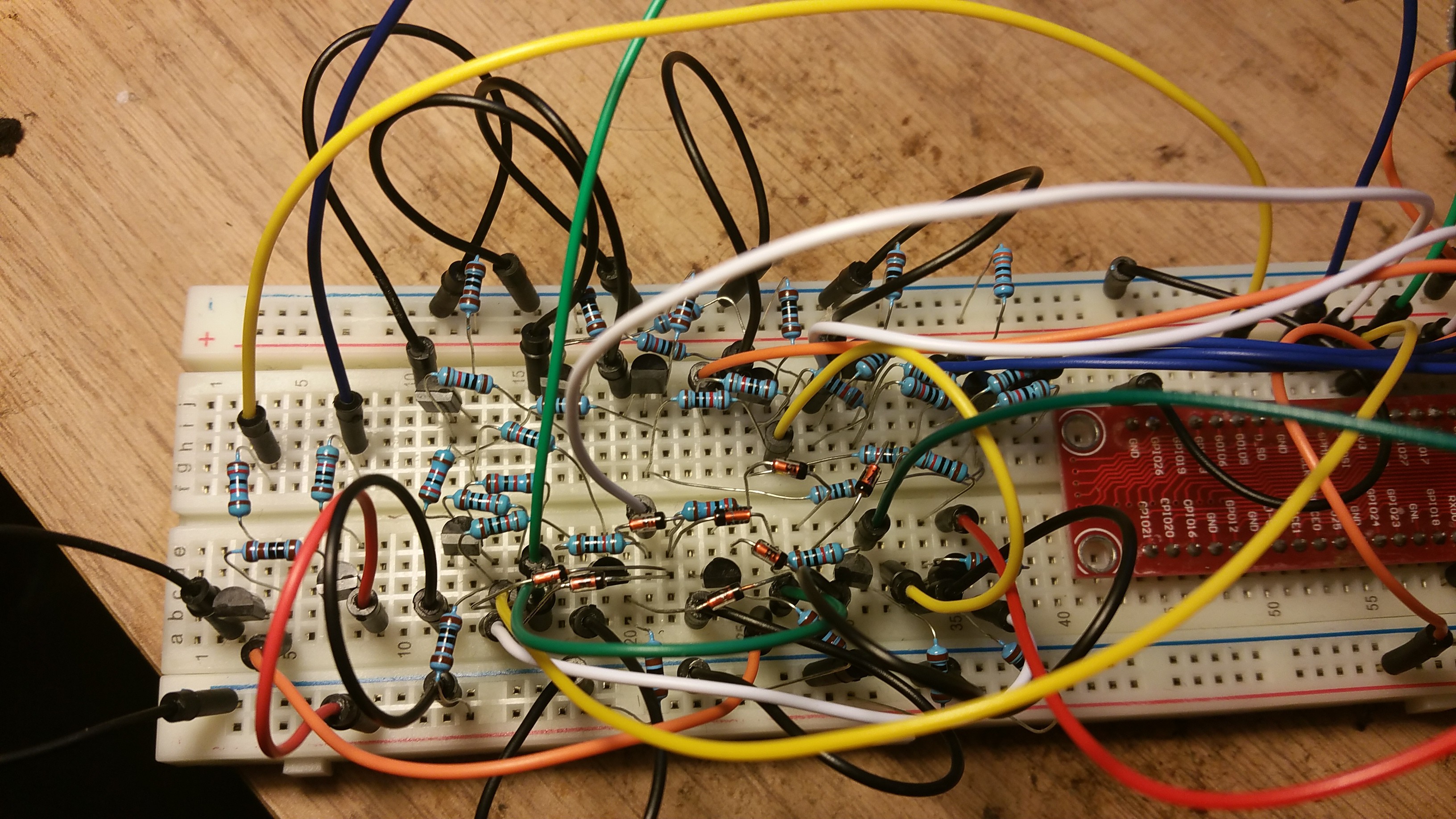

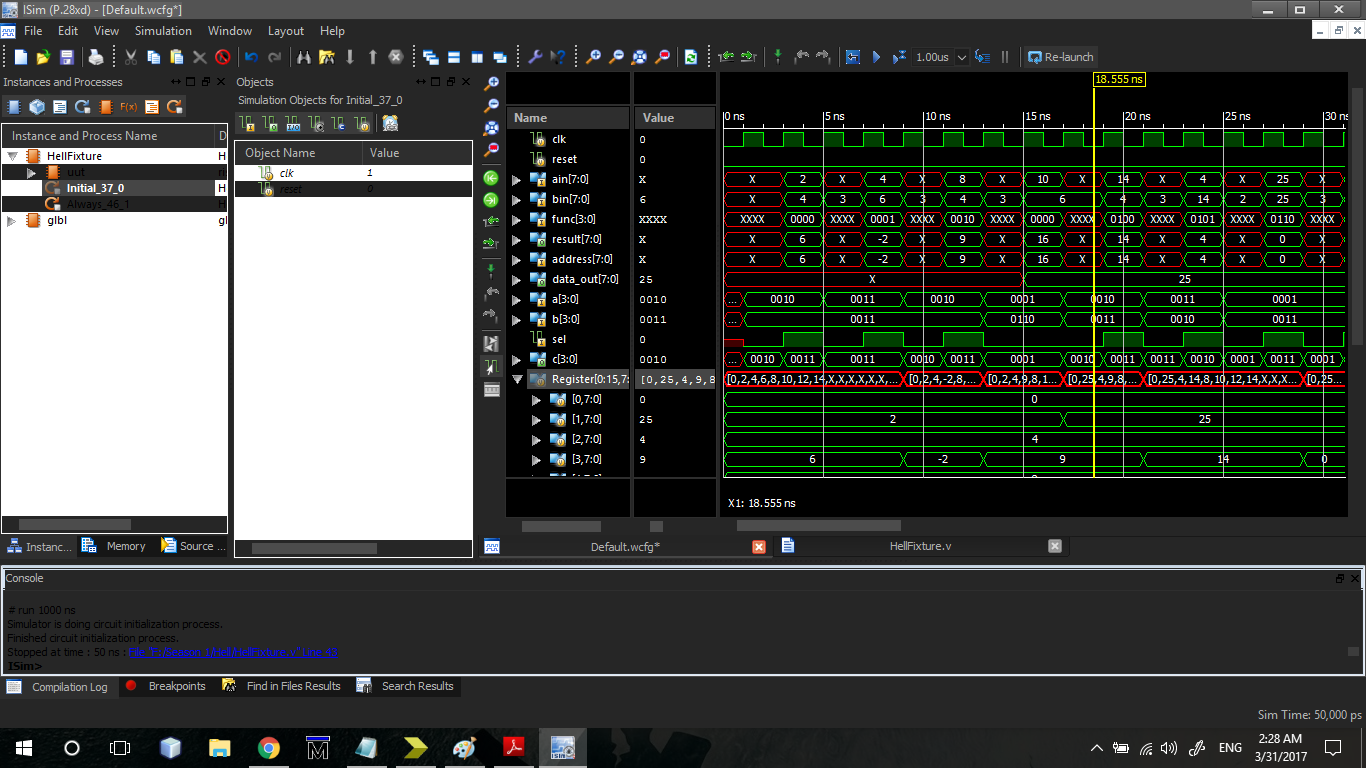

描述:我开始这个项目是为了让自己了解计算机是如何工作的。 作为此类评论,有用的链接或任何其他相关的内容将不胜感激。 在此之前,我在电子领域的经验主要是基于微控制器。计算机永远完成了一半(它可能更多,它可能更少,我只设计我正在处理的块的逻辑)但目前由大约300个晶体管组成。 我很确定计算机遵循'哈佛架构'(更正欢迎),因为RAM和ROM是严格隔离的。 松散使用4位数据宽度为4位,但指令宽度为8位,因为一些指令包括4位值。

描述:在90年代初的大学时代,我喜欢硬件 - 并且完全没有钱花在它上面。 所以我打捞了。 很多。 在垃圾桶里看电视吗? 把它拿回家修理它! 无法修复吗? 拉出尽可能多的组件! 救救他们! HOARD HOARD HOARD !!

描述:又一个Minimalistic One指令CPU。SUBLEQ表示减法跳转小于或EQual为零。

描述:采用20世纪70年代技术的最小8位TTL CPU。

描述:ED-64将是一台采用分立元件构建的8位计算机,并将采用铁氧体磁芯存储器(记录为单独的项目)。

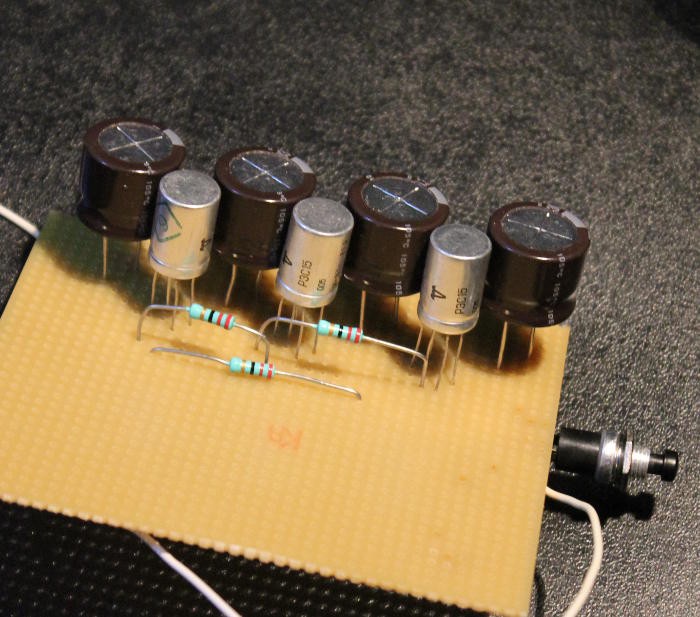

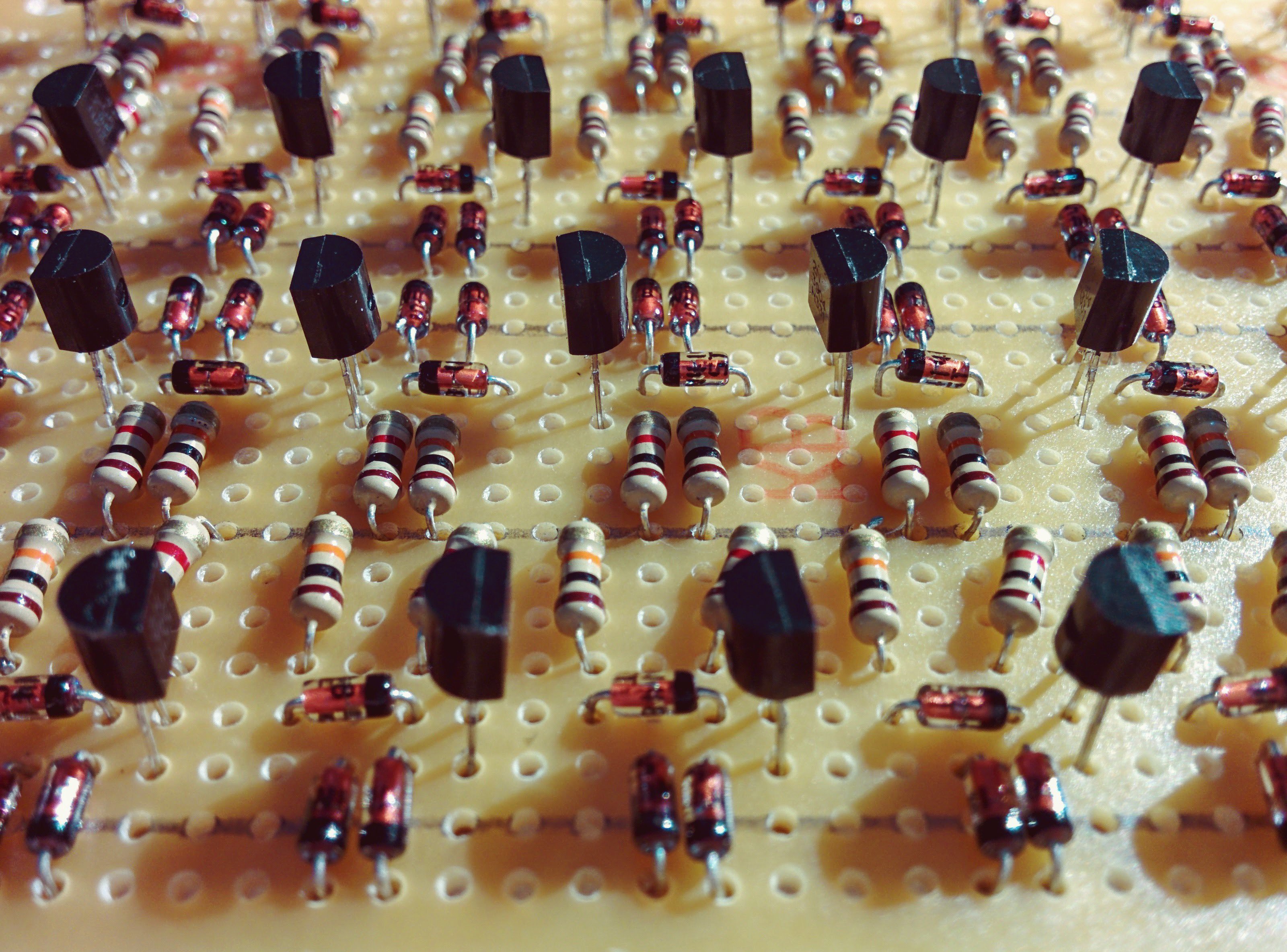

描述:这是一个完全由分立元件构成的可用计算机的简单开端,如晶体管,二极管,电阻器和电容器,正如它们在60年代所做的那样。

描述:MINIVAC 601实验很有趣,而且经常具有挑战性,没有真正的接线图可供使用。

描述:1975年,沃兹尼亚克用44个简单芯片设计了Breakout街机游戏,没有使用微处理器,仅仅是因为当时他无法使用。 一年后推出了MOS 6502和Zilog Z80,他的Apple 1开始了微电脑革命。 关于哪个处理器更好的争论仍然存在争议。 但更有意思的是调查这些设备是否真的是个人计算机革命所必需的:如果它们从未出现过会发生什么?

描述:最终的目标是尽可能简单地(从物理上构建)一台完整的计算机,但功能强大,足以在LED矩阵(可能16x16)上运行俄罗斯方块,Pong,Arkanoid或Snakes等旧游戏。

描述:我正在使用FPGA构建(当前)64k RAM计算机。 现在有很多流水线!

描述:LEO-1是一个完整的16位计算机系统,具有定制设计的CPU。

描述:简单的4位计算机,从头开始设计。

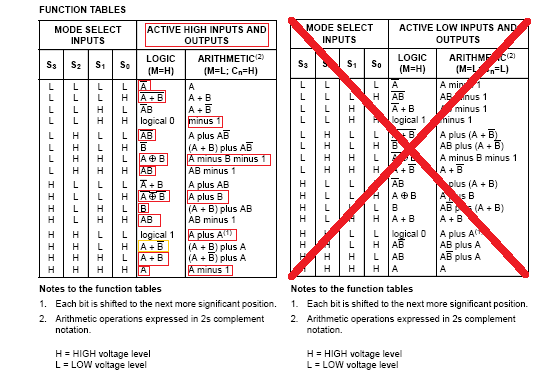

描述:驯服74LS181 ALU芯片。

描述:基于Slice的CPU背后的概念是,根据需要多少位,可以修改CPU。 CPU将有一个允许添加“切片”的背板,每个卡都有4位。 每个切片都有一些RAM来存储数据,但主程序将存储在背板上。 基本上,来自所有切片的总切片ram将看起来像一个大块的cpu - 数据宽度等于切片数乘以四。 现在是8位指令宽度,但仍然不知道如何将常量放入指令中。

描述:我开始这个项目想要更好地理解计算机在逻辑层面的工作方式。 我最初咬掉的东西比我可以咀嚼的多,试图实现我称之为RISC的东西,它实际上是更多的CISC和管道(管道是最大的哎呀)。 话虽这么说,我正在构建一个功能更加简单的设计。处理器处理16位字的数据。 所有标量值均以16位表示。

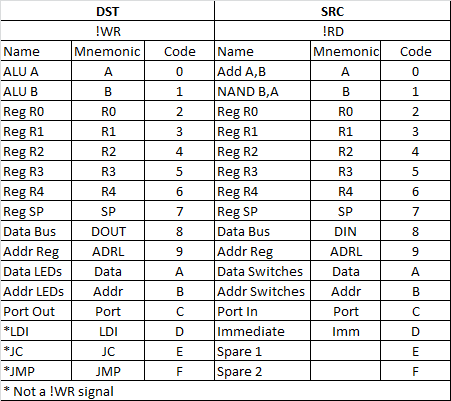

描述:这个项目是我尝试制作一台只有一条指令的计算机 - 移动指令。 具体来说,将数据从一个位置移动到另一个位置。 这些位置可以是寄存器或RAM或其他特殊功能。 这将是我提交的手工制作的整洁小型面包板计算机。具体类型的计算机称为传输触发架构,但触发将非常简单。 它通过将数据从一个位置移动到另一个位置来工作 每个函数都有一个内存位置。 要执行该功能,您只需将数据移动到这些内存位置。 例如,要执行ADD,只需将字节移动到两个ADD存储单元,结果将显示在下一个时钟的第三个存储单元中。 因此程序只会是一系列源地址和目标地址。

描述:WITCH-E项目试图研究Harwell WITCH的工程方面并利用其教育价值。 作为该项目的一部分,我们的目标是以视频,文学和工具(如WITCH-E模拟器和WITCH-E副本)的形式积累教育材料,以便WITCH背后的核心技术可以作为里程碑之一突出显示 在计算历史中导致了现代计算机系统中使用的许多基本概念。

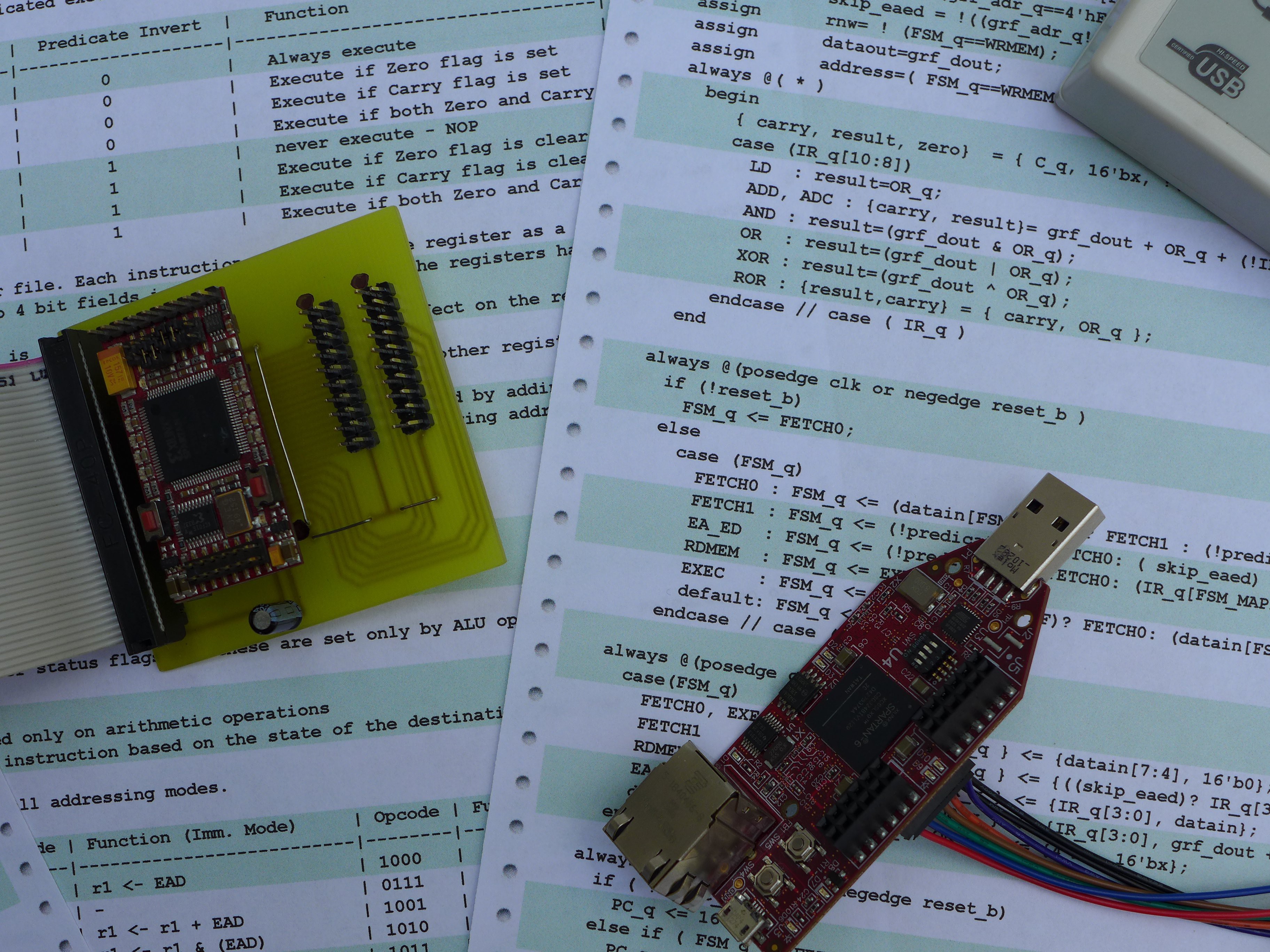

描述:OPC-5是HDL中的一种小型新型CPU设计 - 在Verilog中 - 用于在FPGA上实现。 它是16位:地址总线,数据总线和寄存器都是16位宽。 它有16个寄存器和一个常规和小指令集。 (它是一个可以单词寻址的机器,如Data General Nova,Xerox Alto,当然还有PDP-11。所以,不要将16位字视为两个字节!)与HDL一起,我们有一个规范,两个模拟器和一个宏汇编器。 这些产品中的每一个都只是一页代码:66行乘100个字符,而不是混淆。 这使它成为One Page CPU,并且有望成为一台有趣的机器。

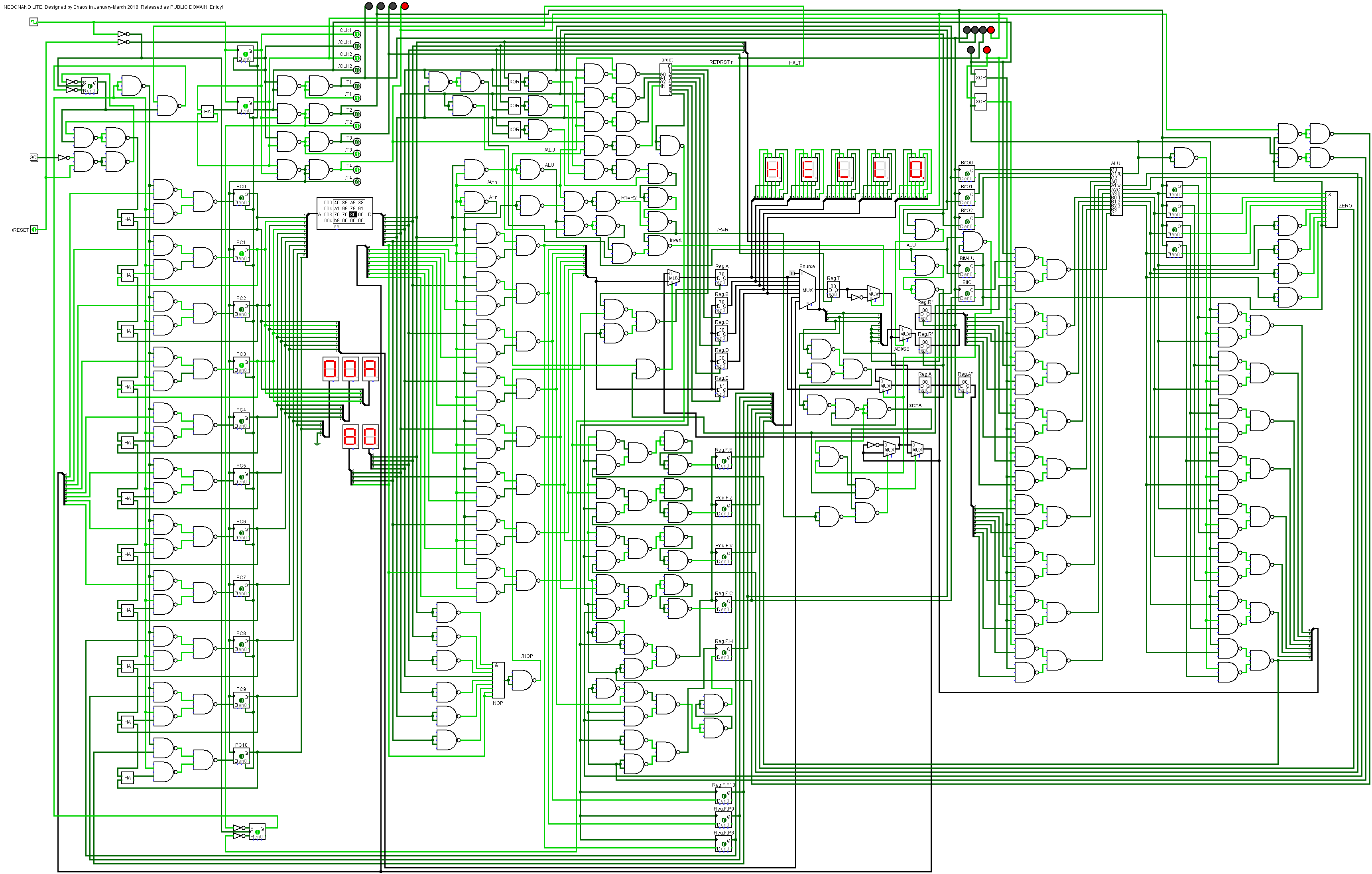

描述:NEDONAND是8位自制电脑,完全由许多74F00芯片(2输入与非门)构成。

描述:A2Z是我自己从A到Z制造的计算机.CPU有自己的指令集,由我自己发明。 这是一个教学项目。 目标是在计算机的每个部分上工作:硬件和软件。 硬件基于小型FPGA,内置16位CPU内核和一些外设。 该软件采用自定义语言编写:“A2Z_Basic”,带有在PC上运行的自制交叉编译器,也是从头开始设计的,并用C语言编写。本页面提供了所有源代码(Verilog,C,A2Z_Basic)。 一切都是开源的。 有一个可用的仿真器,因此即使没有FPGA板也可以发现这台计算机。

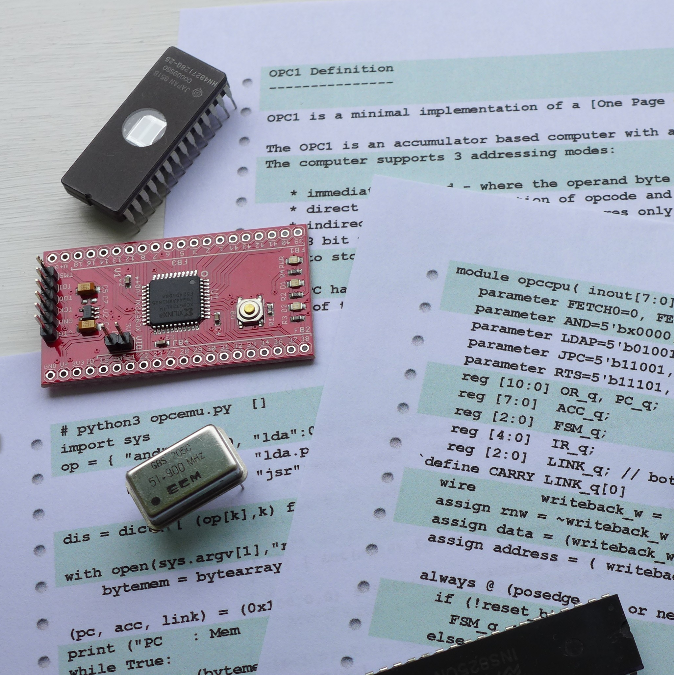

描述:这是我们为单页计算挑战做的第一次努力:在66行标记中我们指定一个CPU,66行python中我们编写一个模拟器,另外66行python用于宏汇编程序,66行HTML和JavaScript用于另一个模拟器 ,当然还有66行verilog来定义CPLD中的CPU。

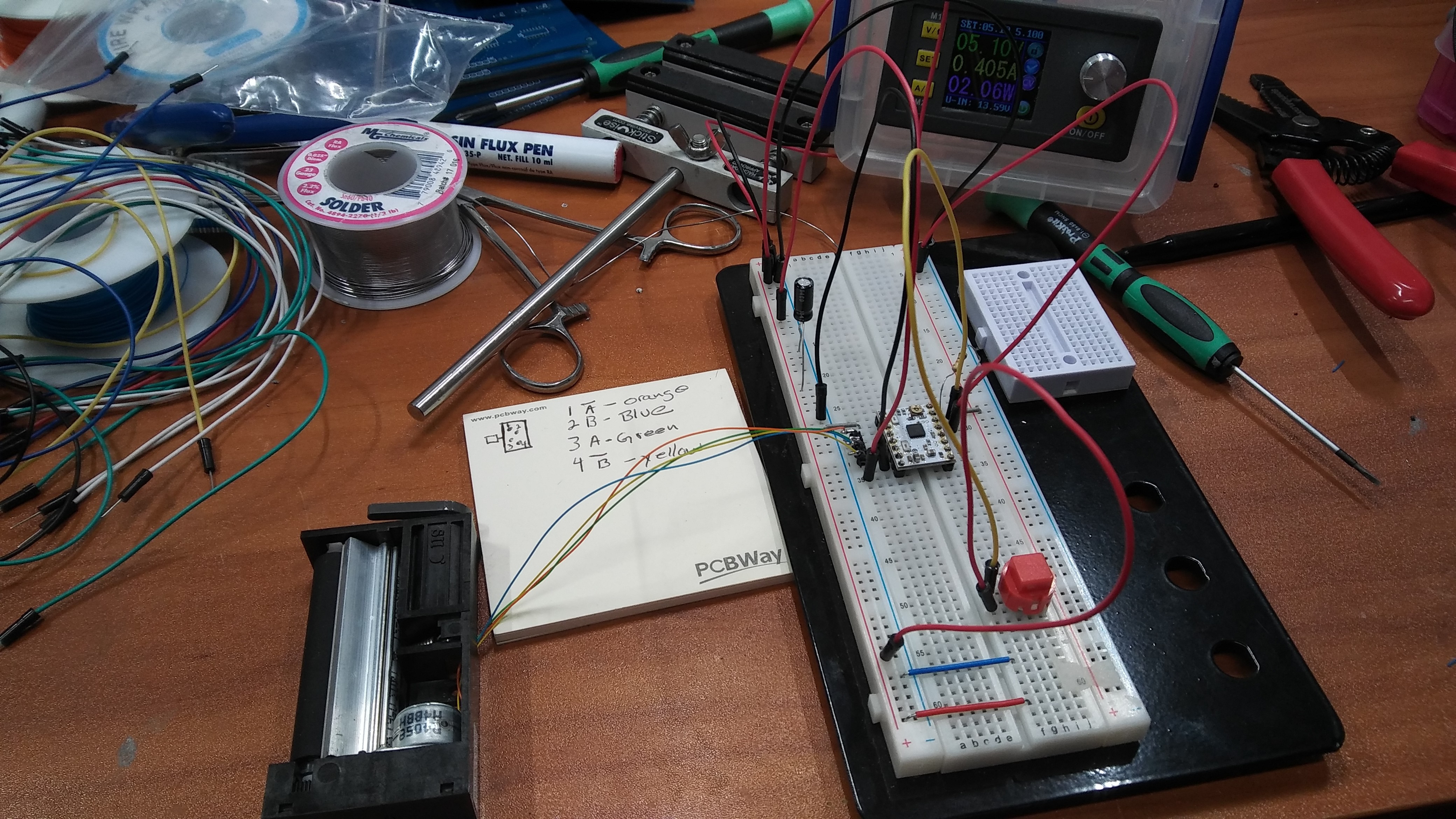

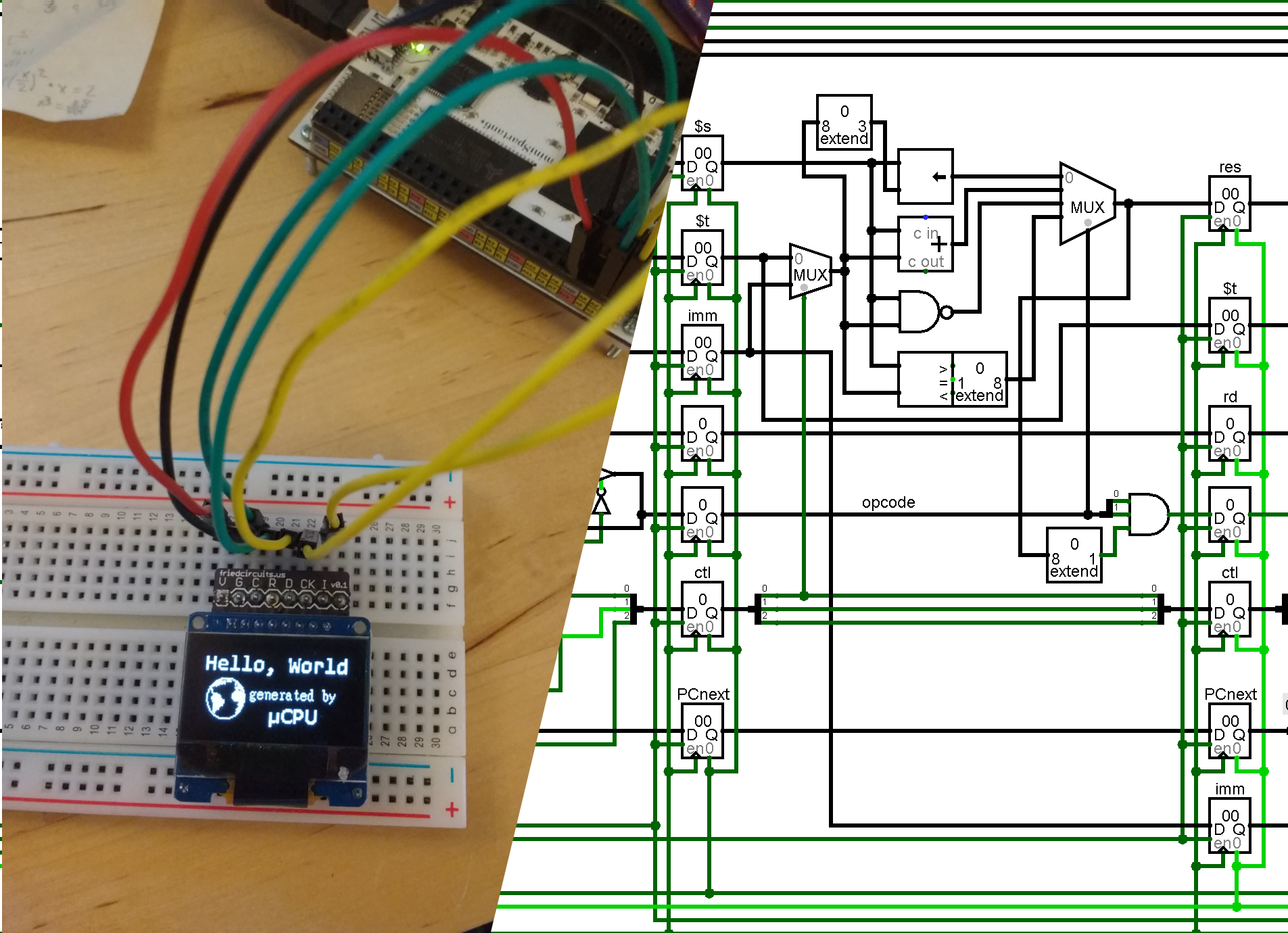

描述:不久前,我开始在Logisim中构建一个32位MIPS处理器。 在该项目正在进行一段时间后,我得到了一个FPGA开发板(miniSpartan6 +)。 虽然我可能会在FPGA上挤压32位版本,但我是可编程逻辑(vhdl,verilog等)的新手,所以我决定构建一个非常简单,非常小(希望)的CPU内核。 我已经在链接部分的google doc中包含了指令集,以及指向github的链接。

描述:这是苏联簧片继电器上的簧片继电器,具有Von-Neumann架构和深奥的编程语言“brainfuck”指令集。 一个BrainfuckPC。所有计算逻辑都安装在192个模块(60x44mm PCB,每个4个继电器)上,放置在6个块(150x200mm)上,每个模块上有32个模块。 块是绕线的。

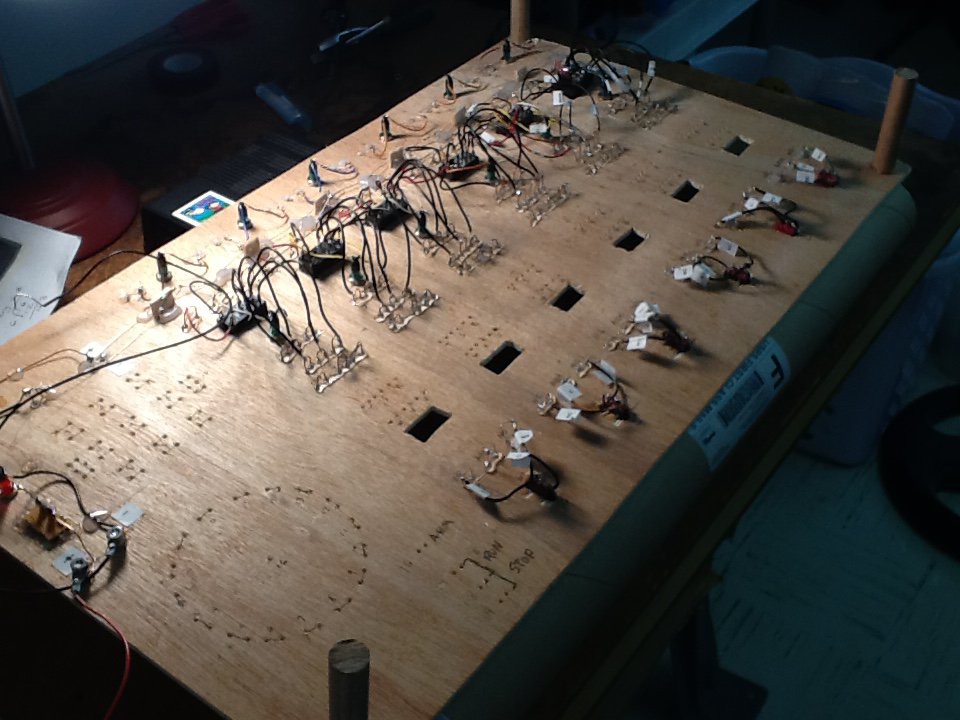

描述:我的目标是使用回收,重新用途和普通垃圾作为主要建筑材料来构建一台四位计算机。 为什么? 好吧,纸板是免费的,因为我的工作场所把它放在垃圾箱里,我没有资金购买更好的材料。 一个非常绿色的构建确实。 除了ALU之外,所有逻辑单元都构造在单独的纸板垫上,作为基本的Nand,Nor或其他门作为基本构建块。这种结构方法对任何年龄段的人都是开放的,他们可以焊接,并且所有电路都是点对点连接的,没有PC板。 学习辅助工具,了解数字逻辑如何在门级工作。 在该项目结束时将找不到黑色IC封装。

描述:感受并了解计算的工作原理 - 采用Konrad Zuse风格。没有涉及二极管 - 具有半导体逻辑的中继计算机不是计算机,因此所有逻辑将仅基于继电器。 一台电机将驱动程序磁带。然而,继电器有LED显示它们是否打开 - 但它们没有任何逻辑功能,它们可以被灯泡替换或完全省略而不会干扰计算机的功能。

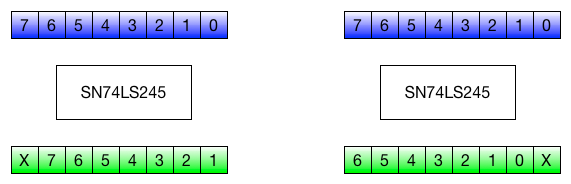

描述:YASEP是一个相当简单的RISC设计,基于它的功能计算机系统需要使用大多数中等规模集成IC(74HC245等)的少量PCB。 它具有80年代自制电脑的一些魅力,具有2010年技术的优势(RAM由单芯片制成,总功率应小于几瓦,使用大量便宜的微型表面贴装设备...)。 然而,我想避免“黑盒子”,所以我尝试只使用固定功能电路。

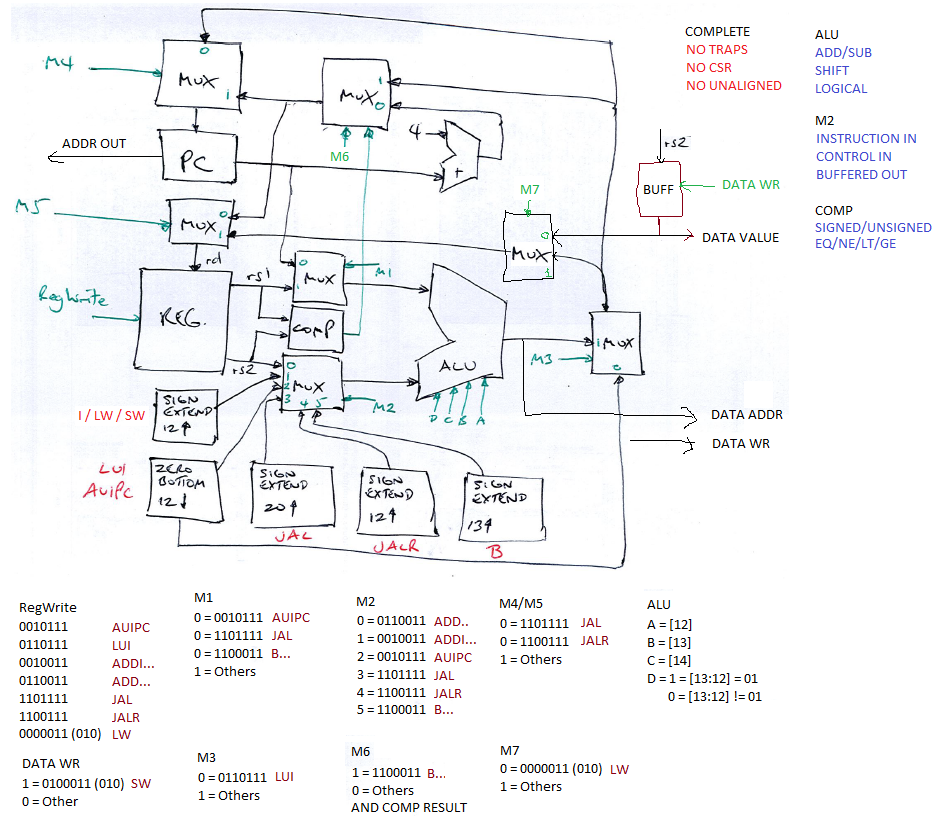

描述:世界上缺少一个主要的CPU。 32位自制CPU,实现完整的现代指令集。 解决方案是使用74'串行逻辑芯片和RISC-V开源指令集架构。 使用已经为RISC-V创建的GNU工具链,这意味着我们已经准备好了汇编器和编译器并等待我们的机器。 因此,让我们摇滚,创造自制项目的终极目标。

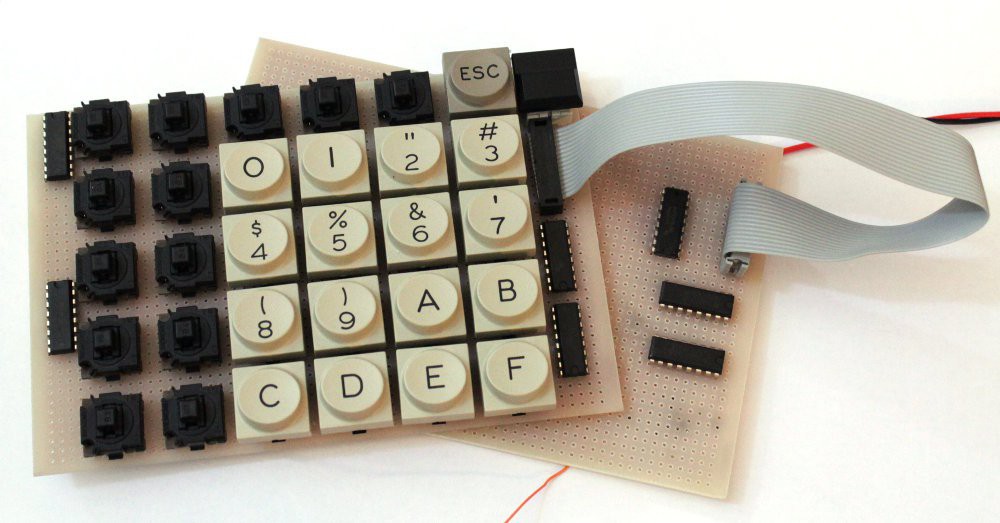

描述:这个项目是关于构建世界上最快的relay-cpu。一旦你有一个自制的CPU(也在它准备好之前),每个人都会问:它能做什么? 因此,有一个很好的应用程序来显示CPU可以做什么是很重要的。 这也将为设计提供一些重点。 我把计算器作为应用程序。 因此设备应该有计算器键和显示器。

描述:同步通用最小指令推算装置。

描述:我的目标是使用回收,重新用途和普通垃圾作为主要建筑材料来构建一台四位计算机。 为什么? 好吧,纸板是免费的,因为我的工作场所把它放在垃圾箱里,我没有资金购买更好的材料。 一个非常绿色的构建确实。 第一个开始这个的电子部件是由一位去世的朋友送给我的,而且比建造一台电脑更有意义。 除了ALU之外,所有门都是NAND或Nor使用DTL。 使用的晶体管是NPN 2N2222型或PNP 2N3906。 感谢Yann Guidon和Jezz - Morning Star的其他部分。 采用了非常大的结构,以帮助我学习逻辑电路,并且当我发现什么不起作用时,也更容易进行更改。 每个门在纸板切口上的尺寸约为0.75 X 1.75英寸。 将使用RISC并且时钟速度将非常慢,大约3Hz才能启动。 主总线为8位(数据为4,地址为4)。

评论

0 / 100

查看更多

2019-08-19

3863

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号