Hackaday.io上的树莓派项目- sdramThingZero - 133MS/s 32 位逻辑分析仪

收藏

分享

脑图

Hackaday.io上的树莓派项目- sdramThingZero - 133MS/s 32 位逻辑分析仪

关于项目

项目描述:是的,如果把旧的SDRAM DIMM添加到当今的单板计算机上,用512MB的板载DDR2,这似乎有点可笑,但信不信由你,这有充分的理由!!!将 SBC 转换为逻辑分析仪、数据记录器或示波器...你会知道的

项目图片

输入外部内存...

通过在"真实世界"(逻辑分析器输入、ADC 等)之间添加一点内存,可以快速采样数据*,*然后以任何可能的速度将数据读取到 RPi 中。然后,在读取后,可以显示、操作、缩放等。

这与大多数逻辑分析器外围设备不同。

输入 SDRAM:

就我而言, Sdram 是最后一个与...它运行在 3.3V, 不需要复杂的计时方案 (和巨大的灵敏度倾斜) 来处理每个边缘的数据, 等等...(在另一个级别上,它允许超过 8 个数据位置的突发,允许一些任意的时钟停止,等等)。

除此之外, 很容易找到 Sdram Dimms 在堆中未使用...当您可以轻松地拥有 32 个并行位和 64MB 已连接 133MHz 速度时,为什么要限制使用单个 16 位宽的 16MB 芯片?

输入 sdram 问题:

sdramThing 是一个 (系列) 项目, 我一直在工作几年。在此之前,最新版本充当 30MS/s 32 位"逻辑分析仪",当连接到 AVR 和示波器时。

所有版本的 SdramThing 的基本思想是将 SDRAM 的"命令"/地址引脚直接连接到其数据引脚...因此,通过向数据位置填充要反馈给 SDRAM的特定指令,SDRAM 本身可以独立于控制器以最高速度(133MHz?)以最高速度"自由运行"。这绝对是一个循环, 绝对是一个 "循环" 的解释。

当前状态(已更新):

sdramThingZero是"自由运行"的速度大于主机,并将很快采样/输出数据!

在 sdramThingZero 中要实现的绝大多数概念在长功能的#sdramThing4.5 "逻辑分析器"中得到了验证...所以在这一点上, 它真的只是一点插头和巧克力。

巴士:大多数单板计算机(和其他接口)可用的 GPIS 数量有限,因此需要将 SDRAM DIMM 上的引脚数缩减到更易于管理的"总线"式接口。我可能会去类似 8051 风格的总线接口, 这 (很酷) 也支持例如 FT2232H, 这意味着 sdramThingZero 可以通过 USB2.0 直接接口, 与中间的微控制器之间几乎没有一个微控制器!

以前,我打算直接转到与这个项目的总线接口。但是,这样做也会限制主机回读采样数据的速度。所以。。。我正在采取一种新的方法:我将在设计这个系统时考虑到常规的GPIOs,此时,通过高引脚数微控制器。一旦设计了一个板,它可以连接到一个子板,然后削减针计数到所需的总线。对于 8051 型总线,这只能是一些 D 锁和一些网络电阻器来完成的。

PCB:目前,SdramThingZero在无焊面包板上以高达23MHz的速度运行。 sdramThing4.5 被限制在 30MS/s,很可能是由于其焊接面包板上的点对点布线非常错误,以及使用的旧 74 系列芯片的速度。具有体面屏蔽和一定量跟踪长度匹配的 PCB(以及考虑添加延迟(例如多路复用器)应显著提高这些速度。

电源:SDRAM DIMM 可能需要一点力量...我不确定有多少可用, 例如, PiZero, 另一个电源可能需要。

触发:这是要确定的,但我的模糊想法,在这一点上,是一个简单的触发器(一个输入,高或低),与一个圆形预缓冲手。这很可能在"自由运行器"上实现,例如输出一个额外的"芯片选择"数据信号,一个用于圆形缓冲区,另一个用于常规采样。然后,触发输入是 2:1 多路复用器的选择性输入,该多路复用器将两个芯片选择输出之一路由回实际芯片选择控制信号。类似的可能也可以通过地址信号来完成。

"DDR"仿真:只需将两个相反边缘触发的 D 锁连接到每个输入信号,输入到两个单独的 SDRAM 引脚中,现在我们谈论的是 16ch 266MS/s

项目文件

1 X PC-133 SDRAM DIMM

1 X 74AHC574

2 X 74HC00

1 X 30MHz 晶体振荡器

1 X 无焊面包板

1 X 各种电容器

1 X CY2305 时钟扇出芯片

1 X 旧电锯主板

1 X "主机"

这里有一个想法:

Sn74lvc1g123 - 可能只是处理我们的单次拍摄...就个人而言, 使用 Rc 计时的想法不太适合我, 对于这个项目来说, 其采样率在很大程度上是可变的...但是, 也许 som 'n 可以完成那些 R 和 C 输入与 SDRAM 时钟之类的东西。或者,即使 R 和 C 固定了一些其他路径(例如,在 10ns 时,最大采样为 100MS/s),只要我们能够确保 10ns 脉冲满足指令负载时钟边缘的设置/保持时间(当采样速率较低时)。

模糊的想法: 由于尝试与 8 位总线接口, 也许回读采样的 32 位可能发生的桶式。[也许类似的写作自由跑者?例如,读取第一个芯片,从第二个芯片写入第一个芯片,再读一遍第一个芯片。因此,合理减少总线上的芯片[加载]数量,以及合理的闩锁/缓冲器数量。

也有道理, 读第一个 Sk 芯片到总线, 读第二芯片到 Fr 第一芯片, 等等 [覆盖 Fr, 但可以重写], 一种左向的桶旅。[可能更可行;由于数据 I/O 是单个引脚,如果 B4->B3->B2->B1,则负载不会减少太多,但如果 B4s->B3f、B3f->B3s...

但是:B4-/\/\/B3-/\/\/-B2-/\/\/B1-/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\嗯。只是没有那么多,[也许],因为所有的SK芯片[和所有FR芯片]使用相同的命令信号[所有芯片同时读取/写入]我不知道,因为读取命令和写入命令需要不同的时钟周期,也许读取的数据会停留足够长的时间,由写入注册,嗯。在其他地方也很方便 [将 FR 命令/NOP 从银行复制到银行?

但是:B4s-/\/\/-B3f-/\/-B3s-/\/\/-B2f-/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\/\B1s-/\/\/-总线...不会有这个限制 [从 Sk 读取, 同时写入 Fr 应该工作]

[当然, B4s = 1, B3s = 0, B3f = 0.5...电阻值从左到右增加?二极管?缓冲区,当然,但随后更多的控制信号/OE,当采样时,没有?

理想情况下,也会减少选择读回哪个字节所需的控制信号数[知道它们始终按顺序读取]...一种字节范围的移位寄存器。

作为一边在#Floppy "乐趣" - 备份一个独特的凯 - Pro 磁盘...我刚刚发生了这一切:

sdramthingZero 仍然被搁置, 但当然仍然运行 '圆 ol' 后头...没有什么能真正阻止进展,只是还没有开始设计/订购多氯联苯。事实上,面包板的sdramThingZero仍然坐在我的办公桌上,就在我的显示器下面。

所以这里有一些有趣的东西:

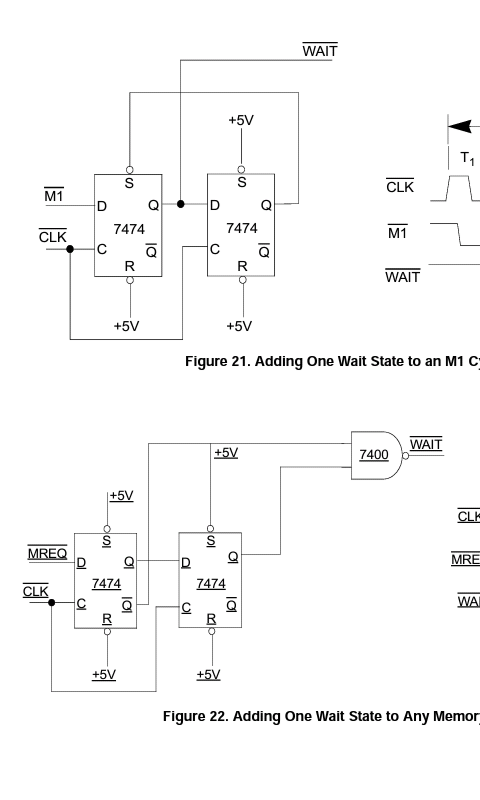

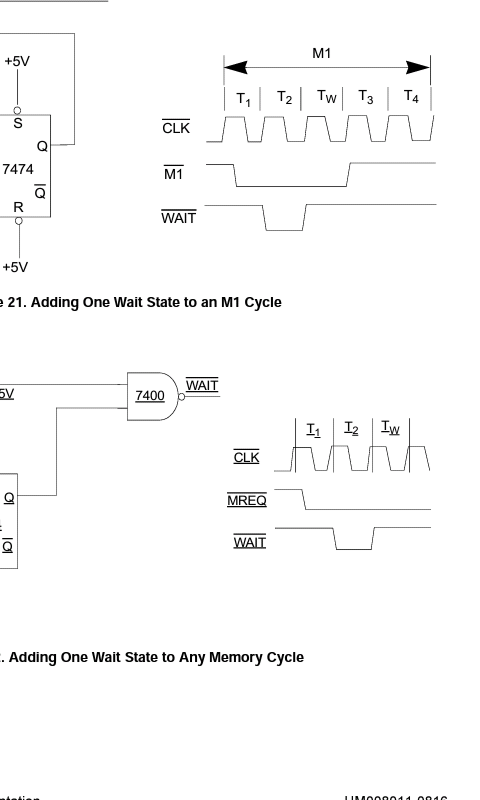

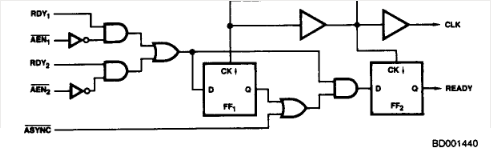

是的, 它几乎与本项目中使用的 "一次" 逻辑完全相同的拓扑。两个触发器系列,既接收(以某种形式)输入,对原始和延迟/锁定输出执行一些逻辑,甚至一个异步输入(类似于我的"一次旁路"输入)。这是从英特尔 8284 数据表, 这是用于 PC/XT (8088) 计算机的时钟生成器。除了时钟生成,8284 的另一个关键功能是我们在这里看到的,同步异步"READY"信号到系统时钟...就像我的一次拍摄将异步芯片选择或时钟启用信号同步到 SDRAM 的时钟一样。

为什么这很有趣...?也许这是某种事实上的拓扑一直使用...?事实是, 我设计电路没有查过...我用了关于我想要的东西的知识和期望,我设计了一个电路来达到这个目标。我知道它*会*工作,在大多数情况下(如果异步输入发生在设置/保持时间之间会发生什么?TI的想法在这里),但我没想到,这是好'nough的产品。然而,它就是它!

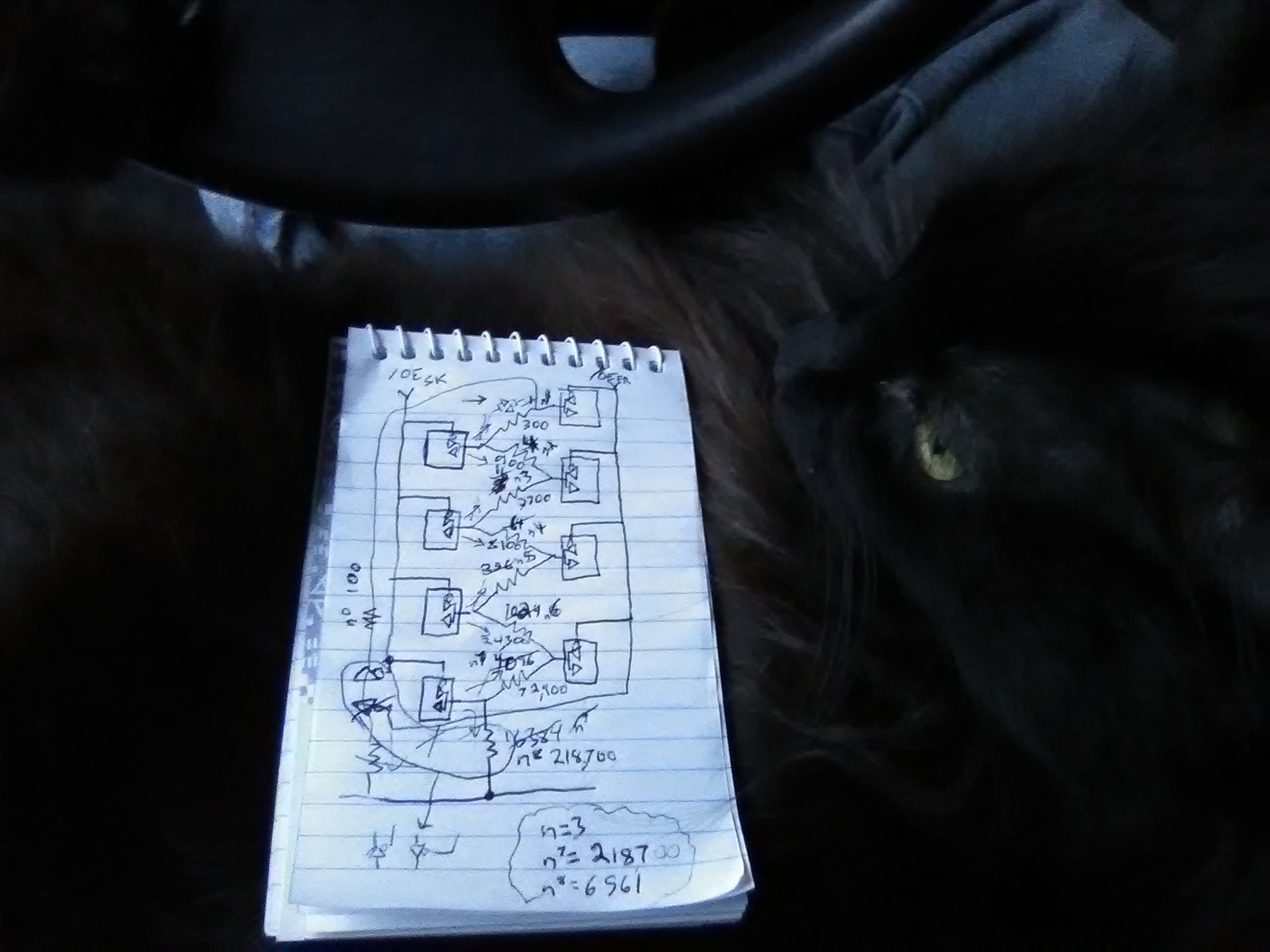

很显然, 现在是脑转储时间。在上一个日志中,我展示了我的想法,使一个通用的原型板,可用于第一个焊接原型,以及用于/可用于许多其他无关的项目...

这是最新的固定...Weee!

我没有提到的是,这个原板也期待什么[这个]项目的未来。这个项目有两个主要阶段,我看首先是得到它作为功能齐全(采样/重复,高速,触发器,可调采样频率),我可以...这是最简单的做与 uc, 有大量的 Gpio 引脚...因此, 我用我的信任 ol 'Atmega8515 40 针 - dips...而且, 正如我在上一个日志中描述的, 这完美地奠定了一些目前不必要的突破空间在我的原型板设计...

第二阶段是取代专用的 Avr, 以有利于任何主机, 人们可能想要使用...例如,单板计算机(如树莓派),甚至通过 FT2232 芯片通过 USB 直接将其连接到计算机。这里的障碍是, 这需要削减所需的 Gpios 数量, 以合理的东西...像 8 或 16 位数据总线。

在我的各种日志中有很多关于我如何做到这一点的沉思, 我毫不怀疑, 我已经得到了它大多想通...我也许, 如果我的大脑工作那么久, 鞭打出来的时间比它需要收到这个 Pcb 订单。

但是, 我想, 我倾向于对我的项目采取迭代方法, 而不是去与设计 - > PCB...而且,目前的情况是,无焊面包板原型已经变得越来越薄片(在很大程度上,我敢肯定,由于电线被颠簸,"天线"无处不在,等等...(有趣的是, 当我以 50mHz 的速度运行它时, 它会干扰我的电视接收!...这家伙持续一年, 并能够只是通电, 并使用它的可能性是相当低。所以, 迭代, 我仍然有一点点, 我可以尝试和实现, 而连接到 Avr...而且, 我不介意有一个可靠的原型, 我可以回到以后下线, 打开, 并期待仍然工作。

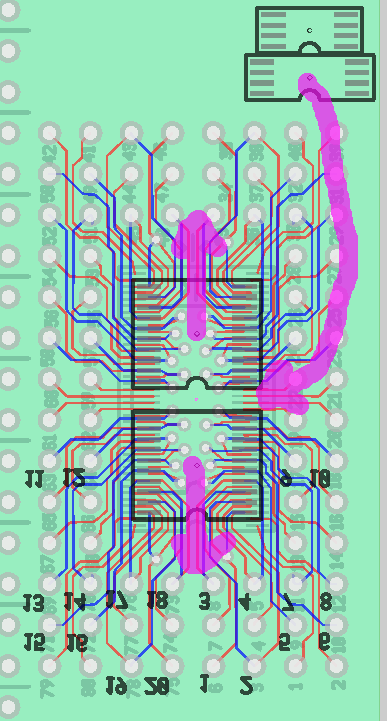

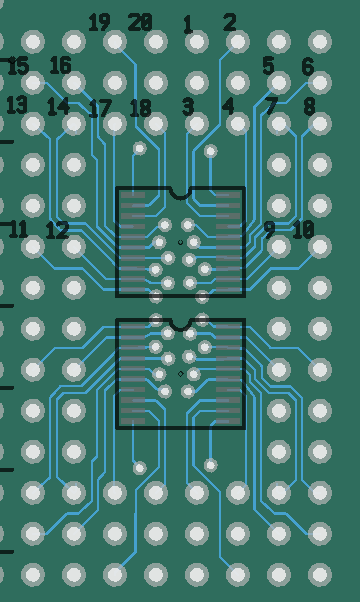

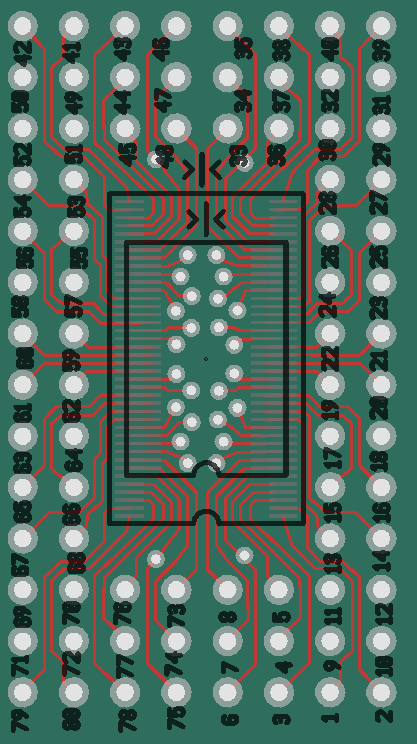

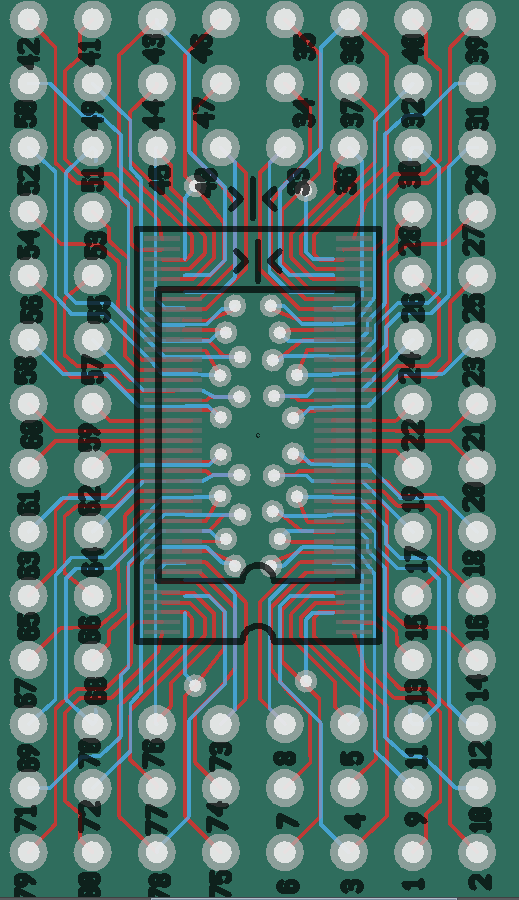

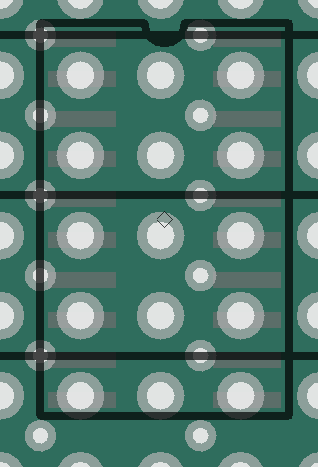

正在开发可焊接原型...由于无焊面包板 - 线 - 松木。决定不设计一个全上PCB,然而,因为它仍处于原型阶段...决定在 70 毫米 x 70 毫米的板, 他们比 Dimm 所需的宽度便宜得多, 所以我会 "拥抱" 两个在一起...它实际上是非常容易和稳定的薄PCB材料,只是重叠他们一两行。因此,电路板设计有些通用。首先,DIMM 插座将焊接成两个 70mm 高的板,从端到端运行:

可能需要一点手钻的支撑安装, 等等。但我同意这一点。关于 DIMM 插座的事情是, 他们有这个奇怪的脚印与对角线...更多关于在位。接下来,我们有一些突破表面安装芯片,因为7400的速度,我们正在寻找大多只来SSOP,或者如果你幸运(作为一个原型)SOIC。(是的,这是一个突破,原型设计。没有这些跟踪不匹配的长度,谁知道什么样的信号问题可能会产生,由于它们彼此的密切)。

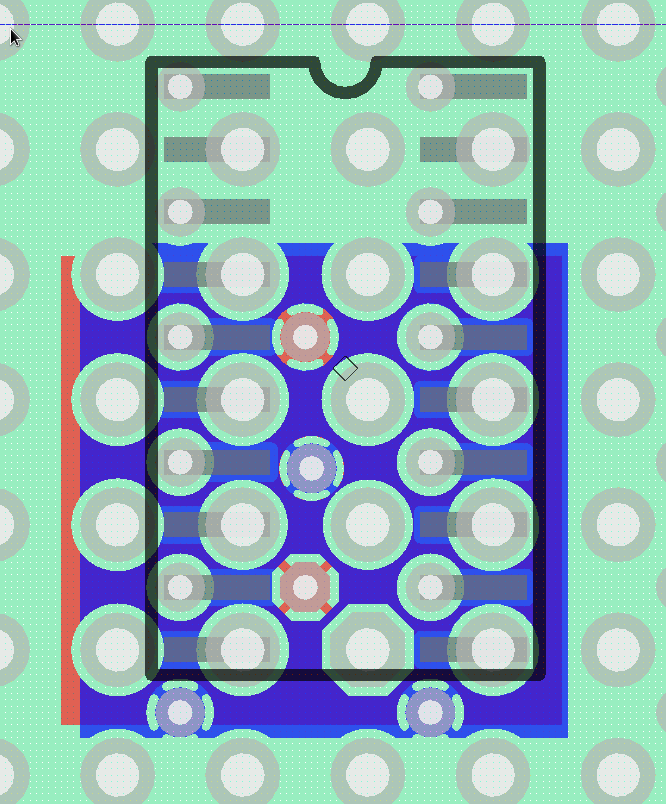

现在, 你可以看看那个布局, 然后去 "哇??!"但看看这个...如果我做了一个原型板, 有十个他们做, 我想其他项目, 以及...因此,上述设计 *后*(在另一边)这:

我其实没有任何 Ssop80 芯片, 我知道, 但我有一些 Tssop56 的, 我一直在计划使用...因此,这将很好地打破这一点,并留下空间为以后的原型。(如果你有更好的想法, 如何标记 "引脚数字", 以适应这样的安排, 我全神贯注。我考虑过 A1 - a9 , B1 - 9 等...只是为了表明这些数字 *不* 对应于将安装的可能较小的芯片上的引脚数。我更清楚, 但被发现滑倒在 Tqfp100 适配器上, 装有较小的设备) 。再次, 你可能会说 "哇?!在这里,布局是专门设计,以占据尽可能少的空间,而*也*很容易"跨越"与32针IPS,甚至40针,耶诺,与一些额外的孔在结束。

所以, 这似乎有点可笑, 但考虑 sdramthingZero 的零件到目前为止...我们有一个40针DIP(AVR),一个SSOP-20(74xx574闩锁),和两个SOC-14的(74x00NAND)。(不过,由于这是设计,我可能会选择SSOP-14的未来订单)。再次,考虑此单板设计将 *两次* 来处理 DIMM 插座...在一个板上, 我可以把 Avr 扔到上面的布局上, 而不是浪费一大堆洞在 Dip 下。在其他板上, 我已经可以处理我的三个 7400 系列芯片中的两个...再次在同一工作区中。

而且, 我目前正在研究一个更通用的 Soic 突破...考虑到它们是常规面包板间距的一半, 这并不难...这意味着, 当它们未填充时, 该空间可以用作常规的 "ol 面包板":

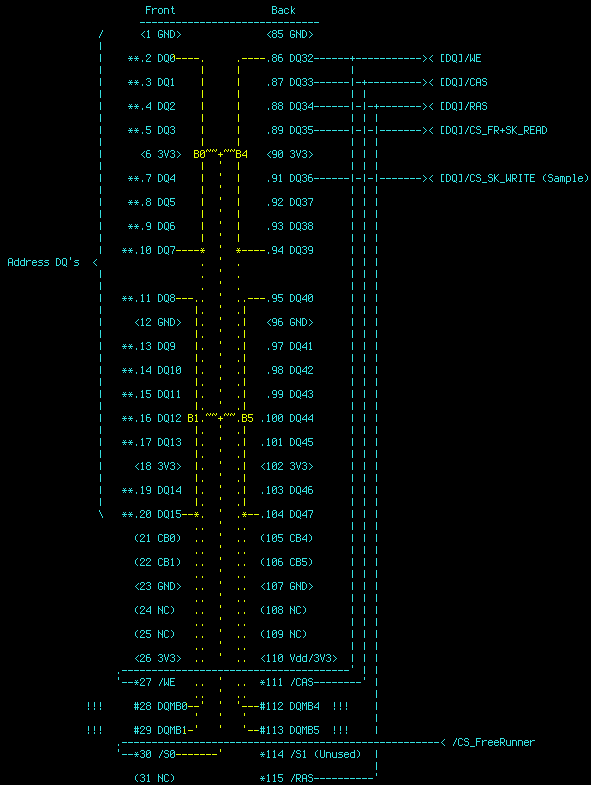

简要回顾(在以往的日志中更好地解释):采样记忆的一部分将用于圆形预缓冲器。然后,当检测到触发器时,它将跳出循环缓冲区,并开始在剩余内存中采样。

因此,这个想法是加载"自由运行器"(内存控制器)与两个顺序的"激活[行]"命令...第一个将激活循环预缓冲区中的下一行,第二行将激活预缓冲区外部*外部* 的第一行。但是:根据是否检测到触发器,将只执行这些"激活 [行]"命令的 *一个*。

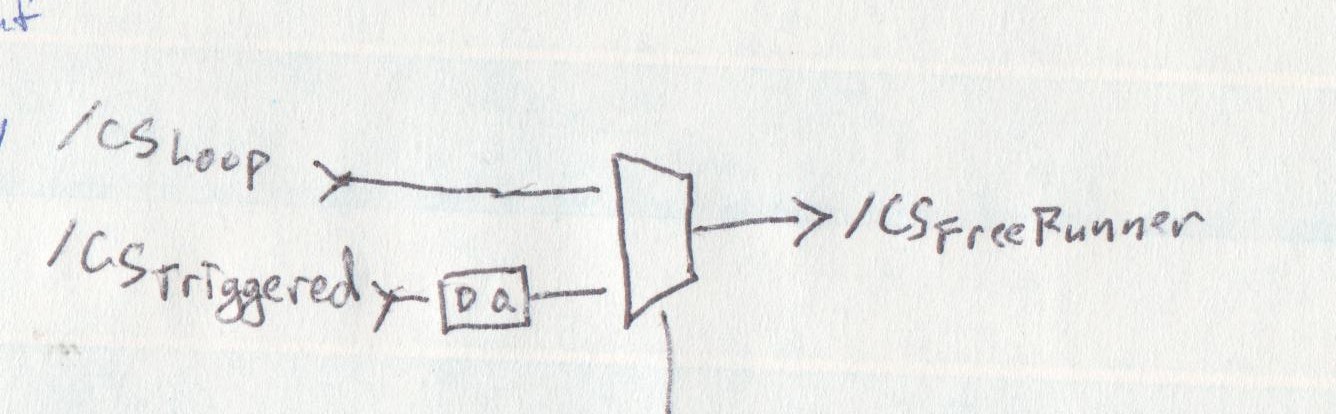

以前,只需为两个"激活"命令输出一个"芯片选择"信号,同时只输出 *第一* Activate 命令即可处理此操作。第二个将是"禁止"。然后,触发器将控制 MUX,该 MUX 可以选择性地将"芯片选择"延迟一个时钟周期。因此,当触发器发生时,最初与第一个"Activate"命令一起选择的芯片现在将延迟执行 *第二* "Activate" 命令,导致系统退出循环预缓冲器,并输入顺序采样内存。下面是一个"简化*"示例。(请注意,/CSLoop 和 /CSTriggered 应连接在一起,以便将单个 /CS 输入连接到电路):

(请注意,这两个"激活"命令之间发生触发器的情况有问题,但在以前的日志中已经处理过。概念仍然相同;有选择地延迟输入 /CS 信号)。

触发后,此系统将延迟 *所有* 芯片选择 *所有*命令...包括读/写命令。没关系...所以,只需重复每个命令两次,只会执行一个...没什么大不了的

我可以再次进入"自由运行者"(内存控制器)的工作原理的细节,但我已经在许多以前的日志中已经看过了。但是,由于它是如何工作的,还有一个轻微的障碍...大多数命令可以稍微移动,而不会造成麻烦。但是,实际上(理想情况下)有两个命令必须背对背地发生。"读取"命令告诉自由运行者从下一个内存页开始执行命令,"写入"命令告诉示例内存在其下一个内存页采样数据。

(这是因为 Read 命令具有固有的"延迟"...直到几个时钟周期之后才会启动,而 Write 命令没有延迟,它立即开始。因此,这两个命令可以在不同的时间执行,但实际上将*同时启动*,保持自由运行和侧踢同步)。

也就是说,如果我在触发器发生后延迟芯片选择,那么我必须有两个读命令,后跟两个写入命令,但由于读取命令和写入命令实际上(理想情况下)必须发生在特定时间,触发器处理程序将影响这一点。他们不能背对背。它可以是解决的,但不是理想的。

然后大杜:

我真的只需要延迟 "激活" 命令...或者,更确切地说,我真的只需要选择两个激活命令之一...理想情况下,其他命令是独立的...

到目前为止,对于这个项目,我已经得到了自由跑和运行,基本上这是最复杂的部分。但是,我忘了侧踢*也*需要初始化,根据SDRAM初始化序列,以及一些其他的事情,以及,如刷新。与"写入"命令(用于将 *采样* 数据输入侧踢)不同,其他一些命令不能*重复执行(例如,通过将 /CS 线路保持活动状态超过一个时钟周期)。而且,由于我们的主机接口很可能比SDRAM时钟慢得多,确保/CS仅在一个时钟周期中处于活动状态的一个方法就是插入一个"一次"电路...

一次电路采用"主机"的长/CS 脉冲输出,并缩短为只有单个 SDRAM 时钟周期的脉冲。

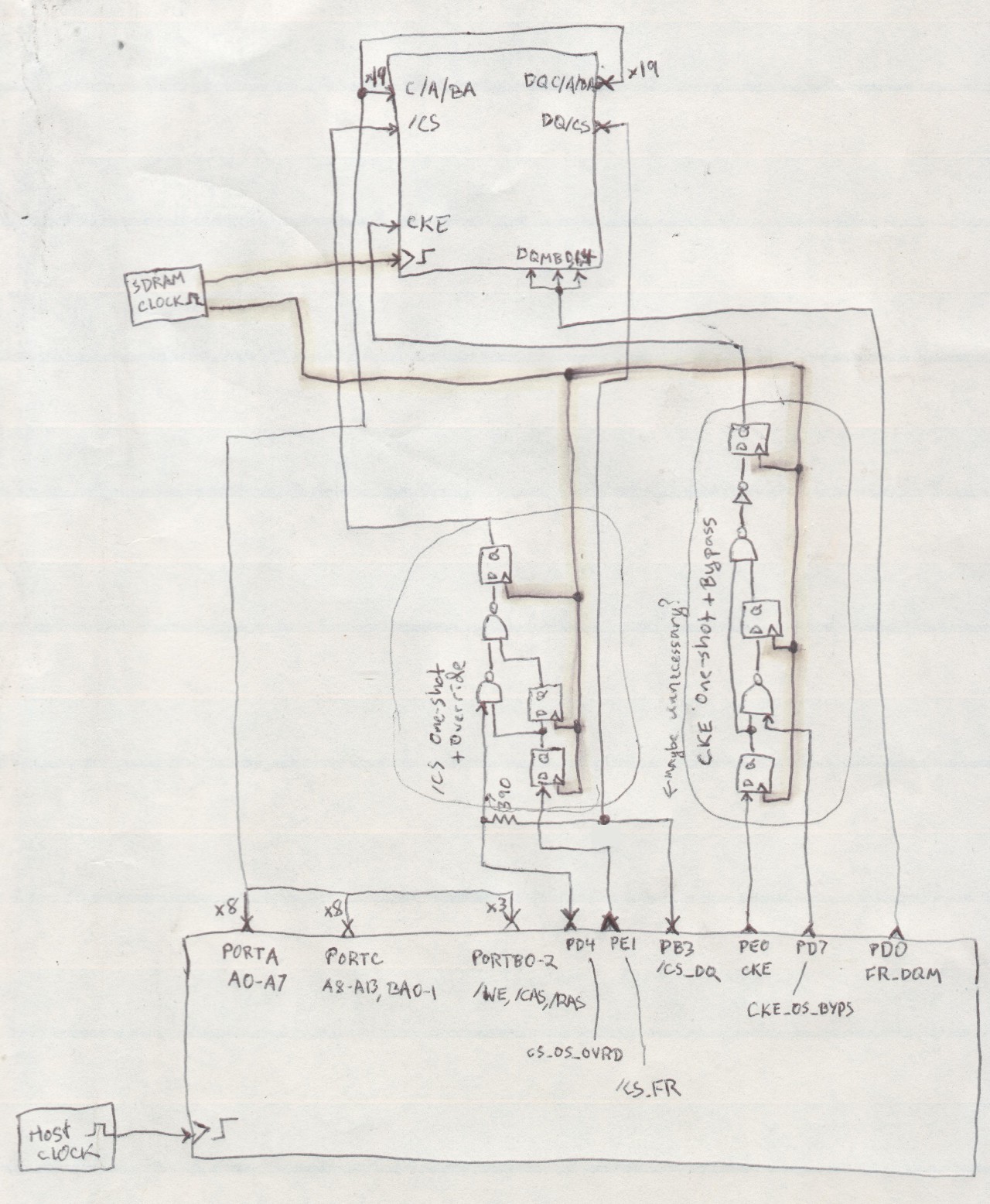

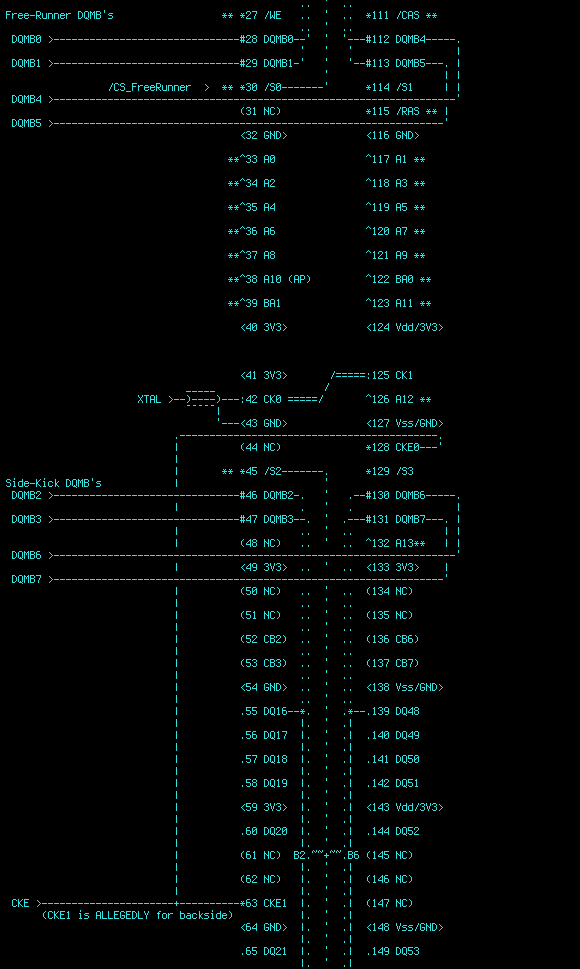

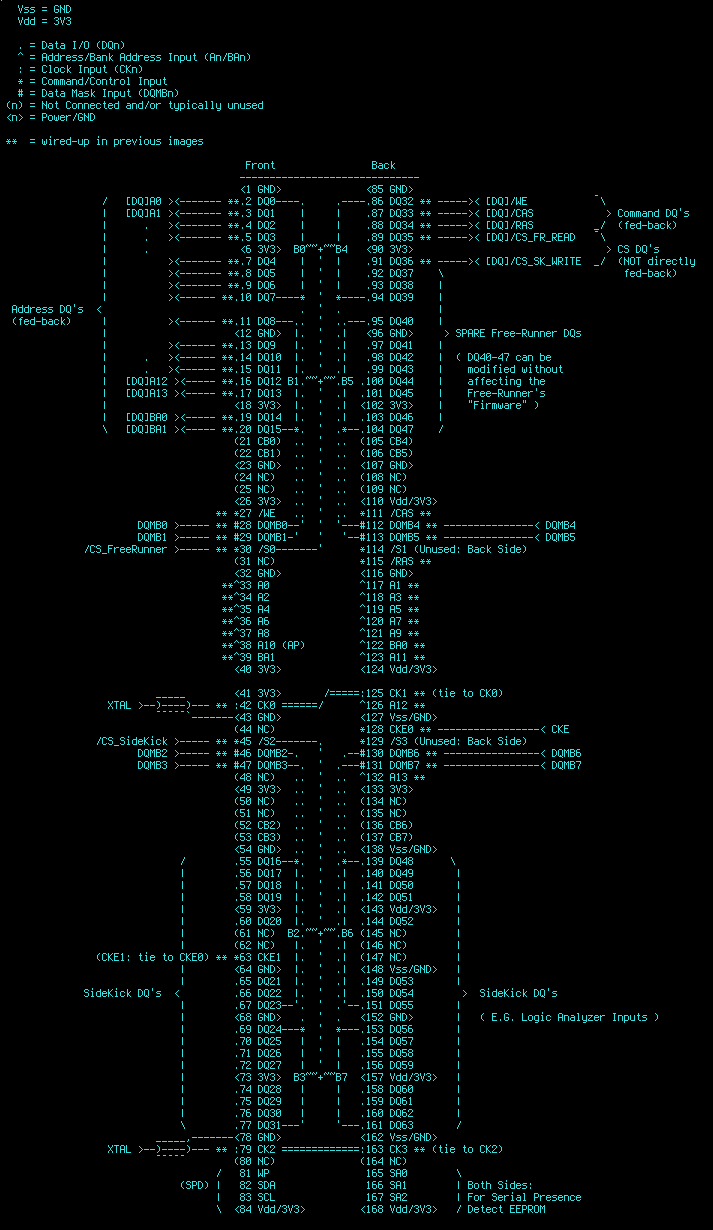

这里是免费跑步者, 作为当前有线...(自由跑者是顶部的"芯片")。请注意主机和自由运行器之间的"/CS 单次拍摄+覆盖"电路。

请注意,我的计划是在两台设备之间共享 CKE,因此我不需要重复CKE单次电路,只需重复 /CS单点电路)。

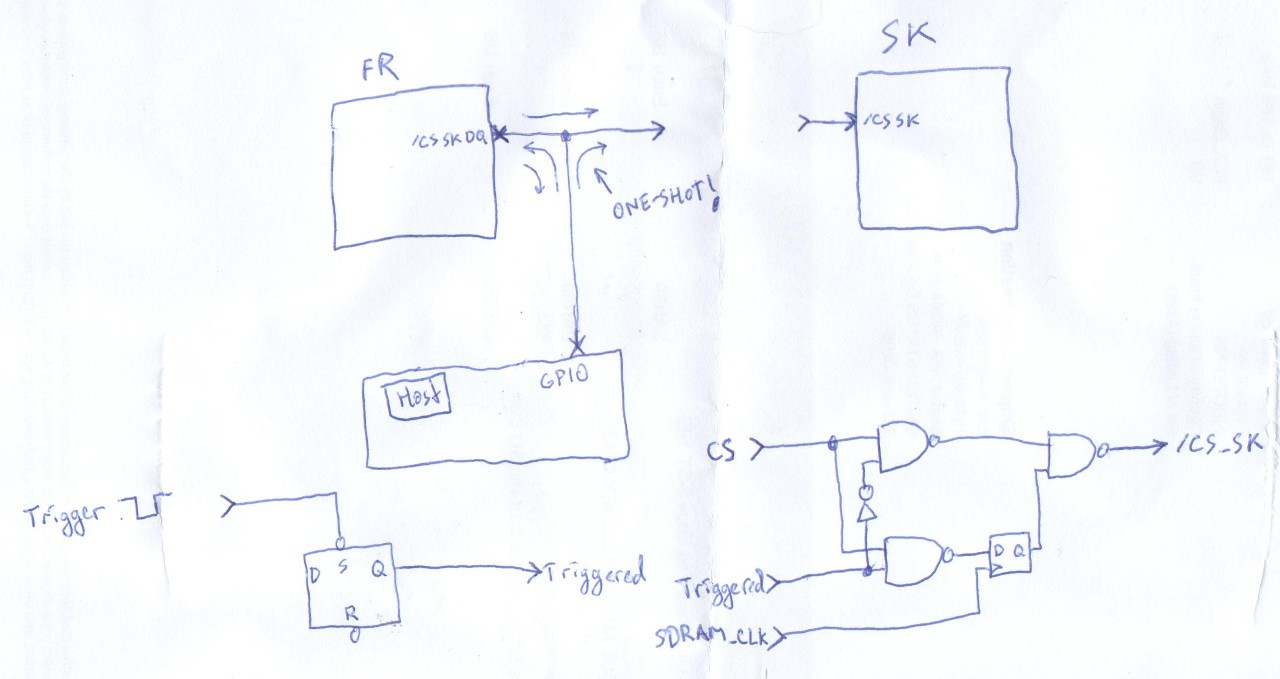

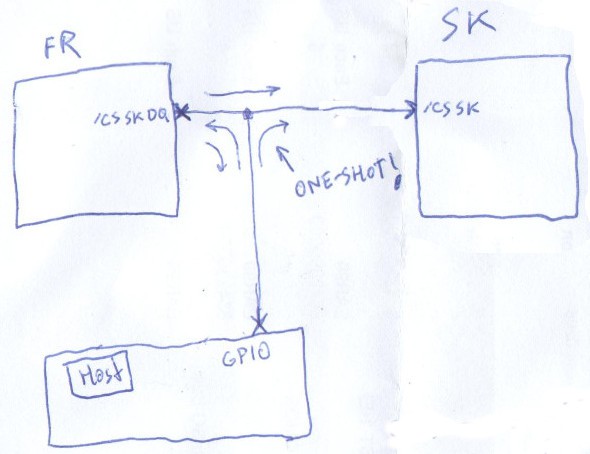

下面是一个更高级别的图表,显示自由运行者与侧踢的 /CS 输入接口的免费运行器的 CS 输出。

此图还显示了触发器处理程序电路

K - den...如果我有这个直...我们基本上可以忽略侧踢上的触发器处理程序...

第 1 步

除非你是受虐狂,否则不要遵守这些指示。他们还没准备好...即使作为后续,如后所述。查看最后一个"说明"中的"说明状态"...那也都过时了。

注意:这些说明是*在没有办法*足够完整的功能sdramThingZero,但...但我会添加到他们作为我自己的原型的进展。欢迎您继续关注!(莱姆知道, 如果你这样做!

这个原型是低速版 ... ...可能仅限于 16mhz 之类的东西, 因为是建立在无焊面包板上的...使用定制PCB,绝对可以实现更快的采样速度。但那是一个路要走。

我会尽量使这些说明作为通用的(对于任何SDRAM DIMM,你可以选择)。

第 2 步

选择 DIMM:

SDRAM (PC-66, PC100, PC133...)

最好是单面(用于此原型)

双面 DIMM 只有一半的内存可用于此 sdramThingZero 原型

抱歉,DDR+ 支持还有很长的路要走(如果真的)。

SODIMM (来自笔记本电脑) 尚未 "支持"...

DIMM 必须至少使用两个 *单独* 芯片选择:

万用表

验证引脚 30、45、114 和 129 之间没有短路

(我不知道那个制造商是如何逃脱称它为 "PC-100", 它如何工作在许多系统中, 也没有听说过更多关于很多油炸主板)

(嘿!如果你碰巧有一个双面 DIMM 与 30 短路到 45, 和 114 到 129, 但不是在 30 和 114 之间, 那么你可能只是发现一个完美的用途, 否则狗屎 DIMM, 不应该安装在主板上!但我不会进入如何使它与 sdramThingZero 工作的细节, 因为它可能相当罕见)

验证是否有两个芯片选择,每个选项连接到一半的可用 IC:

在 Pin30 上放一个万用表探头

将另一个滑下每个芯片上的针脚,直到听到蜂鸣声。

引脚30应连接到 SDRAM IC 一半的一个引脚

对 Pin45 也这样做,它应连接到剩余的 IC

注意: 待办事项

芯片选择可以连接到交替 IC,例如

一个芯片选择可以连接到左侧的四个 IC,另一个芯片选择可连接到右侧的四个 IC。(注意:这是根据英特尔PC SDRAM 未缓冲 DIMM 规范,位于我的"文件部分")

这是一个大 TODO:根据它们路由到哪些芯片,更重要的是,根据这些芯片连接到的 *字节* 引脚,可能需要相应地更改 sdramThingZero 布线!嗯...PC100 规范(第 5 节)显示/S0 应路由到与 DQ0-15 和 DQ32-47(在 PCB 的对立面)关联的 IC,/S2 应路由到与 DQ16-31 和 DQ48-63 关联的 IC,这对应于 CS 被分组到"左"和"右"分组,而不是交替。

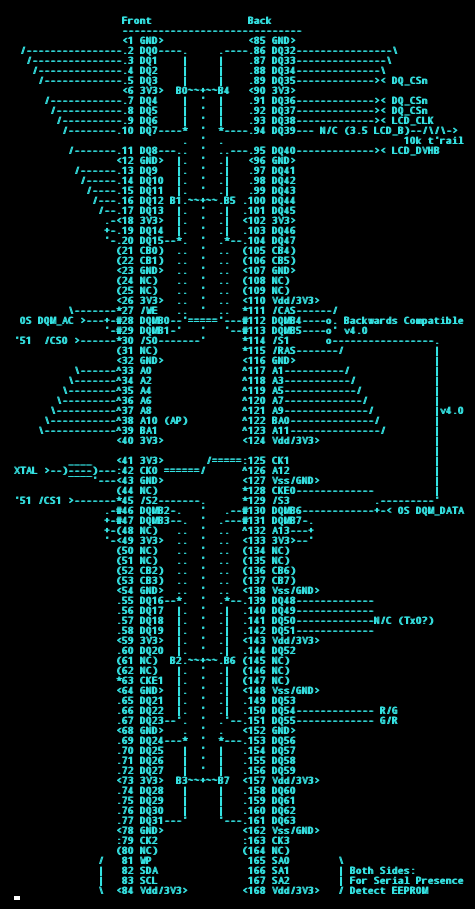

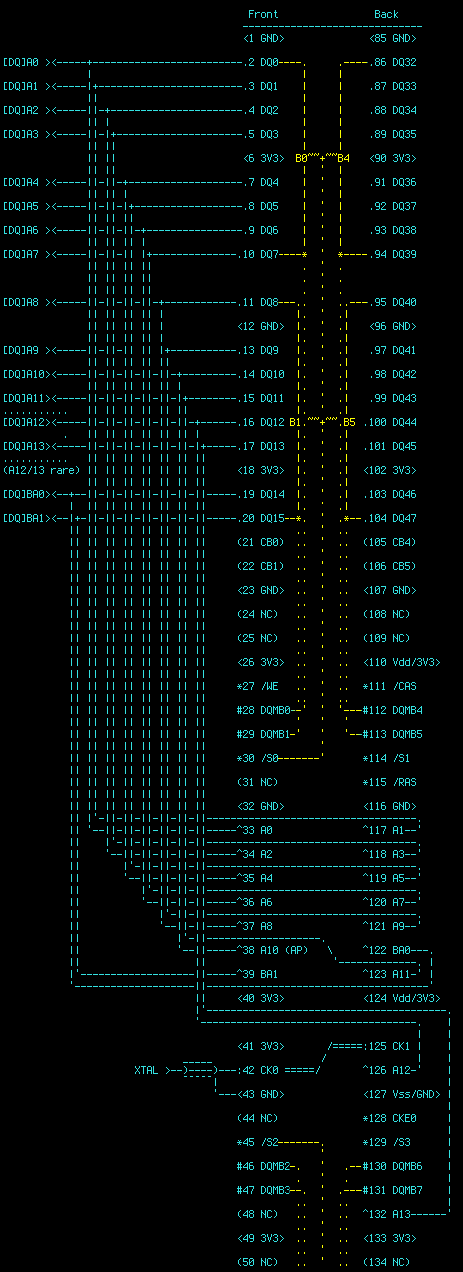

(只查看此 DIMM 的引脚/映射...这是[旧]示意图...新的示意图在以下步骤中)。

第 3 步

规划您的方法

对于这个早期的原型,我计划使用无焊面包板...

我不会使用所有 32 位, 可用于逻辑分析...也许现在只是少数, 我不想焊接 [所有这些引脚] 为这个概念验证。(这是最好的留给 Pcb!

再看看上面的图像,可以看到还有相当多的针脚要焊接起来 ... ...

那么,我怎么把这东西和面包板连接?

正常的面包板线是相当重负荷的,直接焊接到 DIMM 的引脚将最有可能撕裂引脚(又名"Pads")一段时间后。所以,这是一件好事考虑。

我碰巧有一堆更薄的实心铜线从旧的电话线...这些东西在新的面包板工作得很好, 但旧的破旧的面包板可能不会与这些电线紧密接触...所以,再想想你要做什么...

如果有什么会先失败, 它会在连接!

第 4 步

焊接它们地址线(和时钟)

sdramThing 背后的核心概念是将(最终)直接反馈回SDRAM 本身的命令加载(一半)内存位置。考虑到 SDRAM 的特性,可以将这些地址(和命令)引脚*直接连接到数据引脚。它需要一点软件才能工作, 但这比一堆多点更容易!

因此,首先,让我们将地址(和银行地址)行焊接到相应的 DQ(数据引脚)。而且,一定要留下好几英寸连接到你的面包板!

(黄色表示 DIMM 的高级别/内部布局!E.G. 不要将 DQ0 焊接到 DQ7!)

(请注意,A12 和 A13 很少见...我还没有遇到一个 Dimm, 使用他们...)

真的,只要它们都在同一个芯片选择上,DQ 的焊接就无从来。(/S0,引脚30)。但是,是的,它[确实]重要的*地址引脚是什么,所以尽量保持他们很容易识别的顺序,使面包板更容易。

佩丹蒂克:对于这个低速(面包板高度限制)原型来说,它可能不是非常必要的,但是保持电线尽可能相等的长度是很不错的。上次我这样做的时候,我切掉所有的电线,然后焊接起来。(我上次用"线包装"线,30AWG,但那对面包板来说太小了,所以在 DIMM 针之间大概 30AWG,还有更厚一点的东西可以到面包板去)。

彭丹蒂克 2.0:是的...我要留下一些 Dq 的浮动...是啊, 那不是个好主意...但到目前为止, 它并没有引起问题...如果你真的担心它,等到这整个事情走到一起,然后通过上拉电阻将那些剩余浮动的DQ与V+连接。

高级:我还努力保持反馈地址/命令引脚尽可能少的字节(B0、B1、B4 和 B5)。这样,可以将专用字节用于其他目的...例如,输出自定义波形...在这种情况下,将这些特定信号放在自己的 DQM 上非常方便,因此无需修改"自由运行"(Fed-Back)命令即可重写它们。

高级 2.0:我正在考虑使用(小型)圆形缓冲区和外部触发器输入,允许一些"预触发"数据存储。这可以通过例如使用两个单独的 DQ 进行 A0,中间有一个多路复用器。在触发之前,它会循环浏览一小部分内存,覆盖旧样本,直到检测到触发器。一旦触发,复用器将选择第二个 DQ 为 A0,导致系统通过整个内存阵列前进。现在,这是尼。这样的事情也可以在别处做...事实上,这种技术用于芯片选择...但是,我会保持这个初始原型非常简单。不过,考虑使用布线/焊接技术,允许以后在生产线上进行此类修改,;)

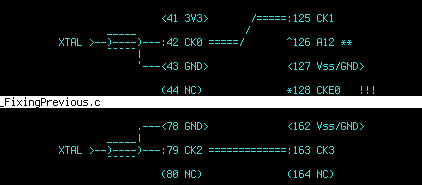

时钟:

请注意,它被发现是*相当*有利于*屏蔽*时钟线...我用电线导致一个旧的 Wifi 天线 (发现在一台旧的笔记本电脑), 但这可能是有点过头了...可能 (屏蔽) 耳机线会很好 '不。

并且,是的,焊接 CK0 (引脚 42) 到 CK1 (引脚 125)。这是短期的,不需要屏蔽。

第 5 步

焊接命令线

与地址行类似,我们有一些命令信号,它们直接连接到数据 I/O 的...

请注意,当芯片选择处于非活动状态(/S0、/S1、/S2、/S3 高)时,这些连接的 SDRAM 芯片将忽略该命令。

因此。。。我们有两个独立的"单位",输出命令的"自由运行器"和"侧踢",在此逻辑分析器的情况下,它采样数据并存储在其内存位置。

我们将在自由运行器中存储两组单独的命令:自由运行者(READs-导致它继续按顺序输出命令)和侧踢(WRITES-导致侧踢到示例数据)的命令集。

从侧踢中回读采样数据将由主机处理。

高级:由于写入和读取延迟不同,"READ"命令可以存储在与"WRITE"命令不同的内存位置,并且这两个系统将保持同步。

高级 2.0:侧踢不必局限于采样数据,它也可用于输出数据(非常像前面提到的"备用字节")。因此,侧踢的芯片选择线不会[直接]绑定到关联的 DQ。相反,它将通过多路复用器提供,多路复用器选择侧踢是注意"读取"还是"写入"命令。

TODO:这在#sdramThing4.5"逻辑分析器"中是必要的,因为它是一个"采样/重复"逻辑分析器。字节对字节。所以, 有什么理由, 真的, 有一个复用器在侧踢的芯片选择... ???嗯。。。注意:将 CS 线路直接连接到 DQ 是无法操作的,因为这样做实际上会同时向 SDRAM 发送命令,同时尝试加载该 SDRAM 的 DQ,该命令应稍后发送。我认为这个MUX是一个好主意,即使"重复"没有实现。

第 6 步

Esot-失败的帐户(到目前为止):

Esot-失败的帐户(到目前为止):

时钟:Ck2 (和 Ck3?) 也应该连接到你的水晶振荡器...(稍后在面包板上)。

(显然, 我的 Dims, 以前, 不匹配英特尔规格...据称CK0和CK2,引脚42和79,应该用于单面 DIMM。因此,我们更不会尝试找出芯片使用哪些 CK# 输入(这可以通过万用表完成),您只需焊接所有 CK 输入。)

推荐操作过程:让 *两* 屏蔽电缆运行到 DIMM 的时钟输入。

这些电缆应该是漂亮的杜恩关闭匹配的长度...我的意思是, 一厘米左右并不重要, 在面包板的速度, 但不要削减一个比另一个故意短。坦率地说, 这用于面包板和 DIMM 之间的所有电线, 以及 DIMM 本身的重新反馈的电线...

注:就目前情况,我一直专注于单面 DIMM。如果你选择双面 DIMM,现在无论如何,只是期望你只有*一半*可用内存为您的项目...(这可能是一个简单的修改, 但是 Nyi...关于添加其他芯片选择 Dqs 的一些...)

高级:如果你的 Dimm 有 Ecc (罕见, 但可能...), 你可以同时采样 40 位 (而不是 'n 32)!但是: 这样做需要交换自由亚军和侧踢, 由于芯片选择的路由...这是。。。NYI,而且,进一步,将需要(一点点)额外的电路...如果你想尝试一下,记住它!另一种可能性是使用自由流道上的额外字节,再次,用于额外的波形输出。

第 7 步

焊接起来, Cke 和 Dqmbs!

CKE是"时钟启用"输入,它使sdramThingZero成为可能。

(在#sdramThing4.5 "逻辑分析器"时代, 我的印象是," 主机" 总线运行速度比 SDRAM 慢的唯一方式是, 在 "主机" 和 SDRAM之间有*精确* 计时...这不可能与大多数主机的 Gpios 。Cke 应该解决这个要求!使 sdramThingZero 成为可能。Wee!)

Ddr?对不起。。。DDR 不利用 CKE :/DQMB是数据掩码输入。通过利用这些,我们可以选择*哪个*字节- 8可用64位宽的 DIMM - 被访问,尽管几个芯片共享芯片选择。

但更重要的是,我们可以控制*访问*字节时。这对于直接反馈布线非常重要。E.G. 说我们要将值 0xff 写入字节 4,地址 0...

以下是我们早期指令中的接线片段

问题是,写入指令必须加载到 CAS、RAS 和 WE 输入。但是,当命令时,"写入"指令将当时 DQ上的数据(连接到 CAS、RAS 和 WE)加载到所选内存地址中。我们将将写入说明指令写入 Byte4 地址 0,而不是将0xff 写入 Byte4 地址 0!

那么,我们如何将 0xff 加载到字节 4?

首先,设置 DQMB4,以便 Byte4 *忽略* DQ 上的数据(写入指令)

在地址 1013 开始写入突发

将 0xff 加载到字节 4 的 DQ

然后 11 SDRAM 时钟周期后, 写入突发现在已环绕到地址 0

取消掩天 DQMB4(对于一个 SDRAM 时钟周期),以便将 0xff 写入地址 0。

你可以看到必要的 *确切* 时间..."主机"必须确切地知道 *准确* 何时发生了 11 个 SDRAM 时钟周期,以揭开 DQMB 在正确的地址位置的掩。(而且, 它必须足够快, 所以!利用 CKE 允许一个新的 "技巧"...与其在地址 1013处启动写入突发,等待 11 SDRAM 时钟周期,我们现在可以在地址 1023开始突发,并等待,只要我们想绕过解开字节...

首先,设置 DQMB4,以便 Byte4 *忽略* DQ 上的数据(写入指令)

开始写爆发, 比来说, 地址 1023

在写入指令之后立即在时钟周期上禁用 CKE

时钟现在将被忽略

突发将在地址 0 暂停(地址 1023 将在写入指令时写入,但当然是 DQMB)

扭动你的拇指做任何你想做的事...有 Lcd 要更新吗?去吧!

将 0xff 加载到字节 4 的 DQ

取消掩天 DQMB4

*一* 时钟周期的频闪 CKE。

好!现在,您可以让 linux 系统运行键盘中断和各种其他任务,并且仍然编写您想要写入的确切内存位置,甚至通过 *真的*速度较慢的 GPIO 端口。

唯一的事情是,当总线比 SDRAM 时钟慢得多时,我们如何只对一个 SDRAM 时钟周期进行频闪 CKE?这就是一枪进来的地方...稍后将详细了解它们。

Ad...这个解释可能有点多这个指令, 其中你只需要焊接到 Cke 和 Dqmb 引脚...

第 8 步

最终 DIMM 焊接

我们几乎完成了焊接到 Dimm 之前, 我们可以得到面包板...将来可能会有些修改, 所以不要把东西密封在环氧树脂里...

电源:图表上标记得很清楚...焊接一些沉重的电线为 3.3v 和 Gnd...你不必焊接*每个*连接器。事实上,我只使用28AWG线焊接到一点3.3V,在上一个版本。所以,你的面包板线焊接到一个垫(或一个电容器?(我还使用了两根大/硬的电线-实际上回形针-作为立场...焊接到接地垫。我还在船上额外钉了一个额外的 22uf 电容器...因为: Ocd 。

(哦, 从技术上讲, 我之前用 3.6v...所以也许更大的电线连接到一个 *几个 * 垫可能会更好地为 3.3v...)

西迪克 Dq 的:这些是可用于逻辑分析的位。我厌倦了焊接, 所以我现在可能只会焊接一把, 也许一个字节。以后,我可能会焊接另一个字节,或者从四个字节中每个几个位只是为了验证我的电路之前设计一个PCB...

在#sdramThing4.5 "逻辑分析器" 中,我从自由运行器连接了 2 位,从侧踢连接到笔记本电脑 LCD (FPD-Link) 上的 4 个信号。我很想把它作为早期的例子,但它基于许多先前的实验,推动该特定LCD的限制,并使用大量的代码来计算帧,Hsync/Vsync计时,和模拟的FPD-Link波形。此外,sdramThingZero的目标是成为一个逻辑分析器的外围设备,所以它的侧踢更多的是用于[采样]数据,而不是[输出]它。但是,如果你陷入你付出的所有努力,到目前为止,这里是几个图像,什么已经完成了与各种以前的版本的sdramThing,和sdramThingZero应该证明更好:

(这家伙在 6 位每色显示屏上显示所有可能的颜色...)

(当连接到褪色 LED 时,此家伙正在重新显示存储在侧踢中的原始样本, 在逻辑分析器模式下。你可以[勉强]找出蓝色"光标",这是存储在"额外的字节"的自由运行者(一个与一个单独的DQM),旁边Hsync/Vsync定时,这是发送在同一线蓝色。FPD-Link时钟信号存储在与自由运行程序命令 DQ 相同的字节上的额外位。这样,在每次移动光标时,都不需要重写 LCD 的时钟信号。

所以, 使用 sdramThingZero,我们将将数据采样到 Side-Kick 中,就像上一个图像中旧系统完成的一样,但我们会将采样数据重新读取到我们的"主机"内存中,以便用更漂亮的光标和标准计时图(或任何您想对数据执行的监视器)显示(和操作!

可以说,不要费心布线所有32位(或连接LCD),但...我们将从一两个LED开始,然后从那里向上移动:)

所以,现在,焊接了几根电线,如DQ48和DQ49,去你的面包板...如果你想分析一些SPI数据或者别的什么,也许有三个。但是,不要忘记哪个 DQMB 与您选择的任何位关联!

上面基本上是整个电线, 应该悬挂从 Dimm 准备面包板...我隐藏了反馈引脚、所选 Sidekick Dq 和电源的详细信息。别忘了那些!此时,DIMM 已准备好进行面包板。

评论

0 / 100

查看更多

2020-08-28

1209

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号