在RISC-V软核上运行Linux的FPGA开发板 - OrangeCrab

收藏

分享

脑图

在RISC-V软核上运行Linux的FPGA开发板 - OrangeCrab

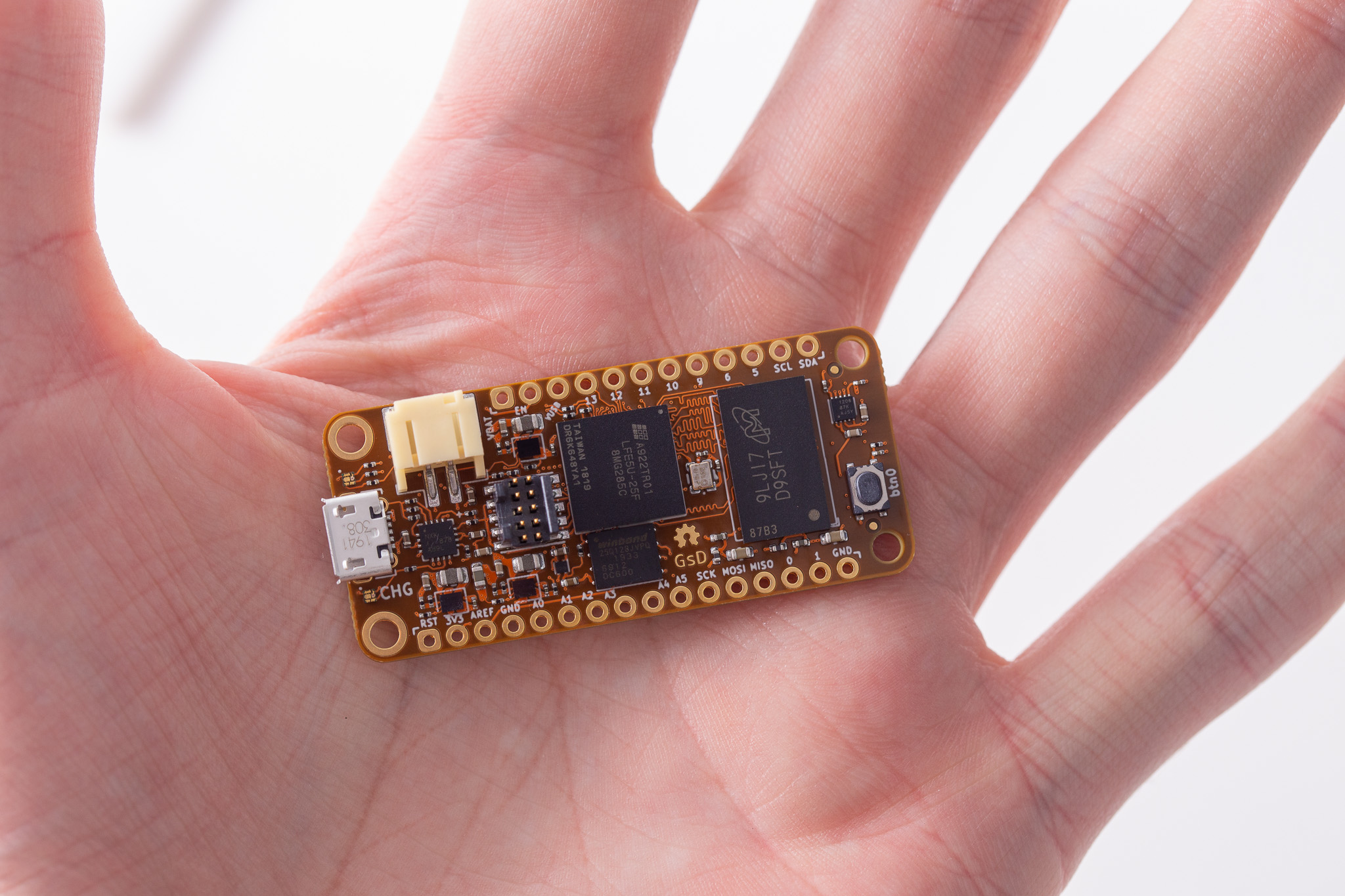

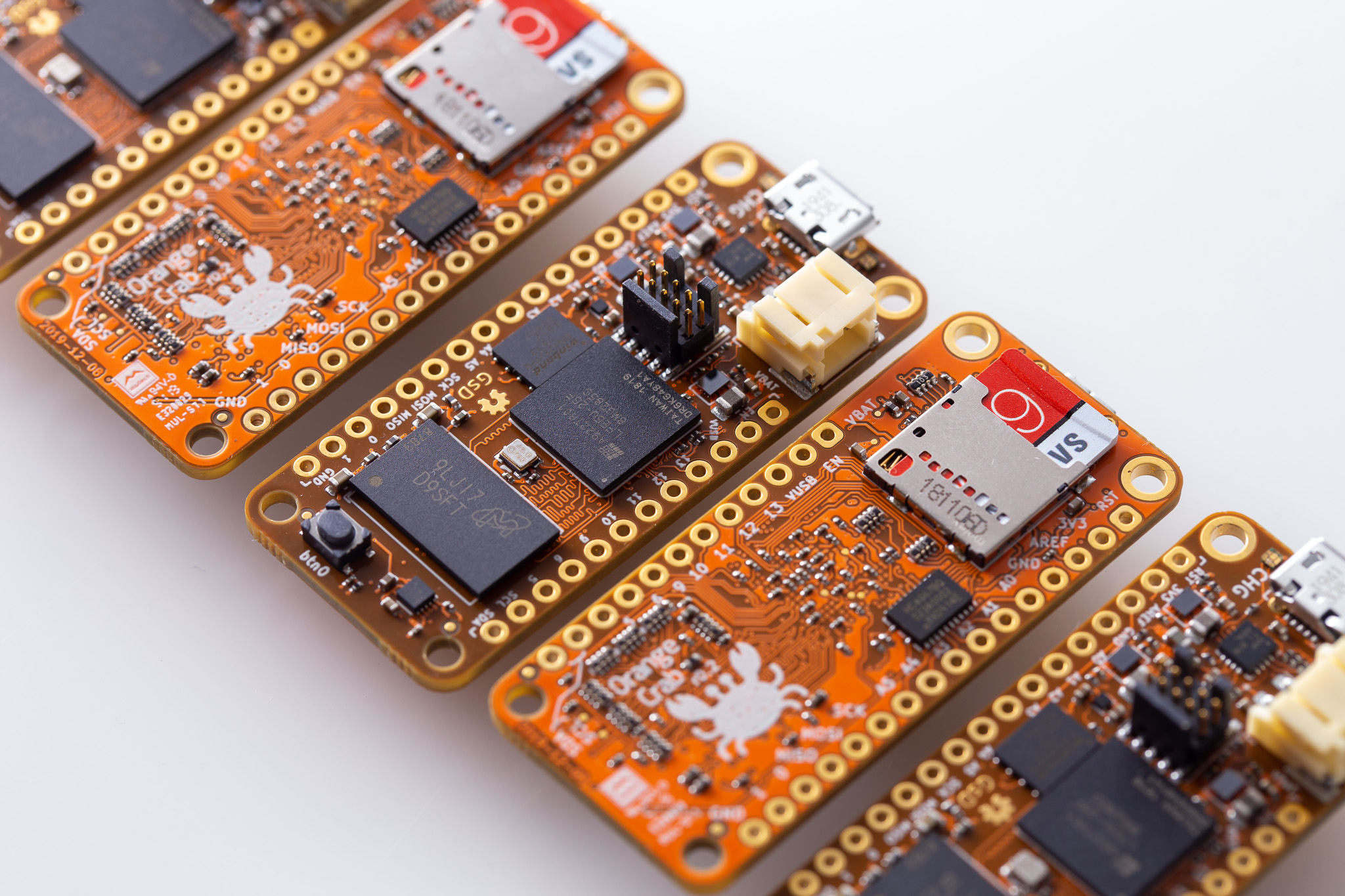

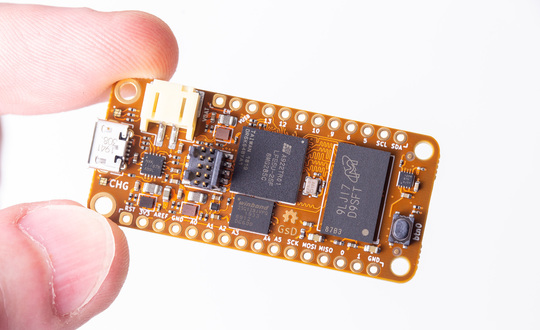

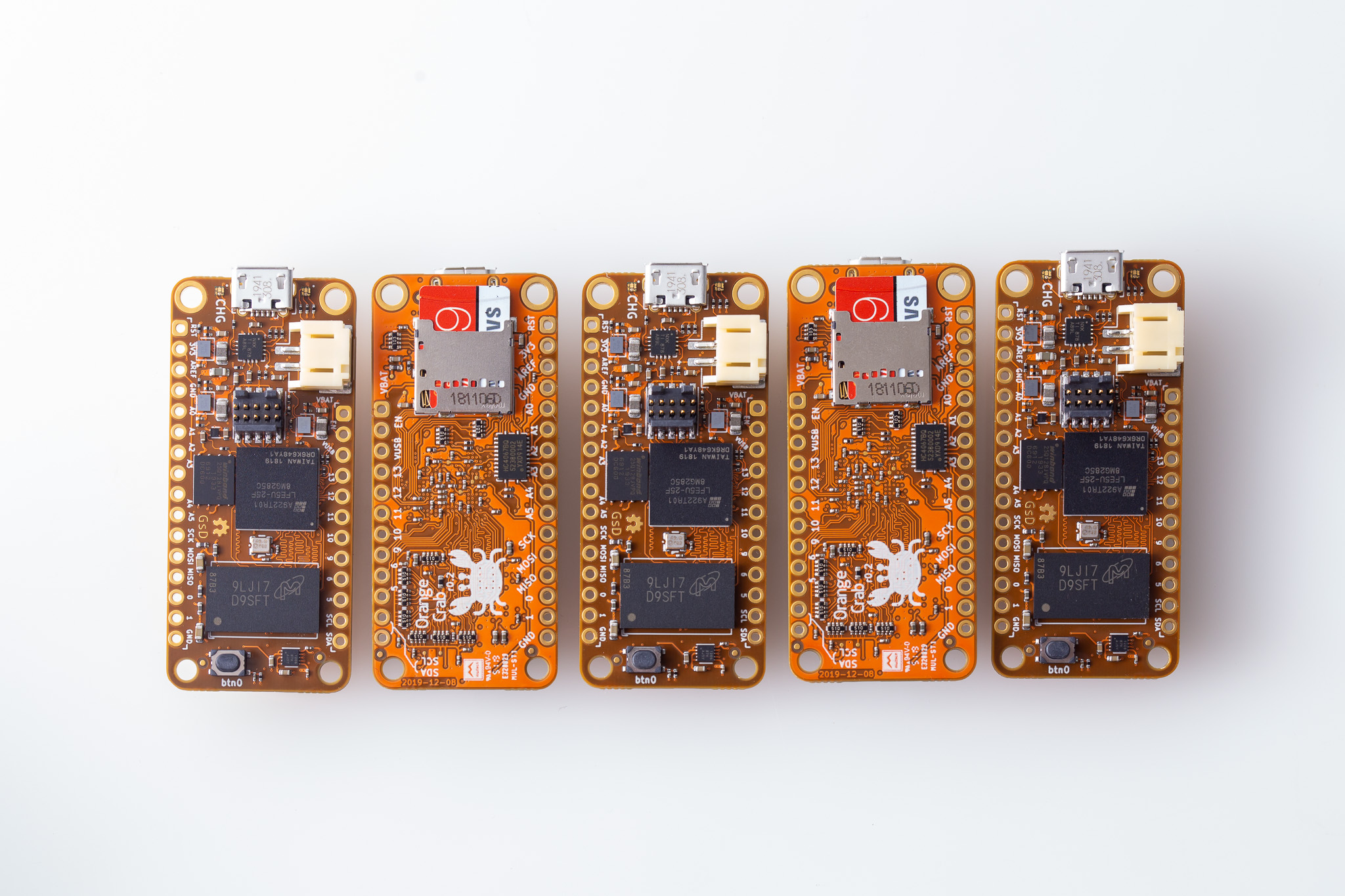

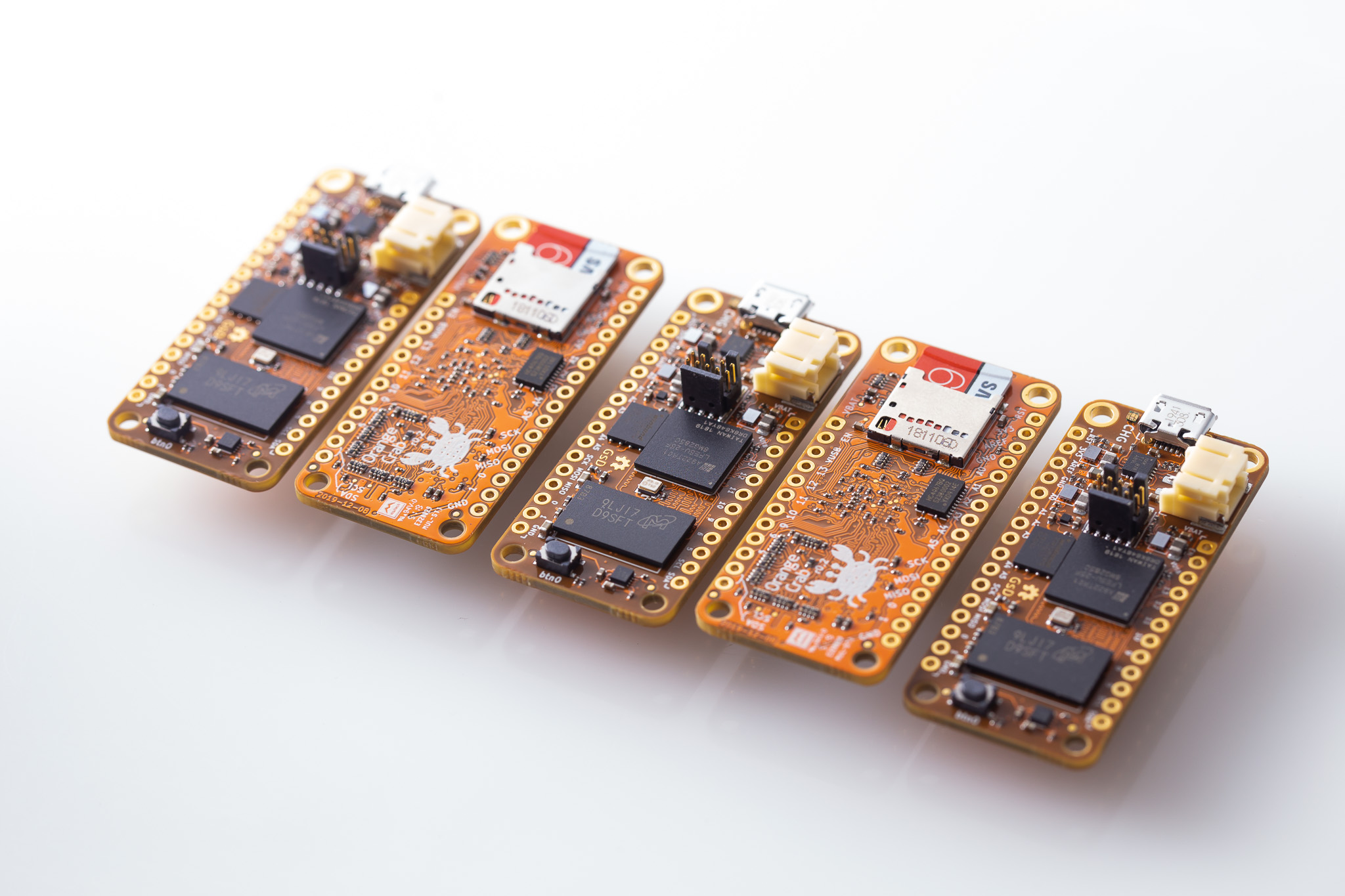

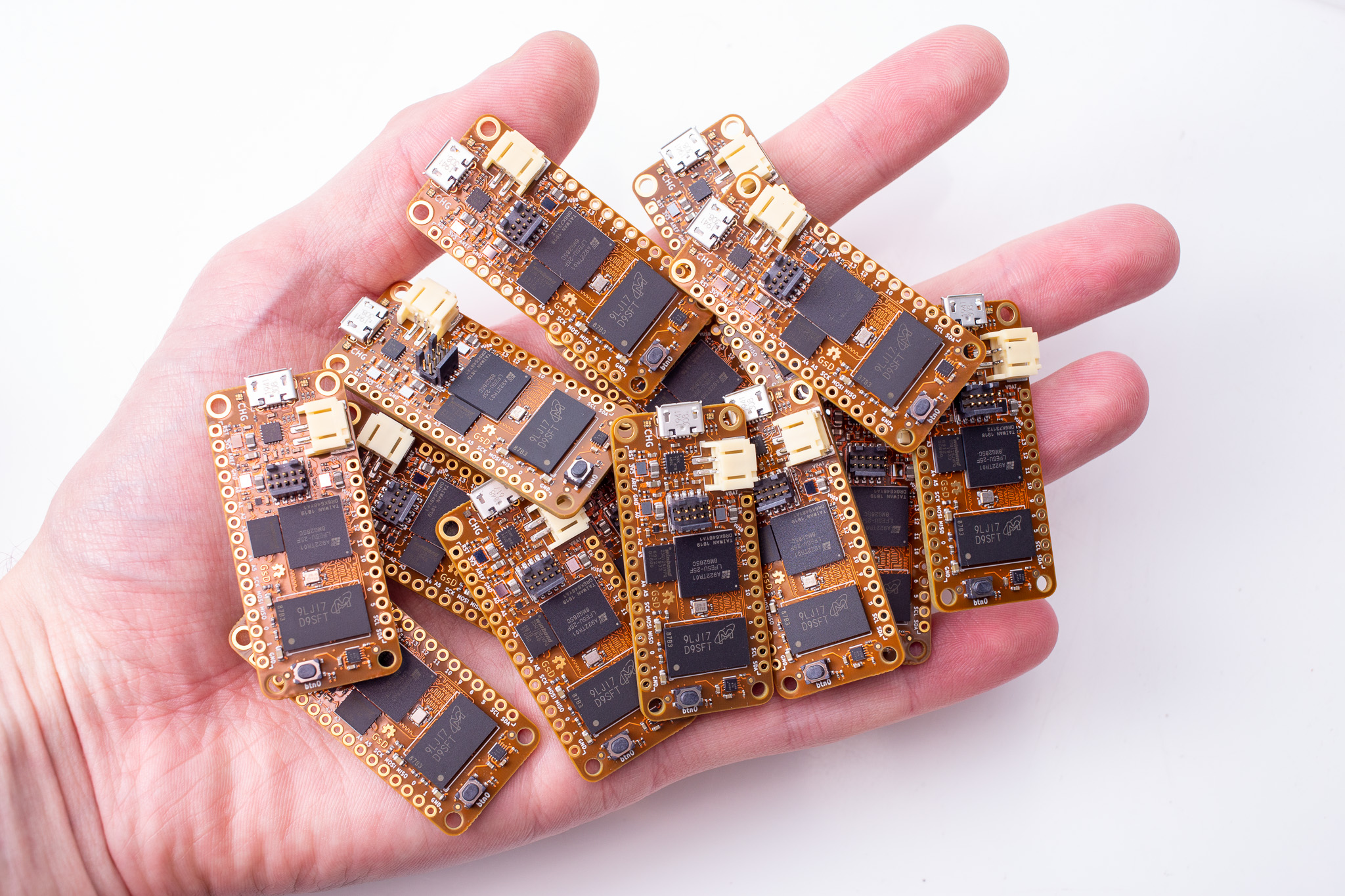

The OrangeCrab is an electronics development board. It is FPGA based featuring an ECP5 from Lattice. The board follows the slim feather board specification from Adafruit. The FPGA is compatible with all open source toolchains and is perfect for experimenting with RISC-V cores. There aren't many FPGA boards available that make use of the ECP5, but here are some distinct features that set this board apart:

Small Compact size (Take it anywhere!)

Direct USB connection to the FPGA (Operate as a DFU, MSC, CDC, or composite device!)

On-board DDR3 Memory (1Gbit!)

Pre-loaded DFU bootloader (No external programmer required!)

It's Orange!

图片

图片1

图片2

图片3

图片4

图片5

图片6

图片7

图片8

图片9

硬件资源

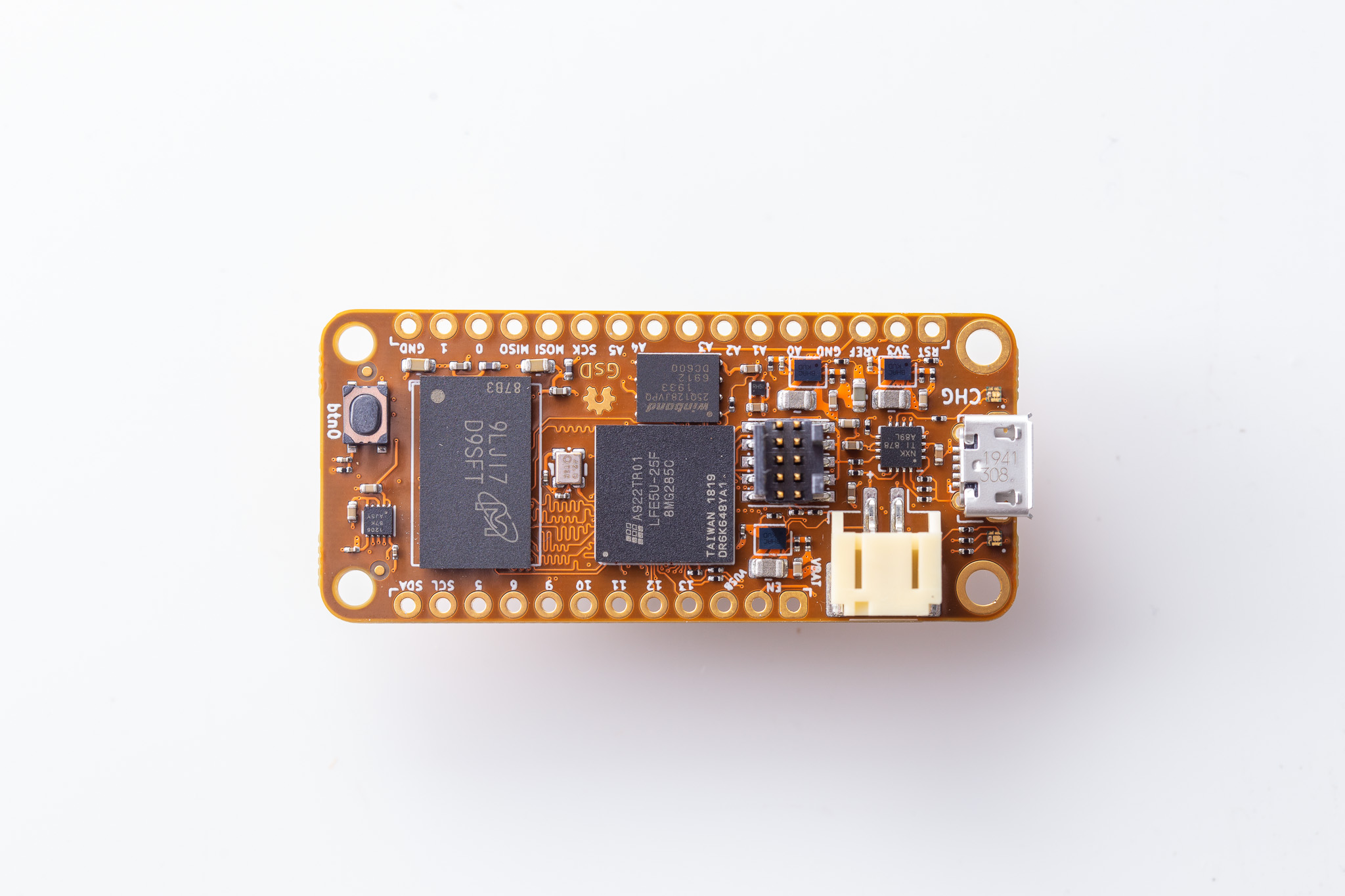

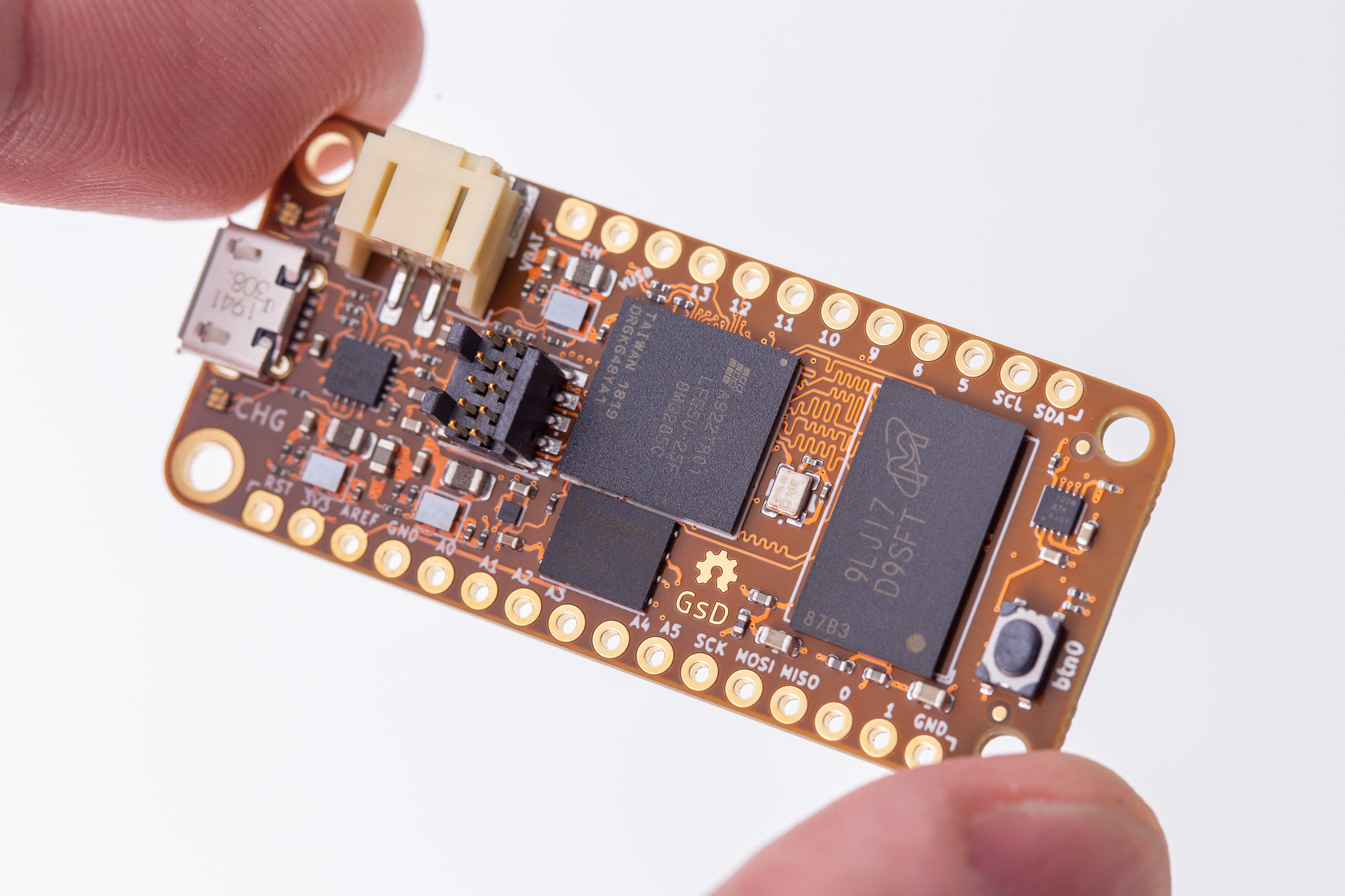

Lattice ECP5-25F FPGA in csfBGA285 package (-8 speed grade) (Part # LFE5U-25F-8MG285C)

24 K - Look Up Tables

1008 Kb - Embedded Block RAM

194 Kb - Distributed RAM

28 - 18x18 Multipliers

PLLs: 2

Internal oscillator

Flexible I/O for DDR3 Memory Support

DDR3L Memory

128 Mbytes (1Gbit)

64M x16

1.35V low voltage operation

Micro USB connection

Full-speed (12Mbit) USB with a direct connection to the FPGA

Non-volatile Storage

128Mbit QSPI FLASH Memory

Bootloader (First 4Mbits)

User Bitstream

User storage (Firmware/MSC backend/etc)

QSPI compatible

MicroSD socket

4bit SD interface (CK, CMD, DAT0-3)

Power supply

High efficiency DCDC for main supplies

Battery charger (100mA), with a charge indicator LED

LiPo battery connector (PH type)

48MHz onboard oscillator

Standard 0.05" JTAG connector

User I/O

1x Button

1x RGB LED

20x I/O on 0.1" headers

Analog System

Analog Mux

SAR ADC, external RC / input comparator of FPGA

Digital bypass

Internal channels for supply monitor

Battery voltage sensing

Feather Format Board

Dimensions: 22.86mm x 50.8mm (0.9" x 2.0").

如何使用

MicroPython + CircuitPython

This is still a work in progress!

Plug the board in and start blinking LEDs straight away with no external tools required.

RISCV firmware

Install the RISCV GCC compiler and start programming the board, code is executed on the SoC created by the bootloader.

FPGA gatware

Update the FPGA gateware using Verilog or other Higher level language: nMigen, Litex, Chisel, etc.

相关文章

使用KiCad画

开源的Bootloader

Which uses an an open source VexRiscv CPU

Which in turn implements the open source ISA: RISCV (rv32im)

Fully compatible with the open source FPGA toolchain and flow:

Yosys- Synthesis

Nextpnr - Place and route

Trellis- ECP5 documentation and utilities.

评论

0 / 100

查看更多

2020-04-25

5302

Copyright © 2024 苏州硬禾信息科技有限公司 All Rights Reserved 苏ICP备19040198号